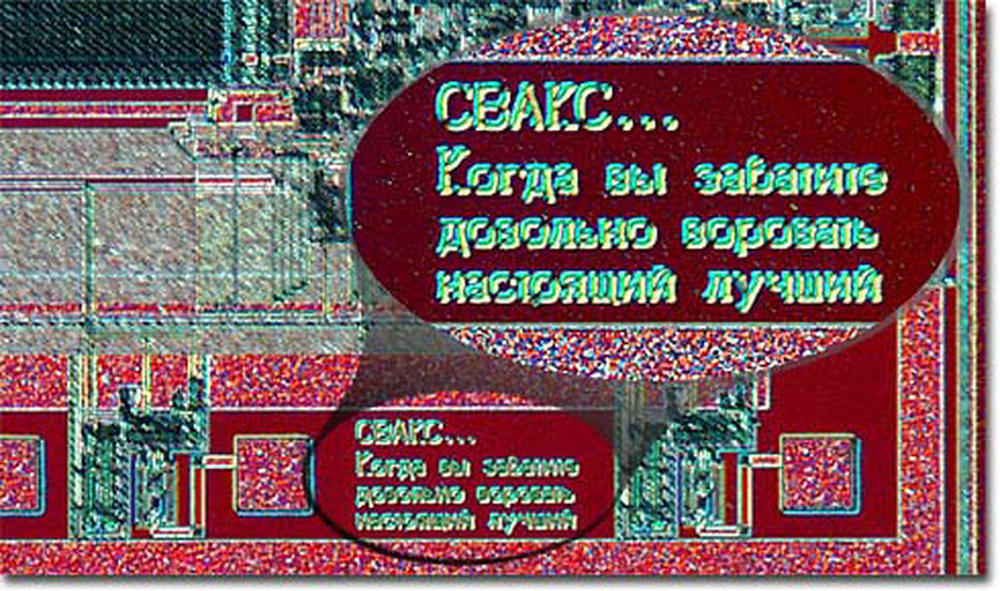

"CVAX: cuando te pones bastante roba lo mejor".

"CVAX: cuando te pones bastante roba lo mejor".La inscripción dejada por los ingenieros estadounidenses para los colegas soviéticos en la topología del microprocesador.

La ingeniería inversa de microchips es un dolor de cabeza para los fabricantes desde los primeros años de existencia de la microelectrónica. Toda la electrónica soviética en un momento se construyó sobre ella, y ahora están haciendo lo mismo en el Imperio Celestial, y no solo en él, a una escala mucho mayor. De hecho, la ingeniería inversa es absolutamente legal en los EE. UU., La Unión Europea y muchos otros lugares, con el objetivo (cito la ley estadounidense) de "enseñar, analizar o evaluar los conceptos o técnicas realizadas en el trabajo de máscara o en el circuito".

Los usos legales más comunes para la ingeniería inversa son los tribunales de patentes y con licencia. El espionaje industrial también es común, especialmente porque los circuitos eléctricos (especialmente los analógicos) a menudo son propiedad intelectual clave y rara vez se patentan, solo para evitar la divulgación de IP y la participación en tribunales de patentes como acusador. Por supuesto, en una situación en la que necesita proteger su propiedad intelectual sin patentarla, los desarrolladores y fabricantes están tratando de encontrar formas de evitar la copia de sus desarrollos.

Otra área no menos importante (o incluso más importante) de proteger los microchips de la ingeniería inversa es garantizar la seguridad de la información almacenada en la memoria. Dicha información puede ser tanto firmware de FPGA (que es, nuevamente, propiedad intelectual del desarrollador) como, por ejemplo, un código PIN de una tarjeta bancaria o una clave de cifrado para una unidad flash segura. Mientras más información valiosa confiemos en el mundo que nos rodea, más importante es proteger esta información en todos los niveles de los sistemas de procesamiento, y el nivel de hardware no es una excepción.

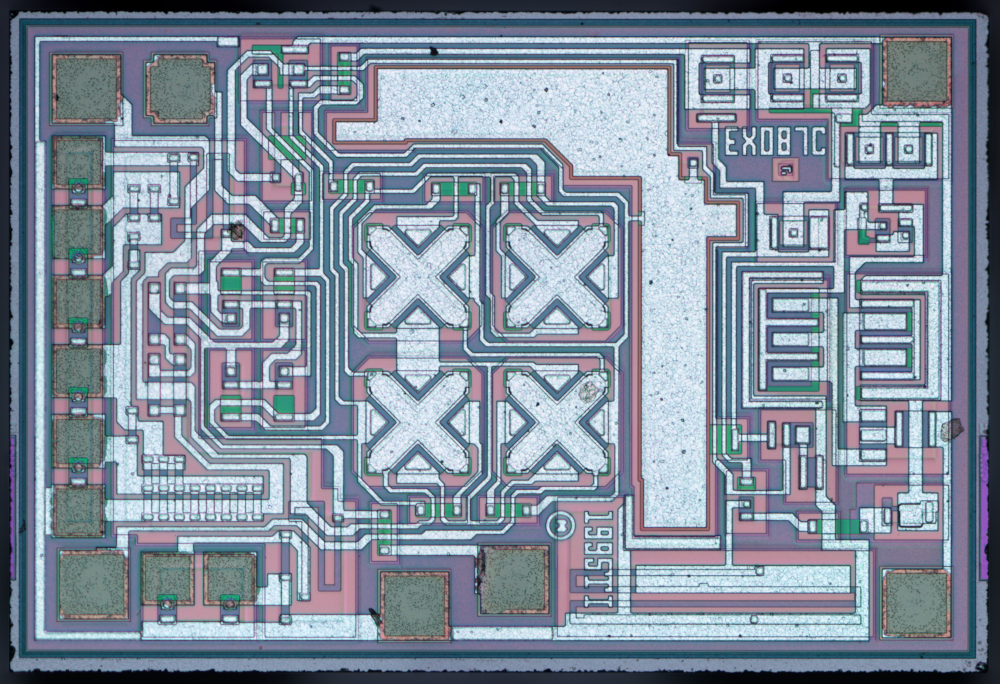

Primero lo primero: algo importante para entender. Hablando tanto de la ingeniería inversa como de la protección contra la copia de datos, debe comprender que no existen métodos de protección absolutamente estables, y todo lo que es real es hacer que el proceso sea tan largo y / o costoso que se vuelva económicamente inoportuno.Hace muchos años, el trabajo de un ingeniero inverso o un pirata microelectrónico era mucho más fácil que ahora. Mire, por ejemplo, esta imagen (gracias a

BarsMonster por nuestra infancia feliz y buenas fotos): con una comprensión básica de la tecnología, restaurar un circuito eléctrico es cuestión de varias horas.

Figura 2. Una instantánea de la topología del amplificador operacional OPA134PA. Fuente - zeptobars.comAquí , por cierto, hay un ejemplo de ingeniería inversa del chip TL431 hecho por Ken Shirriff a partir de fotografías de BarsMonster. Y aquí está la traducción al ruso. El blog de Ken tiene muchas cosas interesantes si te interesa el tema de la ingeniería inversa amateur.Y aquí (¡con cuidado, tráfico!) Hay un informe de la ingeniería inversa del chip Zilog Z80-CTC, realizado en 1979, casi inmediatamente después del lanzamiento del chip. Ahora, este es un documento histórico único, y luego fue información de gran valor comercial y obtenida (a juzgar por varias referencias a estándares militares), probablemente en el proceso de certificación de un microcircuito para aplicaciones especiales.

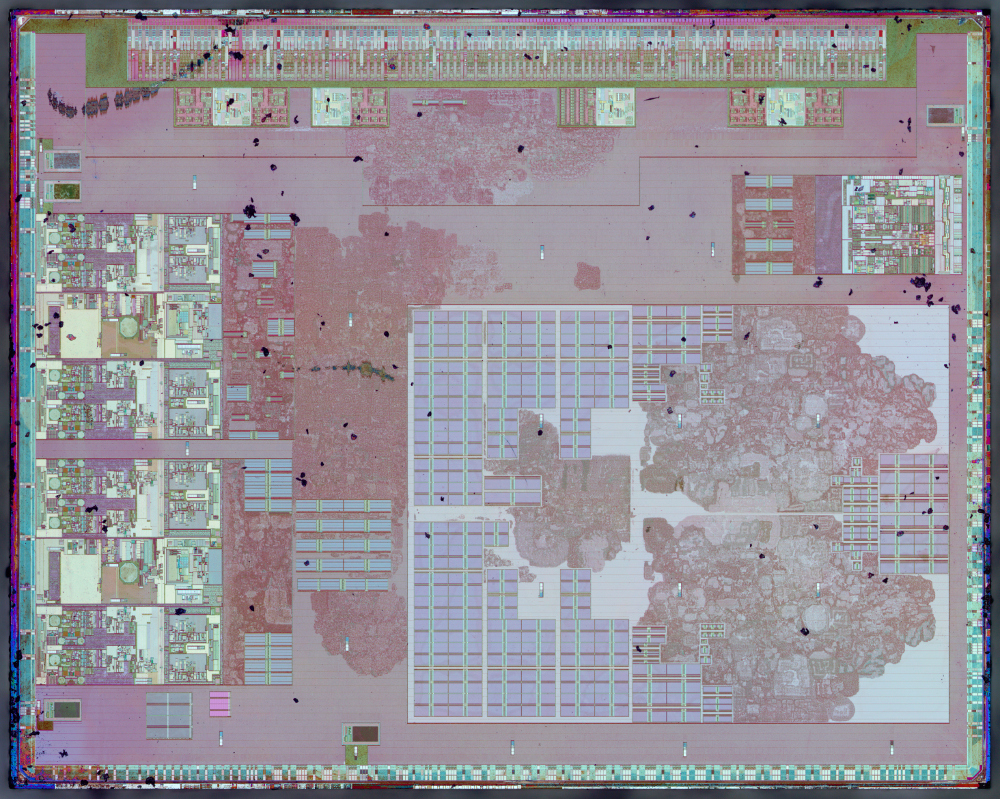

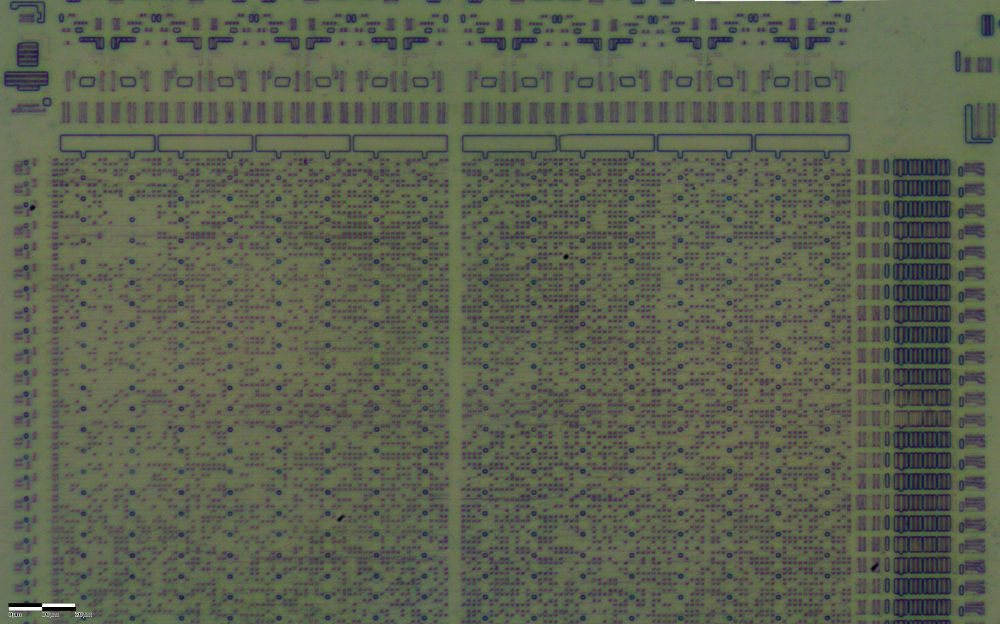

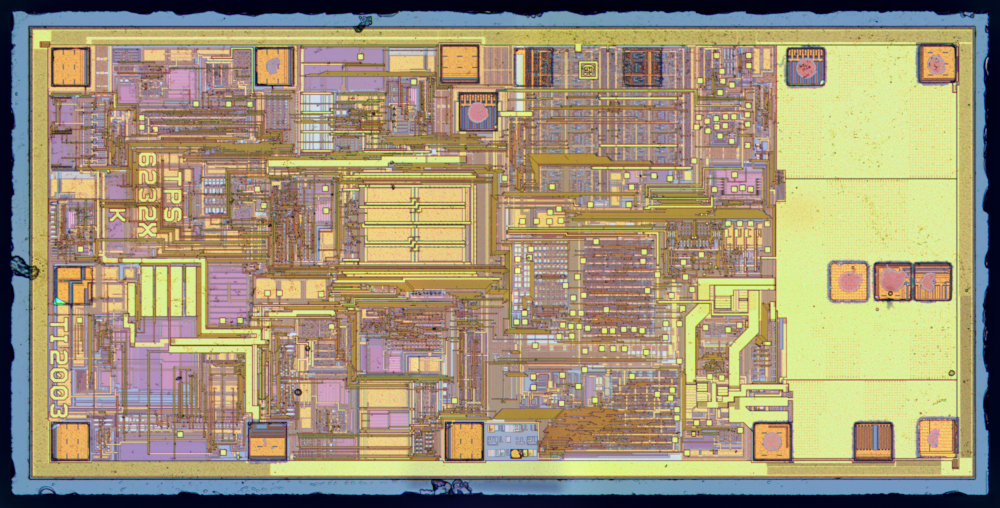

Figura 2. Una instantánea de la topología del amplificador operacional OPA134PA. Fuente - zeptobars.comAquí , por cierto, hay un ejemplo de ingeniería inversa del chip TL431 hecho por Ken Shirriff a partir de fotografías de BarsMonster. Y aquí está la traducción al ruso. El blog de Ken tiene muchas cosas interesantes si te interesa el tema de la ingeniería inversa amateur.Y aquí (¡con cuidado, tráfico!) Hay un informe de la ingeniería inversa del chip Zilog Z80-CTC, realizado en 1979, casi inmediatamente después del lanzamiento del chip. Ahora, este es un documento histórico único, y luego fue información de gran valor comercial y obtenida (a juzgar por varias referencias a estándares militares), probablemente en el proceso de certificación de un microcircuito para aplicaciones especiales.Pero vivimos en 2019, y no en 1979, y ahora invertir el esquema completo de un nuevo microprocesador Intel es cuestión de muchos meses o años, incluso con un buen nivel de automatización del proceso (sin mencionar el hecho de que incluso con una resolución aceptable podemos disparar la topología con estándares de diseño 14 -10-7 nm es una tarea muy difícil). ¿Qué es Intel? Compare la cantidad de trabajo en ingeniería inversa o análisis del amplificador de la imagen anterior y el procesador Baikal-T1, realizado de acuerdo con el muy popular y relativamente asequible proceso de fabricación de 28 nm. La ingeniería inversa completa de productos tan grandes es extremadamente rara, a menudo es interesante observar algunos bloques específicos y relativamente pequeños. Por ejemplo, para averiguar si violan su patente o para comparar su decisión con los productos de la competencia y tratar de entender por qué es mejor o peor. O, para descubrirlo, los propios desarrolladores de chips implementaron esta o aquella funcionalidad, o tomaron prestado su bloque de IP.

Figura 3. Una instantánea de la topología del procesador Baikal-T1. Fuente - zeptobars.com

Figura 3. Una instantánea de la topología del procesador Baikal-T1. Fuente - zeptobars.comAquí pasamos a la siguiente parte importante en la historia de la ingeniería inversa. En la antigüedad, todo el chip se desarrolló de principio a fin dentro de una empresa, a veces incluso por las fuerzas de un equipo muy pequeño o un solitario solitario como Bob Widlar. Los microcircuitos modernos están llenos de bloques de IP, cuya venta y compra es un gran mercado que, por supuesto, también tiene control de derechos de autor, espionaje industrial y piratería. Por lo tanto, es posible y necesario analizar el problema de la protección contra la copia no autorizada no solo desde el punto de vista del desarrollador del producto final, sino también desde el punto de vista del desarrollador de IP, para quien el desarrollador del producto también puede ser un pirata.

En el caso de la piratería, la estructura interna del intruso generalmente no es interesante para recibir datos, y se realiza una ingeniería inversa parcial (si es que existe) para encontrar vulnerabilidades y explotar estas vulnerabilidades, ya sea mediante conexión directa o mediante otros métodos. La tarea del desarrollador contra la piratería es evitar el uso de puntos potencialmente débiles y, si es necesario, destruir datos confidenciales cuando se intenta piratear.

PERSONAS ACTUALES

Para comenzar, descubramos quién puede proteger el diseño del chip de eso. Las siguientes entidades están involucradas en la cadena desde la idea hasta la aplicación, y tienen diferentes tipos de acceso a la información sobre el contenido del microcircuito.

- Desarrollador de bloque de IP. Tiene toda la información, todos los archivos necesarios, métodos de medición, etc. etc.

- Desarrollador de chips. En el caso de Soft IP, Verilog / VHDL tiene un código de bloqueo; en el caso de Hard IP, puede tener una topología o una caja negra. Si hay partes programables o de software en la unidad, también tiene acceso a ellas.

- La fábrica Tiene acceso a los archivos de topología GDSII, pero no tiene acceso a la parte del chip que depende del software (por ejemplo, al firmware PROM).

- Embalaje y pruebas de producción. Tiene acceso al chip, así como a métodos de prueba y tarjetas de firmware para memoria programable de una sola vez. Raramente alguien defiende a propósito de ellos, pero deberían estar en la lista, porque algunos de los métodos adecuados para la protección de la fábrica no funcionan en su contra.

- Competidor / cracker. Solo tiene acceso al producto terminado y a la documentación del usuario.

En el caso más simple, el diseñador de chips (2) quiere protegerse de la copia por parte de un competidor (5) o hacer un chip con memoria protegida de lectura no autorizada. En un poco más complicado, el desarrollador de IP (1) quiere asegurarse de que el desarrollador cumpla con el chip (2) del acuerdo de licencia. También sucede que el desarrollador del chip (2) no confía en la fábrica (3) y sospecha que puede conducir falsificaciones en el turno de noche.

Escribí en detalle sobre qué es IP en circuitos integrados hace algún tiempo, así que no repetiré este artículo. También hay un poco sobre cómo los desarrolladores de IP protegen su propiedad intelectual. En resumen, para proteger la topología, la fábrica generalmente participa como un tercero, y el comprador no recibe la topología propiamente dicha, y se utilizan técnicas de ofuscación similares a las de cualquier otro código para asegurar el código Verilog.Herramientas

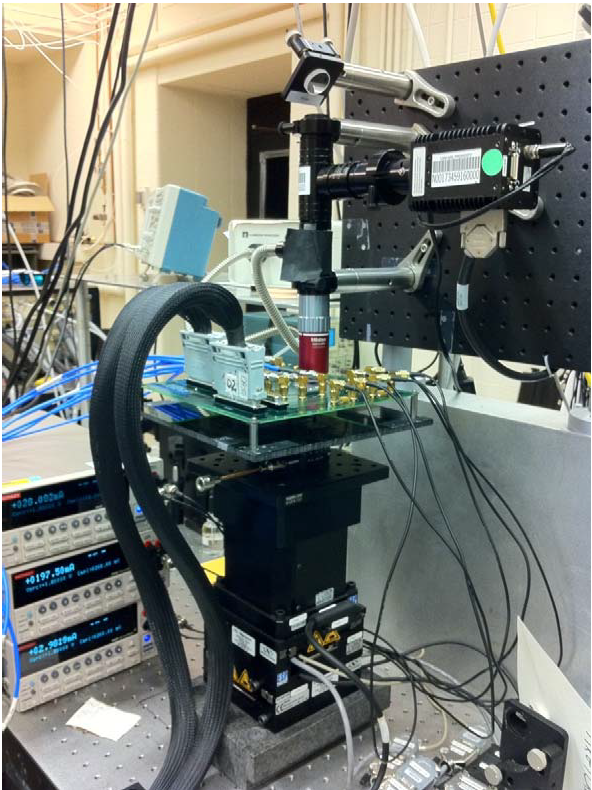

¿Qué herramientas de análisis de microchip existen? El primer nivel es un poco de ácido para abrir primero la carcasa del microcircuito, y luego eliminar las capas una por una, y un microscopio óptico regular con una cámara. Es económico, es fácil trabajar con ellos, y para el análisis de circuitos simples realizados con las últimas tecnologías, esto es suficiente.

Para esquemas más grandes, existen sistemas CAD especiales que permiten de una forma u otra automatizar la restauración de datos desde la topología, proporcionando al ingeniero inverso una interfaz más conveniente para el trabajo que simplemente dibujar líneas en un editor gráfico. La automatización también se simplifica por el hecho de que todos los circuitos digitales modernos se construyen a partir de bibliotecas, y después de la ingeniería inversa, los elementos de la biblioteca para ensamblar un circuito son cuestión de tiempo (o potencia de procesamiento disponible).

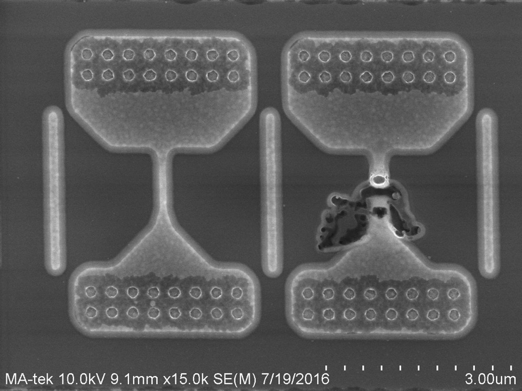

El siguiente nivel, inaccesible para los aficionados, pero presente en laboratorios especializados es un microscopio electrónico de barrido (SEM). Utiliza un haz de electrones enfocado en lugar de un haz de luz. La resolución SEM puede ir hasta 1 nm e incluso un poco más baja, lo que es suficiente para analizar cualquier circuito integrado moderno.

FIB es un análogo de SEM, solo que usa un haz de iones más pesados en lugar de un haz de electrones. En realidad, FIB es un haz de iones enfocado. La principal diferencia entre FIB y SEM es que con su ayuda no solo puede analizar el microcircuito, sino también modificarlo, por ejemplo, hacer cortes (para ver la sección transversal del microcircuito o eliminar una pieza) o rociar material (para crear una conexión allí donde no está) Los desarrolladores y fabricantes de microcircuitos utilizan ampliamente las FIB para trabajar con muestras de prueba, ya que lleva mucho tiempo corregir el error al usarlo, pero aún así es mucho más rápido y económico que reiniciar un lote experimental. Para un ingeniero inverso, esta también es una forma única de llegar a aquellas partes del cristal que, de acuerdo con la intención del desarrollador, no deberían estar disponibles. Y, al diseñar un chip protegido contra piratería, esto también debe tenerse en cuenta.

Figura 4. Sección transversal de un microcircuito hecho con FIB. Fuente - SERESSA-2015 (cuidadosamente, mucho tráfico en pdf desde el enlace).

Figura 4. Sección transversal de un microcircuito hecho con FIB. Fuente - SERESSA-2015 (cuidadosamente, mucho tráfico en pdf desde el enlace). Figura 5. Realizado por modificación FIB del chip, cambiando varias conexiones.

Figura 5. Realizado por modificación FIB del chip, cambiando varias conexiones.Otra herramienta indispensable para un ingeniero inverso es un conjunto de láseres. Los fanáticos pueden usar láseres potentes con los que pueden abrir microcircuitos en cajas de plástico y obtener acceso al cristal. Para los láseres profesionales, dependiendo de la longitud de onda, algunas partes del diseño del microcircuito pueden ser transparentes y otras no transparentes. Esto le permite utilizar un láser, por ejemplo, para abrir con precisión la pasivación y el aislamiento, de modo que luego pueda unir cómodamente la línea de metal sin correr el riesgo de cortocircuitarla con sus vecinos. Otros parámetros le permitirán cortar metal o quemar transistores individuales. El tercero es inducir corriente en los transistores cambiando las celdas de caché o algún tipo de líneas lógicas. La última opción se usa universalmente como una simulación económica de los efectos de partículas cargadas pesadas, pero en principio, el mal funcionamiento de un microcircuito en funcionamiento también puede ser útil para comprometer la información contenida en él. Por ejemplo, puede ser interesante reescribir alguna bandera en el archivo de registro o corregir ligeramente la operación del generador de números aleatorios.

Figura 6. Aspecto del láser para estudiar el efecto de fallas individuales en microcircuitos. Fuente - SERESSA-2015.

Figura 6. Aspecto del láser para estudiar el efecto de fallas individuales en microcircuitos. Fuente - SERESSA-2015. Figura 7. Un ejemplo de la sensibilidad de una parte de un microcircuito a una sola falla y falla obtenida usando una tarjeta láser. Fuente - SERESSA-2015.

Figura 7. Un ejemplo de la sensibilidad de una parte de un microcircuito a una sola falla y falla obtenida usando una tarjeta láser. Fuente - SERESSA-2015.En los laboratorios avanzados de ingeniería inversa, puede encontrar muchas otras herramientas interesantes; por ejemplo, una señal digital de hasta varias decenas de MHz se puede monitorear en tiempo real colocando un pequeño trozo de niobato de litio en la línea correspondiente e iluminándola nuevamente con un láser.

CASO 1: FÁBRICA NO CONFIABLE

¿Cuál podría ser la razón para no confiar en la fábrica donde haces tus cristales? En un mundo ideal, por supuesto, no te involucrarás con una fábrica en la que no confías, pero a veces las consideraciones comerciales te obligan a correr riesgos. Se puede minimizar de dos maneras principales:

- La llamada fabricación dividida o, de manera simple, producción en dos fábricas. Pero no en paralelo (como se suele hacer para minimizar el riesgo de escasez en caso de retrasos imprevistos en la producción), sino parte de las operaciones en una fábrica y parte en otra. Esto es bastante inconveniente para todos los participantes en el proceso (y ciertamente no todas las fábricas estarán de acuerdo con esto), pero esto obligará a la fábrica poco confiable a al menos revertir el resto del diseño del chip y crear las máscaras que faltan por sí mismas. (que, idealmente, debería hacer que el juego no valga la pena). La principal desventaja de este enfoque es que las capas superiores del chip son metalizadas, cuya ingeniería inversa es bastante simple. Sin embargo, la fabricación dividida puede ser realmente efectiva en combinación con algunos conocimientos tecnológicos en metales, que una fábrica poco confiable no puede reproducir. Por ejemplo, si la segunda fábrica de su elección sabe cómo hacer memoria no volátil (MRAM, memristors o algo así) en la capa superior de metalización, sin la cual todo el diseño pierde su significado.

- Si no tiene ningún conocimiento tecnológico, entonces la manera simple y confiable es hacer que el chip no tenga sentido sin más programación. Los bloques programables se pueden hacer de forma independiente utilizando la memoria de configuración, o en forma de un bloque basado en un FPGA incorporado (existen tales IP en el mercado). La memoria de configuración como una forma de protección le permite estar seguro de que la fábrica no puede simplemente tomar y producir su chip sin pasar por usted. Pero puedes leer la memoria de configuración, ¿verdad? Sí, pero la presencia de memoria de configuración obliga a una fábrica poco confiable, en lugar de una forma simple de aumentar los volúmenes de producción, a realizar la misma ingeniería inversa que todos los demás atacantes.

Por separado, observo que los dos métodos de protección descritos de una fábrica poco confiable ayudan contra la copia no autorizada, pero no se guardan de los "marcadores" populares en círculos estrechos. Además, un poco más adelante hablaré sobre cómo marcar la topología nosotros mismos.

CASO 2: PROTECCIÓN DE MEMORIA

La presencia de bloques programables y memoria de configuración en el chip es un atributo casi indispensable de cualquier diseño moderno, tanto digital como analógico. Con una disminución en los estándares de diseño, aumenta la difusión de los parámetros de un chip a otro, y el ajuste digital es la forma más fácil y confiable de superarlo. Y los circuitos digitales (por ejemplo, microcontroladores) generalmente almacenan datos directamente en el chip y pueden tener una estructura de memoria de varios niveles, cuyas diferentes partes tienen diferentes niveles de acceso y protección. Por lo tanto, parece lógico utilizar en primer lugar la herramienta que ya tenemos para aumentar la seguridad y la resistencia a las grietas, y en segundo lugar, la idea de pensar detenidamente sobre qué tipo de memoria utilizar.

Firmware con conexiones metálicas (ROM de máscara). Por lo general, parece la presencia o ausencia de contacto entre dos líneas de metal, un poco menos frecuente, como la presencia o ausencia de un transistor entre ellas. El más roble se usa en cristales de matriz base (BMC), no solo en la antigua industria de defensa, como se podría pensar, sino también en soluciones bastante modernas, por ejemplo, en chips auxiliares dentro de procesadores Xeon. Además, utilizando dicha memoria, se crean familias de microcircuitos (principalmente microcontroladores), porque flashear la memoria en la fábrica cambiando una máscara es más barato que el firmware universal de cada cristal producido en una placa o en un estuche. Máscara ROM se lee muy fácilmente con un microscopio y grabado preciso. En casa puedes manejarlo.

Figura 8. Firmware ROM con interconexiones metálicas en un chip FTDI FT232RL falso. Fuente - zeptobars.com

Figura 8. Firmware ROM con interconexiones metálicas en un chip FTDI FT232RL falso. Fuente - zeptobars.com

También debe señalarse aquí que es posible flashear la memoria no solo con una capa de contactos entre metales, sino también con la presencia y ausencia de metal (fácil de leer ópticamente), la presencia o ausencia de dopaje (fácil de leer ópticamente), o, por ejemplo, el voltaje umbral de un transistor controlado por el nivel de dopaje (mal leer ópticamente). Entonces, en principio, la ROM de máscara no tiene todo perdido si realmente quieres ocultar su contenido.

Memoria en puentes quemados (Fuse ROM). Permite una grabación (incluida la grabación del usuario en el dispositivo terminado) y un número ilimitado de lecturas, es muy simple de fabricar y programar, y por lo tanto popular para todo tipo de memoria de configuración y firmware.

Figura 9. Dos estados de Fuse ROM. Fuente - semiengineering.com

Figura 9. Dos estados de Fuse ROM. Fuente - semiengineering.comComo puede ver, el estado de un puente fusible común (Fusible) es muy fácil de ver a través de un microscopio, es decir, es simplemente imposible protegerse de abrir un cristal con él. Bueno, y además de todo lo demás, el puente quemado clásico es bastante grande (varias micras cuadradas) y, por lo tanto, no es adecuado para grandes cantidades de memoria.

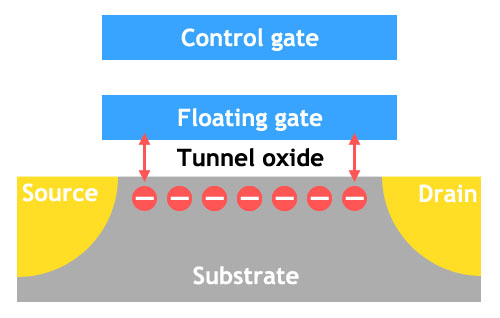

Memoria flash y otras opciones de EPROM y EEPROM basadas en transistores de puerta flotante.

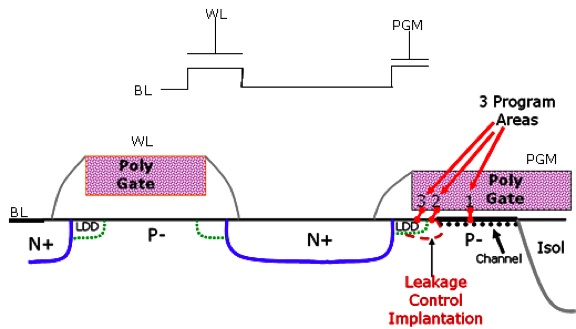

Figura 10. Esquema de grabación flash. Fuente - techreport.com

Figura 10. Esquema de grabación flash. Fuente - techreport.comEl principio de funcionamiento de este tipo de memoria es bastante simple: una puerta "flotante" se encuentra en una capa gruesa de un dieléctrico. Se puede colocar una carga eléctrica en este obturador haciendo un túnel, aplicando un alto voltaje. Y luego, si no aplica alto voltaje, la carga puede almacenarse en el obturador "flotante" durante mucho tiempo.

¿Qué hay de la seguridad?

La buena noticia es que el estado de la EEPROM no se puede ver con un microscopio. Mal? Hay varios de ellos a la vez.La primera mala noticia es que la EEPROM se borra no solo por el alto voltaje, sino también por la exposición a la radiación ultravioleta (los antiguos probablemente recuerden los chips con vidrio de cuarzo). Al mismo tiempo, si observa cuidadosamente la topología con un microscopio, es posible que pueda cubrir toda la memoria con un material opaco, a excepción de esos pocos bits que incluyen protección contra lectura y, después de la exposición, su chip. Moraleja: Usando EEPROM en su proyecto, cúbralo con metal en la parte superior. Y es deseable no solo con un escudo sólido contra la radiación, sino también con algunas líneas significativas, para que el escudo no se pueda grabar con precisión. Sin embargo, una emboscada también está oculta aquí (es la segunda mala noticia), porque en principio un microcircuito o sus partes individuales se pueden resaltar desde abajo. Esto no es fácil, porque lo más probable es que requiera retirar el chip de la carcasa y,por ejemplo, grabar el fondo del sustrato, pero es posible. Dichas técnicas son populares para probar microcircuitos de un solo chip, ya que la metalización es opaca tanto para los rayos UV como para el láser, y el sustrato de silicio es casi transparente, la pregunta es cómo enfocar el haz de radiación correctamente si se necesita exposición local.Como opción alternativa, puede configurar los bits de activación / desactivación de la protección para que su borrado active la protección y no la desactive.La tercera mala noticia es que hay sensores que pueden leer la carga eléctrica en una puerta flotante o sus restos después de una operación de borrado. Además, para leer eléctricamente la memoria, en general, no es necesario alimentar el chip, es decir, no hay riesgo de activar los mecanismos de destrucción de información incorporados.Mram, aunque relativamente raro, sin embargo, también merece nuestra atención. Es, como flash, no puede considerarse ópticamente. MRAM, por supuesto, no se puede borrar con luz ultravioleta, pero existen sensores de campo magnético con una resolución lo suficientemente alta como para enfrentar los metales superiores y leer la memoria poco a poco. Buenas noticias? Es poco probable que un atacante potencial los encuentre rápida y económicamente. En general, MRAM es una buena alternativa al flash desde el punto de vista de la seguridad, pero hasta el momento no está ampliamente disponible y acaba de entrar en producción en masa en tecnologías disponibles para empresas sin fábrica.Hoy, la ROM antifusible se considera la memoria más protegida de la ingeniería inversa.. Como su nombre lo indica, representa una cierta antípoda de puentes quemados, es decir, tiene una alta resistencia en un estado no programado y baja en un programado. ¿Cómo se logra esto? Con la ruptura de la puerta de la puerta dieléctrico de un transistor con un alto voltaje. La región de descomposición es tan pequeña que no es visible desde arriba en el microscopio o en la sección de la FIB, pero también proporciona un cambio bueno y confiable en la resistencia en varios órdenes de magnitud, que es suficiente para una lectura confiable del estado de la memoria de manera regular. Sin embargo, dicha celda de memoria puede leerse conectándose directamente a la puerta y fuente del transistor de memoria. Una celda ininterrumpida se comporta como un condensador, una celda unida se comporta como una resistencia. Figura 11. Sección celular de una memoria antifusible. Se muestran varias áreas de posible descomposición del transistor. Esto puede complicar el esquema de lectura.Por supuesto, hay otras formas de averiguar el contenido de la memoria, además de la inspección visual de las células. La forma más fácil es usar FIB para conectarse directamente a las líneas de lectura correspondientes y enviarles cualquier señal de control que deba enviarse para leer información inaccesible de manera normal. Anteriormente, puede desactivar la protección contra lectura cortando físicamente las líneas que conducen a los bits de memoria correspondientes. ¿Cómo protegerse de esto? Después de haber diseñado correctamente la topología de su chip y, posiblemente, haber integrado algunas funciones adicionales en él. Aquí hay un ejemplo de cómo Cypress hace esto:It is possible to configure the nvSRAM to provide password protected access. In this configuration, instead of performing the normal power up recall sequence on power up, the part waits for the user to enter a 5-byte password followed by an End Password Entry soft sequence. The End Password Entry soft sequence is a specific seven-address read sequence. If you enter the correct password, the part completes the boot up sequence and is ready for the normal nvSRAM operations. If you enter the incorrect password three times or you do not enter the right password within a specified period of time, the part locks up or fills the SRAM memory with random data, as the application requirement may be. The part can be configured to additionally destroy the functionality and cause physical damage to the chip.Por lo general, esto se hace: la memoria está cubierta desde arriba por una cuadrícula de tierra y líneas eléctricas, y todas las líneas de señal se encuentran estrictamente debajo de ellas. En este caso, se debe tener cuidado para garantizar que las líneas de alimentación, por un lado, no se dupliquen entre sí (es decir, al cortar cualquiera de ellas, parte del microcircuito deja de funcionar) y, por otro lado, para que cada una de ellas sirva a muchos bits de memoria , y la inserción de un amperímetro en la línea de alimentación no podría permitirnos estimar el estado de la memoria por consumo en modo de lectura (que difiere para diferentes estados lógicos en la mayoría de los tipos de memoria). Con tal organización de las capas superiores del chip, será extremadamente difícil para un atacante abrir parte de la metalización para conectarse a donde necesita.Incluso en la red de tierras y fuentes de alimentación, se disponen líneas de protección adicionales para que una ruptura en ellas (o su cortocircuito a la alimentación o a la tierra) cuando se suministre energía al chip inicie la eliminación completa del contenido de la memoria protegida (o, como vimos anteriormente, daño físico chip). Dichas líneas de protección, ubicadas al lado del suelo y las líneas eléctricas, complican enormemente el trabajo de los atacantes, porque las operaciones con la FIB requieren un lugar tangible según los estándares de los procesos tecnológicos actuales. Además, debido a la forma en forma de cono del recorte creado por el microscopio, cuanto más baja sea la capa a la que desea conectarse, más área necesita limpiar sobre ella.Pero, de hecho, muy a menudo, un atacante puede no necesitar el valor exacto del contenido de la memoria, puede ser suficiente para reducir el número de opciones para ordenar en varios órdenes de magnitud. Por ejemplo, si una celda de memoria consume mientras lee una unidad lógica X, y mientras lee un cero lógico 100 * X, al leer un byte de dicha memoria, obtendremos un consumo diferente dependiendo del contenido de la memoria:0 - 800 * X1,2,4, ..., 64, 128 - 701 * X3, 6, 7, ..., 160, 192 - 602 * X....255 - 8 * XEn total, si no tocamos la memoria, necesitamos 256 intentos para seleccionar la contraseña que contiene. Y si sabemos que el consumo en modo de lectura es 701 * X, entonces solo hay ocho. Conveniente, ¿no es así? La forma más fácil de hacer algo con este problema es almacenar los datos en forma de un valor y su inversión en una celda vecina; entonces el consumo de cualquier cantidad de memoria en modo de lectura no dependerá de la información almacenada. Es cierto, requiere el doble de memoria, pero la seguridad es importante para nosotros, ¿verdad?

Figura 11. Sección celular de una memoria antifusible. Se muestran varias áreas de posible descomposición del transistor. Esto puede complicar el esquema de lectura.Por supuesto, hay otras formas de averiguar el contenido de la memoria, además de la inspección visual de las células. La forma más fácil es usar FIB para conectarse directamente a las líneas de lectura correspondientes y enviarles cualquier señal de control que deba enviarse para leer información inaccesible de manera normal. Anteriormente, puede desactivar la protección contra lectura cortando físicamente las líneas que conducen a los bits de memoria correspondientes. ¿Cómo protegerse de esto? Después de haber diseñado correctamente la topología de su chip y, posiblemente, haber integrado algunas funciones adicionales en él. Aquí hay un ejemplo de cómo Cypress hace esto:It is possible to configure the nvSRAM to provide password protected access. In this configuration, instead of performing the normal power up recall sequence on power up, the part waits for the user to enter a 5-byte password followed by an End Password Entry soft sequence. The End Password Entry soft sequence is a specific seven-address read sequence. If you enter the correct password, the part completes the boot up sequence and is ready for the normal nvSRAM operations. If you enter the incorrect password three times or you do not enter the right password within a specified period of time, the part locks up or fills the SRAM memory with random data, as the application requirement may be. The part can be configured to additionally destroy the functionality and cause physical damage to the chip.Por lo general, esto se hace: la memoria está cubierta desde arriba por una cuadrícula de tierra y líneas eléctricas, y todas las líneas de señal se encuentran estrictamente debajo de ellas. En este caso, se debe tener cuidado para garantizar que las líneas de alimentación, por un lado, no se dupliquen entre sí (es decir, al cortar cualquiera de ellas, parte del microcircuito deja de funcionar) y, por otro lado, para que cada una de ellas sirva a muchos bits de memoria , y la inserción de un amperímetro en la línea de alimentación no podría permitirnos estimar el estado de la memoria por consumo en modo de lectura (que difiere para diferentes estados lógicos en la mayoría de los tipos de memoria). Con tal organización de las capas superiores del chip, será extremadamente difícil para un atacante abrir parte de la metalización para conectarse a donde necesita.Incluso en la red de tierras y fuentes de alimentación, se disponen líneas de protección adicionales para que una ruptura en ellas (o su cortocircuito a la alimentación o a la tierra) cuando se suministre energía al chip inicie la eliminación completa del contenido de la memoria protegida (o, como vimos anteriormente, daño físico chip). Dichas líneas de protección, ubicadas al lado del suelo y las líneas eléctricas, complican enormemente el trabajo de los atacantes, porque las operaciones con la FIB requieren un lugar tangible según los estándares de los procesos tecnológicos actuales. Además, debido a la forma en forma de cono del recorte creado por el microscopio, cuanto más baja sea la capa a la que desea conectarse, más área necesita limpiar sobre ella.Pero, de hecho, muy a menudo, un atacante puede no necesitar el valor exacto del contenido de la memoria, puede ser suficiente para reducir el número de opciones para ordenar en varios órdenes de magnitud. Por ejemplo, si una celda de memoria consume mientras lee una unidad lógica X, y mientras lee un cero lógico 100 * X, al leer un byte de dicha memoria, obtendremos un consumo diferente dependiendo del contenido de la memoria:0 - 800 * X1,2,4, ..., 64, 128 - 701 * X3, 6, 7, ..., 160, 192 - 602 * X....255 - 8 * XEn total, si no tocamos la memoria, necesitamos 256 intentos para seleccionar la contraseña que contiene. Y si sabemos que el consumo en modo de lectura es 701 * X, entonces solo hay ocho. Conveniente, ¿no es así? La forma más fácil de hacer algo con este problema es almacenar los datos en forma de un valor y su inversión en una celda vecina; entonces el consumo de cualquier cantidad de memoria en modo de lectura no dependerá de la información almacenada. Es cierto, requiere el doble de memoria, pero la seguridad es importante para nosotros, ¿verdad?CASO 3: SIN MEMORIA

Pero, ¿qué pasa si su chip no contiene memoria de configuración o contiene solo unos pocos bits, que no tienen sentido ocultar? Por qué Por lo tanto, es mucho más barato (no tanto al reducir el costo de las máscaras para la litografía, sino por un proceso más simple de empaquetado y prueba), y para la mayoría de los chips simples, el precio es una gran ventaja competitiva.

Hablando de pruebas. El proceso de rechazo de cristales en obleas y memoria de configuración intermitente a menudo se subcontrata, especialmente por pequeñas empresas, porque el equipo apropiado generalmente no es asequible para las nuevas empresas, y se debe garantizar la calidad. Por lo tanto, si la producción de terceros está actualizada con sus métodos de prueba y tiene firmware de memoria de configuración, entonces sería mejor para usted confiar completamente en estas personas. O tenga métodos adicionales de protección contra ingeniería inversa que no estén vinculados a la memoria de configuración.

Entonces, ¿qué hacer si la memoria de configuración no es una opción de protección o si no es suficiente?

El principal inconveniente de un microscopio óptico y SEM es que es muy difícil distinguir entre los tipos de dopaje de silicio. Es decir, la presencia de aleación es visible, pero el tipo no lo es. Por lo tanto, al analizar la topología y la extracción del circuito, el tipo de dopaje se restaura desde el contexto y la lógica implícita del circuito (los transistores de canal n están conectados a tierra, los transistores de canal p están conectados a la alimentación, etc., etc.). Después de haber dibujado la topología de su microcircuito para que no coincida con la opción más intuitiva, probablemente puede estropear la sangre de un ingeniero reverso. Especialmente si usa varios esquemas diferentes disfrazados de lo mismo. Con cierta destreza, no solo puede complicar el análisis de su circuito, sino que también puede hacer que el dispositivo (o al menos modelado, pero más divertido si se produce) utilizando la topología restaurada haga algo específico, desde acortar el suelo con potencia hasta emitir palabras obscenas a todas las salidas. El comportamiento determinista de un diseño robado incorrectamente, por cierto, puede ser útil no solo para quemar un osciloscopio a los piratas, sino también para garantizar que cuando más tarde recibas usuarios decepcionados de tus chips, puedas demostrarles claramente que compraron falso

Figura 12. Sección de tres estructuras indistinguibles por un microscopio. El izquierdo es pMOSFET, el del medio es un cortocircuito, el derecho es un diodo polarizado (gap).

Figura 12. Sección de tres estructuras indistinguibles por un microscopio. El izquierdo es pMOSFET, el del medio es un cortocircuito, el derecho es un diodo polarizado (gap). Figura 13. Topología de tres celdas de biblioteca digital que no se pueden distinguir con un microscopio. El izquierdo es el inversor, el medio es la conexión directa de la entrada y la salida, el derecho es la unidad lógica de salida.

Figura 13. Topología de tres celdas de biblioteca digital que no se pueden distinguir con un microscopio. El izquierdo es el inversor, el medio es la conexión directa de la entrada y la salida, el derecho es la unidad lógica de salida.Cada una de las celdas de la figura anterior se parece casi al inversor más común, pero en realidad puede ser un inversor, repetidor o generador de un cero lógico o una unidad lógica. Solo nuestros contactos para difusión desde la entrada y la salida emiten nuestro "inversor". Sin embargo, al abandonarlos, obtendremos un circuito completamente indistinguible a cambio de la imposibilidad de implementar la conexión de entrada y salida (pero podemos usar dos inversores para este propósito). Sin embargo, con la capacidad de invertir o no invertir una señal usando la misma celda, la lucha contra un atacante es mucho más interesante, porque nada complica los intentos de lidiar con problemas de un diseño desconocido como un inversor adicional en algún lugar del reloj o circuito de encendido / apagado.

Aunque no, sucede. Una topología manual bien construida suele leerse bien. Un gran

ejemplo es el ya mencionado blog de Ken Schirriff.

Figura 14. Unidad lógica aritmética (ALU) del chip Intel 8008. Se muestran dígitos separados.

Figura 14. Unidad lógica aritmética (ALU) del chip Intel 8008. Se muestran dígitos separados.En la topología de ALU Intel 8008, ocho circuitos idénticos son perfectamente visibles, por la cantidad de bits. Al comprender que esto es ALU, puede restaurar fácilmente el esquema de topología. Si algunos de los elementos que contiene son falsos, esto complicará un poco su trabajo, pero no más. Y todo porque la topología encaja bien en la idea básica de las interfaces entre las partes constituyentes. Para confundir tanto a un atacante que abandone los intentos de ingeniería inversa, es necesario hacer que la topología sea impredecible y no se repita. La forma más fácil no es hacer bloques manualmente, sino generar la lista de redes completa del chip usando CAD. Los trazadores automáticos, a pesar del enorme ahorro de tiempo en la creación de una topología (en comparación con el trabajo manual), hacen un excelente trabajo al crear una disposición no intuitiva de elementos y en lugares completamente locos. Y cuanto más grande es el diseño, cuya topología se sintetizó en su conjunto, más difícil es realizar ingeniería inversa.

Pero esta es la forma más fácil. Hay más opciones interesantes. Por ejemplo, use un conjunto de celdas de camaleón como un conjunto de generadores de ceros lógicos y unos para las entradas del multiplexor, mientras realiza una función lógica arbitraria. En realidad, así es como se organizan los elementos de FPGA, LUT (tabla de consulta).

Figura 15. Implementación de una LUT de tres entradas. Fuente

Figura 15. Implementación de una LUT de tres entradas. FuenteAl colocar varias LUT en diferentes lugares del circuito y llevar algunas señales a las entradas de las "celdas de memoria", resolveremos varios problemas a la vez:

- Si nuestra maniobra permanece sin resolver, podremos establecer cómo se comportará exactamente el circuito de ingeniería inversa. Opciones: cualquiera, limitada solo por su imaginación.

- El uso de señales arbitrarias de otros bloques como "entrada" para las celdas que generan cero lógico y uno complicará el proceso de separación visual del diseño en bloques.

- Incluso si el ingeniero inverso se da cuenta de que estamos usando tales LUT protegidas, tendrá que clasificar muchas opciones para restaurar la funcionalidad del circuito de acuerdo con la topología, de modo que incluso un número relativamente pequeño de celdas protegidas puede hacer que la ingeniería inversa requiera innecesariamente mucho tiempo. Mi favorito es ensamblar una máquina de estado en tales LUT que controle las transiciones del microcircuito de un modo operativo a otro.

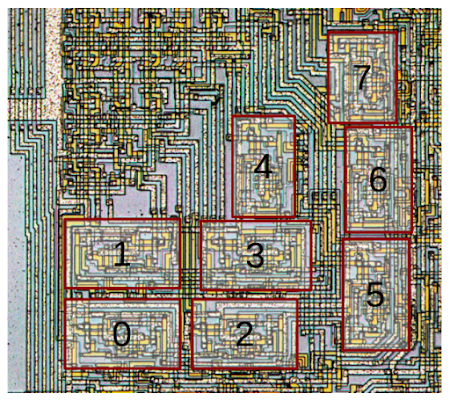

DIAGRAMAS DE PRUEBA

Los buenos ingenieros son muy aficionados a probar exhaustivamente sus chips. Y por "exhaustivamente" quiero decir, aproximadamente de la misma manera que en el convertidor TI DC / DC en la figura a continuación. Decenas de pequeñas almohadillas de contacto, a las que puede conectarse antes de cortar la placa en cristales individuales, para verificar todos los parámetros necesarios, el estado de las líneas internas importantes, decidir si el chip es adecuado o no y, si es necesario, averiguar la causa de los problemas.

Figura 16. Topología TPS 62321 de Texas Instruments. Fuente - zeptobars.com

Figura 16. Topología TPS 62321 de Texas Instruments. Fuente - zeptobars.comUna buena cobertura con almohadillas de prueba para lanzamientos de prueba y prototipos es especialmente importante, pero para la producción en serie a menudo se desactivan (mediante la corrección de una o dos máscaras o puentes quemables) para minimizar el efecto sobre el comportamiento del producto. Entonces, ¿de qué estoy hablando? Las almohadillas de contacto de prueba son de gran ayuda para un atacante, ya que no solo señala puntos importantes en el diseño usted mismo, sino que también le brinda un acceso conveniente. El puente quemado se restaura fácilmente en FIB, ¡y listo! Idealmente, la seguridad requiere la eliminación completa de las almohadillas de prueba del chip en serie. Si esta opción es irracional (por ejemplo, también necesita pruebas en la placa en la producción en serie), entonces al menos asegúrese de que el mecanismo para desconectar los sitios de prueba no sea recuperable, por ejemplo, esté ubicado directamente debajo de la plataforma y se dibuje de manera que la brecha No se pudo conectar convenientemente.

Ni siquiera quiero comenzar por el hecho de que todos los diseños digitales modernos tienen un JTAG incorporado para pruebas, que le permite ver directamente el estado de cualquier disparador en un chip. La idoneidad de la prueba es una de las características clave de cualquier diseño, y es este hecho el que hace que sea extremadamente importante desactivar de forma segura y permanente todas las interfaces de prueba antes de que el chip salga de las paredes del fabricante.

Aún así, a los buenos ingenieros les gusta colocar circuitos de prueba en la periferia del chip para las próximas revisiones. Por lo general, estos son esquemas bastante importantes, de lo contrario, ¿por qué perder tiempo y esfuerzo organizando sus pruebas? "¿Los circuitos importantes que componen su propiedad intelectual y son críticos para el funcionamiento del chip?" ¿Cuidadosamente separado de todo el diseño? ¡Muchas gracias! - El ingeniero inverso le dirá por un regalo tan real. Si no desea que los de prueba ayuden a un atacante a estudiar y copiar su diseño, asegúrese de que no entren en cristales para la producción en masa o que se destruyan después de probar en placas durante el proceso de cortar la placa en cristales.

UNA PEQUEÑA PRÁCTICA

Para demostrar una vez más cómo funciona esto, el

ejemplo de abrir el microcontrolador PIC12C508A descrito en la disertación de Sergei Skorobogatov, defendido en 2004 en Cambridge. La traducción es corta y bastante gratuita:

Es necesario abrir el estuche y encontrar en el chip una memoria protectora borrada por la radiación ultravioleta. Esto se hace con bastante facilidad al ver las líneas que van al pin de programación del chip. Luego, cubre la memoria principal con un material opaco para los rayos UV, y después de cinco a diez minutos de exposición, puede considerar la memoria como un programador regular. Otra opción: después de encontrar la memoria de protección de copia, simplemente corte la ruta de metal que lo conduce, que en este chip se encuentra lejos de otras líneas, por lo que puede cortarla no solo con FIB, sino solo con una aguja. Figura 17. Y aquí está la línea muy desafortunada. De hecho, se encuentra en el medio de un espacio vacío, no está protegido de ninguna manera, se puede cortar.

Figura 17. Y aquí está la línea muy desafortunada. De hecho, se encuentra en el medio de un espacio vacío, no está protegido de ninguna manera, se puede cortar.CONCLUSION

Por supuesto, es imposible comprender la inmensidad, porque la tecnología y la ingeniería inversa de los microcircuitos, y la protección contra ellos, no se detienen y se mejoran constantemente. El tema de la seguridad de la información es una de las claves en el diseño para Internet de las cosas, por lo que los desarrolladores le prestan mucha atención, y los ingenieros inversos no pueden esperar una extracción tan fácil como hace quince o veinte años. Sin embargo, uno siempre debe recordar que un sistema mal protegido significa pérdidas potenciales, pérdidas enormes o incluso la vida de las personas, y la protección contra el acceso no autorizado y la ingeniería inversa debe ser parte del sistema en todos los niveles de operación, sin excluir el hardware .