Aunque han pasado 14 años desde que se introdujo el

primer SSD SATA , muchos consumidores todavía se refieren a unidades de estado sólido con bastante escepticismo. La razón principal de la desconfianza es el recurso de trabajo limitado de la memoria flash, debido a la degradación gradual de la estructura de semiconductores de los chips, como resultado de lo cual los dispositivos pierden tarde o temprano su capacidad de registrar y almacenar información. Las especificaciones técnicas detalladas a menudo solo agravan la situación: ¿es difícil para un comprador comprender si el TBW 500 TB mencionado en la descripción del SSD NAND SATA 3D Digital Blue Western para dos terabytes es mucho o poco? ¿Cuánto durará una unidad de este tipo en condiciones operativas reales y se puede confiar en los archivos más valiosos? Intentemos comprender este problema juntos y hablemos sobre la fiabilidad de la memoria flash moderna.

Hablando estrictamente, la respuesta a la "pregunta principal de la vida, el universo y todo eso" se recibió en diciembre de 2014, cuando los chicos de la publicación de la red

TechReport completaron las pruebas de SSD de los consumidores, que duró un total de un año. Utilizando los productos HyperX, Corsair, Kingston y Samsung como ejemplos, han demostrado de manera convincente que la vida real de los SSD supera 1 petabyte de doblaje. Dichos volúmenes son casi impensables no solo para el usuario promedio, sino incluso para los creadores de contenido profesionales: la unidad se volverá moralmente obsoleta mucho antes de que se agoten sus recursos.

Sin embargo, hay un matiz significativo: hace cuatro años, los chips MLC NAND estaban en uso, capaces de almacenar 2 bits de información en cada celda y fabricados utilizando una tecnología de proceso de 25 nanómetros. En ese momento, era un buen compromiso entre el SLC altamente confiable (celda de un solo nivel) y el TLC más costoso y económico (celda de tres niveles): los chips con celdas de dos bits proporcionaron una densidad de almacenamiento de datos aceptable, soportando hasta 5,000 ciclos de escritura / borrado (en en promedio, esta cifra alcanza los 3 mil). Lo que no se puede decir sobre sus hermanos más cercanos: a pesar de todas las ventajas, que incluyen alta capacidad y bajo costo, los TLC fueron mucho menos resistentes, apenas habían superado los 1,500 mil ciclos de programación / borrado, a pesar de que la mayoría de los microcircuitos planos apenas pueden soportar mil.

El principal culpable de esta situación fue la transición a un proceso de 15 nanómetros utilizado en la producción de chips. Para entender por qué sucedió esto, solo recuerde cómo funciona la memoria NAND. La codificación de bits de información ocurre al cambiar la carga en una puerta flotante debido al túnel cuántico de electrones a través de la capa dieléctrica, debido a la alta intensidad del campo eléctrico.

Circuito de transistor de puerta flotanteDesde el punto de vista de la física, no estamos lidiando con nada más que el fenómeno de un colapso reversible similar a una avalancha. Acelerando en un campo eléctrico, los electrones reciben suficiente energía cinética para la ionización por impacto de las moléculas dieléctricas, lo que resulta en un par de partículas elementales que llevan la carga opuesta, que también son aceleradas por un campo eléctrico, y el proceso se repite, mientras que el número de portadores de carga aumenta exponencialmente (de ahí el nombre ) Es fácil adivinar que tales procesos causan un desgaste gradual de las capas dieléctricas, como resultado, aumenta la probabilidad de fuga de carga a las celdas vecinas, lo que, a su vez, provoca daños o incluso la pérdida completa de datos. Y la transición a una nueva tecnología de proceso solo exacerba la situación: una disminución en el grosor del dieléctrico conduce al hecho de que las células fallan mucho antes.

Sin embargo, si el problema fuera solo esto, los consumidores comunes y los usuarios corporativos simplemente no notarían la diferencia entre MLC y TLC, y en las especificaciones técnicas para SSD veríamos cifras mucho más impresionantes. En realidad, una imagen completamente diferente aparece ante nuestros ojos, y la arquitectura de los chips flash y los detalles de su trabajo son la razón de esto: las celdas individuales se combinan en páginas y las páginas en bloques, mientras que la información de grabación solo es posible en páginas en blanco, y su eliminación se lleva a cabo bloque por bloque.

¿Qué significa esto en la práctica? Supongamos que tenemos un bloque parcialmente lleno y queremos escribir nuevos datos en él. Si su volumen es menor que el espacio libre restante, la grabación se produce instantáneamente, sin ninguna manipulación adicional. Si no hay suficiente espacio, entran en juego algoritmos complejos de múltiples etapas. Considere la situación en el diagrama a continuación.

Así es como se escriben los datos en la memoria flashLos nuevos datos que queremos registrar ocupan dos páginas en un bloque, pero solo una es realmente gratuita: aunque la página anterior (resaltada en amarillo) fue eliminada por el usuario anteriormente, de hecho, la información registrada no desapareció. Para liberar espacio para nuevos datos, el controlador inicia un procedimiento conocido como recolección de basura, eliminando datos innecesarios y redistribuyendo los existentes. Para hacer esto, todas las páginas, excepto las innecesarias, se copian en el segundo bloque libre, mientras que el primero se borra por completo. Luego, las páginas reales se transfieren de nuevo al primer bloque, se eliminan del segundo, y solo después de eso, los nuevos datos ocupan el lugar que les corresponde.

En el ejemplo anterior, para grabar dos páginas, tuvimos que reescribir completamente 2 bloques dos veces, seis páginas cada uno. De hecho, el proceso de "Recolección de basura" se verá mucho más complicado y, como resultado, el número de ciclos de reescritura será mucho mayor. La imagen real solo se puede estimar conociendo el coeficiente de amplificación de escritura, que muestra cuántas veces la carga real en la memoria flash excede la calculada. Este indicador puede ser igual a la unidad solo cuando se graba información en un disco absolutamente limpio y formateado, en todos los demás casos su valor variará de 2 a 25. Además, incluso a primera vista, las unidades idénticas pueden diferir significativamente, por lo que dependiendo del modelo del controlador utilizado y las características del firmware. Por lo tanto, la tolerancia a fallos de SSD está determinada no solo por el tipo de memoria flash, sino también por cuánto los desarrolladores pudieron optimizar el rendimiento de la capa FTL (capa de traducción flash).

¿Por qué el aumento dramático en la densidad de almacenamiento no afectó la confiabilidad de la memoria 3D NAND?

Entonces, ahora sabemos cómo funciona la memoria flash y qué factores determinan la confiabilidad de una unidad SSD. Es hora de descubrir qué ventajas ofrece la transición de chips "planos" a los tridimensionales. En primer lugar, 3D NAND difiere de sus predecesores debido al uso de la "trampa de carga" (Flash de trampa de carga) en lugar de las persianas flotantes familiares. Si en este último, el polisilicio con dopantes se usa para almacenar cargas, entonces en CTF es una región aislada de material no conductor, más a menudo SiN - nitruro de silicio. Tal enfoque hizo posible minimizar la probabilidad de fuga de carga y, como resultado, aumentar la estabilidad de la celda.

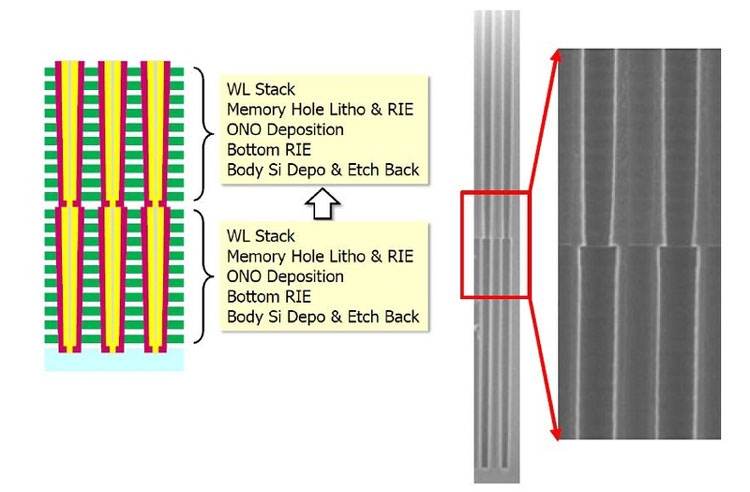

La arquitectura de los chips de memoria tridimensionales también ha sufrido cambios significativos en comparación con su predecesor, ya que ahora cada celda tiene una estructura cilíndrica: la capa externa es una puerta de control y la interna es un aislante. Como las celdas ahora están ubicadas una encima de la otra, forman una pila, dentro de la cual pasa un canal hecho de silicio policristalino. Es fácil entender que la cantidad de capas en un chip determina la cantidad de celdas en la pila.

Dispositivo de celda de chip 3D NANDEsta estructura hizo posible reducir la interferencia entre las células y, por lo tanto, simplificar el algoritmo de grabación: dado que no había necesidad de verificar el estado de carga, la grabación en la célula comenzó en un solo paso. Otro matiz importante: para la producción de 3D NAND, se utilizan procesos de ejecución, a pesar de que la densidad de empaquetamiento de las células pudo aumentar significativamente. Así, por ejemplo, incluso se produjeron chips de 48 capas (la tercera generación de memoria flash tridimensional) utilizando una tecnología de proceso de 40 nanómetros. Esto hizo posible no solo aumentar su confiabilidad, sino también reducir el costo de producción, ya que las líneas de producción existentes solo necesitaban una modernización mínima, y la necesidad de litografía en ultravioleta profundo desapareció por completo.

Hablando específicamente sobre los productos de Western Digital, luego en los modernos

SSD WD Black SN750 NVMe ,

cuyo inicio de ventas comenzó el 18 de enero de 2019, se utiliza el TLC 3D NAND BiCS (costo de bits escalable) de 64 capas, hecho con la tecnología de proceso de 28 nanómetros. Además de aumentar la densidad de empaque en otras 1,4 veces (el modelo superior ahora tiene una capacidad de 2 TB, que es el doble del tamaño del buque insignia de la generación anterior), una característica importante de este tipo de chip es el uso de cadenas en forma de U.

Arquitectura 3D NAND BiCSDado que ahora el transistor de conmutación y la línea de origen se encuentran en la parte superior del chip, prácticamente no están expuestos a influencias de alta temperatura, que pueden provocar errores durante las operaciones de lectura / escritura, lo que mejora aún más la confiabilidad de las unidades de estado sólido.

¿Cómo afectan los algoritmos de grabación la vida de un SSD?

Ya escribimos anteriormente que no importa cuán resistente y segura sea la memoria flash, sus recursos se desperdiciarán si los desarrolladores de SSD no se molestan en crear algoritmos de grabación efectivos. Para optimizar este procedimiento, se utilizan dos técnicas muy efectivas: almacenamiento en caché SLC y nivelación de desgaste.

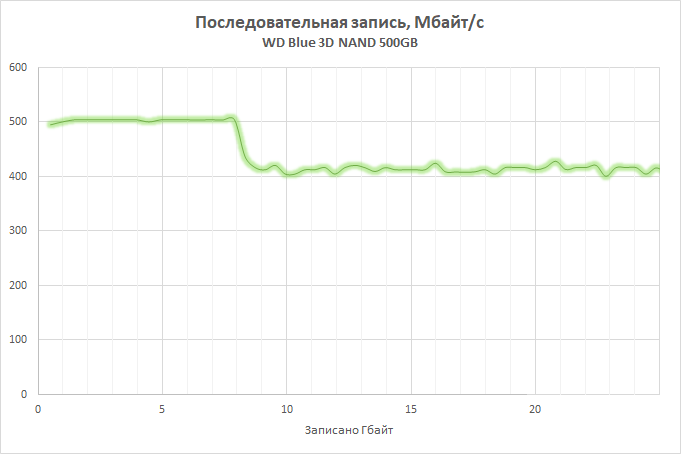

La esencia de la primera es que parte de la matriz de memoria disponible, cuyo tamaño depende del volumen total de la unidad (por ejemplo, al desarrollar el

SSD WD Blue 3D NAND, procedimos del cálculo de 4 GB de caché por cada 250 GB de capacidad) se transfiere al modo de operación SLC, es decir. , solo se registra un bit de información en cada celda, lo que permite aumentar significativamente su rendimiento y reducir la tasa de desgaste. SLC participa en el registro y la consolidación de los datos almacenados en el SSD, lo que permite no solo aumentar la velocidad de las operaciones, sino también reducir la tasa de desgaste de la celda. En las versiones actuales de SSD Western Digital, se utiliza la tecnología nCache 3.0, cuya última versión ha adquirido la función directa a TLC, lo que permitió encontrar un equilibrio entre el almacenamiento en caché y la velocidad: los datos se escriben sin pasar por el caché cuando está lleno o cuando se usa SLC- El buffer no es práctico. Esto, por un lado, ayudó a descargar el caché y, al mismo tiempo, a evitar una caída dramática en el rendimiento al llenarlo.

En cuanto a la tecnología de nivelación del desgaste, ayuda a garantizar que todos los bloques de páginas disponibles se utilicen de la manera más uniforme posible. Como sabe, cualquier sistema operativo utiliza un mecanismo lógico para direccionar bloques de datos (LBA), mientras que el controlador mismo opera con direcciones físicas (PBA), correlacionándolas con las lógicas. Como resultado de esto, no importa dónde se encuentren realmente los fragmentos de los archivos, debido a lo cual es posible escribir un microprograma que garantice que la carga entre las celdas se distribuya de manera uniforme.

La nivelación del desgaste asegura una carga uniforme en las celdasEn el caso general, su algoritmo es el siguiente. Usted compró un SSD nuevo y, aunque hay espacio libre en él, la información se registrará en bloques libres. A medida que opera, comienza a eliminar archivos innecesarios, y el mecanismo de recolección de basura los limpia en segundo plano, sin embargo, se usarán para grabar solo después de que no quede un solo bloque en el disco al menos una vez en el que se escribieron los datos. Por supuesto, en realidad, todo es mucho más complicado, pero el significado no cambia.

Y aquí debería hacerse una nota más importante con respecto a los productos de Western Digital. Cuando decidimos desarrollar el mercado de SSD, podíamos ir de dos maneras: comprar memoria y controladores de terceros, centrándonos solo en el desarrollo y la optimización del firmware, o configurar una producción de ciclo completo. Ejecutar un proyecto así desde cero sería poco práctico, e incluso la

compra de SanDisk nos

ha costado un centavo. Pero los fondos invertidos superaron por completo: controlando la producción de chips, tuvimos la oportunidad de adaptar los microprogramas a las características de los microcircuitos.

Debe entenderse que escribir bits de información en celdas de memoria flash es un proceso mucho más complicado de lo que parece a primera vista: tiene en cuenta cientos de parámetros diferentes, el más importante de los cuales es el voltaje requerido para la transferencia de carga y el tiempo de grabación. A medida que los chips se desgastan, sus características físicas también cambian: para un registro de datos exitoso, se requiere menos voltaje y, al mismo tiempo, se reduce el tiempo necesario de su influencia en la célula. En la mayoría de los SSD, estos parámetros son constantes, pero en los SSD de Western Digital, por el contrario, cambian dinámicamente a medida que las células se desgastan, lo que permite maximizar la vida útil de cada uno de ellos, minimizando el impacto negativo en las estructuras de semiconductores.

QLC 3D NAND - memoria flash de última generación

Si sigue las noticias del mundo de las altas tecnologías, probablemente sepa que Western Digital está dominando activamente la producción de memoria tridimensional de próxima generación: QLC 3D NAND (el primer anuncio tuvo lugar en junio de 2018). El acrónimo QLC significa celda de cuatro niveles. En otras palabras, se pueden almacenar 16 niveles de carga en una celda, codificando no solo tres, sino cuatro bits de información. En comparación con TLC 3D NAND, la densidad de grabación en QLC aumentó en un 33%: por lo tanto, la capacidad de un chip de 64 capas aumentó a 768 Gbps. Pero este no es el límite: en agosto de 2018 comenzamos el lanzamiento de microcircuitos de 96 capas. Al aumentar el número de capas, pudimos obtener un aumento del 50 por ciento en la capacidad y superar la barrera de 1 Tbit: los nuevos chips, llamados 3D NAND BiCS4, pueden acomodar 1,33 Tbit de información, que es de aproximadamente 166 GB. Fue posible lograr una densidad de almacenamiento de datos tan alta combinando dos cristales de 48 capas (hoy es el enfoque más viable económicamente).

La mayor capacidad es potencialmente capaz de reducir el rendimiento de los SSD, pero no debe preocuparse por esto: la nueva memoria flash 3D NAND BiCS4 utiliza cuatro en lugar de dos matrices físicas, lo que permite optimizar la lectura y escritura de datos mediante operaciones paralelas, y esto, a su vez, Ayudará a utilizar de manera más eficiente el caché y a controlar el nivel de desgaste de la celda, al tiempo que mantiene la vida útil de los chips QLC a un nivel comparable a las soluciones TLC modernas. Sin embargo, una descripción de las tecnologías subyacentes QLC está más allá del alcance de este material y ciertamente merece un artículo separado.