Continuamos considerando UDB basado en la documentación patentada de Cypress, es decir, trivia útil relacionada con Datapath.

El contenido general del ciclo “UDB. ¿Qué es esto?

Parte 1. Introducción. Pld.Parte 2. Ruta de datos.Parte 3. Datapath FIFO.Parte 4. Datapath ALU.Parte 5. Ruta de datos. Pequeñas cosas útiles. (Artículo actual)

Parte 6. Módulo de gestión y estado.Parte 7. Módulo de control de temporización y reinicioParte 8. Abordar UDB21.3.2.6 Soporte CRC / PRS

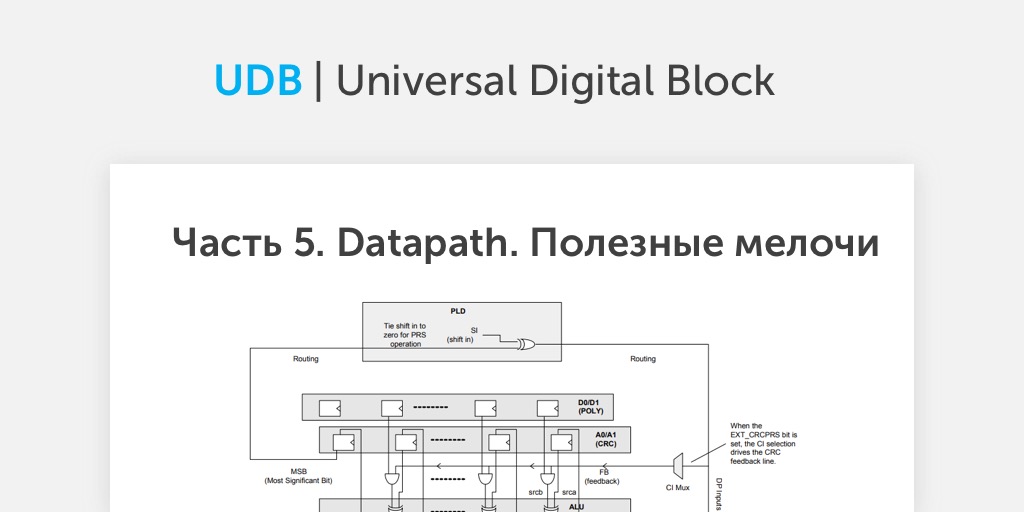

Datapath admite la generación de la verificación de redundancia cíclica (CRC) y secuencias pseudoaleatorias (secuencia pseudoaleatoria, PRS). Las señales encadenadas se rastrean entre los bloques de Datapath para admitir CRC / PRS de más de 8 bits.

El número de bit más significativo (MSB) del bloque CRC / PRS más alto se selecciona y rastrea (y encadena a otros bloques) a los bloques más bajos. Después de eso, la operación XOR con datos de entrada (datos SI) se aplica al MSB, proporcionando una señal de retroalimentación (retroalimentación, FB). Después de eso, la señal de retroalimentación se rastrea (y se conecta en una cadena con otros bloques) a los bloques inferiores. Este valor de retroalimentación se utiliza en todos los bloques para realizar la operación

XOR del polinomio (del registro Data0 o Data1) con el valor actual de la batería.

La figura 21-18 muestra la configuración estructural de la operación CRC. La configuración PRS es idéntica, pero la entrada de desplazamiento (SI) se extrae a 0. En modo PRS, D0 o D1 contiene el valor polinomial, y A0 o A1 contiene el valor inicial (semilla) y el valor CRC obtenido después del cálculo.

Nota del traductor.Aparentemente, hay un error tipográfico en la documentación de propiedad en esta oración, ya que se debe obtener un número aleatorio en modo PRS. Y la información sobre CRC se encuentra justo debajo. Figura 21-18. Estructura funcional de CRC.

Figura 21-18. Estructura funcional de CRC.Para activar el soporte CRC, debe establecer el bit

CFB_EN en la RAM de configuración dinámica en 1. Esto activa la operación

AND con respecto a la entrada SRCB ALU y la señal de retroalimentación CRC. Si este bit se establece en cero, la señal de retroalimentación se asignará a uno, lo que permite realizar operaciones aritméticas normales. El control dinámico de este bit en cada ciclo le permite alternar las operaciones CRC / PRS con otras operaciones aritméticas.

Encadenamiento CRC / PRS

La figura 21-19 muestra un ejemplo de unión de CRC / PRS en cadenas entre tres UDB. Este escenario admite la operación en modos con una resolución de 17 a 24 bits. Los bits de enlace de control en las cadenas se configuran de acuerdo con la posición del Datapath en la cadena (ver figura).

Figura 21-19. Cadena de unión de CRC / PRS.

Figura 21-19. Cadena de unión de CRC / PRS.Cómo se conecta la señal de retroalimentación CRC / PRS (cfbo, cfbi) en una cadena:

- Si el bloque seleccionado es el más joven, la señal de retroalimentación en este bloque se genera a partir de la lógica incorporada, que lleva la entrada de desplazamiento a la derecha (señor) y realiza una operación XOR en ellos con el bit más significativo. (En el caso de PRS, la señal "señor" se establece en "0").

- Si el bloque seleccionado no es un bloque de orden inferior, el bit de configuración CHAIN FB debe ser amartillado y la retroalimentación se transmite en una cadena desde el bloque anterior.

¿Cómo encadena la señal CRC / PRS MSB (cmsbo, cmsbi):

- Si el bloque seleccionado es alto, el bit de configuración MSB (de acuerdo con el polinomio seleccionado) se configura utilizando los bits de configuración MSB_SEL .

- Si el bloque seleccionado no es alto, el bit de configuración CHAIN MSB debe ser amartillado y la señal MSB se enviará a lo largo de la cadena desde el siguiente bloque.

Especificación polinómica CRC / PRS

Como ejemplo de la configuración del polinomio para escribir en el registro correspondiente D0 / D1, considere el polinomio

CCITT CRC-16 , que tiene la forma x

16 + x

12 + x

5 + 1. El método para extraer el formato de datos del polinomio se muestra en la Figura 21-20. El término X0, por definición, siempre es 1, por lo tanto, no necesita ser escrito. Para todos los demás miembros del polinomio, la unidad se establece en las posiciones necesarias, como se muestra en la figura.

Figura 21-20. El formato del polinomio CCITT CRC16.

Figura 21-20. El formato del polinomio CCITT CRC16.Tenga en cuenta que el formato del polinomio es ligeramente diferente del formato especificado en el formato hexadecimal clásico. Por ejemplo, el polinomio

CCITT CRC16 se conoce comúnmente como

1021H . Para convertirlo al formato requerido para Datapath, debe realizar un desplazamiento a la derecha en una posición y agregar 1 al bit MSB. En este caso, el valor polinómico correcto que se escribirá en D0 o en D1 es

8810H .

Ejemplo de configuración CRC / PRS

La siguiente es una breve descripción de los requisitos de configuración de CRC / PRS, siempre que D0 sea un polinomio y CRC / PRS se calcule en A0:

- Elija un polinomio adecuado (ejemplo anterior) y escríbalo en D0.

- Seleccione la semilla apropiada (por ejemplo, todos ceros para CRC o todos para PRS) y escríbala en A0.

- Si es necesario, configure el encadenamiento como se describe anteriormente.

- Seleccione un elemento MSB como se describe arriba.

- Configure los campos dinámicos de RAM RAM:

a. Seleccione D0 como ALU "SRCB" (fuente de datos ALU B)

b. Seleccione A0 como ALU "SRCA" (fuente de datos ALU A)

c. Seleccione

XOR para la operación ALU

d. Seleccione

SHIFT LEFT para la operación SHIFT

e. Seleccione

CFB_EN para habilitar el soporte CRC / PRS.

f. Seleccione ALU como fuente de registro A0

Al elegir CRC, debe configurar el

desplazamiento en el campo

derecho para los datos de entrada y enviar datos sobre esta entrada en cada paso. Al elegir PRS, debe establecer

shift en derecha a 0.

Esta configuración de UDB genera el CRC necesario o produce el bit más significativo, que puede reenviarse al exterior, eliminando de él una secuencia pseudoaleatoria.

Modo externo CRC / PRS

Para habilitar la computación externa CRC o PRS, puede especificar un bit de configuración estática (

EXT CRCPRS ). Como se muestra en la Figura 21-21, el cálculo de retroalimentación CRC se realiza en el bloque PLD. Cuando el bit está armado, la señal de retroalimentación CRC se transmite directamente desde el multiplexor de entrada CI (Carry In), omitiendo los cálculos internos. La figura muestra una configuración simple que admite CRC o PRS de hasta 8 bits. Por lo general, se utilizan circuitos electrónicos integrados, pero este parámetro le permite implementar configuraciones más complejas, por ejemplo, funciones CRC / PRS de 16 bits en un UDB, utilizando multiplexación por división de tiempo.

Figura 21-21. Modo externo CRC / PRS.

Figura 21-21. Modo externo CRC / PRS.En este modo, el bit

CFB_EN de la RAM de configuración dinámica también controla si la operación

AND se usa en la señal de retroalimentación CRC en la entrada CRU de ALU o no. Por lo tanto, como en el caso del modo CRC / PRS interno, esta función puede, si es necesario, alternar con otras funciones.

21.3.2.7 Salidas de ruta de datos y multiplexación

Las condiciones se generan a partir de los valores de activación de la batería, las salidas ALU y el estado FIFO. Estas condiciones pueden transmitirse a través de canales de rastreo digital a otros UDB para formar solicitudes de interrupción, ya sea al DMA o a las "patas del chip". 16 condiciones posibles se muestran en la tabla a continuación.

Tabla 21-16. Generación de condición de ruta de datos.

Hay seis salidas de Datapath. Como se muestra en la Figura 21-22, cada salida tiene un multiplexor 16 en 1 que le permite enrutar cualquiera de las 16 señales a cualquier salida de Datapath.

Figura 21-22. Conexiones al multiplexor de salida.

Figura 21-22. Conexiones al multiplexor de salida.Comparaciones

Hay dos comparaciones, una de las cuales tiene fuentes fijas (

Comparar 0 ), y la otra se selecciona dinámicamente (

Comparar 1 ). Cada comparación tiene un registro de enmascaramiento estático de 8 bits, lo que permite comparaciones en el campo de bits especificado. Por defecto, el enmascaramiento está deshabilitado (se comparan todos los bits) y debe activarse manualmente.

Las entradas de Comparar 1 se configuran dinámicamente. Como se muestra en la tabla a continuación, hay cuatro parámetros de Comparar 1 que se aplican a las condiciones menos e iguales. Los

bits de configuración

CMP SELA y

CMP SELB determinan las posibles configuraciones de comparación. Los bits de RAM de la configuración dinámica especifican una de las configuraciones (A o B) en cada ciclo.

Tabla 21-17. Configuración de comparación.

Compare 0 y

Compare 1 están asociados con las condiciones generadas en el Datapath anterior de forma independiente (en el orden de tratamiento). Si se deben encadenar o no las comparaciones estáticamente especificado en los registros de configuración UDB. La Figura 21-23 muestra la vinculación "igual" a la cadena de comparación, lo que se reduce a aplicar la operación

AND a la comparación "igual" de este bloque y a la entrada del bloque anterior.

Figura 21-23. Vincular a la cadena de comparación es "igual".

Figura 21-23. Vincular a la cadena de comparación es "igual".La figura 21-24 muestra el enlace a la cadena de comparación menor. En este caso, el resultado de salida (cl0) para un bloque dado es generado por el circuito de comparación "menor que" y es incondicional. Esta señal se combina

O con el resultado entrante de la cadena si la condición es igual al bloque actual y el modo de enlace está activado.

Figura 21-24. Enlace menor que

Figura 21-24. Enlace menor queDetección de todos los ceros y todos

Cada batería tiene un detector de todos los ceros y un detector de todas las unidades. Estas condiciones se pueden encadenar estáticamente como se indica en los registros de configuración de UDB. El modo de enlace se establece en los registros de configuración UDB. La vinculación en la cadena de detección de ceros se produce de acuerdo con el mismo concepto que la comparación "es igual". Si se activa el encadenamiento, la operación

AND se aplica a los datos vinculados con éxito.

Desbordamiento

Un desbordamiento se define como una operación de transferencia

XOR en un MSB y una transferencia desde un MSB. Los cálculos se realizan con el MSB actual, como se indica en los bits

MSB_SEL . Esta condición no se puede encadenar, sin embargo, el cálculo será correcto si la función de capacidad total se realiza en el Datapath superior hasta que se conecte la transferencia entre los bloques.

21.3.2.8 Ruta de datos de entradas y salidas paralelas

Como se muestra en la figura 21-25, las señales de entrada

paralela (PI) y

salida paralela (PO) proporcionan una capacidad limitada para entregar datos y rastrear recursos a Datapath y enviar datos desde ella. Las señales PO siempre están disponibles para el rastreo como una opción de ALU asrc entre A0 y A1.

Nota del traductor.Este es un mecanismo extremadamente importante que permite que UDB funcione no solo con datos en serie, sino también con datos paralelos. Por alguna razón, este documento no enfatiza esto, pero puede leerlo al pasar en una de las Notas de aplicación. Figura 21-25. Señales de ruta de datos de entrada / salida paralelas.

Figura 21-25. Señales de ruta de datos de entrada / salida paralelas.Para ingresar datos en la ALU, debe seleccionar

Parallel In . Hay dos modos: estático y dinámico. En modo estático, el bit

PI SEL convierte el valor de asrc ALU a PI. El bit

PI DYN se usa para proporcionar el modo dinámico PI. Cuando está armado, y también siempre que

PI SEL sea 0, el multiplexor PI puede controlar el bit de control dinámico

CFB_EN . La función principal del bit

CFB_EN es proporcionar la funcionalidad PRS / CRC.

21.3.2.9 Encadenamiento Datapath

Cada bloque Datapath tiene una ALU de 8 bits, que está diseñada para encadenar guiones, desplazamientos, disparadores de captura y señales condicionales al Datapath vecino más cercano para crear funciones aritméticas y registros de desplazamiento con profundidades de bits más altas. Estas señales, conectadas en cadenas, están aisladas y le permiten implementar de manera efectiva funciones de 16-24 y 32 bits en un solo ciclo sin carreras y otros problemas derivados de los retrasos en los canales de rastreo. Además, los agarres de encadenamiento admiten la lectura atómica de baterías en bloques vinculados. Como se muestra en la Figura 21-21, todas las señales condicionales y de captura generadas están conectadas en una cadena que se mueve desde el bloque más joven al más antiguo. Un cambio a la izquierda también se realiza de junior a senior. Se realiza un desplazamiento a la derecha del más antiguo al más joven. La señal de encadenamiento CRC / PRS para retroalimentación se enruta de mayor a menor, y la salida MSB se envía de mayor a menor.

Figura 21-26. Datapath cadena de subprocesos.

Figura 21-26. Datapath cadena de subprocesos.21.3.2.10 Configuración dinámica de RAM

Cada Datapath contiene una RAM de configuración dinámica con 8 palabras de 16 bits cada una (consulte la Figura 21-27). El propósito de dicha RAM es controlar los bits de la configuración de Datapath en cada ciclo, en función del reloj seleccionado para este Datapath. RAM tiene puertos síncronos de lectura y escritura para descargar configuraciones a través del bus del sistema.

Para enviar rápidamente estas palabras de 16 bits a Datapath, se proporciona un puerto de lectura asíncrono adicional como bits de control. Las entradas de dirección asincrónicas se seleccionan mediante multiplexores de las entradas de Datapath, que se pueden tomar de cualquier señal posible, incluidas las patas de microcircuitos, las salidas PLD, las salidas de la unidad de control o cualquier salida de Datapath.

El propósito principal de un puerto de lectura asíncrono es proporcionar una decodificación rápida de bits de control de Datapath en un solo ciclo.

Figura 21-27. Configuración de E / S de RAM.

Figura 21-27. Configuración de E / S de RAM.Los campos de la palabra RAM de la configuración dinámica se muestran en las siguientes tablas junto con una descripción del uso de cada campo.

Tabla 21-18. Referencia de configuración dinámica.

(a. - Para los campos CI, SI y CMP, los campos RAM le permiten seleccionar una de dos opciones predefinidas. Consulte la configuración del registro estático).

Continuará ...