La tecnología FPGA (FPGA) actualmente está ganando gran popularidad. El número de aplicaciones está creciendo: además de procesar señales digitales, los FPGA también se utilizan para acelerar el aprendizaje automático, en tecnologías blockchain, procesamiento de video y en IoT.

Esta tecnología tiene un inconveniente significativo: para la programación, se utilizan lenguajes de descripción bastante complejos y específicos de los equipos digitales Verilog y VHDL. Esto complica la entrada de un recién llegado a la FPGA y es difícil para un empleador encontrar un especialista con este conocimiento específico en el mercado laboral. Por otro lado, el popular lenguaje de programación Python de alto nivel con el marco

MyHDL hace que la programación FPGA sea simple y agradable. Además, las personas que conocen Python son un orden de magnitud más especialistas con Verilog / VHDL. Con una serie de artículos, quiero mostrar lo fácil que es ingresar al campo de FPGA conociendo Python y comenzar a realizar proyectos FPGA realmente complejos en este lenguaje. Observo que python no se ejecuta directamente en el FPGA, sino que es una herramienta para generar firmware.

Primero, necesitamos la versión 3.6 de Python (en adelante, todas las operaciones se realizan en el sistema operativo Ubuntu 18.04).

Instalar myhdl:

pip3 install myhdl

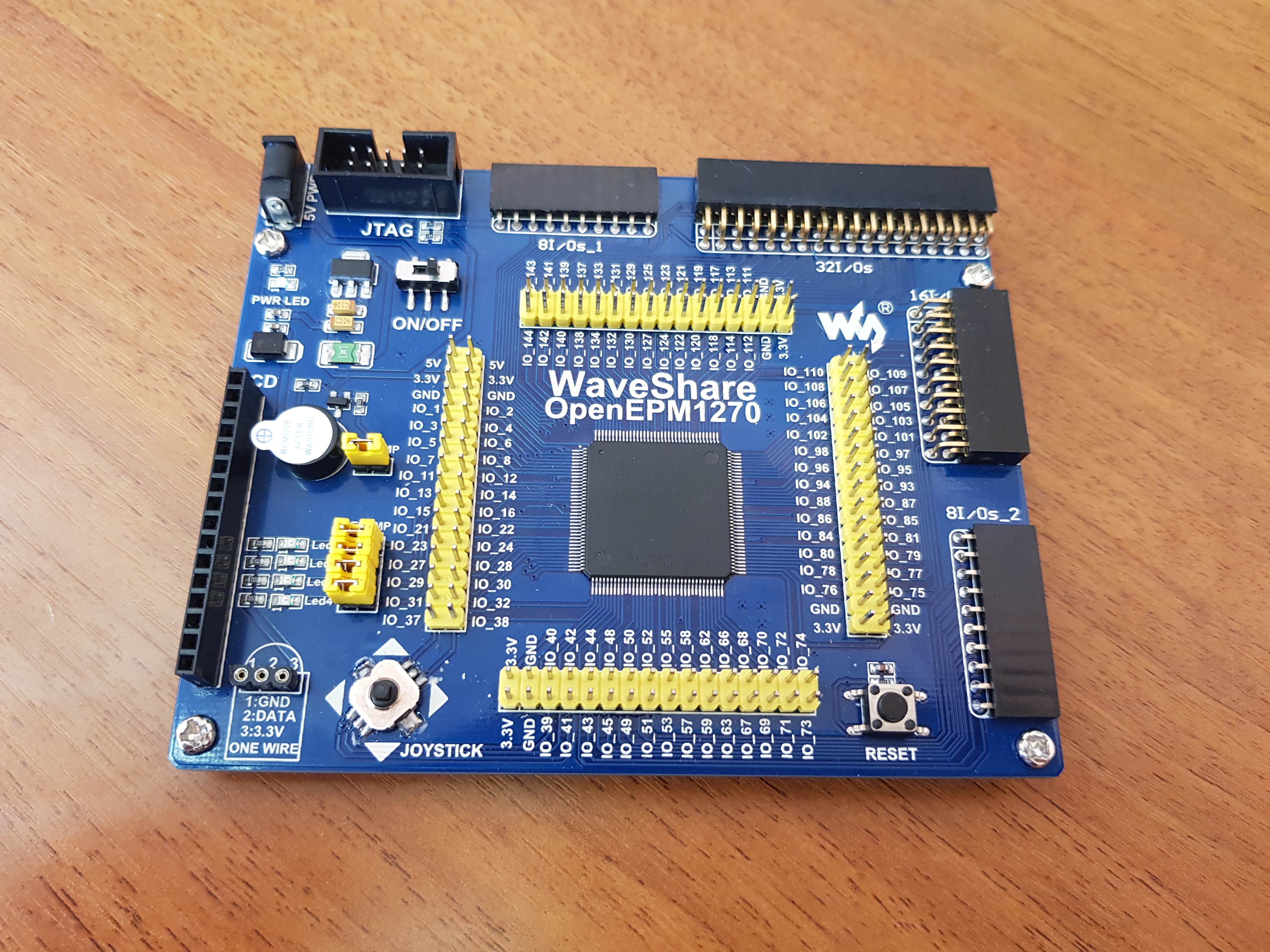

Como "¡Hola mundo!" Escribiremos un programa simple que haga que los LED se enciendan cuando se presione un botón. En el mundo de los microprocesadores "¡Hola Mundo!" Este es un programa que parpadea con un LED, en el mundo FPGA Hello World es el parpadeo de miles de LED. Solo hay cuatro LED en el tablero, por lo que solo los parpadearemos, dependiendo de la presión del botón. Es importante tener en cuenta que todo el código en FPGA, a diferencia de los microcontroladores, se ejecuta al mismo tiempo, todos los diodos se encienden y se apagan al mismo tiempo. Y no secuencialmente en el caso de los microcontroladores. La prueba utiliza la placa WaveShare OpenEPM1270 con placas Altera Max II EPM1270T144C5 a bordo.

Crea un nuevo archivo de Python:

from myhdl import * from random import randrange def led_blinker(input1, led1, led2, led3, led4): @always_comb def on_off_led(): if input1 == 1: led1.next = 1 led2.next = 1 led3.next = 0 led4.next = 0 else: led1.next = 0 led2.next = 0 led3.next = 1 led4.next = 1 return on_off_led

Para saber si nuestro código funciona correctamente, necesita una herramienta de verificación. De hecho, cualquier programa para FPGA es un procesador de señal digital, por lo que el desarrollador debe asegurarse de indicar correctamente qué hacer con el chip. Esto se hace a través de la simulación, para esto necesita instalar un programa que muestre las señales procesadas. Hay muchos de estos programas, pero en mi opinión, el mejor GTKWave gratuito en este momento. Se pone desde la terminal:

sudo apt-get install gtkwave

A continuación, en el archivo con el firmware, se debe describir el entorno de prueba. Esta también es una función de Python:

def test(): input1, led1, led2, led3, led4 = [Signal(bool(0)) for i in range(5)] test = led_blinker(input1, led1, led2, led3, led4) @always(delay(10)) def gen(): input1.next = randrange(2) return test, gen

Aquí el entorno de prueba genera una secuencia aleatoria de ceros y unos (se usa el módulo Python random).

def simulate(timesteps): tb = traceSignals(test) sim = Simulation(tb) sim.run(timesteps)

E inicializamos el simulador, arrastrando la función de entorno test_inverter allí. Por lo tanto, obtenemos el inversor de muñeca ruso → test_inverter → simulate (tiempo en unidades arbitrarias).

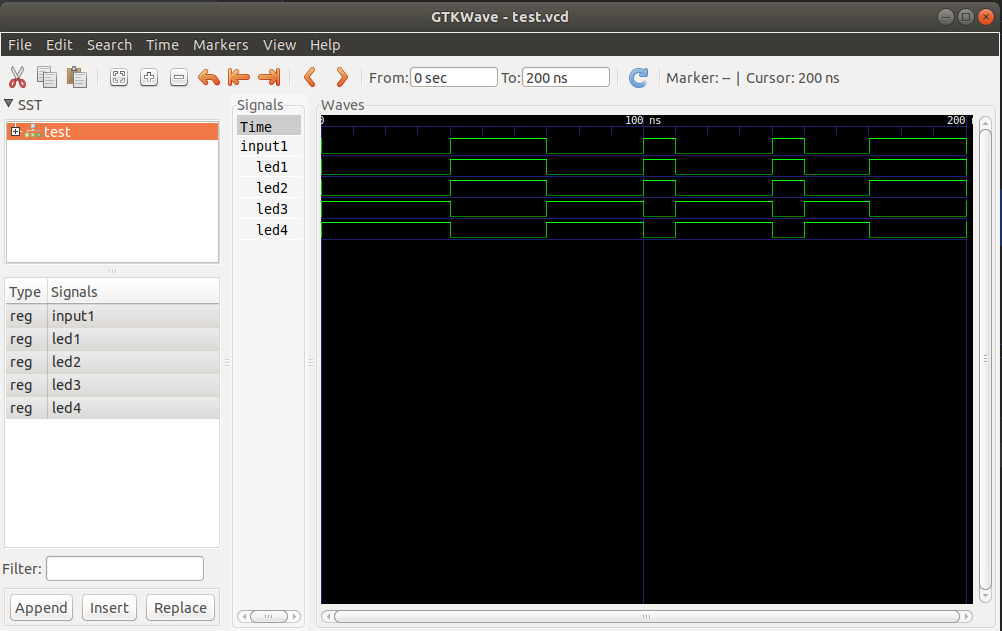

Después de ejecutar el script en la carpeta de trabajo, cree un archivo .vcd y ejecútelo a través de gtkwave, en el terminal: gtkwave test_invereter.vcd.

Como resultado, se generó una secuencia aleatoria de señales de entrada input1 y cómo la función led_blinker procesó estas señales.

Después de asegurarnos de que la lógica funcionara exactamente como queríamos, deberíamos incluir esta función en FPGA. Estoy acostumbrado a trabajar con chips de Intel (anteriormente Altera), esta secuencia de operaciones es similar para los chips de otros fabricantes con sistemas CAD adecuados. Se crea un archivo binario en el chip FPGA, creado por el compilador del fabricante del chip, para Intel es Quartus, para Xilinx Vivado. Los compiladores solo pueden trabajar con código en VHDL / Verilog, por lo que el código de Python debe traducirse a cualquiera de estos idiomas (no importa cuál).

def convert(): input1, led1, led2, led3, led4 = [Signal(bool(0)) for i in range(5)] toVerilog(led_blinker, input1, led1, led2, led3, led4) convert()

En este ejemplo, el código se traduce a Verilog. El resultado está en el archivo led_blinker.v, y Quartus deberá proporcionarlo para generar el firmware FPGA:

module led_blinker ( input1, led1, led2, led3, led4 ); input input1; output led1; reg led1; output led2; reg led2; output led3; reg led3; output led4; reg led4; always @(input1) begin: LED_BLINKER_ON_OFF_LED if ((input1 == 1)) begin led1 = 1; led2 = 1; led3 = 0; led4 = 0; end else begin led1 = 0; led2 = 0; led3 = 1; led4 = 1; end end endmodule

En este enfoque para el desarrollo del firmware FPGA, puede ignorar este archivo y simplemente colocarlo en Quartus.

Puede descargar Quartus desde

fpgasoftware.intel.com , necesitamos una versión gratuita de Lite, será suficiente para nosotros. Descargue el tamaño de la versión básica de 9 GB.

Instalar Quartus no debería ser un problema para el usuario promedio de Linux. Después de la instalación, debe establecer algunos parámetros en el sistema para poder usar el dispositivo para flashear el programa FPGA: el programador:

1. Crear una regla de udev. Para hacer esto, cree un nuevo archivo /etc/udev/rules.d/51-altera-usb-blaster.rules con el siguiente contenido:

Reinicie udev usando udevadm:

sudo udevadm control --reload

2. Permita el acceso no root al dispositivo USB-Blaster. Para hacer esto, cree el archivo /etc/udev/rules.d/altera-usb-blaster.rules con la línea:

ATTR{idVendor}=="09fb", ATTR{idProduct}=="6001", MODE="666"

Esto le da acceso rw-rw-rw- al programador.

3. Configure jtagd. Quartus utiliza el demonio jtagd para trabajar, que asocia el software con un dispositivo programador. Copie la descripción de su directorio con Quartus:

sudo mkdir /etc/jtagd sudo cp <Quartus install path>/quartus/linux64/pgm_parts.txt /etc/jtagd/jtagd.pgm_parts

Ejecute Quartus y cree un nuevo proyecto "Archivo" - "Asistente de nuevo proyecto", escriba el nombre del proyecto.

Luego, haga clic en Siguiente. Y en el menú Agregar archivos, conectamos el archivo Verilog generado con la extensión .v. Por lo tanto, si el archivo verilog se edita desde un archivo python, Quartus lo recogerá automáticamente. A continuación, llegaremos al menú de selección de dispositivos, en nuestro caso es MAX II EMP1270T144C5 y las próximas dos veces. El proyecto está creado.

En el Navegador de proyectos, vaya al menú de archivo y haga clic derecho en nuestro archivo verilog "Establecer como entidad de nivel superior".

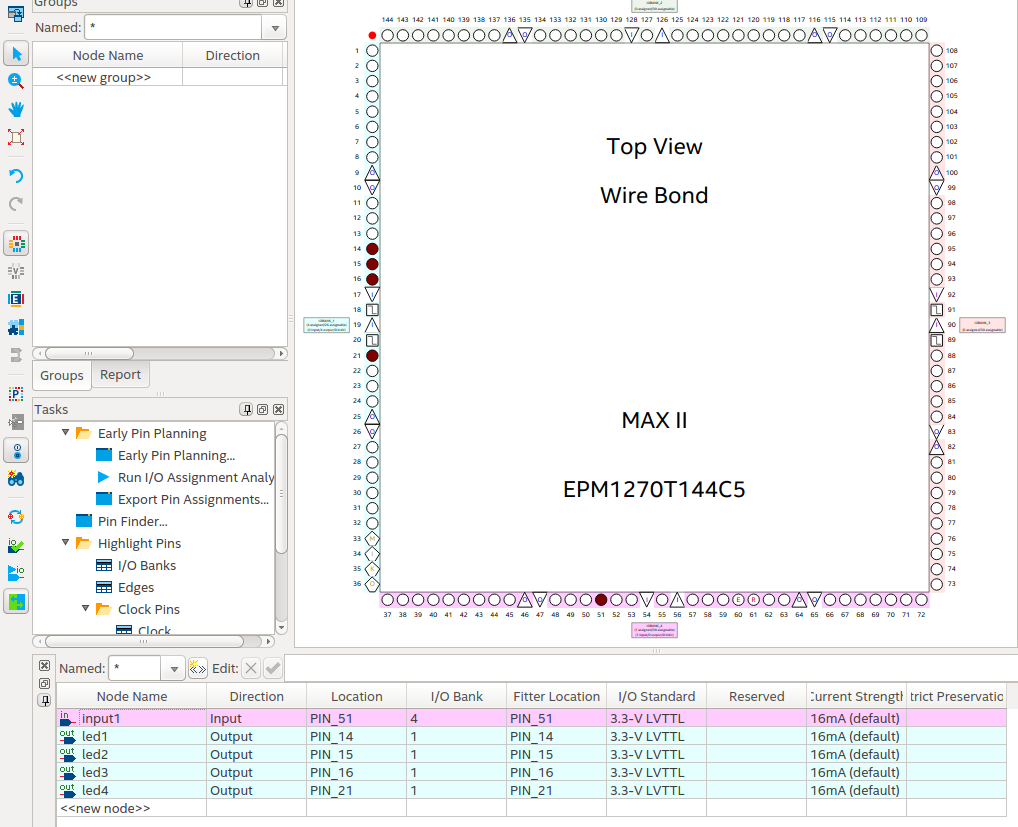

Compilamos el proyecto. Ahora, en el menú "Asignaciones-Pin Planner", configure los pines en el chip:

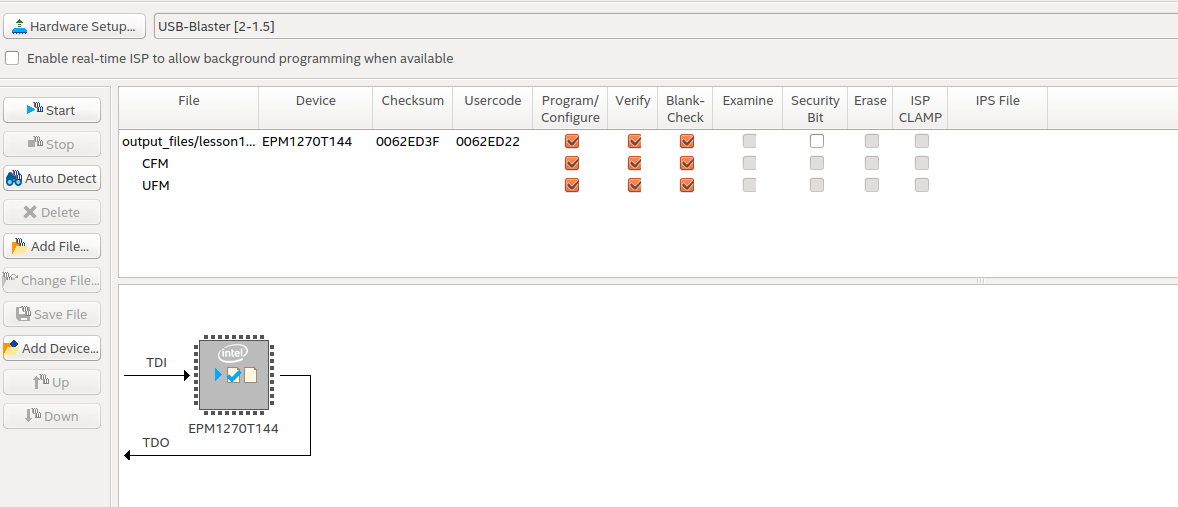

Compilar de nuevo. Ahora todo está listo para la programación: Herramientas-Programador. Conectamos el programador y la alimentación a la placa, en la configuración de hardware seleccionamos nuestro USB-Blaster, configuramos las casillas de verificación como se muestra en la figura y comenzamos.

Después de que el programador informó exitoso. Puedes ver el resultado en el tablero:

Conclusión

Esta lección describe cómo crear un entorno de trabajo y el primer proyecto simple de FPGA en el lenguaje de programación Python.

Considerado:

- cómo instalar:

- Programador USB Blaster configurado en Ubuntu;

- FPGA Proyecto FPGA desarrollado;

- Prueba y verificación del proyecto;

- Compiló un proyecto para FPGA;

- Proyecto subido a FPGA.