Recientemente, recientemente se lanzó un curso en línea gratuito en tres partes titulado "Cómo funcionan los creadores de nanochips inteligentes" (

1 ,

2 ,

3 ). Está destinado a la orientación profesional de los escolares y se caracteriza por la máxima especificidad: así es como se ve la distribución del trabajo en el equipo de diseño de microchips, aquí el desarrollo se basa en dichos conceptos de diseño a nivel de transferencia de registro, y estos algoritmos se utilizan para determinar cuántos megahercios funcionará el procesador diseñado para la computadora electrónica automotriz.

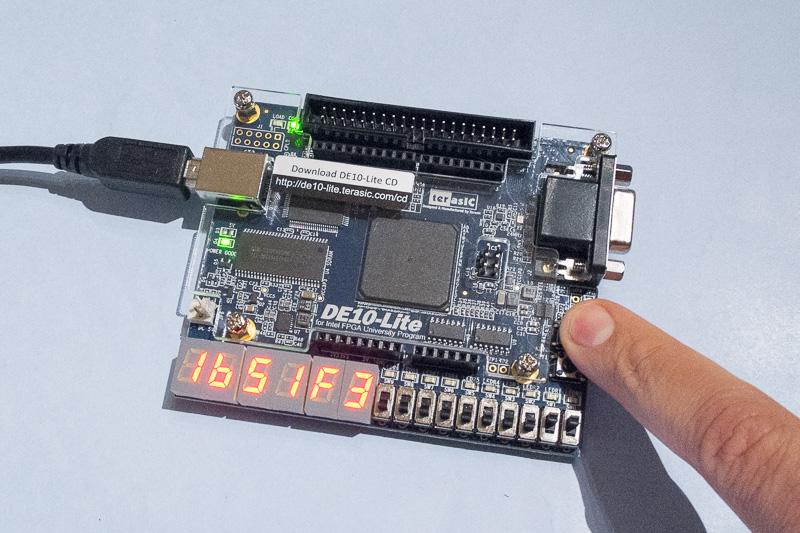

Además de la orientación profesional teórica, el curso se puede utilizar para seleccionar estudiantes para escuelas prácticas de verano sobre FPGA y diseño de procesadores. Tal escuela está planeada este año en Zelenograd, su prototipo fue probado en la Escuela de Verano para Jóvenes Programadores en Novosibirsk y en la Semana de la Electrónica para escolares en Kiev el año anterior. También puede intentar hacer un hackathon en redes neuronales implementadas en hardware e implementación de hardware de juegos con salida a una pantalla VGA (más sobre eso más adelante en la publicación).

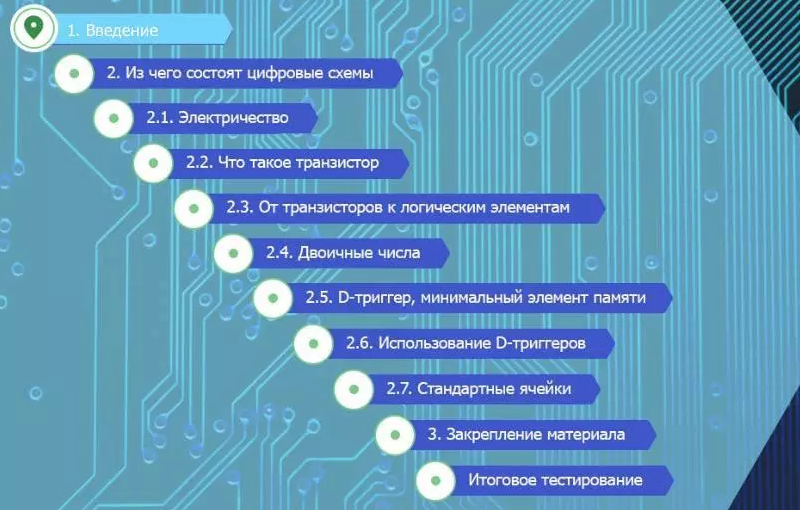

Brevemente sobre lo que se incluye en cada uno de los tres módulos: "Del transistor al microcircuito", "El lado lógico de los circuitos digitales" y "El lado físico de los circuitos digitales".

El curso "Cómo funcionan los creadores de nanochips inteligentes" comienza desde cero absoluto, por lo tanto, su primera parte, "Del transistor al microcircuito", repite en gran medida otros materiales electrónicos para escolares que se han creado en los últimos 50 años: lo que es un transistor, elementos lógicos, binarios números y disparadores. El concepto del D-flip-flop dentro del iPhone moderno sigue siendo el mismo que en la revista Quantum de 1986. Los transistores disminuyeron mil veces, pero su esencia no ha cambiado.

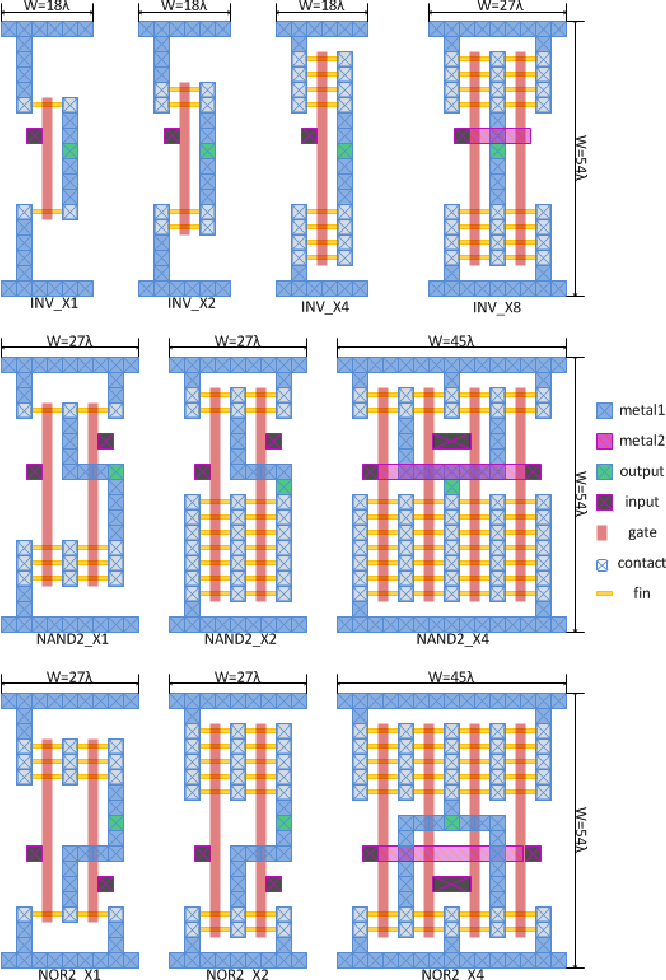

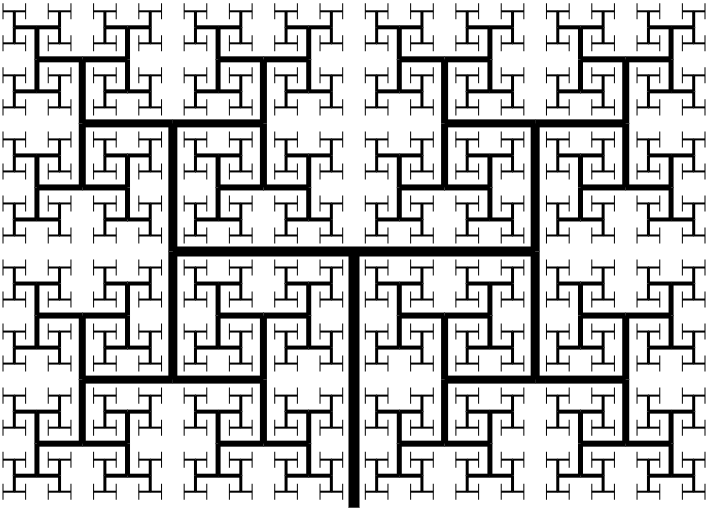

El único bloque de información que no estaba en los cursos anteriores es sobre las llamadas células estándar, sobre las tecnologías de las cuales se construye la gran mayoría de los microcircuitos especializados modernos. Se ven así:

Intente responder la pregunta de las pruebas a continuación, y si conoce la respuesta, puede omitir el primer módulo del curso:

¿Por qué las células estándar de microchips modernos (células estándar ASIC) se llaman estándar?

- Oh lo se! Esto se debe a que implementan las funciones lógicas estándar AND, OR, NOT

- Los elementos del transistor en las celdas estándar tienen una composición química estándar.

- Las celdas estándar funcionan a la velocidad de reloj estándar

- Tienen una altura estándar (dimensión en el área), lo que simplifica el suministro de energía para ellos y su conexión automática entre sí.

- La estructura de las celdas estándar alguna vez fue estandarizada por algún comité europeo de estándares.

La respuesta correcta es:

Texto oculto4. Las celdas estándar (celdas estándar ASIC) tienen una altura estándar (dimensión en el área), lo que simplifica el suministro de energía para ellas y su conexión automática entre ellas.

Si no lo sabe, puede pasar por el primer módulo del curso: "Del transistor al microcircuito". Aquí está su contenido:

Si la mayor parte del primer módulo del curso "Cómo funcionan los creadores de nanochips inteligentes" habla sobre las mismas cosas que han estado en textos populares para escolares desde la década de 1970, entonces en la segunda parte, "El lado lógico de los circuitos digitales", entramos en el área que no había una revista Quantum, y que, en general, fue abandonada en la educación rusa debido al colapso de la URSS. Estamos hablando de la llamada ruta RTL a GDSII, métodos para diseñar un plan para colocar miles de millones de transistores y pistas de chips basados en la compilación / síntesis de código en los lenguajes de descripción de hardware Verilog y VHDL. El fracaso en esta área debe superarse, comenzando con el nivel de estudiantes avanzados. De lo contrario, no hay iPhones, robots o automóviles autónomos realmente rusos.

En los últimos años, Rusia ha estimulado la popularización del diseño de circuitos digitales al sintetizar descripciones de hardware a partir de idiomas, incluso debido al lanzamiento en ruso de un libro de texto gratuito (versión electrónica) de David Harris y Sarah Harris "Circuitos digitales y arquitectura de computadoras" . Las publicaciones en Habré sobre este libro de texto recibieron más de 300 mil visitas, y las descargas abrumaron dos veces al sitio británico Imagination Technologies. Recientemente se lanzó una versión revisada final del tutorial, que puede descargar

desde el enlace desde el sitio web de MIPS . Es cierto que el enlace funciona solo en Windows, pero en Mac y Linux tiene errores. Si tiene problemas con él, puede descargar la misma versión

desde aquí . O compre un libro de papel de DMK Press en Ozone o en el Labyrinth.

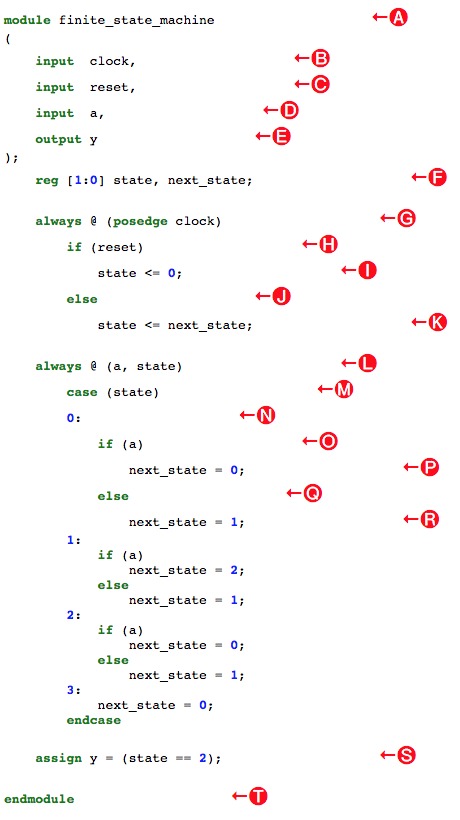

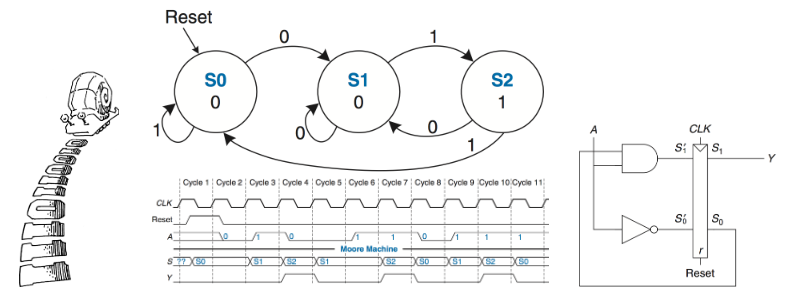

El módulo "Lado lógico de los circuitos digitales" del curso "Cómo trabajan los creadores de nanochips inteligentes" utiliza el ejemplo de un "caracol sonriente" de Harris. Un caracol es una máquina de estados que reconoce secuencias de ceros y unos. El curso comprende el código fuente de la máquina "caracol" en el lenguaje de descripción de hardware Verilog e introduce los conceptos de diagramas de estado de máquina de estado y diagramas de señales de tiempo. Después de esto, se muestra un circuito electrónico sintetizado a partir de la descripción, con elementos lógicos y disparadores D para almacenar el estado de la máquina de estado "caracol".

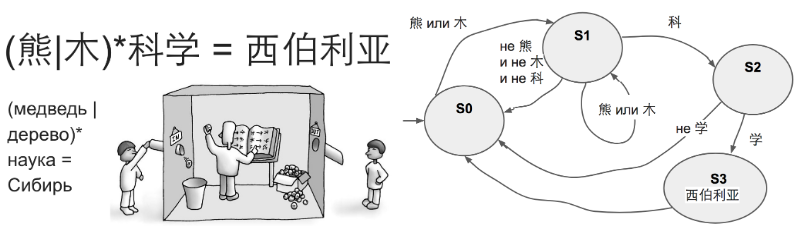

Basado en el ejemplo de "caracol", los escolares en hackatones pueden sintetizar varios "bloqueos de código" para tarjetas FPGA. En el examen del curso "Cómo funcionan los creadores de nanochips inteligentes", hay una pregunta sobre el diagrama de estado de la máquina de estado de la llamada "sala china", un ejemplo popular del campo de la inteligencia artificial. Aquí hay un diagrama de una máquina de estado simple para el diálogo con caracteres chinos. Si le das una combinación de varios jeroglíficos "árbol" y "oso", con los siguientes jeroglíficos "ciencia", la máquina emitirá una secuencia de jeroglíficos "Siberia" - este es un ejemplo que nació durante un seminario para escolares en el campus académico de Novosibirsk:

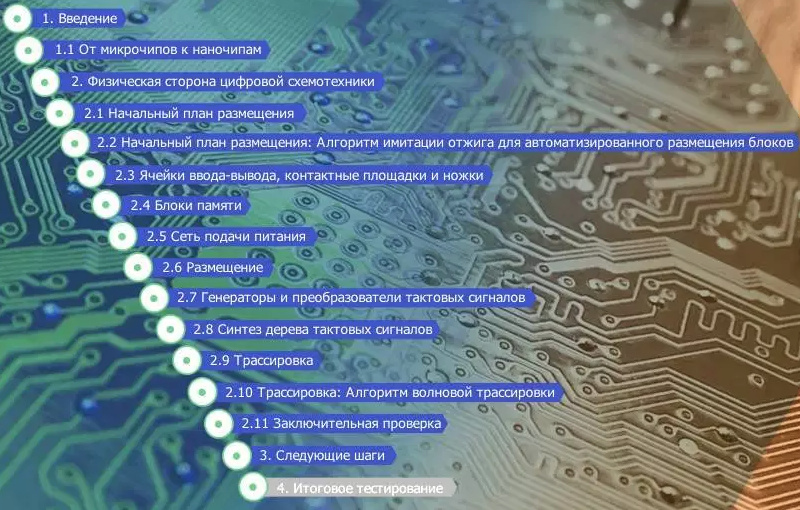

La tercera parte, "El lado físico de los circuitos digitales", describe cómo un gráfico de elementos lógicos sintetizados en la segunda parte se presenta en un microcircuito y se convierte en un dibujo GDSII que se envía a la fábrica donde se hornean los microcircuitos. Esta parte también analiza los algoritmos de ubicación y rastreo que serán de interés para los estudiantes con orientación matemática. La investigación en el campo de la automatización del diseño de microcircuitos es un área popular entre los antiguos ganadores de concursos de matemáticas.

Así es como se ve el diseño del chip después de colocarlo y rastrearlo usando el Compilador IC de Synopsys:

Pero esta elegante estructura fractal es un árbol de una señal de reloj dentro del chip, construida para que la señal de reloj llegue a todos los disparadores D aproximadamente al mismo tiempo. El ancho de las "ramas" de este árbol varía de compuestos metálicos gruesos a delgados en el microcircuito para satisfacer las limitaciones físicas de los conductores de cobre a nivel nanométrico de la tecnología de semiconductores:

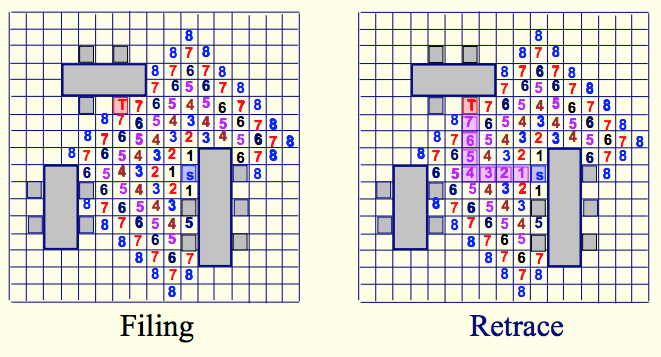

Y aquí hay una ilustración del llamado algoritmo de trazado de onda (en inglés Maze Routing - "Buscando rutas en el laberinto"). Este algoritmo se utilizó en los primeros programas de automatización de diseño para conectar los elementos lógicos de un circuito. El algoritmo de trazado de onda es tan simple que un estudiante de secundaria capaz puede escribirlo en C, Python o Java. Este es un ejercicio útil para aquellos que van a escribir algoritmos mucho más complejos en el futuro, por ejemplo, para futuros chips tridimensionales:

¿Qué pueden hacer los estudiantes después de dominar los conceptos de diseño de circuitos digitales en Verilog? Los ejercicios en el simulador o con luces intermitentes en la placa FPGA, aunque necesarios, son bastante molestos, y el diseño de procesadores simples y calculadoras neuronales es interesante solo para un pequeño porcentaje de estudiantes que deciden dominar la arquitectura de la computadora. Afortunadamente, los ejercicios que son posibles para los estudiantes no se limitan a estas dos áreas.

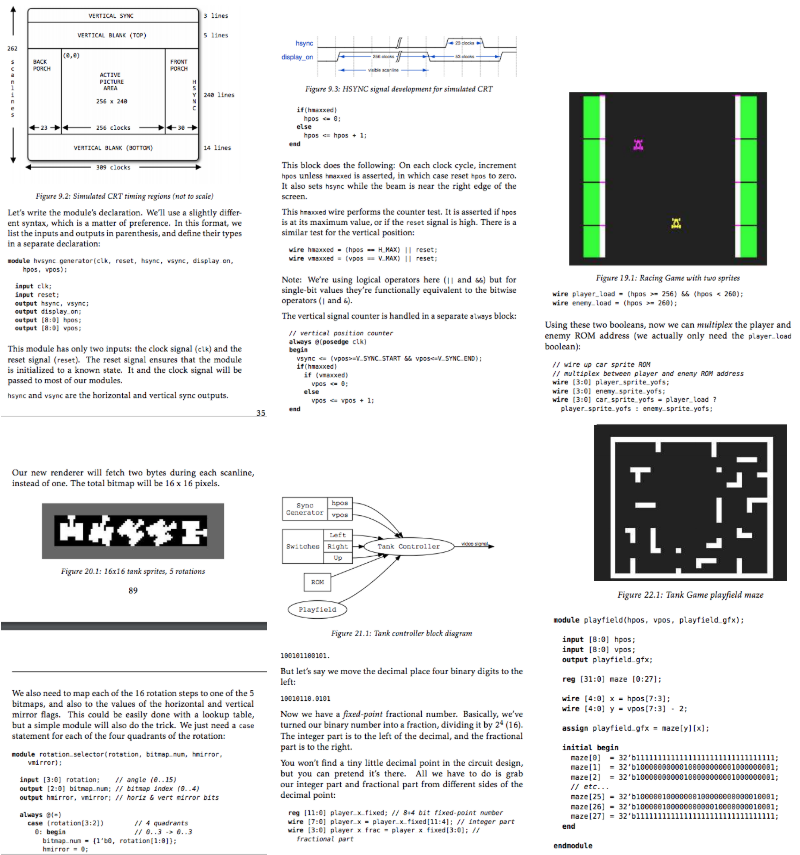

Hace solo dos meses, se publicó el libro Designing Video Game Hardware in Verilog de Steven Hugg, que describe el diseño de esquemas de juegos en Verilog, con la implementación en el FPGA conectado a la pantalla VGA. Estamos hablando de videojuegos de los años setenta y ochenta, con la generación de un escaneo, un frame buffer, sprites. Atari ping pong, guerras espaciales, tanchiki. Las máquinas tragamonedas para estos juegos se ensamblaron por primera vez en la década de 1970 en microcircuitos de un pequeño grado de integración, luego en PAL y microcontroladores, incluido Motorola 6502, que Apple utilizó por primera vez. El libro de Steven Hagg también analiza la implementación de hardware de sprites familiares para los programadores y jugadores soviéticos en la segunda mitad de la década de 1980 utilizando el procesador de video Texas Instruments TMS9918, que se instaló en las computadoras japonesas Yamaha MSX importadas en ese momento en las escuelas soviéticas.

El libro de Hagg es útil no solo y no tanto para los chiflados nostálgicos. Este es un excelente conjunto de tareas para estudiantes modernos y escolares que están comenzando a estudiar electrónica. Dado que las tareas son antiguas, pero aquí las tecnologías (Verilog, síntesis lógica, creación de prototipos FPGA) son nuevas, las mismas que ahora se están estudiando en el año académico 2018-2019

en el MIT en el curso de 6.111 . Sin ejercicios simples con Verilog y FPGA, los ingenieros que ahora se sientan en Santa Clara en Intel, NVidia y AMD, en Cupertino en Apple y otras compañías electrónicas no habrían crecido.

Para resumir. Sería bueno que ahora un cierto número de maestros de escuela y universidad revisen el curso "Cómo funcionan los creadores de nanochips inteligentes", después de lo cual enviarían a los estudiantes interesados. Luego, para los escolares que recibirán un certificado de este curso, puede invitarlos a un seminario práctico con paneles de FPGA (algunos de los cuales se distribuirán como premios para proyectos exitosos). Estos seminarios se están discutiendo ahora en Zelenograd, Moscú, también hay interés en Sochi, Minsk y otros lugares. A largo plazo, Rusia desarrollará una comunidad de desarrolladores de chips que se ha desarrollado en Silicon Valley, Japón, Taiwán, Corea del Sur, el Reino Unido, y que ahora está tomando forma en Shanghai y otros lugares. Esto es algo que debería existir en todos los países grandes técnicamente avanzados, y en Rusia hay suficientes tradiciones en matemáticas, física e ingeniería para apoyar tal desarrollo.