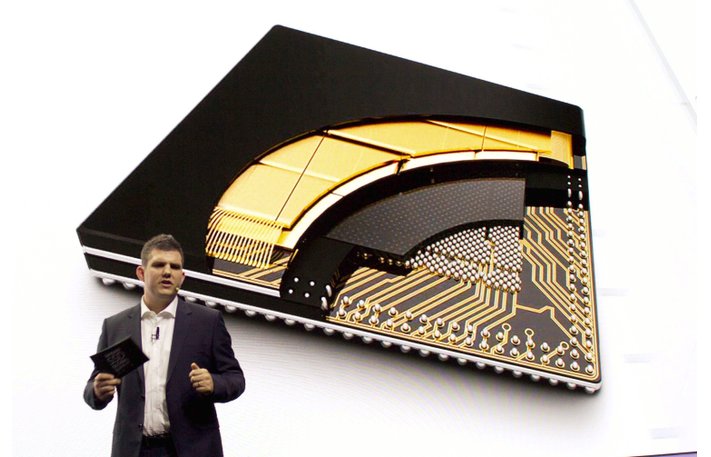

Intel Foveros 3D

Intel Foveros 3DDado que la Ley de Moore ya no se aplica, los diseñadores de chips deben buscar otras formas de mejorar el rendimiento. Una tecnología adecuada para esto se llama apilamiento de chips 3D. Esta es una arquitectura de pila tridimensional de chips, en cuyo desarrollo Intel es el líder. Hace dos meses, Intel presentó la arquitectura

3D de Foveros : una estructura tridimensional, que incluye una tecnología de proceso de 10 nm, un chip de E / S y conexiones eléctricas verticales TSV (Through Silicon Via) en el centro del chip, y un chip de memoria en la parte superior del chip completo.

En la conferencia de computación de alto rendimiento Rice Oil and Gas HPC, AMD

aseguró que estaba trabajando en su propia versión de la arquitectura de chips 3D.

Forrest Norrod, vicepresidente senior y gerente general, dijo que la compañía está desarrollando varias tecnologías para aumentar los retornos y evitar los problemas asociados con la terminación de la Ley de Moore y las consecuencias de detener el crecimiento de la densidad del transistor y la frecuencia de reloj. Estas son consecuencias inevitables de los fabricantes que se acercan al límite donde el tamaño del transistor es de solo unos pocos átomos (el tamaño de un átomo de silicio es de 0.2 nanómetros). El crecimiento de la potencia de la computadora en los últimos años no se debe tanto a un aumento en la velocidad informática, sino a un aumento en el paralelismo.

Al igual que otras compañías, AMD ha enfrentado una limitación en el área del chip de aproximadamente 700 mm² y se ve obligado a desarrollar una arquitectura 3D. La compañía ya está adoptando este enfoque, colocando la memoria HBM2 al lado del sustrato GPU, es decir, está en el mismo caso que el procesador. Pero en el futuro, la compañía planea pasar a un apilamiento 3D más avanzado.

Norrod dijo que AMD está trabajando en colocar SRAM y DRAM directamente sobre los componentes informáticos (como procesadores y GPU) para proporcionar aún más ancho de banda y rendimiento.

Samsung Polaris

Samsung PolarisEste enfoque difiere de las implementaciones habituales de paquete a paquete (PoP), que simplemente colocan dos casos terminados uno encima del otro, como lo demostró Norrod usando el chip Samsung Polaris como ejemplo. En este ejemplo, el gabinete DRAM está conectado a través de dos filas adicionales de conectores BGA que rodean el chip base. Estos conectores BGA transfieren datos entre dos chips. Al igual que con cualquier diseño estándar, la lógica está en la parte inferior de la pila debido a la necesidad de más conectores, pero los dos cristales no están conectados directamente. Por lo tanto, el enfoque de PoP proporciona la máxima densidad, pero esta no es la opción más rápida.

En el verdadero apilamiento 3D, dos chips (en este caso, memoria y procesador) están ubicados uno encima del otro y conectados por conexiones TSV verticales que los conectan directamente. Estas conexiones TSV transfieren datos entre los cristales a la velocidad más alta posible y generalmente se encuentran en el centro del chip, como vimos con Intel Foveros 3D. Este emparejamiento directo mejora el rendimiento y reduce el consumo de energía (todo el movimiento de datos requiere energía, pero las conexiones directas optimizan el proceso). El apilamiento 3D también aumenta la densidad.

Norrod no entró en detalles sobre los proyectos en desarrollo, pero esto puede resultar ser un cambio fundamental en el diseño del procesador AMD.

La nueva tecnología 3D Intel Foveros puede ser un momento decisivo para la industria, por lo que no es sorprendente escuchar que AMD se está moviendo en esta dirección,

escribe Tom's Hardware .

Hasta el momento, no hay detalles técnicos sobre la tecnología de apilamiento 3D de AMD, aparte de lo que Forrest Norrod dijo en una presentación titulada Working Beyond Moore's Law, vea el video a continuación.

¿Qué otras alternativas hay para volver a la curva de crecimiento exponencial predicha por Gordon Moore? No hay una respuesta única para esta pregunta. La industria de los semiconductores está experimentando con materiales que pueden usarse en lugar de silicio. Algunos materiales semiconductores III-V pueden operar

a voltajes más bajos y a frecuencias más altas que el silicio , pero no hacen que los átomos sean más pequeños o más lentos. Todavía se aplican restricciones físicas.

La pregunta sigue siendo cómo se enfriarán los futuros chips 3D. ¿Cómo enfriar efectivamente tal chip cuando la energía se distribuye a través de él? El microcircuito no podrá transferir energía a todos los circuitos simultáneamente sin sobrecalentamiento. Probablemente tendrá que mantener algunas partes desconectadas la mayor parte del tiempo y suministrar energía a cada parte solo durante el uso.