La Fundación Linux ha abierto una nueva dirección: la Alianza CHIPS. En el marco de este proyecto, la organización desarrollará un sistema de instrucción RISC-V y tecnologías gratuitas para crear procesadores basados en él. Le diremos con más detalle lo que está sucediendo en esta área.

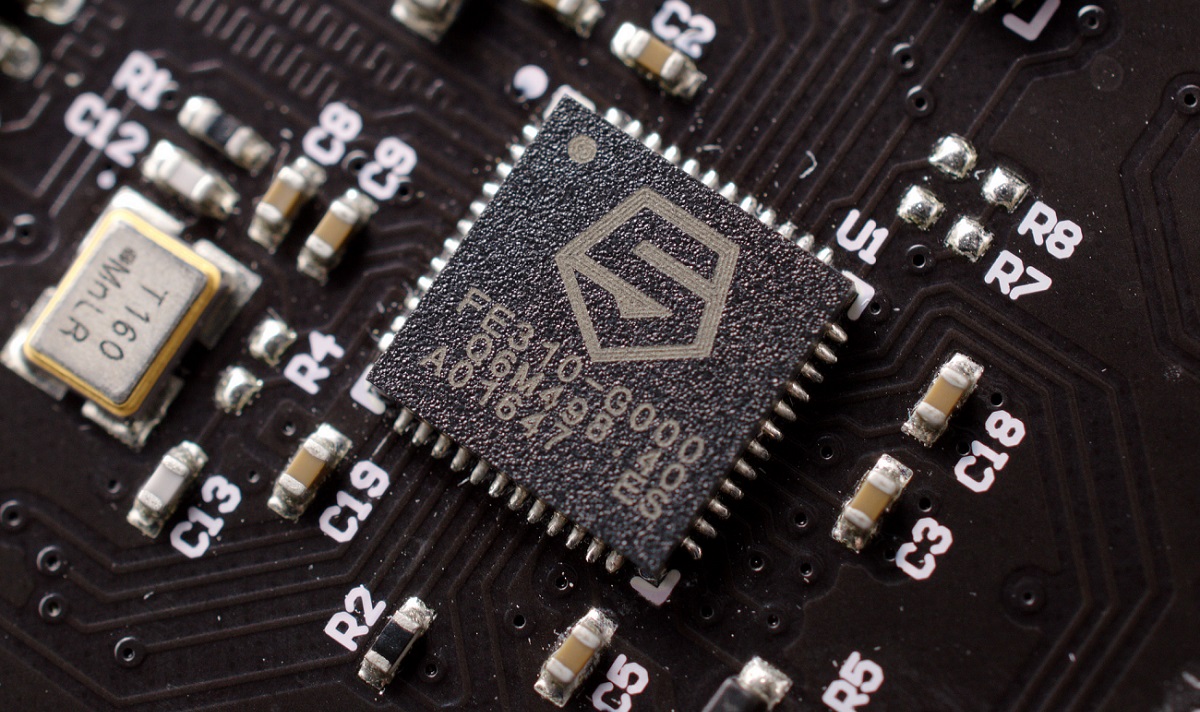

/ foto Gareth Halfacree CC BY-SA

/ foto Gareth Halfacree CC BY-SA¿Por qué apareció la Alianza CHIPS?

Los parches que protegen contra Meltdown y Spectre, en algunos casos,

reducen el rendimiento del servidor en un 50%. Al mismo tiempo, todavía aparecen nuevas variaciones de vulnerabilidades asociadas con la ejecución especulativa de comandos. Uno de ellos se

dio a conocer a principios de marzo : los expertos en seguridad de la información lo llamaron Spoiler. Esta situación afecta la

discusión sobre la necesidad de revisar las soluciones de hardware existentes y los enfoques para su desarrollo. En particular, Intel

ya está

preparando una nueva arquitectura para sus procesadores, no afectados por Meltdown y Spectre.

No se hicieron a un lado en la Fundación Linux. La organización lanzó su propia iniciativa, la Alianza CHIPS, cuyos miembros participarán en el desarrollo de procesadores basados en RISC-V.

Qué proyectos ya se están desarrollando

La lista de miembros de CHIPS Alliance incluye Google, Western Digital (WD) y SiFive. Cada uno de ellos presentó sus propios desarrollos. Hablemos de algunos de ellos.

RISCV-DV

El gigante de TI de búsqueda se transfirió a la plataforma de código abierto para probar procesadores basados en RISC-V. La solución

genera aleatoriamente comandos que le

permiten verificar la operatividad del dispositivo: probar procesos de transición, pilas de llamadas, registros

CSR , etc.

Por ejemplo,

aquí hay una clase que se encarga de realizar una prueba simple de instrucciones aritméticas:

class riscv_arithmetic_basic_test extends riscv_instr_base_test; `uvm_component_utils(riscv_arithmetic_basic_test) `uvm_component_new virtual function void randomize_cfg(); cfg.instr_cnt = 10000; cfg.num_of_sub_program = 0; cfg.no_fence = 1; cfg.no_data_page = 1'b1; cfg.no_branch_jump = 1'b1; `DV_CHECK_RANDOMIZE_WITH_FATAL(cfg, init_privileged_mode == MACHINE_MODE; max_nested_loop == 0;) `uvm_info(`gfn, $sformatf("riscv_instr_gen_config is randomized:\n%0s", cfg.sprint()), UVM_LOW) endfunction endclass

Según

los desarrolladores, la plataforma difiere de los análogos en que le permite verificar constantemente todos los componentes del chip, incluido el bloque de memoria.

Protocolo OmniXtend

Este es un protocolo de red de WD que proporciona coherencia de caché al transferir datos a través de Ethernet.

OmniXtend le permite intercambiar mensajes directamente con el caché del procesador y se utiliza para conectar varios aceleradores: GPU o FPGA. También es adecuado para crear sistemas basados en varios chips RISC-V.

El protocolo ya es compatible con

chips SweRV centrados en el procesamiento de datos en centros de datos. SweRV es un procesador superescalar de doble tubería de 32 bits basado en una tecnología de proceso de 28 nanómetros. Cada canalización tiene nueve niveles, lo que permite cargar y ejecutar varios comandos simultáneamente. El dispositivo funciona a una frecuencia de 1.8 GHz.

Generador de chips de cohete

Una solución de SiFive, que fue fundada por los desarrolladores de la tecnología RISC-V.

Rocket Chip es un generador de núcleo de procesador RISC-V en Chisel. Es

una colección de bibliotecas parametrizadas que se utilizan para crear

SoC .

En cuanto a

Chisel , este es un lenguaje de descripción de hardware basado en Scala. Genera código de bajo nivel en Verilog, que

es adecuado para procesar en ASIC y FPGA. Por lo tanto, permite el uso de principios OOP en el desarrollo de

RTL .

Perspectivas de la Alianza

Los expertos dicen que la iniciativa de la Fundación Linux hará que el mercado de procesadores sea más democrático y esté abierto a nuevos jugadores. IDC

señala que la creciente popularidad de tales proyectos tendrá un efecto positivo en el desarrollo de tecnologías de aprendizaje automático y sistemas de inteligencia artificial en general.

/ foto Fritzchens Fritz PD

/ foto Fritzchens Fritz PDEl desarrollo de procesadores de código abierto también reducirá el costo de diseñar chips personalizados. Sin embargo, esto solo sucederá si la comunidad de la Fundación Linux logra atraer suficientes desarrolladores.

Proyectos similares

Otras organizaciones están desarrollando proyectos relacionados con hardware abierto. Un ejemplo sería el consorcio CXL, que introdujo el estándar Compute Express Link a mediados de marzo. La tecnología es un análogo de OmniXtend y también conecta CPU, GPU, FPGA. Para el intercambio de datos, el estándar utiliza el bus PCIe 5.0.

Otro proyecto involucrado en el desarrollo de tecnologías de procesador es MIPS Open, que apareció en diciembre de 2018. La iniciativa fue creada por la startup Wave Computing. Los desarrolladores planean

abrir los últimos conjuntos de instrucciones MIPS de 32 y 64 bits a la comunidad de TI. El inicio del proyecto

se espera en los próximos meses.

En general, el enfoque de código abierto se está volviendo generalmente aceptado no solo para el software, sino también para el hardware. Dichos proyectos son apoyados por grandes empresas. Por lo tanto, podemos esperar que en el futuro cercano aparezcan más dispositivos en el mercado, que se basan en estándares de hardware abiertos.

Nuevas publicaciones de nuestro blog corporativo:

Publicaciones de nuestro canal de Telegram: