¿Qué pasa si nunca se inventaron TFT? LCD de matriz CSTN

Entrada

Cuando prevalecieron los monitores CRT, se presentó el siguiente argumento a su favor: a pesar de todas las mejoras, las pantallas LCD nunca superarán las pantallas de tubo en calidad de imagen. Ellos, como antes, encontrarán aplicación solo donde se requiera eficiencia energética y pequeño espesor [1]. Han pasado décadas, y ahora sabemos si los partidarios de este argumento tenían razón. Pero hoy es interesante mirar las pantallas LCD de esa época: ¿son realmente tan de baja calidad? ¿Cómo es mirar la matriz CSTN en 2019?

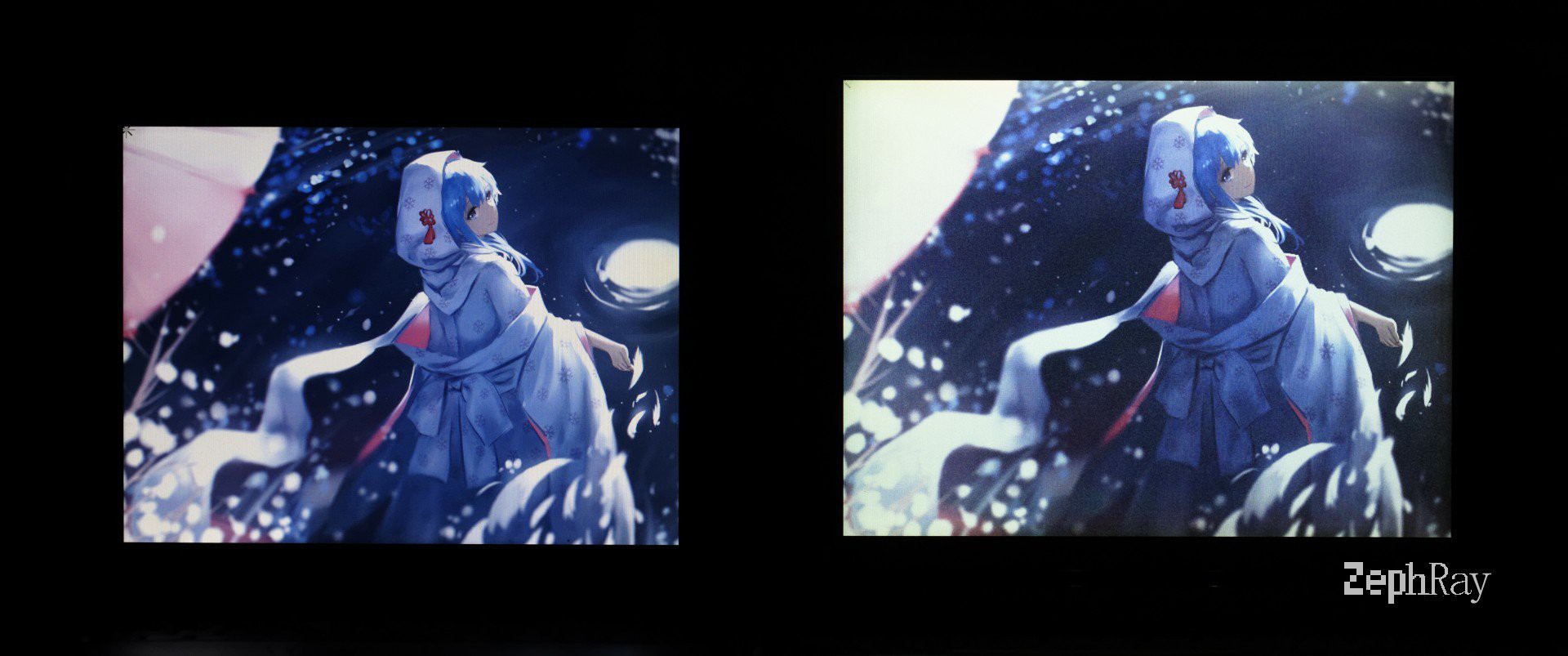

TFT izquierda, CSTN derecha, ambas pantallas de los noventa

TFT izquierda, CSTN derecha, ambas pantallas de los noventaLCD en el siglo pasado

Antes de cambiar a TFT, se utilizaron una variedad de tecnologías de visualización en las computadoras portátiles. Al principio, usaron los mismos monitores CRT que en las computadoras de escritorio, solo que los más pequeños. Por ejemplo, en Compaq Portable (1983), IBM 5155 (1984) o Commodore SX-64 (también 1984).

IBM 5155, autor: Soupmeister, con licencia: CC-BY-SA-2.0, desde aquí

IBM 5155, autor: Soupmeister, con licencia: CC-BY-SA-2.0, desde aquíLlevar una PC con usted a todas partes fue difícil, una cosa completamente diferente: una computadora portátil con una TN-LCD (giro nemático), por ejemplo, IBM 5140 (1986), Toshiba T1000 (1987). Estas pantallas tienen bajo contraste y ángulo de visión.

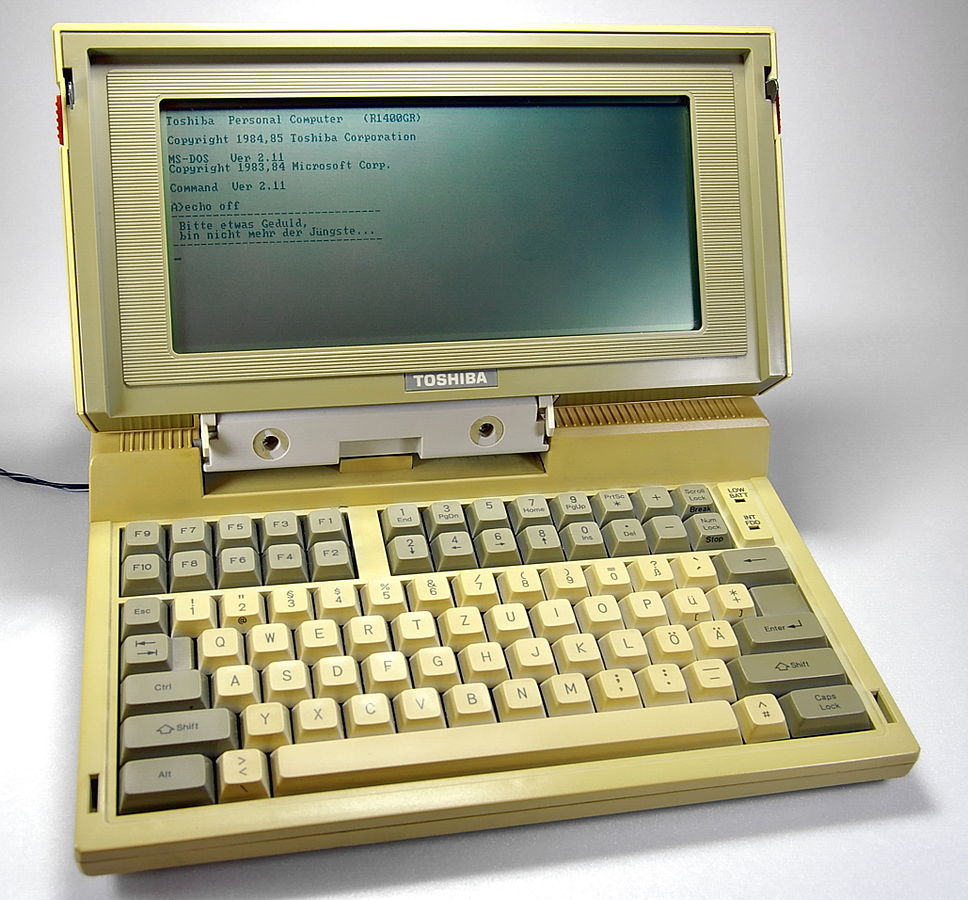

Toshiba T1100 con pantalla TN monocroma, autor: Johann H. Addicks, licencia: GFDL, por lo tanto , el enlace está roto, también en el original

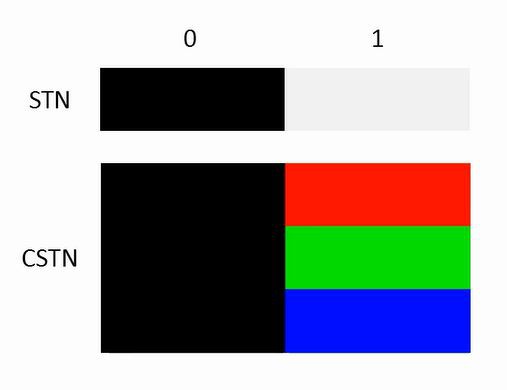

Toshiba T1100 con pantalla TN monocroma, autor: Johann H. Addicks, licencia: GFDL, por lo tanto , el enlace está roto, también en el originalAlgunos fabricantes experimentaron con matrices de descarga de gas, ya que Toshiba T3200 (1987) e IBM PS / 2 P70 (1991) vieron la luz del día. Proporcionaron un alto contraste y varias gradaciones de brillo de luz rojo-naranja, pero eran bastante caros. Finalmente, se desarrollaron STN-LCD (supertwist nematic), como, por ejemplo, en Electronics MC1504 y su prototipo Toshiba T1100. El contraste fue mucho mejor: de 1: 5 a 1:50, y varias gradaciones de brillo fueron suficientes para las aplicaciones comerciales (usar una computadora portátil en la vida cotidiana todavía era demasiado costoso). Pero, ¿qué pasa si el usuario quiere una imagen en color? En este caso, le ofrecieron dos tecnologías: TFT y CSTN (supertwist de color nematic). La primera computadora portátil con TFT - NEC PC9801NC - se introdujo en 1990, la calidad de imagen para esos años fue sobre todo elogio, pero costó "tal juguete" es mucho más caro que otras computadoras portátiles costosas. Bueno, una pantalla CSTN es solo una pantalla STN, en la que se superpone un filtro. Durante mucho tiempo, las computadoras portátiles usaron matrices de ambos tipos. Y en el metro de Nueva York, los monitores CSTN aún funcionan.

Uno de ellos, fuente: Transit + PLUS

Uno de ellos, fuente: Transit + PLUSCstron

El autor quería mirar la pantalla CSTN. Como? Para empezar, solo compre una computadora portátil vieja y úsela. Resultó ser un procesador AMD 5x86-P133. Es decir, lo más dinámico que puedes ejecutar son los juegos de DOS (bueno, MPEG1 extraerá QV - traductor en el programa). Por supuesto, jugarlos es genial, pero quería ver cómo se ve YouTube, por ejemplo, o un juego moderno en esa pantalla, pero esto es imposible.

O?

En general, debe agregarle de alguna manera una entrada VGA o HDMI, y puede enviar una señal desde algo moderno. Las pantallas TFT de las computadoras portátiles se vuelven a convertir en monitores con bastante frecuencia. Simplemente compre un tablero que coincida con la matriz, y ya está. Y puede hacer su propio prefijo en el FPGA, que convierte una señal VGA o HDMI en un flujo de datos de píxeles.

Érase una vez, también se produjeron placas para convertir matrices CSTN en monitores VGA, pero esto ya no se encuentra. Pero puede adaptar la placa de depuración para FPGA ML505 para esto.

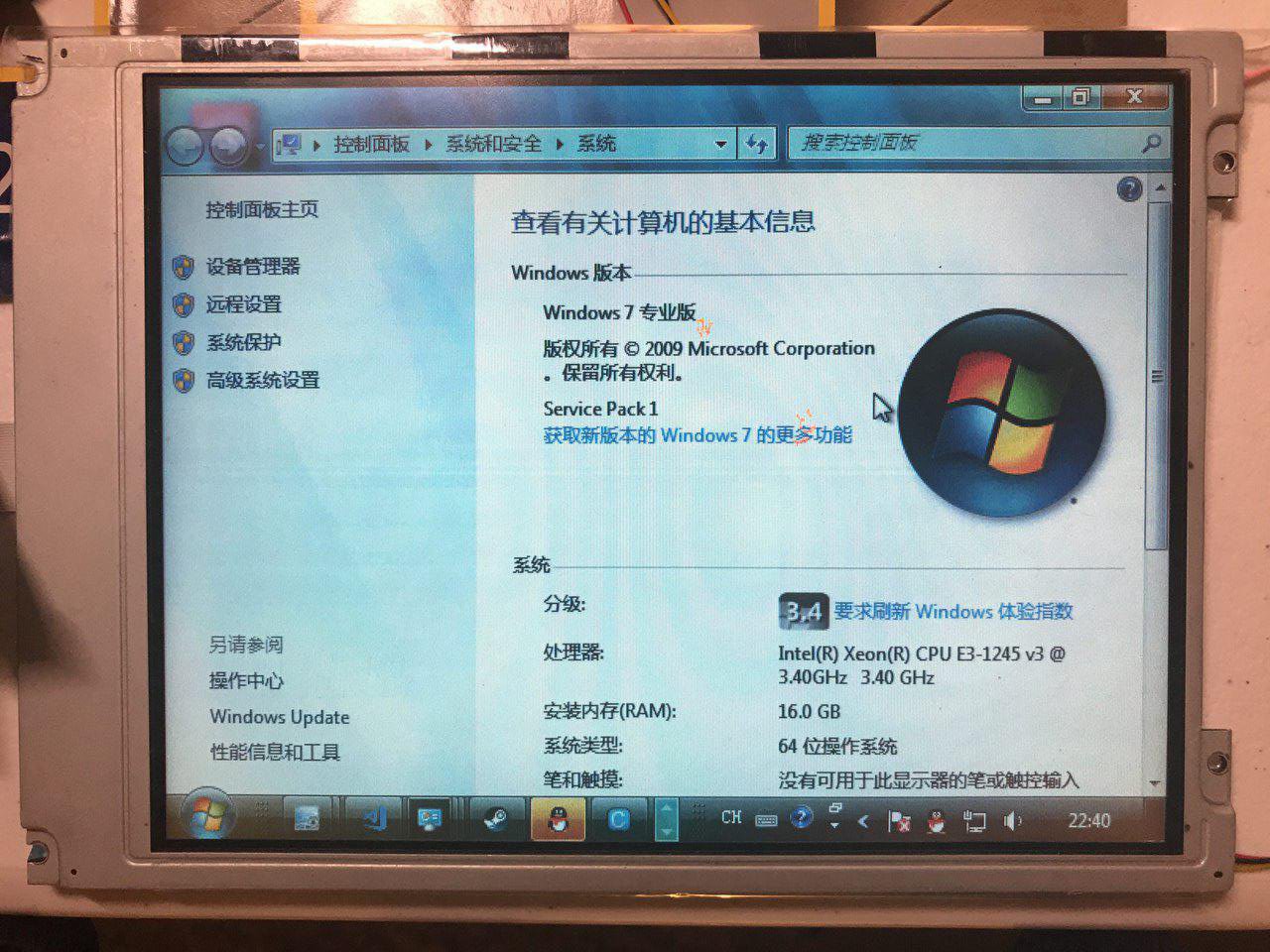

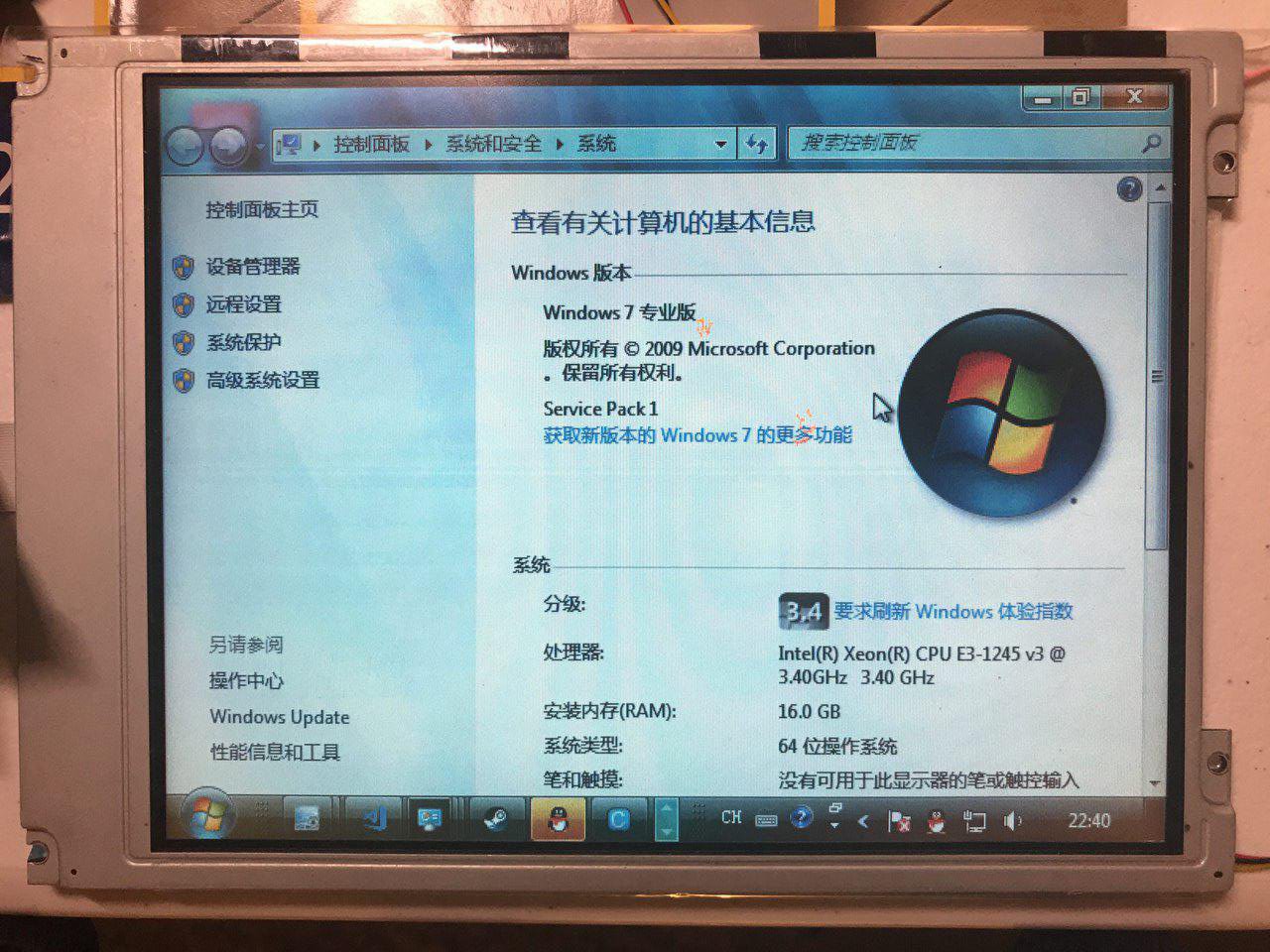

El resultado final. Es bastante inusual observar esto en una pantalla CSTN: 16 GB de RAM.

El resultado final. Es bastante inusual observar esto en una pantalla CSTN: 16 GB de RAM.Gestión de matrices

Comencemos con lo básico. Al igual que cualquier pantalla de matriz, la pantalla CSTN tiene filas y columnas. ¿Alguna vez has controlado una matriz LED desde un microcontrolador? Aquí es lo mismo, pero los voltajes son variables. Debe aplicar ciertas señales a las filas y columnas seleccionadas y no seleccionadas, y el píxel en la intersección de la fila y columna seleccionadas mostrará lo que necesita. La forma de las señales es muy compleja, el valor cuadrado medio del voltaje, el cambio de fase entre los voltajes en la fila y la columna, y el desplazamiento ... Y así, píxel por píxel, se forma una imagen.

Afortunadamente, no se requieren FPGA para generar todas estas señales, e incluso en una cantidad tan grande de líneas. Todo esto lo hace el módulo integrado en la pantalla. Allí, el convertidor de pulso aumenta el voltaje constante, pasa a través del divisor y el repetidor, por lo que se obtiene el voltaje de polarización. Los controladores de fila y columna convierten este voltaje en una variable de la forma requerida. Todo lo que se requiere es enviar una secuencia de datos de estado de píxeles al módulo de visualización.

En un TFT-LCD con una interfaz DPI (interfaz paralela digital), todos los datos sobre un píxel llegan de una vez en un ciclo. En la línea de sincronización horizontal y de trama, se reciben pulsos después de cada línea y trama, respectivamente. Los píxeles simplemente se transmiten continuamente línea por línea, cuadro por cuadro. Si la transmisión de fotograma completo tarda 1/60 s, la frecuencia de actualización es de 60 Hz. El ancho del bus de datos es igual a la profundidad de color en bits, generalmente 16 (5 bits para rojo y azul, 6 para verde), 18 (6 bits para cada color) o 24 (8 bits para cada color). LVDS es lo mismo, solo los bits no se transmiten en paralelo, sino secuencialmente en pares diferenciales, pero en MIPI DSI también se combinan en paquetes. El bus SPI / i80 le permite transmitir varios comandos al controlador y, al ejecutarlos, genera señales para DPI o una interfaz similar. Lo que, a su vez, recuerda un poco a VGA, solo los datos sobre el brillo de cada uno de los colores no se reciben en forma analógica, sino digital. Hay convertidores de VGA a DPI y viceversa. Las placas son muy convenientes, ya que le permiten recibir una señal VGA de la Raspberry Pi, aunque inicialmente esta computadora solo produce HDMI y video compuesto.

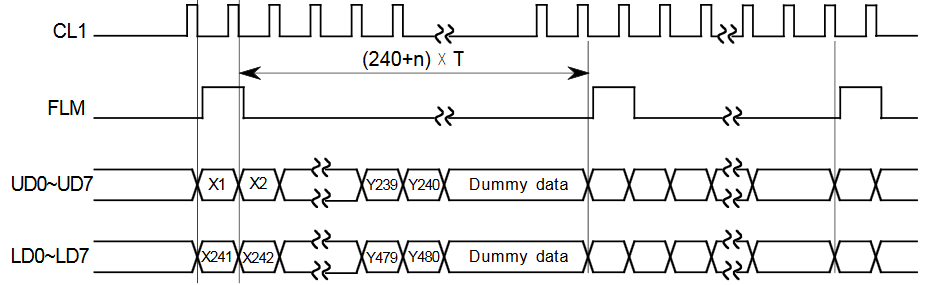

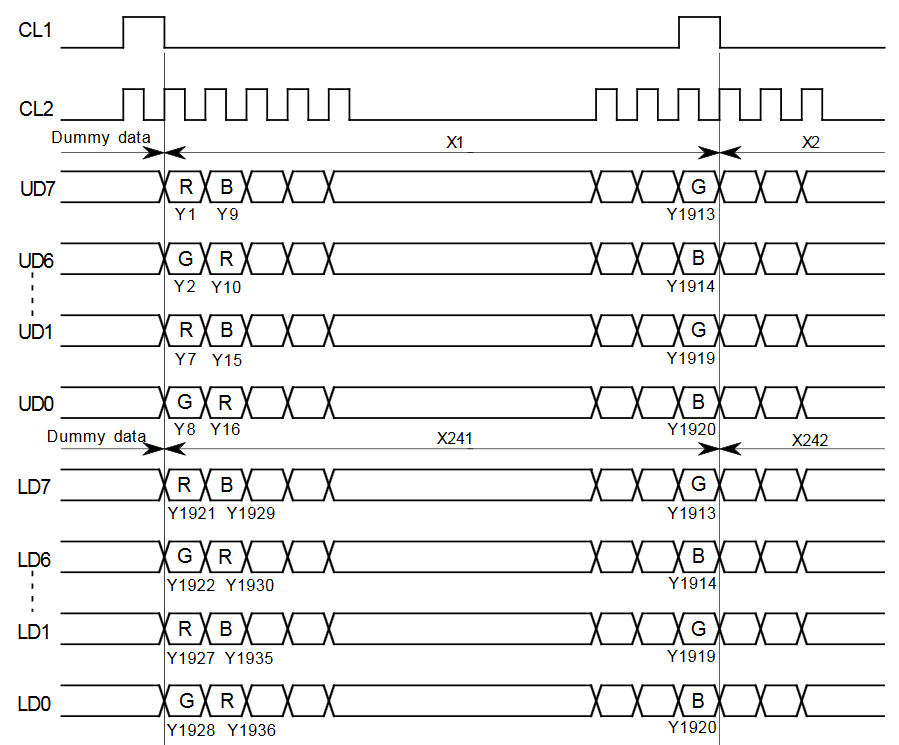

Las señales muy similares a las suministradas a una matriz TFT con una interfaz DPI se deben suministrar al módulo de visualización de la matriz CSTN. La hoja de datos del SX21V001 [2] muestra cómo controlar una pantalla CSTN con una resolución de 640x480:

Esto muestra la transferencia de todo el marco. La señal llega a la línea CL1 después de cada línea, a FLM después de cada trama. Y hay un bus de datos de 16 líneas. En realidad, se cometió un error en esta figura: durante la transmisión de las líneas primera y segunda, los datos Y1 e Y2, y no X1 y X2, sino Y140 e Y242, respectivamente, se reciben en las líneas UD0-UD7. Aquí U y L son, respectivamente, superior e inferior, es decir, la pantalla consta de dos matrices con una resolución de 640x240, ubicadas una encima de la otra. Aquí está, el misterioso "escaneo dual" de un viejo anuncio de computadora portátil, del cual proviene una franja horizontal en toda la pantalla. Para las pantallas STN y CSTN, el contraste es inversamente proporcional al número de líneas, por lo que esta separación permite aumentarlo. Pero esta no es la única forma en que difieren en la forma en que se controlan desde el TFT.

No está claro por qué el eje horizontal se llamaba Y ... En cualquier caso, CL2 aquí es una línea para suministrar pulsos de reloj que cambian píxeles. Pero en los buses UD y LD en un ciclo, no se transmiten datos sobre un píxel de múltiples bits, como en TFT, sino datos sobre varios píxeles a la vez, tres bits cada uno. Un bit por color, tres bits por píxel: ocho colores en total.

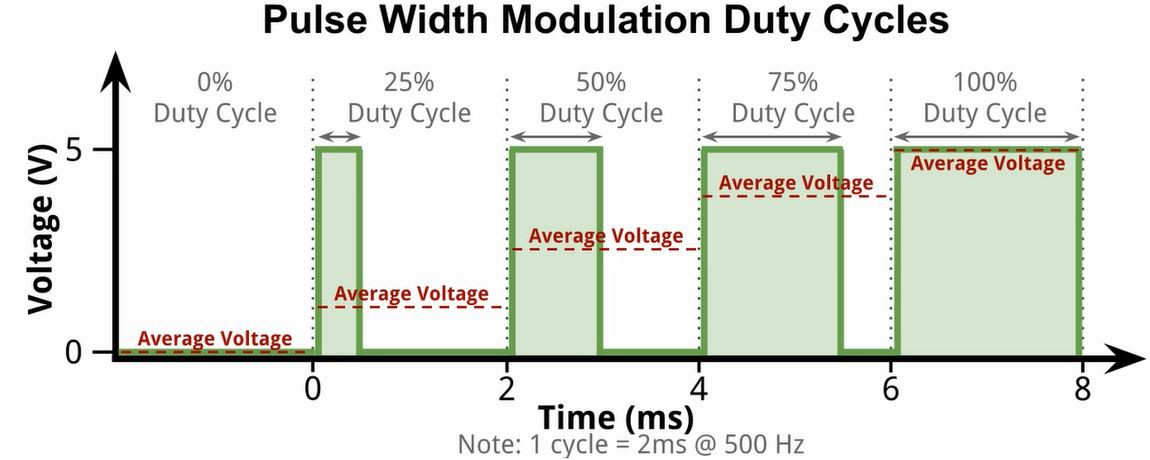

Pero como es eso? Está claro que las pantallas CSTN tienen pocos colores, por ejemplo, 4096 o 32768, pero no 8. Resulta que PWM se aplica aquí. Los LED se controlan de esta manera, lo que significa que los píxeles de LCD son posibles. Necesita, por ejemplo, un brillo del 50%: encienda el píxel en cuadros pares y apáguelo en cuadros impares. Este método se llama FRC (control de velocidad de cuadro), pero PWM en este contexto se llama control de brillo de píxeles de la misma manera, pero dentro de dos o más cuadros, pero uno. FRC implementa un dispositivo externo, y PWM implementa chips de módulos de pantalla, si hay soporte para esta función. El autor no conoce las pantallas CSTN con PWM, pero sugiere que estas son matrices de tipo HPA. En cualquier caso, dado que PWM no está disponible, se puede obtener la profundidad de color necesaria utilizando FRC.

El parpadeo será el precio de esto, por lo que se pueden encontrar velocidades de cuadro monstruosas (en comparación con TFT) en las pantallas CSTN. Por ejemplo, este módulo inicialmente tenía 120 Hz, y el autor lo aceleró a 240.

Cómo se implementó

El desarrollador enfrentó varias dificultades a la vez:

- la señal de entrada tiene una velocidad de cuadro de 60 Hz, debe duplicarse o incluso cuadruplicarse

- en la señal de entrada, el cuadro no se divide en mitades superior e inferior de 640x240 píxeles cada una, pero aquí es necesario dividir

- también necesita implementar FRC, de lo contrario la profundidad de color será de 3 bits por píxel

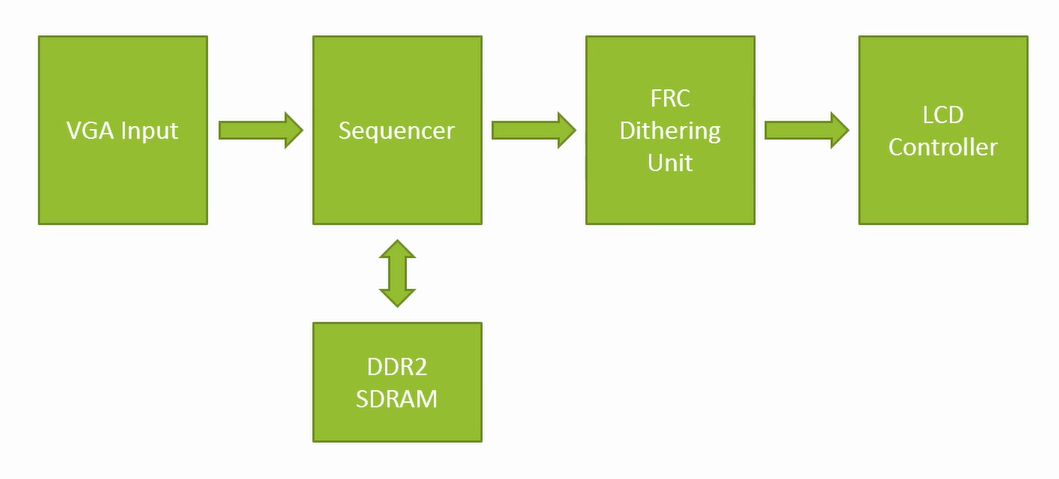

Los primeros dos puntos significan que se necesita un framebuffer, y no uno simple, sino uno de dos puertos. Bueno, la tercera tarea se resuelve utilizando GLDP LUT (tabla de búsqueda de patrones de visualización en escala de grises) [3]. La tabla de búsqueda tiene dos tipos de datos de entrada: el color que se mostrará y el estado del contador de cuadros. Y un tipo de salida: esos tres bits que deben enviarse a los subpíxeles de un píxel dado en un momento dado. Por lo tanto, se requerirán los siguientes nodos:

Lo primero que debe hacer es llenar toda la pantalla con algo de color. En esta etapa, no es necesario saber dónde se encuentra el píxel, es suficiente para asegurarse de que el módulo de visualización entregue las señales de forma necesarias a la matriz. El código para completar el FPGA está

aquí .

Ahora intenta sacar algo y con un brillo incompleto también. Buscando tablas de búsqueda de FRC para minimizar el parpadeo. Al autor se le ocurrieron dos tablas aplicadas a píxeles en un patrón de tablero de ajedrez. Por lo tanto, cada dos píxeles vecinos parpadean de forma asincrónica. El codigo esta

aqui .

Entonces, ya hemos "enseñado" al tablero a mostrar la imagen, lo siguiente que se requerirá es un framebuffer. Con 640x480 y 5 bits para cada uno de los colores, su volumen será de unos 600 kilobytes. No mucho, pero muchos en FPGA. Bueno, la placa tiene RAM como DDR2 y Xilinx MIG para controlarlo. Se implementan dos FIFO, uno para lectura y otro para escritura. El árbitro decide si el próximo intercambio de datos con DDR2 es de lectura o escritura. Hay dos buffers, el registro va a uno, se lee del otro, y cuando cambian los marcos, cambian de lugar. El código del árbitro está

aquí .

Queda por implementar la captura de video, en uno de los proyectos anteriores, el autor ya tiene un tiempo de funcionamiento similar, después del refinamiento, el código para el convertidor de VGA a DPI se ha vuelto

así .

Y que paso

Míralo!

Este es el tercer proyecto FPGA para el autor, fue interesante trabajar con Xilinx MIG y DDR2, así como con un transportador simple. Se planea un mejor FRC con modulación delta sigma, así como experimentos con paneles CSTN posteriores utilizando la tecnología HPA (direccionamiento de alto rendimiento) de Sharp.

Gracias por su atencion!

Fuentes

1. Li, W. y Guo, Q. (2000). Tecnología de aplicación de pantalla de cristal líquido. Beijing: prensa de la industria eléctrica.

2. HITACHI (1999). SX21V001-Z4 Especificaciones de aceptación del cliente.

3. Hsueh, Y. y Lee, J. (2008). Método de mejora de imagen para el controlador de velocidad de fotogramas LCD. Simposio internacional IEEE 2008 sobre electrónica de consumo. doi: 10.1109 / isce.2008.4559534