El otro día, la

estación automática japonesa Hayabusa-2 arrojó una bomba sobre el asteroide Ryugu . La nave espacial está controlada por un sistema estable a la radiación basado en un chip HR5000 (JAXA2010 / 101) con un núcleo de procesador MIPS 5Kf de 64 bits. La computadora de a bordo ejecuta el sistema operativo en tiempo real uITRON, uno de la familia RTOS estándar de TRON, que apareció en Japón en la década de 1980

y merece un puesto por separado .

En esta nota, describiré brevemente lo que se incluye en el HR5000 SoC y su núcleo de procesador, mostraré fotos de dos de los desarrolladores clave de las líneas MIPS 4K y 5K, y también contaré cómo puedes jugar en casa en el FPGA con el "descendiente de un hermano menor" de esta computadora: El kernel MIPS microAptiv UP de 32 bits, cuyo código en el lenguaje de descripción de hardware Verilog se basó en MIPS 4KEc.

La agencia aeroespacial japonesa JAXA autorizó el núcleo del procesador MIPS 5Kf de MIPS Technologies, una empresa estadounidense. Esto sucedió en la década de 2000. El grupo que desarrolló este núcleo ha existido en varias configuraciones durante 40 años:

- Primero, en 1978-1984, MIPS fue un proyecto en Stanford, dirigido por John Hennessey. Tras el éxito de este proyecto, Hennessey se convirtió en el autor del libro de texto más famoso sobre arquitectura de computadoras y, en algún momento, el presidente de Stanford.

- Luego, en 1984, MIPS se convirtió en una empresa comercial: MIPS Computer Systems. En el mismo año, ARM también se comercializó. En 1991, MIPS lanzó el primer microprocesador de 64 bits del mundo: MIPS R4000.

- Después de eso, MIPS fue absorbido por Silicon Graphics y en la década de 1990 se usó dentro de estaciones gráficas donde se hicieron las primeras películas con gráficos realistas en Hollywood (Jurassic Park).

- En la década de 2000, el grupo se separó en Tecnologías MIPS y, en particular, diseñó un procesador para JAXA. MIPS tenía su sede en California; algunos de los desarrolladores de MIPS 5Kf estaban ubicados en MIPS Europe en Copenhague.

- En 2012, MIPS Technologies fue comprada por la compañía británica Imagination Technologies, que se hizo famosa como desarrollador de GPU dentro del primer iPhone de Apple.

- En 2017, Apple lanzó Imagination, y después de algunas perturbaciones, la tecnología y parte del grupo MIPS se integraron en Wave Computing, una startup que desarrolla un chip para acelerar las redes neuronales.

- El chip Wave Computing es una combinación de un grupo de procesadores MIPS I6500 de 64 bits, un multiplicador de matriz basado en una matriz sistólica a la Google TPU y un procesador de procesador de datos basado en un dispositivo con una arquitectura reconfigurable de grano grueso - CGRA ) Los procesadores clásicos en el clúster I6500 cargan el multiplicador de matriz y el procesador de flujo de datos, el multiplicador de matriz proporciona densidad computacional y el procesador de datos de tareas se encuentra en el medio entre los procesadores clásicos y el multiplicador de matriz: es más flexible que el multiplicador y más productivo que la CPU clásica.

Así que tomé una foto con uno de los dos desarrolladores clave de la línea MIPS 4K y 5K: Larry Hudepohl, Larry Huedepol (a la derecha con una camisa roja). Larry comenzó su carrera en Digital Equipment Corporation (DEC) como diseñador de procesadores para MicroVAX. Luego, Larry trabajó para una pequeña empresa, Cyrix, que a fines de la década de 1980 desafió a Intel e hizo un coprocesador FPU que era compatible con Intel 80387 y era un 50% más rápido. Luego, Larry diseñó chips MIPS en Silicon Graphics. Cuando MIPS Technologies se separó de Silicon Graphics, Larry y Ryan Quinter lanzaron juntos el primer producto MIPS independiente, MIPS 4K, que se convirtió en la columna vertebral de la línea que dominaba la electrónica doméstica de los años 2000 (reproductores de DVD, cámaras, televisores digitales). Luego, MIPS 5K voló al espacio: fue utilizado por la agencia espacial japonesa JAXA. Luego, Larry, como vicepresidente de ingeniería de hardware, dirigió el desarrollo de las siguientes líneas, y ahora está trabajando en nuevas arquitecturas de acelerador Wave:

Ahora de vuelta al procesador en Hayabusa-2 (en Hayabusa-1 es diferente). Aquí hay una

hoja de datos para el núcleo del procesador MIPS64 5Kf y una

página con datos del sistema en un chip HR5000 . Tenga en cuenta algunos puntos interesantes.

En primer lugar, MIPS 5Kf es un procesador canalizado. Si no está familiarizado con cómo funciona esto, entonces la forma más fácil de conocerse es estudiar el séptimo capítulo del libro "Circuitos digitales y arquitectura de computadoras" de David M. Harris y Sarah L. Harris, cuya última versión se puede descargar al ruso

aquí o

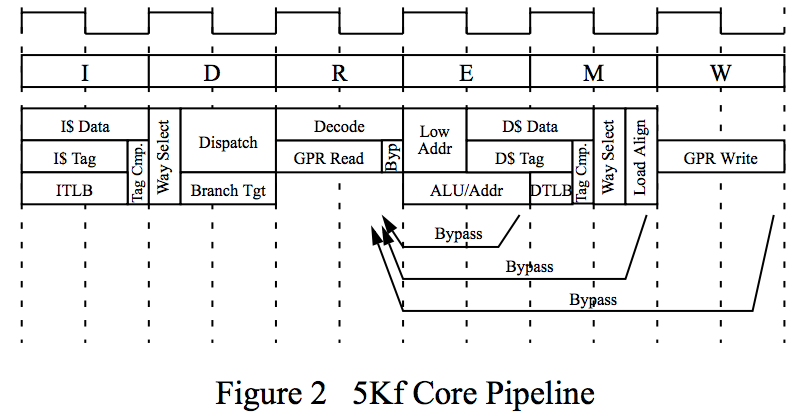

aquí ) . El transportador en MIPS 5Kf es diferente del transportador MIPS clásico de Harris & Harris. Aquellos de ustedes que han leído X&X pueden ver las diferencias y adivinar por qué:

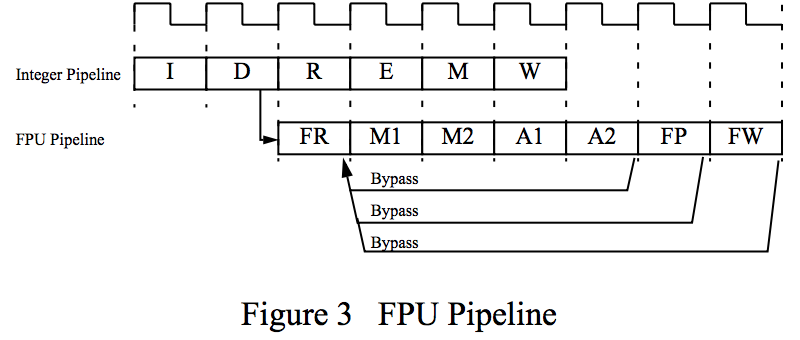

Por supuesto, MIPS 5Kf no tiene cinco etapas de canalización, sino seis, con una etapa de Despacho adicional. Esta etapa es necesaria para hacer que MIPS 5Kf sea superescalar. Puede realizar no solo operaciones una tras otra en la tubería, sino que también puede realizar una operación de punto flotante simultáneamente con una operación de enteros o con una operación de memoria (carga o guardado). Stage Dispatch lanza un coprocesador de coma flotante que tiene su propia tubería de siete etapas:

Y aquí a la derecha en la foto está Darren Jones, Darren Jones, desarrollador de FPU en MIPS 5Kf. La letra "f" en "5Kf" significa exactamente que tiene un punto flotante:

Aquí, en esta placa, puede ver cuántos ciclos requieren diferentes operaciones en la FPU y con qué frecuencia (frecuencia de repetición) se pueden ejecutar en la tubería. Por ejemplo, la multiplicación de precisión simple requiere cuatro ciclos, pero puede comenzar una nueva multiplicación en la tubería cada ciclo. Por lo tanto, la FPU puede procesar simultáneamente cuatro multiplicaciones de precisión individuales en cada etapa de procesamiento. Pero la multiplicación de doble precisión requiere cinco ciclos, y solo puede comenzar con una pausa en el ciclo. La compleja operación de sacar la raíz cuadrada de doble precisión requiere hasta 32 ciclos, y puede comenzar una nueva toma de la raíz cuadrada solo después de 29 ciclos. Así es como se optimiza el cálculo de las coordenadas de la nave y sus fórmulas de movimiento en el espacio exterior:

Hayabusa-2 usa la configuración MIPS 5Kf con instrucciones separadas de 32 kilobytes y cachés de datos. Al mismo tiempo, de la

breve descripción de HR5000 no queda claro si utiliza un caché de cuatro canales de 8 kilobytes, o un caché de dos canales de 16 kilobytes. Puede leer cómo funcionan estos cachés tanto en X&X como en

mi antigua presentación sobre cachés , así como en el útil libro

Ver MIPS Run Linux 2nd Edition de Dominic Sweetman:

Hayabusa-2 también tiene una Unidad de administración de memoria (MMU), con un búfer de traducción (TLB). TLB es una herramienta universal para convertir rápidamente direcciones de virtual a físico. TLB le permite:

Oculta la memoria del sistema operativo del código no privilegiado.

Proteja los programas de los usuarios entre sí.

Proporcione acceso al programa a la cantidad de memoria virtual que excede la cantidad de RAM física.

Dirección de memoria física más grande que las direcciones virtuales están disponibles.

Coloque el programa en cualquier parte de la memoria física.

Permite que varias regiones de memoria se vean como una pieza secuencial.

Le permite cargar partes del programa desde un dispositivo externo según sea necesario.

El TLB también asocia varios atributos con la dirección: lectura, escritura y ejecución, así como atributos de caché y coherencia.

El atributo de caché es necesario para mostrar al procesador dónde está el espacio de direcciones para el siguiente nivel de caché y dónde están las resistencias de E / S que no se pueden almacenar en caché.

Los atributos de coherencia son necesarios para que varios núcleos de procesador trabajen juntos, cada uno con su propio caché de primer nivel, y juntos usan un caché común de segundo nivel.

TLB puede almacenar un indicador de que se ha registrado una página con una dirección determinada. Esto ayuda al intercambiar, cargar y descargar páginas de memoria en sistemas con menos memoria física de la que la aplicación necesita para abordar todas las partes de su código y datos con direcciones virtuales.

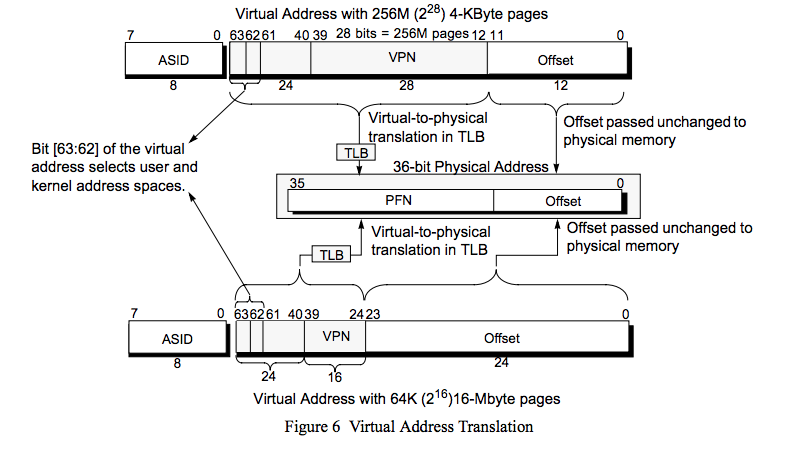

Así es como se ve la traducción de una dirección virtual de 64 bits a una dirección física de 36 bits en MIPS 5Kf. ¿Por qué en Hayabusa-2 un procesador de 64 bits con direcciones físicas de 36 bits? Sospecho que Hayabusa-2 toma fotografías y debe procesar imágenes, lo que requiere mucha memoria. Quizás para algunos algoritmos, la aritmética de 64 bits y los intercambios de caché de 64 bits (o los intercambios de memoria no almacenable en caché de 64 bits) mejoran algo, y resulta ser útil en el espacio. Pero no estoy seguro, probablemente deba preguntarle a

Zelenyikot y a la

amartología , que saben más sobre el espacio que yo.

Puede leer sobre TLB en X&X y Ver MIPS Run, pero hay un matiz: ambos libros describen cómo se ve TLB desde el punto de vista de un programador. Pero desde el punto de vista del desarrollador de hardware, los diseñadores del procesador están engañando al programador mostrándole el TLB como una tabla de traducción asociativa, a pesar del hecho de que en realidad hay tres tablas dentro del TL: hay tres instrucciones micro-TLB, datos micro-TLB y un común (TLB conjunto). Primero, el dispositivo de administración de memoria busca ITLB y DTLB, y solo si no lo encuentra, lo toma de JTLB. Esto le cuesta al procesador 2 ciclos adicionales. También vea

mi antigua presentación sobre TLB :

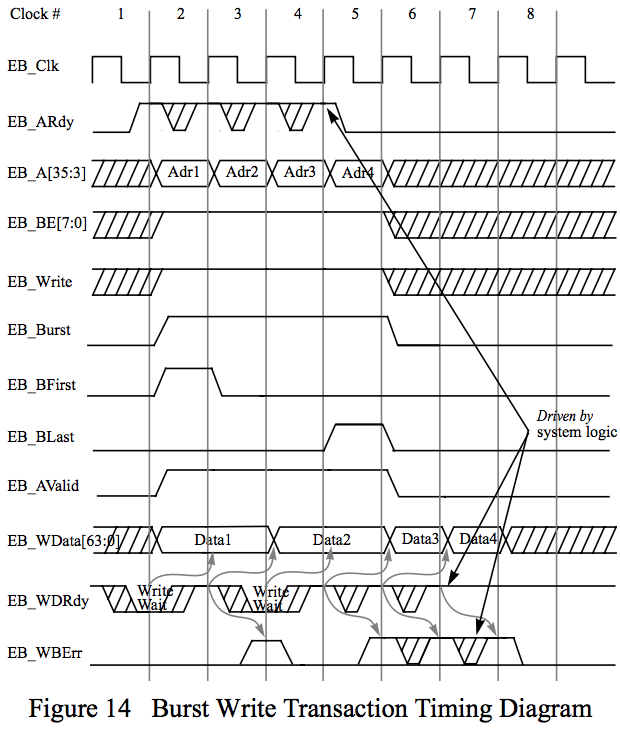

La interfaz entre los cachés de primer nivel y el controlador de memoria en MIPS 5Kf en Hayabusa-2 se llama EB (pronunciado IB). Esto es la abreviatura de bus externo. Es similar a AHB y AXI, y le permite explotar, volcar desde el caché o llenar el caché de la memoria en una línea completa, utilizando transferencias en bucles secuenciales.

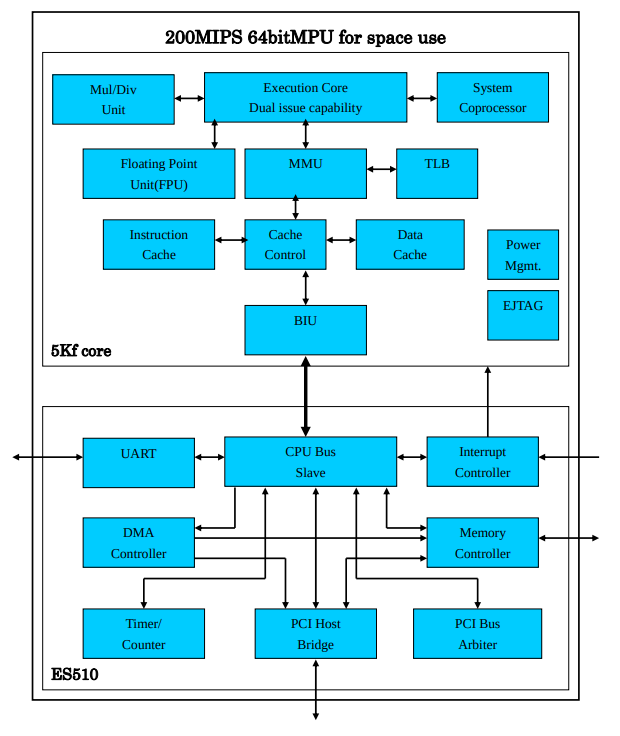

Fuera del núcleo del procesador, el HR5000 tiene un controlador de interrupción, un módulo UART, un controlador de acceso directo a memoria, temporizadores y un controlador PCI:

Para trabajar en el espacio, el chip debe protegerse de la radiación. No soy especialista en protección radiológica, para esto hay una

tecnología en Habré, pero sé que dicha protección se puede hacer tanto a nivel de tecnología de producción física como a nivel de varias comprobaciones de ECC, e incluso a nivel de arquitectura, con triplicación, etc. Los creadores del sistema de cristal HR5000 decidieron usar la ruta RTL2GDSII habitual adoptada en aplicaciones comerciales, síntesis de un gráfico a partir de elementos lógicos del código en el lenguaje de descripción de hardware Verilog. Sin embargo, después de recibir dicho gráfico (netlist), lo modifican utilizando una biblioteca especial de primitivas dureza por diseño (HBD) (nunca lo usó, por lo que cualquier aclaración en los comentarios es bienvenida):

Dado que MIPS 5Kf está escrito en Verilog, se puede convertir no solo en una lista de red, y no solo en una máscara para fabricar un chip en una fábrica, sino también en una configuración FPGA. Desafortunadamente, las fuentes de MIPS 5Kf no están en el dominio público, pero en el dominio público están el código fuente de un descendiente de su "hermano menor", un procesador MIPS 4K de 32 bits. Este "descendiente" se llama MIPS microAptiv UP, y su configuración básica está incluida en el paquete MIPSfpga. El código MIPS 4K / 4KEc / microAptiv UP / M5150 (todas estas son versiones progresivas de la línea) también fue escrito por Larry, Ryan y Darren.

Puede jugar con la tubería, cachés, dispositivo de administración de memoria e interrupciones del núcleo MIPS microAptiv UP, ejecutarlo en un simulador o placa con FPGA / FPGA. Para hacer esto, simplemente descargue el

paquete de inicio de FPGA MIPS Open ™ , junto con los

laboratorios de FPGA de MIPS Open ™ y (¡esto es importante!)

Compleméntelo con

MIPSfpga + . En este último hay

laboratorios sobre la tubería, el caché y el dispositivo de administración de memoria .

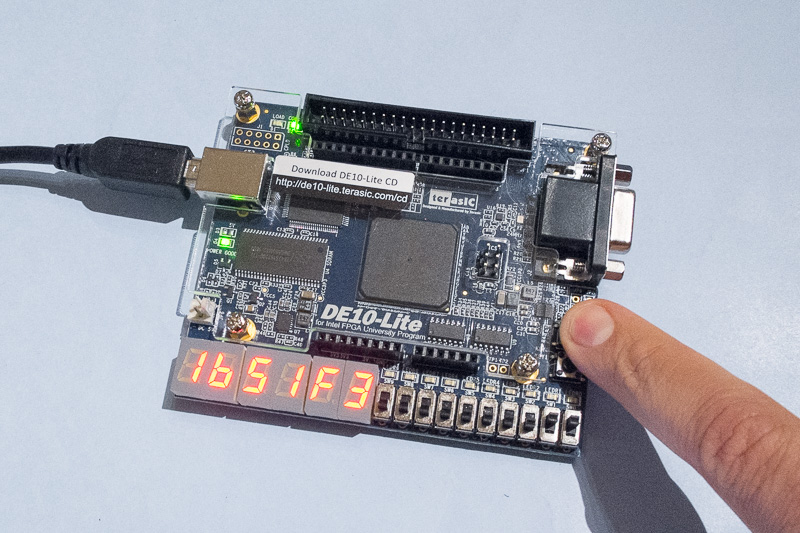

Puede sintetizar y ejecutar el procesador MIPS microAptiv UP en una placa económica por $ 85 (precio académico $ 55):

Para trabajar con el paquete MIPSfpga / MIPSfpga +, necesita conocer el lenguaje de descripción de hardware Verilog, los principios de diseño en el nivel de transferencia de registro y la capacidad de escribir en el ensamblador MIPS.

El ensamblador MIPS es el más fácil de aprender. Para hacer esto, puede

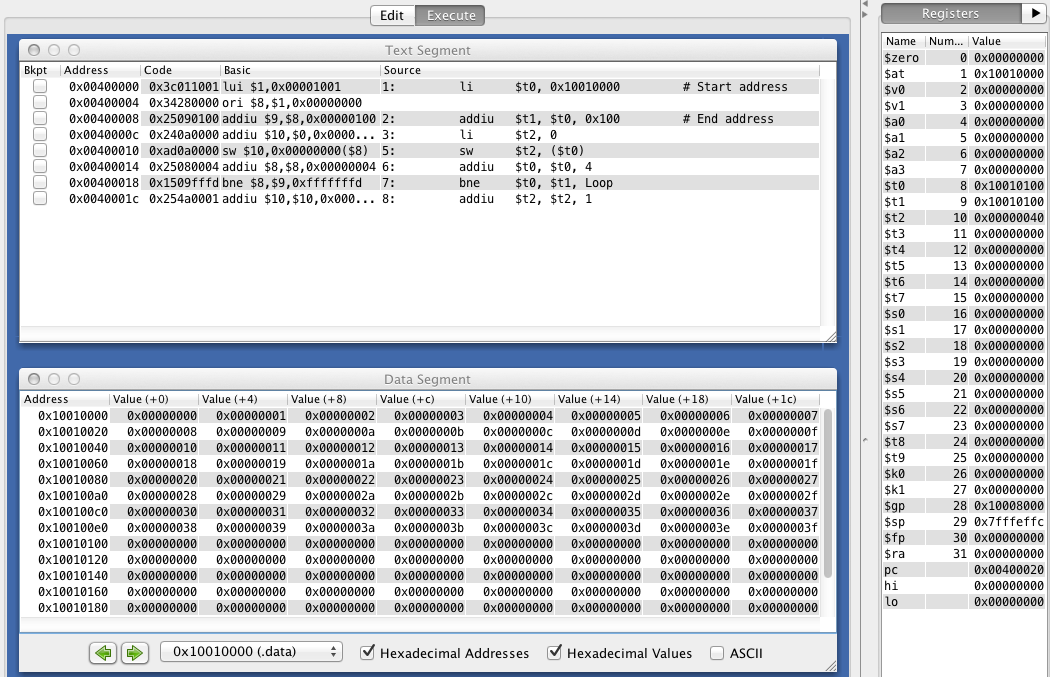

descargar el simulador MARS (MIPS Assembler y Runtime Simulator) . Puede aprender a usarlo en 5 minutos, de hecho, tiene tres botones: ensamblar, ejecutar, ejecutar paso a paso:

Luego puede pasar el día practicando la escritura en lenguaje ensamblador para los libros

Harris y Harris y

See MIPS Run Linux .

Si no sabe nada sobre el desarrollo de circuitos digitales en general y en el lenguaje para describir equipos en particular, puede comenzar con el curso en línea de Rosnanov para escolares, en tres partes:

"Del transistor al microcircuito" ,

"El lado lógico del circuito digital" ,

"El lado físico circuitos digitales " ). Luego puede estudiar Verilog en X&X y comprender que hay un procesador en el procesador simplificado

schoolMIPS .

Si está interesado en este tema y desea participar en el trabajo sobre

MIPS Open (dentro del marco del cual se abrió el núcleo MIPS microAptiv UP), escriba los comentarios. Rosnanovtsy también realizará un

seminario para escolares sobre diseño digital del 17 al 19 de abril , que incluirá, entre otras cosas, este procesador espacial. Hayabusa-2 bombardeó a Ryuga no en vano: esta es también una ocasión para que los escolares y estudiantes rusos descubran qué hay dentro de ella.