El siguiente capítulo de la documentación oficial de Cypress sobre administración de tiempo y reinicio. Como ya se mencionó en el primer artículo de esta serie, este módulo proporciona selección de tiempo y resolución, así como restablecer la selección dentro de UDB. Más detalles - debajo del corte.

El contenido general del ciclo “UDB. ¿Qué es esto?

Parte 1. Introducción. Pld.Parte 2. Ruta de datos.Parte 3. Datapath FIFO.Parte 4. Datapath ALU.Parte 5. Ruta de datos. Pequeñas cosas útiles.Parte 6. Módulo de gestión y estado.Parte 7. Módulo de control de temporización y reinicio. (Artículo actual)

Parte 8. Abordar UDB21.3.4 Reinicio y módulo de control de reloj

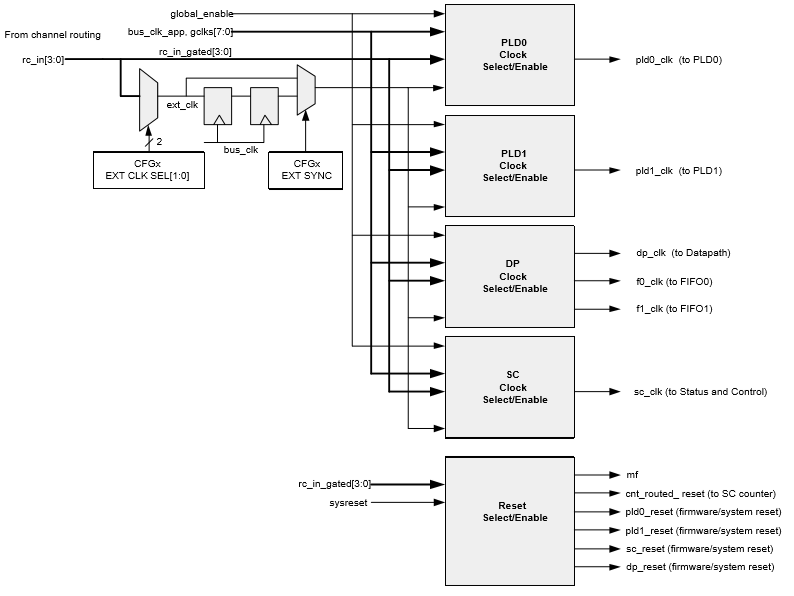

La función principal de este módulo es seleccionar relojes de los relojes globales disponibles o del reloj del bus para cada PLD, Datapath y módulo de control y estado. El módulo también admite reinicios dinámicos y de bloque UDB de software. Como se muestra en la Figura 21-38, hay cuatro unidades de control de reloj y una unidad de control de reinicio. Cuatro entradas (RC_IN [3: 0]) están disponibles para reenviar desde la matriz de rastreo global. Cada unidad de control de reloj puede seleccionar una fuente para la entrada de activación de reloj de estas entradas de rastreo, y también hay un multiplexor que le permite seleccionar una de las entradas de rastreo para usar como una fuente de reloj externa. Como puede ver en la figura, la elección de una fuente de reloj externa se puede sincronizar. Para cada componente UDB, hay 10 relojes para elegir: 8 relojes digitales globales, un reloj de bus y un reloj externo seleccionado (ext clk). Cualquiera de las señales de entrada rastreadas (rc_in) se puede usar como activador sensible al nivel o como activador sensible al borde. La función de reinicio de este bloque proporciona un reinicio rastreado de los bloques PLD y el contador SC, así como la capacidad de reiniciar mediante programación cada bloque para admitir la reconfiguración.

El reloj del bus aplicado al reloj y al módulo de control de reinicio es diferente del reloj del bus del sistema. Esta señal se llama "bus_clk_app" y se bloquea de la misma manera que otras señales de reloj digital. El reloj del bus del sistema se usa solo para operaciones de entrada-salida y se desbloquea automáticamente para cada acceso. El Datapath Clock Generator genera tres relojes: uno para Datapath y una señal para cada FIFO.

Figura 21-38. Reloj y módulo de control de reinicio.

21.3.4.1 Control de reloj

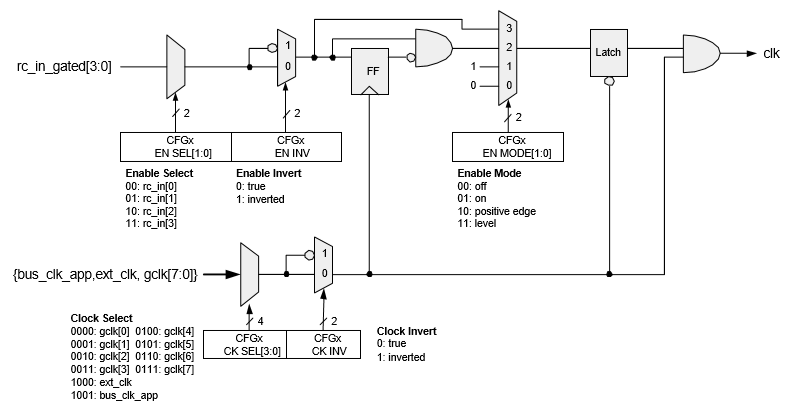

La figura 21-39 muestra un ejemplo de un esquema de selección y resolución de tiempos. Cada UDB tiene cuatro esquemas de este tipo: uno para cada bloque PLD, uno para Datapath y uno para el bloque de control y estado. Los componentes principales de este circuito son el multiplexor selector de reloj global, el inversor de reloj, el multiplexor de señal de habilitación de reloj, el inversor de señal de habilitación de reloj y la lógica de detección diferencial.

Figura 21-39. Gestionar la selección / activación del tiempo.

Selección de relojHay ocho relojes digitales globales enviados a todas las UDB. Cualquiera de ellos puede ser seleccionado. Los relojes digitales globales son salidas de divisores de frecuencia seleccionados por el usuario. Consulte "Sistema de sincronización" en la página 109 del original. Otra opción es el reloj del bus, que tiene la frecuencia más alta en el sistema. Esta señal se llama "bus_clk_app" y se rastrea por separado del reloj del bus del sistema. Además, para admitir funciones con una señal de reloj directa (por ejemplo, SPI), se puede seleccionar una línea de rastreo externa como señal de reloj de entrada. Como las funciones de la aplicación están vinculadas a límites arbitrarios dentro de la UDB, la selección de una señal de reloj individual para cada subcomponente de la UDB contribuye a una granularidad precisa en la programación.

Inversión de relojLa señal de reloj seleccionada se puede invertir. Esto limitará la frecuencia máxima de trabajo debido a la existencia de secciones con un ciclo de medio ciclo. La grabación simultánea de bus y las grabaciones internas (por ejemplo, el programa que registra un nuevo valor de contador durante su funcionamiento) no se admiten cuando el reloj interno está invertido y tiene la misma frecuencia que el reloj del bus. Esta limitación afecta a A0, A1, D0, D1, así como al registro de control en modo contador.

Selección de activación del relojLa señal de activación del reloj se puede reenviar a cualquier señal síncrona y seleccionarse en cualquiera de las cuatro entradas de la matriz de rastreo disponibles para este bloque.

Inversión de activación de relojLa señal de activación del reloj se puede invertir. Debido a esto, esta señal se puede generar en cualquier polaridad.

Modo de activación del relojPor defecto, el modo de resolución del reloj está apagado. Después de configurar el funcionamiento de la unidad de destino, el software puede configurar uno de los modos de funcionamiento descritos a continuación utilizando el registro MODO CFGxEN [1: 0], que se muestra en la Figura 21-39.

Cuadro 21-23. Modos de resolución de tiempo.

Uso de permiso de relojHay dos casos de uso comunes para los permisos de temporización.

Habilitación de software (habilitación de firmware) : se supone que la mayoría de las funciones requieren una habilitación de reloj de software para iniciar y detener la función. Dado que el límite de la función vinculada a la matriz UDB es condicional, la función puede abarcar varias UDB y / o partes de las UDB. Por lo tanto, se necesita una forma de incluir cada función atómicamente. Esto generalmente se implementa utilizando un bit en el registro de control reenviado a una o más entradas de activación de reloj. Este escenario también es compatible con el caso en que las aplicaciones necesitan ejecutar múltiples bloques no relacionados al mismo tiempo.

Generación de reloj local emulada: esta característica permite a los UDB generar relojes locales y distribuirlos a otros UDB en la matriz utilizando la plantilla de implementación de activación del reloj de sincronización, en lugar de marcar directamente cada UDB por separado. El uso de la función de borde positivo para habilitar la resolución elimina las restricciones en el ciclo de trabajo de la señal de resolución.

Tiempo especial de FIFOLos bloques FIFO Datapath tienen características de temporización. Por defecto, el reloj FIFO tiene la misma configuración que el reloj Datapath. Sin embargo, los bloques FIFO tienen bits de control especiales que cambian la configuración del reloj:

- cada reloj FIFO puede invertirse en relación con la polaridad del reloj Datapath seleccionado;

- cuando se selecciona el modo FIFO FAST, el reloj del bus reemplaza la elección del reloj Datapath que generalmente usa FIFO.

21.3.4.2 Restablecer administración

Hay dos modos de administración de reinicio: heredado y estándar. El modo se establece utilizando el bit

ALT RES en cada registro de configuración del UDB CFG31. Por defecto, el valor de bit es 0 (modo heredado); Se recomienda que le asigne un valor de 1 (modo estándar). El modo estándar tiene un mayor grado de granularidad: los bloques individuales dentro de UDB pueden usar descargas trazadas. Para obtener información sobre el modo heredado, comuníquese con Cypress.

Control de reinicio PLDLa figura 21-40 muestra el sistema de reinicio PLD.

Figura 21-40. Restablecer estructura PLD.Datapath Reset Control

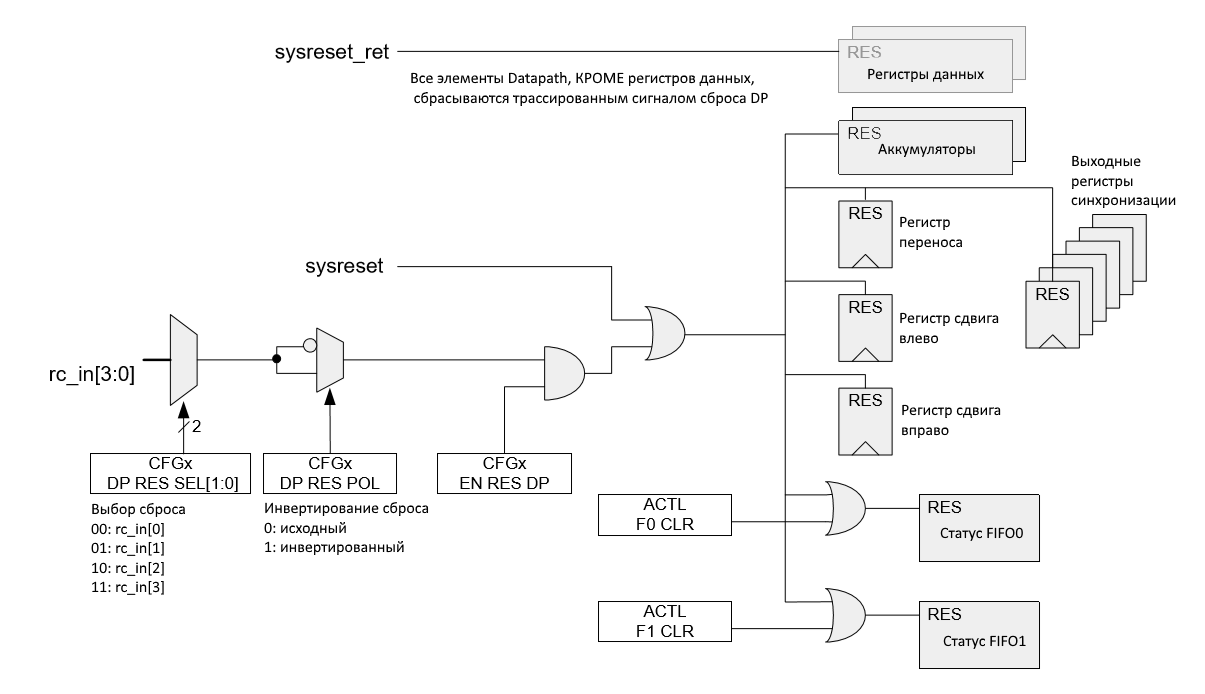

Figura 21-40. Restablecer estructura PLD.Datapath Reset ControlLa figura 21-41 muestra el sistema de restablecimiento de Datapath. La descarga rastreada se aplica a todos los registros y estados de Datapath, excepto los registros de datos D0 y D1. Los registros de datos son registros persistentes. El contenido del FIFO no se define después del reinicio, ya que se encuentra en la RAM.

Figura 21-41. Estructura de restablecimiento de ruta de datos.Control de reinicio de estado y control

Figura 21-41. Estructura de restablecimiento de ruta de datos.Control de reinicio de estado y controlLa Figura 21-42 muestra el sistema de control y restablecimiento de estado. Los registros de control / contador y estado tienen un restablecimiento de rastreo común, sin embargo, se habilitan por separado. Los registros de superposición de máscara / período y los controles auxiliares son registros de guardado.

Figura 21-42. Restablecer gestión y gestión de estado.

Figura 21-42. Restablecer gestión y gestión de estado.21.3.4.3 Encendido Inicialización UDB (POR)

Registro e inicialización del estadoTabla 21-24. Inicialización de estados UDB cuando está habilitado

Inicialización de rastreoCuando está habilitado, el estado de las entradas y salidas de rastreo tiene las siguientes características:

- todas las salidas UDB que dirigen datos a la matriz de rastreo se mantienen en '0';

- Todos los controladores que salen de la traza e ingresan a las entradas UDB se ponen a cero inicialmente.

Esta inicialización evita estados en conflicto durante el rastreo, y la configuración inicial ocurre en una secuencia en la que el orden no importa.

El final sigue. Estamos preparando la

última traducción de la sección restante de la documentación patentada de Cypress sobre UDB, a saber, UDB Addressing.