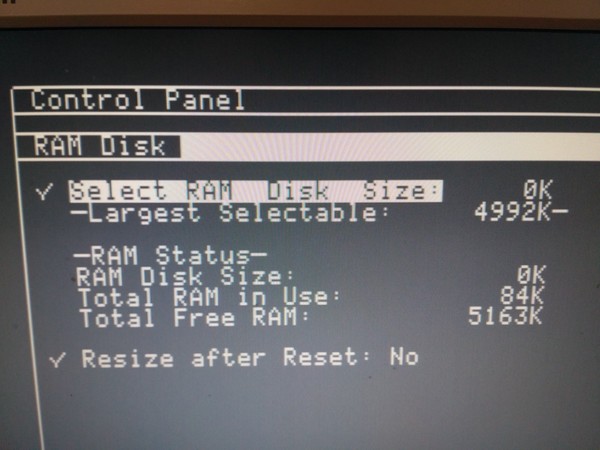

La placa de expansión RAM propuesta para la computadora Apple IIgs se basa en chips NEC uPD424400-70 de varios módulos SIMM de 1 megabyte. Cada uno de estos microchips almacena mordiscos de 1 M y está alojado en una caja tipo SOJ de 26 pines.

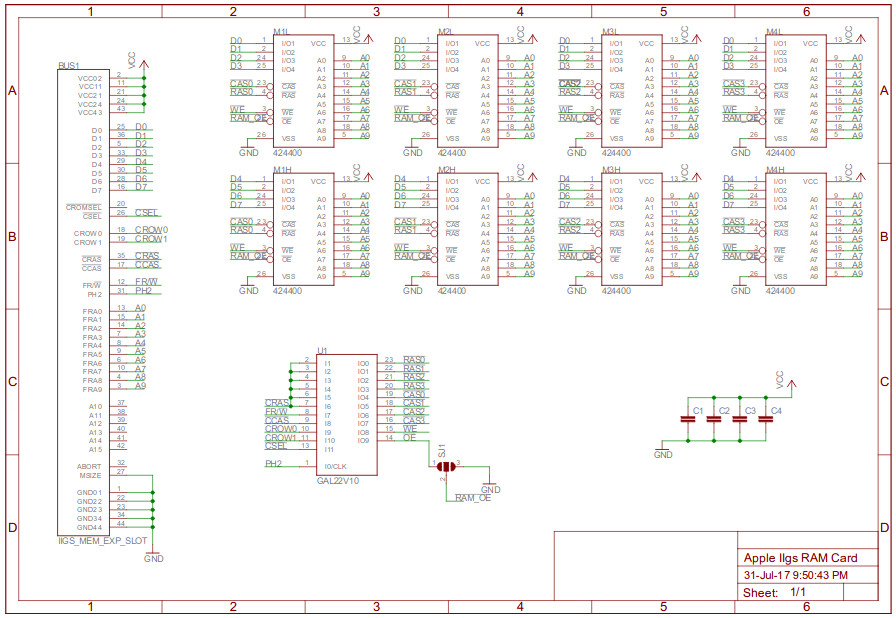

La computadora Apple IIgs funciona con un procesador 65C816 de 16 bits, pero con un bus de datos de 8 bits. La tarjeta de expansión contiene 4 MB de RAM. La memoria se divide en cuatro líneas, 1 MB cada una. La línea consta de dos chips de mordiscos de 1 M, por lo que se requirieron un total de ocho chips.

La computadora ya tiene una ranura para la tarjeta de expansión RAM. Muestra todas las señales necesarias, la computadora también se encarga de la regeneración de la RAM dinámica. Por lo tanto, la tarjeta de expansión es bastante simple. El autor decidió hacer la placa de tamaño pequeño, ya que el costo de su fabricación depende de esto, y también puso toda la lógica en el FPGA GAL22V10.

Las siguientes señales están presentes en la ranura de expansión RAM:

FRA0-FRA9: dirección de celda multiplexada de 10 bits, servida directamente a las entradas de dirección de chips RAM dinámicos

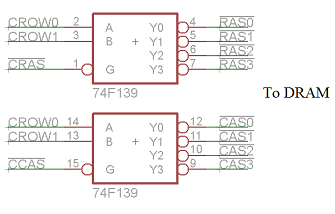

CROW0, 1: dos bits para seleccionar una de las cuatro líneas

/ CRAS - línea de dirección estroboscópica de señal de RAM dinámica

/ CCAS - dirección de columna de compuerta de señal de RAM dinámica

FR / W - permiso de escritura en RAM, esta señal requiere un procesamiento adicional, ver abajo

D0-D7 - bus de datos, conectado directamente a las líneas de entrada / salida de chips RAM

/ CSEL: una unidad lógica aparece en esta línea cuando se lee desde la RAM, debe invertirse y alimentarse a las entradas / OE de los chips de RAM

MSIZE: le dice a la computadora el volumen de la línea: uno - 256 kB, cero - 1 MB, aquí esta línea está conectada a un cable común

14M, PH2CLK, A10-A15 - no están involucrados en la junta propuesta

Las señales / CRAS y / CCAS deben demultiplexarse para obtener señales / RAS y / CAS separadas para cada línea. Para esto, el chip 74F139 es adecuado (en adelante se entiende que no habrá chips separados en la placa, en lugar de ellos habrá un FPGA común).

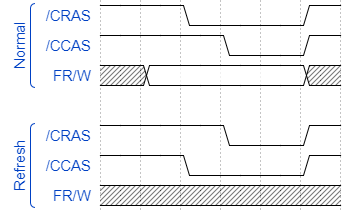

La señal FR / W no se puede alimentar directamente a la entrada / WE de los chips de RAM dinámica, y esta es la razón. En una operación normal de lectura y escritura, la línea / RAS primero se activa (que corresponde a un cero lógico), luego la línea / CAS. Durante un ciclo dinámico de regeneración de RAM, por el contrario, la línea / CAS se activa primero, luego / RAS se activa. Pero los chips utilizados requieren que aparezca una unidad en la línea / WE antes de que la línea / RAS se active. Y la señal FR / W proveniente de Apple IIgs no cumple con este requisito. El estado de FR / W durante el ciclo de regeneración no está definido. Por lo tanto, se requiere un circuito que detecte un ciclo de regeneración y alimente una unidad a / WE.

El primer paso es identificar el ciclo de regeneración. A continuación se muestra el cuadro de tiempo:

La idea del autor es utilizar un pestillo "transparente". La señal / CRAS para ella es la señal de entrada, / CCAS es la señal de cierre. Cuando la unidad está encendida / CCAS, el dispositivo pasa la señal de entrada a través de sí misma: el estado de la salida cambia después del estado de la entrada. Cuando / CCAS va de uno a cero, el pestillo recuerda la señal en la entrada y ahora no cambia en la salida. En una operación normal de lectura / escritura en / CRAS, el cero está presente en el momento de cambiar / CCAS de uno a cero. Y durante el ciclo de regeneración en / CRAS, también hay uno en el momento de cambiar / CCAS a cero. Luego, cuando / CCAS vuelve a cambiar a uno, el pestillo se vuelve transparente nuevamente. Recuerda una flor fantástica de "Secretos del tercer planeta", que puede ser tanto un "espejo" como una "cámara".

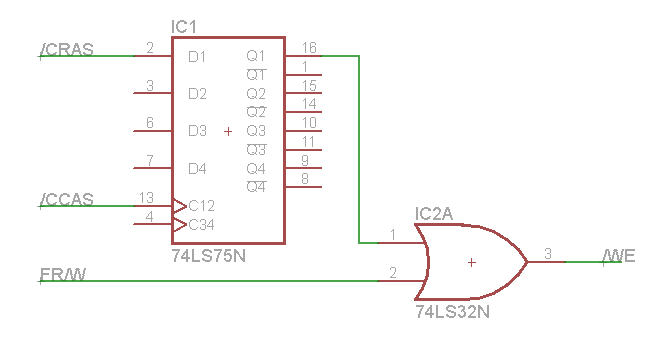

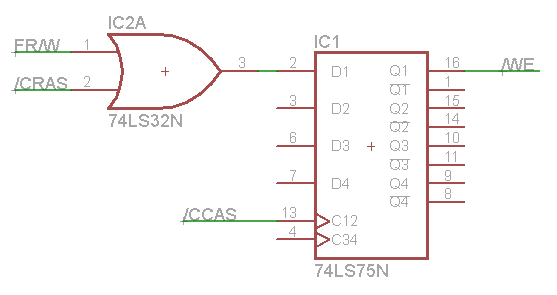

Al principio, el autor elaboró el siguiente esquema:

Pero para su transferencia al FPGA GAL22V10, se requieren dos pines de salida. Por lo tanto, el esquema tuvo que ser simplificado. Durante el funcionamiento normal, la señal FR / W toma el valor deseado hasta que haga clic, por lo que esto también es posible.

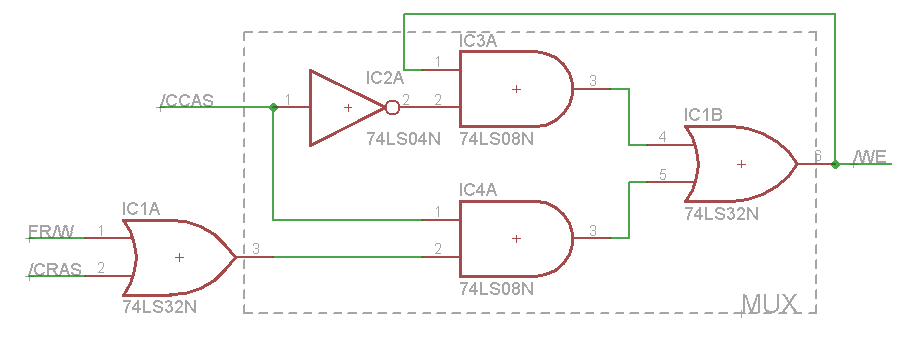

Se puede hacer un pestillo "transparente" desde un multiplexor y, a su vez, desde elementos lógicos. El esquema se convierte así:

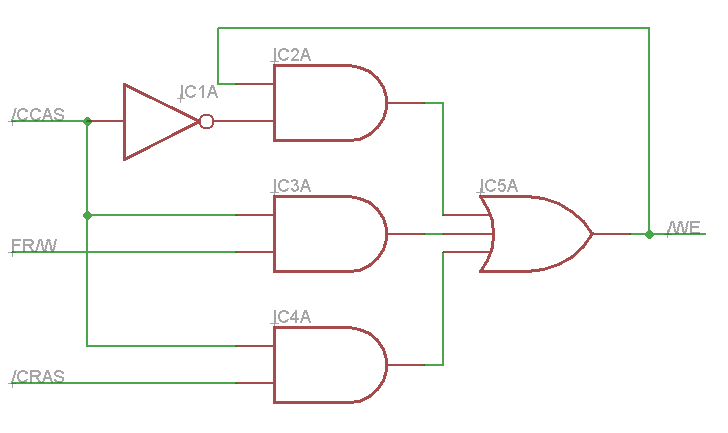

Y después de la simplificación, así:

Esta opción se transfiere a la FPGA. Para la compilación, el autor utilizó WinCUPL. Este programa está en el sitio web de Atmel. Es crudo y vuela constantemente, pero hizo frente a la tarea perfectamente. Programador - Genius G540.

El puente SJ1 en el tablero actúa así. Si los pines 1 y 2 están conectados, la señal / OE pasa a través del FPGA. Si los pines 2 y 3 están conectados, está conectado a un cable común. El autor no estaba seguro de que el esquema para identificar el ciclo de regeneración funcionaría. Por lo tanto, agregó este puente en caso de que la configuración de FPGA tuviera que rehacerse.

Como resultó que todo funciona, no necesita soldar los pines, solo conecte los terminales 1 y 2 con una gota de soldadura.

Para reducir el tamaño de la placa, el autor aplicó un condensador de energía por cada cuatro chips de RAM, y colocó los chips en ambos lados de la placa.

Los microchips en los casos de SOJ son difíciles de soldar, y especialmente con un soldador. El autor recomienda usar un secador de pelo.

Expande las fichas correctamente. En la línea inferior están invertidos. El pin 1 mira hacia abajo.

Algunos agujeros pasantes están demasiado cerca de las almohadillas. No los cortocircuite con soldadura.

Y las plataformas 1 y 2 para el saltador, por el contrario, se cierran.

Los condensadores C1 - C3 tienen una capacitancia de 0.1 μF, C4 - 10 μF.

El autor ordenó los tableros en OSH Park. Se aplica el recubrimiento ENIG - dorado, pero muy delgado. Para los cartuchos de juego no es adecuado, se borrará rápidamente. Y aquí el tablero se colocó en la ranura una vez y no se retira más de allí.

El autor agradece a

GGLabs por el circuito de una placa similar, ayudó mucho, ¡gracias!

El circuito terminado resultó así:

Archivos:

FPGA firmware GAL22V10 , versión del programa WinCUPL 5.30.4 aplicada

Tablero , software Eagle versión 7.1 aplicado

Esquema PDFGanado!