Traducción de la primera parte de la presentación del Tesla Autonomy Investor Day sobre el desarrollo de la computadora de conducción autónoma completa para el piloto automático de Tesla. Completamos el vacío entre las revisiones de tesis para la presentación y su contenido.El texto de la presentación se traduce cerca del original. Preguntas al orador, selectivamente con abreviaturas.Anfitrión: Hola a todos. Perdón por llegar tarde. Bienvenido a nuestro primer día de conducción autónoma. Espero que podamos hacer esto más regularmente para mantenerlo actualizado sobre nuestros desarrollos.

Hace unos tres meses, nos estábamos preparando para el informe de ganancias del cuarto trimestre con Ilon y otros ejecutivos. Luego dije que la mayor brecha en las conversaciones con los inversores, entre lo que veo dentro de la empresa y cuál es su percepción externa, es nuestro progreso en la conducción autónoma. Y esto es comprensible, durante los últimos años hablamos sobre aumentar la producción del Modelo 3, alrededor del cual hubo mucho debate. De hecho, mucho ha sucedido en el fondo.

Trabajamos en un nuevo chip para piloto automático, rediseñamos por completo la red neuronal de visión artificial y finalmente comenzamos a lanzar la Computadora autónoma completa (FSDC). Pensamos que era una buena idea abrir el velo, invitar a todos y contar todo lo que hemos hecho en los últimos dos años.

Hace unos tres años que queríamos usar, queríamos encontrar el mejor chip para la conducción autónoma. Descubrimos que no hay ningún chip diseñado desde cero para redes neuronales. Por lo tanto, invitamos a mi colega Pete Bannon, vicepresidente de diseño de circuitos integrados, a desarrollar un chip para nosotros. Tiene unos 35 años de experiencia en el desarrollo de chips. Incluidos 12 años en PASemi, que luego fue adquirida por Apple. Trabajó en docenas de arquitecturas e implementaciones diferentes, y fue el diseñador jefe del Apple iPhone 5, poco antes de unirse a Tesla. También se une a nosotros en Elon Musk. Gracias

Ilon: En realidad, iba a presentar a Pete, pero como ya lo han hecho, agregaré que es simplemente el mejor arquitecto de sistemas y circuitos integrados del mundo que conozco. Es un honor que usted y su equipo en Tesla. Por favor, cuéntenos sobre el increíble trabajo que ha realizado.

Pete: Gracias Ilon. Me complace estar aquí esta mañana y es realmente agradable contarles sobre todo el trabajo que mis colegas y yo hemos realizado aquí en Tesla durante los últimos tres años. Te contaré un poco sobre cómo comenzó todo, y luego te presentaré la computadora FSDC y te contaré un poco cómo funciona. Profundizaremos en el chip y consideraremos algunos de los detalles. Describiré cómo funciona el acelerador especializado de redes neuronales que diseñamos y luego muestra algunos resultados, y espero que para ese momento todavía no se quede dormido.

Fui contratado en febrero de 2016. Le pregunté a Ilon si estaba listo para gastar tanto como fuera necesario para crear este sistema especializado, él preguntó: "¿Ganaremos?" . Contratamos a un grupo de personas y comenzamos a pensar en cómo sería un chip diseñado específicamente para una conducción totalmente autónoma. Pasamos dieciocho meses desarrollando la primera versión, y en agosto de 2017 la lanzamos para producción. Obtuvimos el chip en diciembre, funcionó, y en realidad funcionó muy bien en el primer intento. En abril de 2018, realizamos varios cambios y lanzamos la versión B zero Rev. En julio de 2018, el chip fue certificado y comenzamos la producción a gran escala. En diciembre de 2018, se lanzó la pila de conducción autónoma en un nuevo equipo, y pudimos proceder con la conversión de los autos de la compañía y las pruebas en el mundo real. En marzo de 2019 Comenzamos a instalar una nueva computadora en los modelos S y X, y en abril, en el Modelo 3.

Por lo tanto, todo el programa, desde la contratación de los primeros empleados hasta el lanzamiento completo en los tres modelos de nuestros automóviles, tomó un poco más de tres años. Este es quizás el programa de desarrollo de sistemas más rápido en el que he participado. Y realmente habla de los beneficios de la alta integración vertical, lo que le permite hacer un diseño paralelo y acelerar la implementación.

En términos de objetivos, estábamos completamente centrados únicamente en los requisitos de Tesla, y esto simplifica enormemente la vida. Si tiene un solo cliente, no necesita preocuparse por los demás. Uno de los objetivos era mantener la potencia por debajo de los 100 vatios para poder convertir las máquinas existentes. También queríamos reducir los costos para proporcionar redundancia para una mayor seguridad.

En el momento en que apuntamos al cielo, sostuve que conducir un automóvil requeriría un rendimiento de red neuronal de al menos 50 billones de operaciones por segundo. Por lo tanto, queríamos obtener al menos la misma cantidad, y mejor, más. Los tamaños de lote determinan la cantidad de artículos con los que trabaja al mismo tiempo. Por ejemplo, los TPU de Google tienen un tamaño de paquete de 256, y debe esperar hasta que tenga 256 elementos para procesar antes de comenzar. No queríamos esperar y desarrollamos nuestro motor con un tamaño de paquete de uno. Tan pronto como aparece la imagen, la procesamos de inmediato para minimizar el retraso y aumentar la seguridad.

Necesitábamos un procesador de gráficos para realizar un procesamiento posterior. Al principio, ocupó bastante, pero asumimos que con el tiempo se volvería más pequeño, ya que las redes neuronales están mejorando cada vez más. Y realmente sucedió. Nos arriesgamos poniendo un procesador de gráficos bastante modesto en el diseño, y resultó ser una buena idea.

La seguridad es muy importante, si no tiene un automóvil protegido, no puede tener un automóvil seguro. Por lo tanto, se presta mucha atención a la seguridad y, por supuesto, a la seguridad.

En términos de arquitectura de chip, como Ilon mencionó anteriormente, en 2016 no hubo un acelerador creado originalmente para redes neuronales. Todos simplemente agregaron instrucciones a su CPU, GPU o DSP. Nadie hizo desarrollo con 0. Por lo tanto, decidimos hacerlo nosotros mismos. Para otros componentes, compramos CPU y GPU industriales IP estándar, lo que nos permitió reducir el tiempo de desarrollo y los riesgos.

Otra cosa que fue un poco inesperada para mí fue la capacidad de usar comandos existentes en Tesla. Tesla tenía excelentes equipos de desarrolladores de fuentes de alimentación, análisis de integridad de señal, diseño de vivienda, firmware, software de sistema, desarrollo de placa de circuito y un programa de validación de sistema realmente bueno. Pudimos usar todo esto para acelerar el programa.

Así es como se ve. A la derecha, verá los conectores para video que provienen de las cámaras del automóvil. Dos computadoras de conducción autónomas en el centro de la placa, a la izquierda: la fuente de alimentación y los conectores de control. Me encanta cuando una solución se reduce a sus elementos básicos. Tienes un video, una computadora y energía, simple y claro. Aquí está la solución anterior de Hardware 2.5, que incluía la computadora y que instalamos los últimos dos años. Aquí hay un nuevo diseño para una computadora FSD. Son muy parecidos. Esto, por supuesto, se debe a las limitaciones del programa de modernización de automóviles. Me gustaría señalar que esta es en realidad una computadora bastante pequeña. Se coloca detrás de la guantera y no ocupa la mitad del tronco.

Como dije antes, hay dos computadoras completamente independientes en el tablero. Se destacan en azul y verde. A los lados de cada SoC puede ver chips DRAM. En la parte inferior izquierda, verá chips FLASH que representan el sistema de archivos. Hay dos computadoras independientes que arrancan y se ejecutan bajo su propio sistema operativo.

Ilon: El principio general es que si alguna parte falla, la máquina puede continuar moviéndose. La cámara, el circuito de alimentación, uno de los chips de computadora Tesla falla: la máquina continúa moviéndose. La probabilidad de falla de esta computadora es significativamente menor que la probabilidad de que el conductor pierda el conocimiento. Este es un indicador clave, al menos un orden de magnitud.

Pete: Sí, entonces una de las cosas que hacemos para mantener la computadora en funcionamiento son las fuentes de alimentación redundantes. El primer chip se ejecuta en una fuente de alimentación y el segundo en otra. Lo mismo es para las cámaras, la mitad de las cámaras en la fuente de alimentación están marcadas en azul, la otra mitad en verde. Ambos chips reciben todo el video y lo procesan de forma independiente.

Desde el punto de vista de la conducción, la secuencia es recopilar mucha información del mundo que lo rodea, no solo tenemos cámaras, sino también radar, GPS, mapas, estabilizador giroscópico (IMU), sensores ultrasónicos alrededor del automóvil. Tenemos un ángulo de dirección, sabemos cómo debería ser la aceleración de un automóvil. Todo esto se une para formar un plan. Cuando el plan está listo, las dos computadoras intercambian sus versiones del plan para asegurarse de que coincidan.

Asumiendo que el plan es el mismo, emitimos señales de control y manejamos. Ahora que te estás moviendo con los nuevos controles, ciertamente quieres probarlo. Verificamos que las señales de control transmitidas coinciden con lo que pretendíamos transmitir a los actuadores del automóvil. Los sensores se utilizan para verificar que el control realmente se está llevando a cabo. Si le pide al automóvil que acelere, que disminuya la velocidad o que gire a la derecha o izquierda, puede mirar los acelerómetros y asegurarse de que esto realmente esté sucediendo. Existe una importante redundancia y duplicación tanto de nuestros datos como de nuestras capacidades de monitoreo de datos.

Hablemos del chip. Está empaquetado en un BGA de 37.5 mm con 1600 pines, la mayoría de los cuales son de alimentación y tierra. Si quita la cubierta, puede ver el sustrato y el cristal en el centro. Si separas el cristal y lo das vuelta, verás 13,000 protuberancias C4 esparcidas por la superficie. Debajo están las doce capas de metal del circuito integrado. Este es un proceso FinFET CMOS de 14 nanómetros que mide 260 mm.sq., un circuito pequeño. A modo de comparación, un chip de teléfono celular convencional mide aproximadamente 100 mm2. Un procesador de gráficos de alto rendimiento tendrá aproximadamente 600-800 mm.kv. Entonces estamos en el medio. Yo lo llamaría el medio dorado, este es un tamaño conveniente para el ensamblaje. Hay 250 millones de elementos lógicos y 6 mil millones de transistores que, aunque he estado trabajando en esto todo este tiempo, me sorprenden. El chip se fabrica y prueba de acuerdo con el estándar automotriz AEC Q100.

Simplemente daría la vuelta al chip y explicaría todas sus partes. Iré en el mismo orden que el píxel que viene de la cámara. En la esquina superior izquierda puede ver la interfaz de la cámara. Podemos tomar 2.500 millones de píxeles por segundo, lo que es más que suficiente para todos los sensores disponibles. Una red que distribuye datos desde un sistema de memoria a controladores de memoria en los bordes derecho e izquierdo del chip. Utilizamos LPDDR4 estándar que funciona a una velocidad de 4266 gigabits por segundo. Esto nos da un rendimiento máximo de 68 gigabytes por segundo. Este es un ancho de banda bastante bueno, pero no excesivo, estamos tratando de mantenernos en el punto medio. El procesador de procesamiento de imágenes tiene una tubería interna de 24 bits, lo que nos permite utilizar completamente los sensores HDR que se encuentran en el automóvil. Realiza un mapeo de tonos avanzado, que ayuda a resaltar mejor los detalles y las sombras, y también realiza una reducción de ruido avanzada, que simplemente mejora la calidad general de las imágenes que utilizamos en una red neuronal.

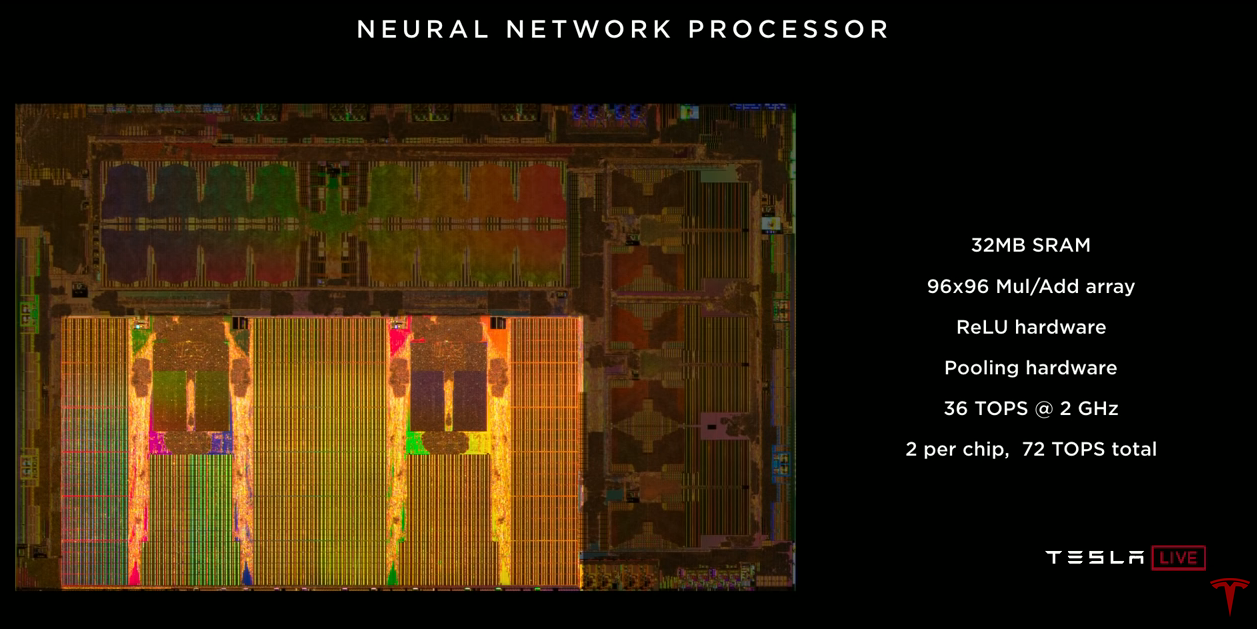

El acelerador de la red neuronal en sí. Hay dos en el chip. Cada uno de ellos tiene 32 megabytes de SRAM para almacenar resultados temporales. Esto minimiza la cantidad de datos que necesitamos transferir al chip y viceversa, lo que ayuda a reducir el consumo de energía. Cada uno contiene una matriz de multiplicadores de 96x96 con acumulación, lo que nos permite hacer casi 10,000 operaciones MUL / ADD por ciclo. Hay un acelerador ReLU dedicado, un acelerador de agrupación. Cada uno de ellos proporciona 36 billones de operaciones por segundo que funcionan a una frecuencia de 2 GHz. Dos aceleradores en un chip dan 72 trillones de operaciones por segundo, que es notablemente más alto que el objetivo de 50 trillones.

El codificador de video, el video que usamos en el automóvil para muchas tareas, incluida la salida de imágenes desde la cámara de visión trasera, la grabación de video, así como para grabar datos en la nube, Stuart y Andrew hablarán sobre esto más adelante. Un procesador gráfico bastante modesto se encuentra en el chip. Admite números de coma flotante de 32 y 16 bits. También 12 procesadores A72 de uso general de 64 bits. Operan a una frecuencia de 2.2 GHz, que es aproximadamente 2.5 veces mayor que el rendimiento de la solución anterior. El sistema de seguridad contiene dos procesadores que funcionan en modo de bloqueo. Este sistema toma la decisión final de si es seguro transmitir señales de control a las unidades del vehículo. Aquí es donde los dos aviones se unen, y decidimos si es seguro avanzar. Y, por último, un sistema de seguridad cuya tarea es garantizar que solo se use en este chip el software Tesla firmado criptográficamente.

Les dije muchos indicadores de rendimiento diferentes, y creo que sería útil mirar hacia el futuro. Consideraremos una red neuronal desde nuestra cámara (estrecha). Se necesitan 35 mil millones de operaciones. Si utilizamos las 12 CPU para procesar esta red, podemos hacer 1,5 cuadros por segundo, es muy lento. Absolutamente no es suficiente para conducir un automóvil. Si usáramos GPU con 600 GFLOP para la misma red, obtendríamos 17 cuadros por segundo, lo que aún no es suficiente para conducir un automóvil con 8 cámaras. Nuestro acelerador de red neuronal puede producir 2100 cuadros por segundo. Puede ver que la cantidad de cómputo en la CPU y la GPU es insignificante en comparación con el acelerador de la red neuronal.

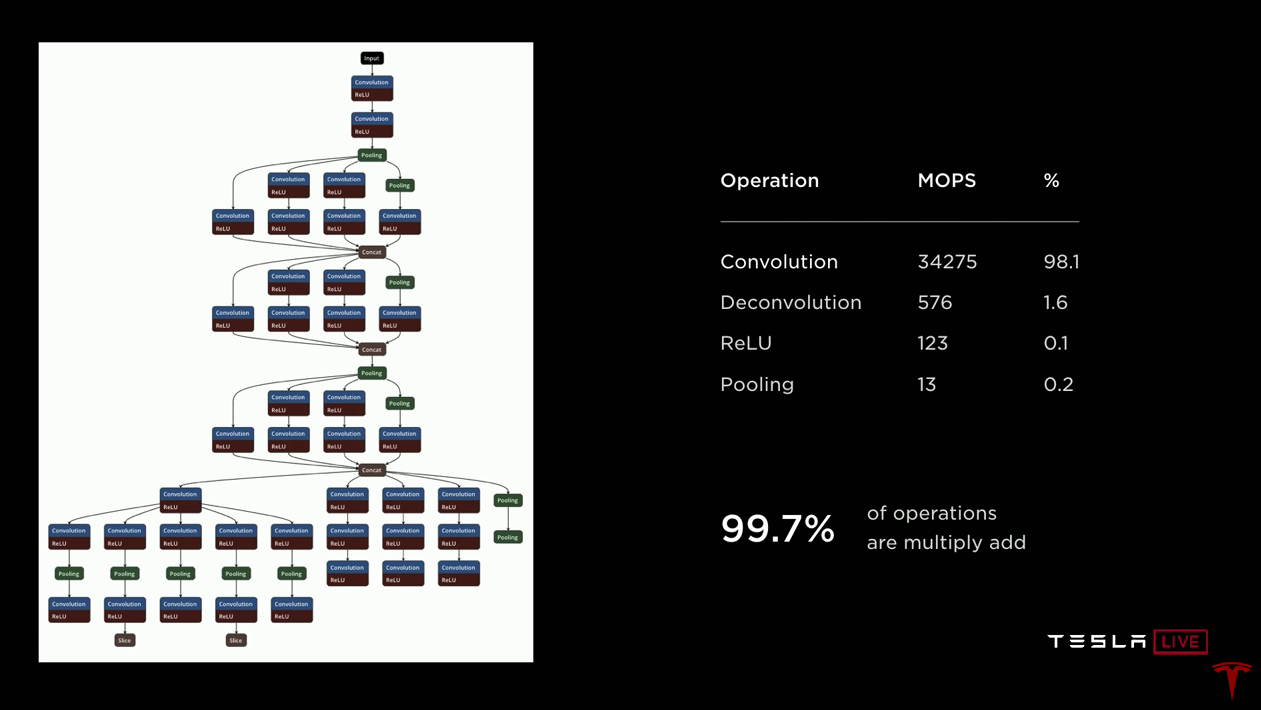

Pasemos a hablar sobre un acelerador de red neuronal. Solo beberé un poco de agua. A la izquierda aquí hay un dibujo de una red neuronal para darle una idea de lo que está sucediendo. Los datos llegan a la parte superior y pasan a través de cada uno de los bloques. Los datos se transmiten a lo largo de las flechas a varios bloques, que generalmente son convoluciones o convoluciones inversas con funciones de activación (ReLU). Los bloques verdes combinan capas. Es importante que los datos recibidos por un bloque sean luego utilizados por el siguiente bloque, y ya no los necesite, puede tirarlos. Por lo tanto, todos estos datos temporales se crean y destruyen al pasar por la red. No es necesario almacenarlos fuera del chip en DRAM. Por lo tanto, solo los almacenamos en SRAM, y en unos minutos explicaré por qué esto es muy importante.

Si observa el lado derecho, verá que en esta red de 35 mil millones de operaciones, casi todas son convoluciones, esencialmente productos escalares, el resto son deconvolución (convoluciones inversas), también basadas en el producto escalar, y luego ReLU y agrupación son relativamente simples. operaciones Por lo tanto, si está desarrollando un acelerador, se enfoca en implementar productos escalares basados en la adición con acumulación y optimizarlos. Pero imagine que acelera esta operación 10.000 veces y el 100% se convierte en 0.1%. De repente, ReLU y las operaciones de agrupación se vuelven muy significativas. Por lo tanto, nuestra implementación incluye aceleradores dedicados para el procesamiento y la agrupación de ReLU.

El chip opera en un presupuesto de calor limitado. Necesitábamos tener mucho cuidado con la forma en que quemamos energía. Queremos maximizar la cantidad de aritmética que podemos hacer. Por lo tanto, elegimos la suma de enteros de 32 bits, consume 9 veces menos energía que la suma de punto flotante. Y elegimos la multiplicación de enteros de 8 bits, que también consume significativamente menos energía que otras operaciones de multiplicación, y probablemente tiene suficiente precisión para obtener buenos resultados. En cuanto a la memoria. Acceder a la DRAM externa es aproximadamente cien veces más costoso en términos de consumo de energía que usar la SRAM local. Está claro que queremos aprovechar al máximo la SRAM local.

Desde el punto de vista de la administración, aquí están los datos publicados en un artículo de Mark Horowitz, donde examinó críticamente cuánta energía se necesita para ejecutar una sola instrucción en un procesador entero normal. Y ve que la operación de adición consume solo el 0.15% de la potencia total. Todo lo demás está sobrecargado para la administración y más. Por lo tanto, en nuestro diseño nos esforzamos por deshacernos de todo esto tanto como sea posible. Lo que realmente nos interesa es la aritmética.

Así que aquí está el diseño que hemos terminado. Puedes ver que en él el lugar principal está ocupado por 32 megabytes de SRAM, están a la izquierda, a la derecha, en el centro y en la parte inferior. Todos los cálculos se realizan en la parte central superior. En cada ciclo, leemos 256 bytes de datos de activación del conjunto SRAM, 128 bytes de pesos del conjunto SRAM y los combinamos en un conjunto 96x96, que realiza 9000 adiciones con acumulación por ciclo a 2 GHz. Esto es solo 36.8 billones. operaciones Ahora que hemos terminado con el producto escalar, cargamos los datos, los pasamos a través del ReLU dedicado, opcionalmente mediante extracción, y finalmente lo colocamos en el búfer de escritura, donde se agregan todos los resultados. Y luego escribimos 128 bytes por reloj de vuelta a SRAM. Y todo esto sucede continuamente. Trabajamos con productos escalares, mientras descargamos resultados anteriores, realizamos tiradas y escribimos los resultados en la memoria.

Si lo apila todo a 2 GHz, necesitará 1 terabyte por segundo de ancho de banda SRAM para admitir la operación. Y el hierro proporciona esto. Un terabyte por segundo de ancho de banda por acelerador, dos aceleradores por chip, dos terabytes por segundo.El acelerador tiene un conjunto relativamente pequeño de comandos. Hay una operación de lectura DMA para cargar datos desde la memoria, una operación de escritura DMA para cargar los resultados de nuevo a la memoria. Tres instrucciones de convolución (convolución, deconvolución, producto interno). Dos operaciones relativamente simples son la operación shift y elementwise (eltwise). Y, por supuesto, la operación de parada cuando finalizan los cálculos.Tuvimos que desarrollar un compilador de redes neuronales. Tomamos una red neuronal capacitada por nuestro equipo de desarrollo, en la forma en que se usaba en el hardware antiguo. Cuando lo compila para usarlo en un nuevo acelerador, el compilador realiza la fusión de capas, lo que nos permite aumentar el número de cálculos para cada llamada a SRAM. También realiza suavizado de accesos a memoria. Realizamos relleno de canales para reducir conflictos entre bancos de memoria. La asignación de memoria también tiene en cuenta los bancos SRAM. Este es el caso cuando el procesamiento de conflictos podría implementarse en hardware. Pero con la implementación de software, ahorramos en hardware debido a cierta complejidad del software. También insertamos automáticamente operaciones DMA para que los datos lleguen a tiempo para los cálculos, sin detener el procesamiento. Al final, generamos el código,pondera los datos, comprime y agrega una suma de verificación CRC para mayor confiabilidad. La red neuronal se carga en SRAM al inicio y está ahí todo el tiempo.Por lo tanto, para iniciar la red, debe especificar la dirección del búfer de entrada, que contiene una nueva imagen que acaba de llegar de la cámara; establecer la dirección del búfer de salida; establecer el puntero al peso de la red; vamos El acelerador "entra en sí mismo" y pasará secuencialmente por toda la red neuronal, generalmente durante uno o dos millones de ciclos de reloj. Al finalizar, recibe una interrupción y puede procesar los resultados.Volviendo a los resultados. Nuestro objetivo era alcanzar los 100 vatios. Las mediciones en automóviles que conducen con una pila completa de piloto automático han demostrado que disipamos 72 vatios. Esto es ligeramente mayor que en el proyecto anterior, pero una mejora significativa en el rendimiento es una buena excusa. De estos 72 vatios, aproximadamente 15 vatios se consumen en redes neuronales. El costo de esta solución es aproximadamente el 80% de lo que pagamos antes. En términos de rendimiento, tomamos la red neuronal (estrecha) de la cámara, que ya mencioné, con 35 mil millones de operaciones, la lanzamos en equipos antiguos y recibimos 110 cuadros por segundo. Tomamos los mismos datos y la misma red, los compilamos para la nueva computadora FSD y, utilizando los cuatro aceleradores, podemos procesar 2300 cuadros por segundo.Ilon:Creo que esta es quizásla diapositiva más importante de Pete: nunca he trabajado en un proyecto donde la mejora de la productividad había terminado 3. Por lo tanto, fue bastante divertido. En comparación con la solución nvidia Drive Xavier, el chip proporciona 21 billones. operaciones, mientras que nuestro FSDC con dos chips - 144 billones. operacionesEn conclusión, creo que hemos creado una solución que ofrece un rendimiento sobresaliente de 144 billones. operaciones para procesar una red neuronal. Tiene excelentes características de potencia. Logramos exprimir toda esta productividad en el presupuesto de calefacción que teníamos. Esto le permite implementar una solución de duplicación. La computadora tiene un costo moderado, y lo que es realmente importante, el FSDC proporcionará un nuevo nivel de seguridad y autonomía en los autos Tesla, sin afectar su costo y millaje. Todos lo esperamos.Ilon: Si tiene preguntas sobre el equipo, pregúnteles ahora mismo.La razón por la que le pedí a Pete que hiciera un trabajo detallado, mucho más detallado de lo que quizás la mayoría de las personas hubiera apreciado sumergirse en una computadora Tesla FSD es la siguiente. A primera vista, parece increíble cómo podría suceder que Tesla, que nunca antes había diseñado tales chips, creara el mejor chip del mundo. Pero esto es exactamente lo que sucedió. Y no solo los mejores por un pequeño margen, sino los mejores por un amplio margen. Todos los Tesla fabricados en este momento tienen esta computadora. Cambiamos de la solución Nvidia para S y X hace aproximadamente un mes y cambiamos el Modelo 3 hace aproximadamente diez días. Todos los automóviles producidos tienen todo el hardware necesario y todo lo necesario para una conducción totalmente autónoma. Lo diré nuevamente: todos los autos Tesla producidos ahora,tiene todo lo que necesita para una conducción totalmente autónoma. Todo lo que tienes que hacer es mejorar el software. Más tarde hoy, puede conducir automóviles con una versión para desarrolladores de software de conducción autónomo mejorado. Lo verás por ti mismo. PreguntasP: ¿tiene la capacidad de usar funciones de activación que no sean ReLU?Pete: sí, tenemos un sigmoide, por ejemploP: ¿ quizás valió la pena cambiar a un proceso de fabricación más compacto, tal vez 10 nm o 7 nm?Pete: en el momento en que comenzamos a diseñar, no todas las IP que queríamos estaban disponibles en 10 nmIlon: vale la pena señalar que completamos este diseño hace aproximadamente un año y medio y comenzamos la próxima generación. Hoy no estamos hablando de la próxima generación, pero ya estamos a la mitad. Todo lo que es obvio para el chip de próxima generación, lo hacemos.P: La computadora está diseñada para funcionar con cámaras. ¿Puedo usarlo con lidar?Ilon:Lidar es una decisión desastrosa, y cualquiera que confíe en Lidar está condenado. Condenados Caro Estimados sensores que no son necesarios. Es como tener un montón de costosas aplicaciones innecesarias. Una pequeña no es nada, pero un montón ya es una pesadilla. Esto es estúpido, ya lo verás.P: ¿Puede evaluar el impacto del consumo de energía en el kilometraje?Pete: Para el Modelo 3, el consumo objetivo es de 250 vatios por milla.Ilon:Depende de la naturaleza de la conducción. En la ciudad, el efecto será mucho mayor que en la carretera. Conduce en la ciudad durante una hora y tiene una solución hipotética que consume 1 kW. Perderá 6 km en el Modelo 3. Si la velocidad promedio es de 25 km / h, perderá un 25%. El consumo del sistema tiene un gran impacto en el kilometraje en una ciudad donde creemos que habrá una gran parte del mercado de robotax, por lo que la potencia es extremadamente importante.P: ¿Qué tan confiable es su tecnología en términos de IP? ¿No va a dar IP gratis?Pete: Hemos presentado una docena de patentes para esta tecnología. Esto es esencialmente álgebra lineal, que no creo que pueda patentar. (Ilon se ríe)P:su microcircuito puede hacer algo, tal vez encriptar todos los pesos para que su propiedad intelectual permanezca adentro, y nadie pueda robarlo.Ilon: Oh, me gustaría conocer a alguien que pueda hacer esto. Lo contrataría en un instante. Este es un problema muy difícil. Incluso si puede extraer los datos, necesitará una gran cantidad de recursos para usarlos de alguna manera.La gran ventaja sostenible para nosotros es la flota. Nadie tiene una flota. Los pesos se actualizan y mejoran constantemente en función de miles de millones de millas recorridas. Tesla tiene cien veces más autos con el hardware necesario para el entrenamiento que todos los demás combinados. Para fines de este trimestre, tendremos 500,000 vehículos con 8 cámaras y 12 sensores ultrasónicos. En un año tendremos más de un millón de automóviles con FSDC. Esto es solo una gran ventaja de datos. Esto es similar a cómo el motor de búsqueda de Google tiene una gran ventaja, porque las personas lo usan y realmente entrenan a Google con sus consultas.Anfitrión:Una cosa para recordar acerca de nuestra computadora FSD es que puede funcionar con redes neuronales mucho más complejas para un reconocimiento de imagen mucho más preciso. Es hora de hablar sobre cómo realmente obtenemos estas imágenes y cómo las analizamos. Aquí tenemos un director sénior de IA, Andrey Karpaty, quien le explicará todo esto. Andrei es doctor por la Universidad de Stanford, donde estudió ciencias de la computación con énfasis en el reconocimiento y el aprendizaje profundo.Ilon: Andrey, por qué no empiezas, vamos. Muchos médicos salieron de Stanford, no importa. Andrey está enseñando un curso de visión por computadora en Stanford, que es mucho más importante. Cuéntanos sobre ti.

(La traducción resultó no ser una cuestión rápida, no sé si tengo suficiente para la segunda parte sobre el sistema de entrenamiento de la red neuronal, aunque me parece el más interesante).