Una pequeña introducción:

La idea de escribir su propio núcleo surgió después de aprobar un seminario escolar sobre circuitos digitales en la ciudad de Tomsk . En este evento, conocerá los lenguajes de descripción de hardware actuales (Verilog HDL y VHDL), así como con un pequeño procesador core schoolMIPS . Para comprender la estructura de los núcleos, se decidió inventar su propia bicicleta, siguiendo el camino del desarrollo de schoolMIPS, pero tomando como base otro sistema de comando. Debido a la creciente popularidad de RISC-V y la apertura de su sistema de comando (MIPS no tenía un sistema de comando abierto en el momento en que se escribió el kernel), se eligió un conjunto de instrucciones RISC-V, a saber RV32I, para el desarrollo del kernel futuro. RV32I tiene un pequeño conjunto de instrucciones básicas (37 excluyendo las especiales) y se puede ampliar si lo desea, por ejemplo, agregando instrucciones de multiplicación y división de enteros (RV32M) o soporte para instrucciones acortadas (RV32C). Además, este proyecto fue concebido como educativo, por lo que se decidió maximizar la visibilidad del núcleo para demostrar su trabajo de manera efectiva.

Por analogía con schoolMIPS, se implementaron las siguientes versiones de kernel:

- Versión de ciclo único (00_simple_risc_v_cpu).

- Una versión de ciclo único con soporte para instrucciones lw / sw (cargar palabra / almacenar palabra) (01_simple_risc_v_cpu_lwsw).

- Versión de tubería (transportador de 5 etapas) (02_pipe_risc_v_cpu).

Actualmente, se describe la próxima versión del kernel (03_pipe_risc_v_cpu_fc) con el conjunto completo de comandos RV32I (sin tener en cuenta algunos especiales).

En el curso de la descripción del núcleo, se pensaron formas de mejorar la visibilidad del trabajo, la depuración y la verificación. Actualmente implementa los siguientes métodos:

Agregar un módulo VGA de texto de depuración (para dos ramas de núcleo de ciclo único). La inclusión de este módulo le permite rastrear simultáneamente el valor de 32 registros en la pantalla del monitor, lo que no es posible cuando se utiliza la salida de información en indicadores de siete segmentos. En las figuras presentadas a continuación, el núcleo calcula los números de Leonardo y muestra información sobre el módulo de depuración correspondiente;

hex_display y DebugScreenCoreSalida de información sobre indicadores de siete segmentos:

Salida de información en la pantalla VGA:

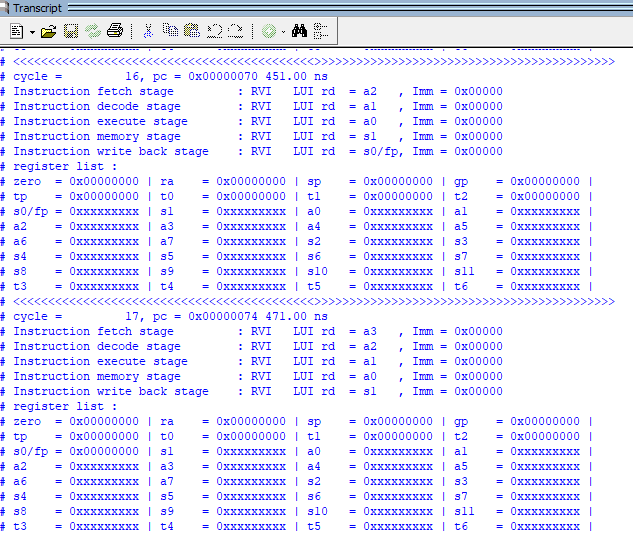

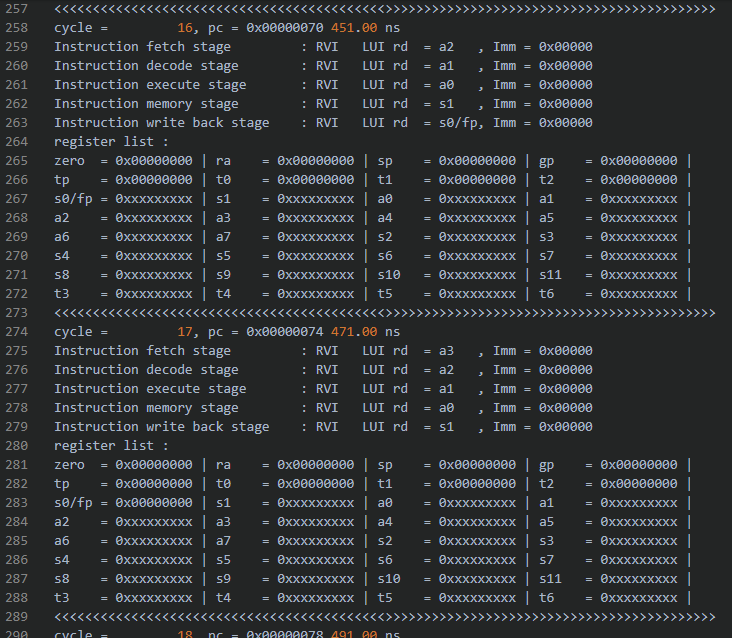

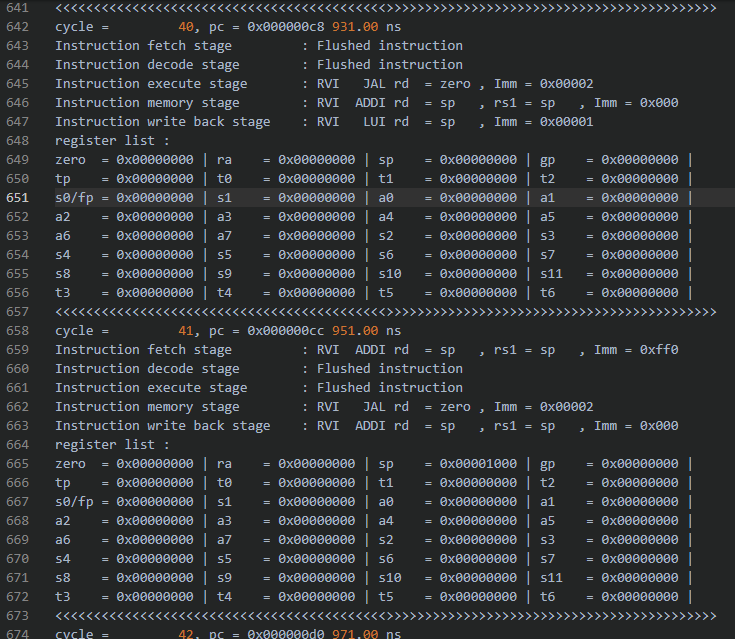

Agregar mensajes al terminal del simulador sobre el estado del archivo de registro y ejecutar las instrucciones actualmente. Este método le permite analizar mejor el funcionamiento del núcleo en las primeras etapas de desarrollo, pero no siempre es conveniente;

TerminalInicialización del archivo de registro:

Cambiar valor de sp:

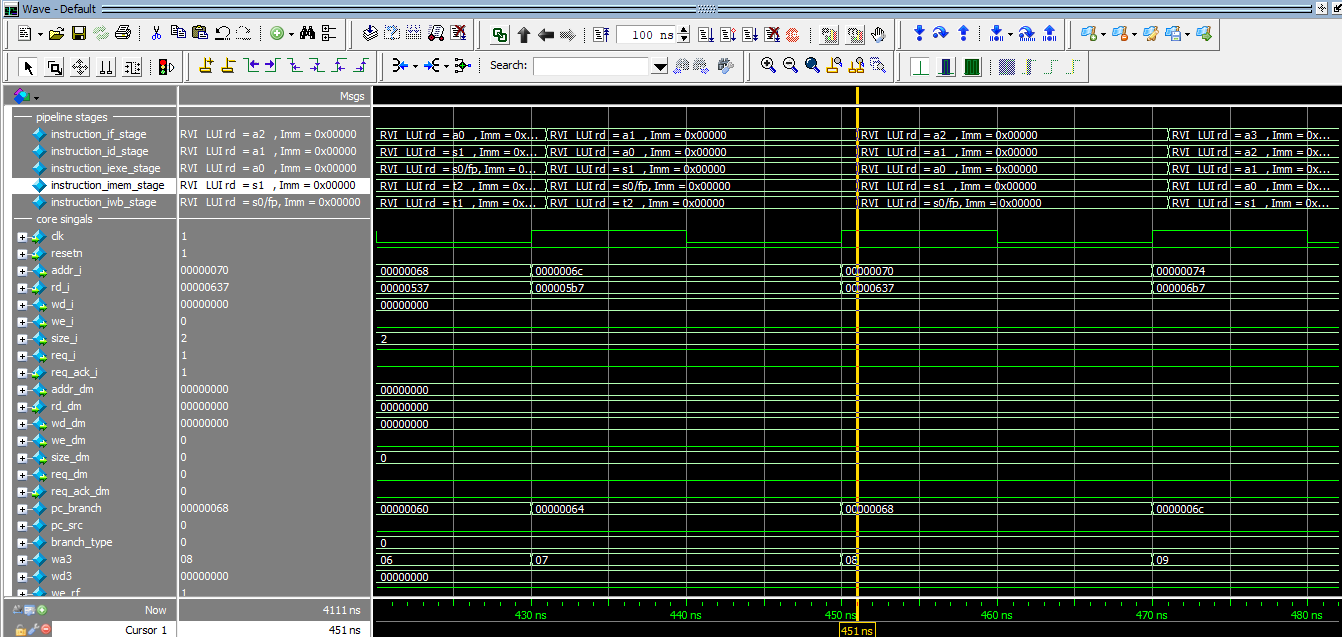

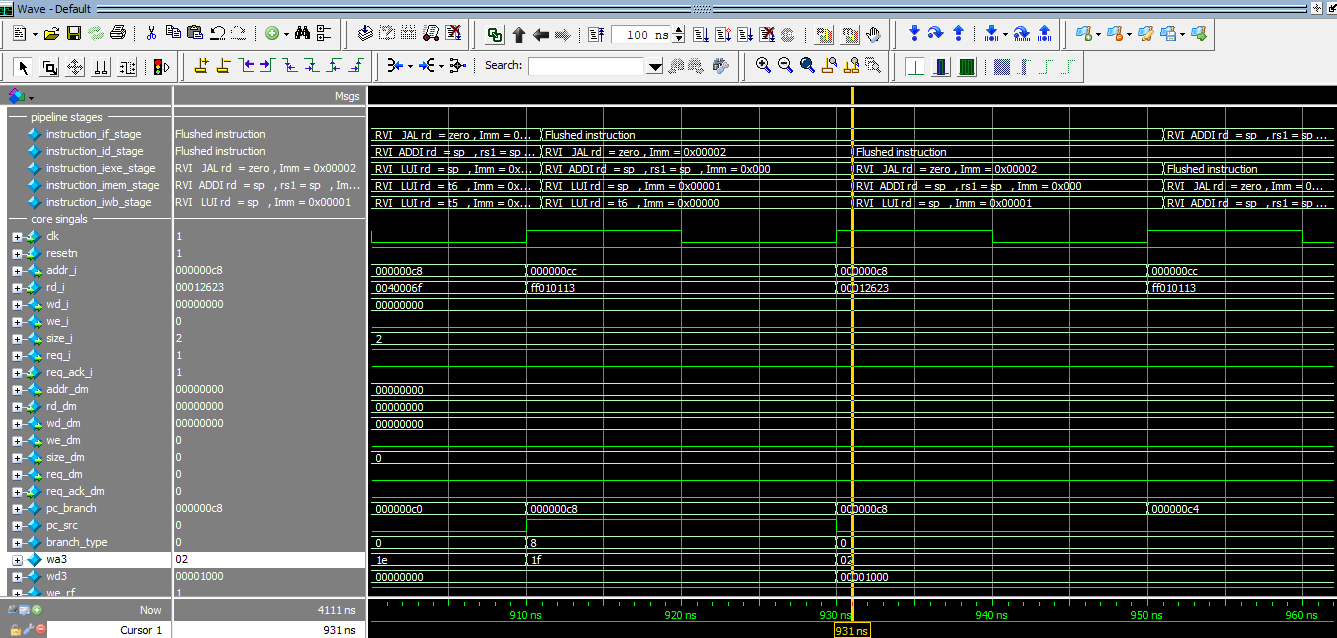

Agregar variables de cadena a la forma de onda con la visualización de instrucciones ejecutables. Usando estas variables de cadena, el desarrollador puede rastrear la configuración correcta de las señales de control en todas las etapas de la tubería;

Forma de ondaInicialización del archivo de registro:

Cambiar valor de sp:

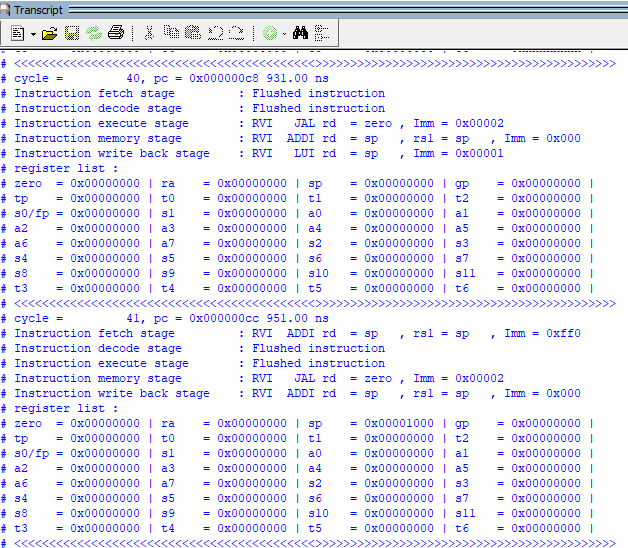

Agregar la capacidad de escribir información de depuración sobre el estado del núcleo en un archivo de texto. El estado del archivo de registro se presenta en forma de tabla y también se indican las instrucciones / instrucciones actualmente ejecutadas por el núcleo. Es un análogo de 2 puntos, pero permite más manipulaciones con la información recibida;

Archivo de textoInicialización del archivo de registro:

Cambiar valor de sp:

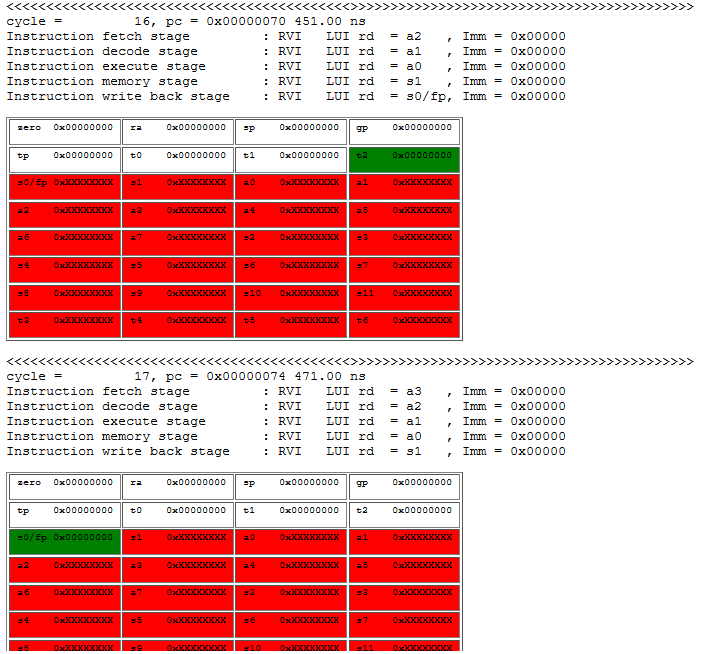

Agregar la capacidad de escribir información de depuración sobre el estado del núcleo en un archivo HTML. El estado del archivo de registro se presenta en forma de tabla con notas sobre cómo cambiar los valores de las celdas, así como también se muestran las instrucciones que el núcleo está ejecutando actualmente. Es un análogo de los párrafos 2 y 4, pero además de ellos le permite indicar convenientemente un cambio en los datos. Como se puede ver en las imágenes a continuación, si el valor del registro no se definió, los registros se resaltan en rojo (registros s0 / fp - t6). En el ciclo 17, el valor del registro s0 / fp cambia y la celda se resalta en verde.

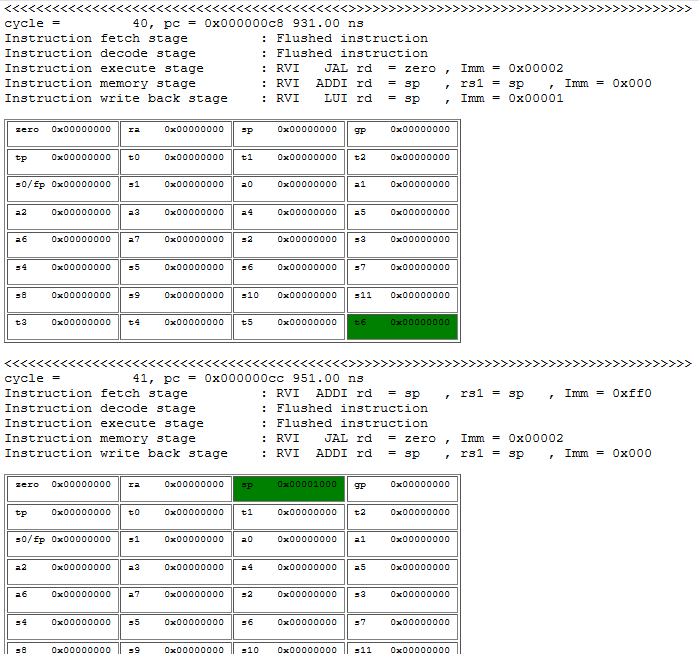

En el ciclo 41, el valor 0x00010000 se carga en el registro sp.

Archivo HTMLInicialización del archivo de registro:

Cambiar valor de sp:

Comparación de las ramas del núcleo:Instrucciones de kernel actualmente admitidas para diferentes ramas:

Periféricos compatibles:

Idiomas admitidos para escribir programas:

Recursos de FPGA necesarios para el núcleo (nf_cpu):

EP4CE22F17C6 (de0_nano):

10M50DAF484C7G (de10_lite):

Desarrollo de proyectos.

Lo que se planea hacer en el futuro:

- agregue todas las instrucciones RV32I (en la etapa de descripción);

- implementar depuración;

- agregar un controlador DMA (DMA);

- agregue soporte para otros neumáticos AXI, Avalon, Wishbone;

- agregar memoria caché (caché);

- integrar varios periféricos (SPI, TWI (I2C), Ethernet (10 base-t));

- agregar controlador de interrupción;

- portar diferentes versiones a otras placas de depuración;

- agregue otros métodos para aumentar la visibilidad del núcleo;

- ejecutando RTOS, por ejemplo zephyr .

También se aceptan recomendaciones y sugerencias para el desarrollo del núcleo.

Enlace al repositorio: nanoFOX .