Tienes este sueño: te encuentras en un examen o hablas frente a cierta audiencia, y de repente te das cuenta de que no te estabas preparando y ahora tendrás que improvisar. En esta situación, pero no en un sueño, sino en la vida real, me enfrenté a las vacaciones de mayo en Moscú, donde volé desde California para llevar a cabo un seminario de tres días para estudiantes cuidadosamente seleccionados de las principales escuelas de física de Moscú. Bajo los auspicios de RUSNANO, en el gimnasio RUT (MIIT) y en presencia de profesores de MIET, MIREA, MEPhI, MPEI y HSE MIEM.

Mis colegas de Moscú me esperaban y, en teoría, debería haber traído instrucciones paso a paso y ejemplos de varios ejercicios en una placa de circuito con un microcircuito lógico reconfigurable. En realidad, tenía algunos ejemplos para otros tableros, de los cuales no construí nada en el desorden de vuelos y otros eventos.

Por lo tanto, tomé un ejemplo universal, que escribí hace un año y medio, sentado en un avión de Alma-Ata-Astana, arrojé todo el interior del ejemplo y comencé a llenarlo de escolares sin un plan difícil. Y curiosamente, funcionó. En el proceso de llenado, surgieron momentos instructivos de circuitos digitales y el lenguaje de descripción de hardware Verilog, que durante la planificación no habría surgido.

El 4 de junio, mis colegas y yo en Wave Computing llevaremos a cabo un seminario similar en Las Vegas, pero solo para adultos, y del 8 al 19 de julio ayudo a MIET a dirigir una escuela de verano en Zelenograd. Planes para estos eventos (no finales, pero para discusión en un grupo de maestros e ingenieros, incluido aquí en Habré) - al final del post.

¿Por qué necesitamos un seminario sobre FPGA para escolares? Los circuitos integrados de lógica programable (FPGA o FPGA - Field Programmable Gate Arrays) son una forma tradicional de consolidar el conocimiento en la práctica cuando se estudia el diseño de circuitos digitales a nivel de transferencias de registros utilizando lenguajes de descripción de hardware. En otras palabras, la tecnología clave para el desarrollo de iPhones: los microchips dentro de los iPhones están diseñados de esa manera. El retraso de Rusia con respecto a los iPhones también se debió al hecho de que los FPGA, la microarquitectura y los lenguajes de descripción de hardware se introdujeron en Berkeley y MIT a principios de la década de 1990, y en Rusia debido al colapso de la URSS mucho más tarde.

El último seminario de Rosnanov fue sorprendentemente fluido principalmente porque los estudiantes que asistieron habían completado previamente un curso teórico en línea con una encuesta orientada a la carrera de métodos modernos de diseño de microcircuitos. El curso en línea está dirigido a escolares avanzados del tipo de olimpiada y consta de tres módulos:

"Del transistor al microcircuito" ,

"El lado lógico de los circuitos digitales" y

"El lado físico de los circuitos digitales" . En este curso, los estudiantes se familiarizan con la llamada ruta RTL2GDSII, un grupo de tecnologías que los ingenieros usan en compañías electrónicas para diseñar chips a granel, Circuitos integrados de aplicaciones específicas - ASIC. Los FPGA / FPGA se utilizan para crear prototipos de ASIC, incluidas compañías como Intel, Apple y NVidia.

Desde que los estudiantes tomaron el curso en línea, ya han aprendido qué es D-trigger, máquina de estado, síntesis lógica y rastreo. También vieron el lenguaje de descripción de hardware en el curso en línea. Ahora este conocimiento, que yacía pasivamente en su memoria, solo necesitaba ser revivido.

Ahora siempre lo haré para cualquier seminario en los países de la CEI (además de los seminarios ya planeados, tengo propuestas para llevarlo a cabo en Minsk, Sochi y Yakutsk) para establecer la condición para que el anfitrión deje a los alumnos o estudiantes a través de tres módulos del curso en línea, ya que después solo quedan personas motivadas que ya han pasado por todos los aspectos tediosos, y la creatividad pura permanece como refuerzo, el último momento, como la caída de una manzana que golpeó la cabeza de Newton. Además, el curso en línea vincula toda esta actividad a las profesiones de adultos, la siguiente etapa, dibuja un objetivo distante.

En total, antes de volar a Moscú, lancé un ejemplo universal en mi casa en Sunnyvale, California.

Código de ejemplo :

El primer día del taller, practicamos con microcircuitos con un pequeño grado de integración en una placa de pruebas. Esta tecnología tiene 50 años, pero a nadie se le ocurrió una idea mejor, en la vida real, que en la simulación, de mostrar cómo funcionan los D-triggers, por ejemplo. Aunque a muchos maestros de tecnología moderna en las escuelas les parece obsoleto e innecesario, pero ahora en el curso 6.111 del Instituto de Tecnología de Massachusetts, ahora, en el año académico 2018/2019, el primer laboratorio de circuitos digitales funciona exactamente de esta manera con microcircuitos con un pequeño grado de integración.

//web.mit.edu/6.111/volume2/www/f2018/index.html .

Además, utilizando el ejemplo de la conexión de microcircuitos con un pequeño grado de integración con botones, es conveniente explicar qué es, por qué es necesario y cómo funcionan las resistencias pull-up. Y por qué dan un potencial de 0 cuando no se presiona el botón, y cómo se relaciona esto con el divisor de voltaje.

Incluso cuando, con el ejemplo de un microcircuito de un pequeño grado de integración, el LED se apaga, los estudiantes obtienen la experiencia de la vida de que es necesario colocar una resistencia allí. Si ven esto en la pantalla de una computadora en un simulador de software de una placa de prueba, no obtendrán esa experiencia de vida, ya que puede dibujar cualquier cosa en la pantalla y los escolares no estarán seguros de que el agotamiento sea verdadero.

Así es como la función del D-flip-flop es claramente visible en microcircuitos de un pequeño grado de integración:

El segundo día comenzó con un bosquejo histórico: cómo se diseñaron los microchips hace 50 años y cómo ha cambiado dos veces desde entonces. Una de las revoluciones se superpuso al colapso de la URSS y esta es la razón técnica principal por la que Rusia no tiene iPhones.

A las 8.45, la historia de cómo el espía de la boya soviética, que controlaba el movimiento de los barcos estadounidenses, fue atrapado en los océanos, y a qué condujo.

El 13 de marzo, la historia de cómo la publicación de un blogger John Cooley desplazó a toda la industria global de VHDL a Verilog.

El 16.10, la historia de cómo Microsoft Windows perdió ante Linux como plataforma para el trabajo de los diseñadores de chips.

En esta parte, una demostración de cómo ejecutar un programa para la síntesis de lógica digital y configuración de firmware en el FPGA. De dos maneras: ejecutando un script en Linux y en un shell gráfico integrado. También una breve descripción de los contenidos de la demostración. Después de este galope por toda Europa, los estudiantes se sientan en el caparazón gráfico y hacen ejercicios simples, comenzando con los elementos lógicos AND-OR-NOT, cuyas entradas están conectadas a los botones y las salidas a los LED. Algo asi:

module top (input [2:0] key, output [7:0] led); wire a = ~ key [0]; // 0, , wire b = ~ key [1]; wire c = a & b; assign led [0] = ~ c; // , 0 endmodule

En el proceso, dos preguntas interesantes surgieron de inmediato. En primer lugar, al principio, yo mismo olvidé que tanto los botones como los LED están invertidos en esta placa. Es decir, cuando se presiona el botón, luego 0 en el cable, y cuando no se presiona, luego 1. Y cuando 0 se alimenta al LED, está encendido y cuando 1 no está encendido. Si no conoce la inversión, entonces el elemento lógico AND (led [0] = tecla [0] y tecla [1]) comienza a comportarse como OR, y OR - como I. ¡Leyes de Morgan en acción! ~ (a & b) == ~ a | ~ b, así como ~ (a | b) == ~ a & ~ b.

Pero incluso después de que algunos escolares corrigieron, este negocio siguió funcionando al revés. Luego miré su código y descubrí que cuando reescribían el código que escribí en la pizarra, pensaban que "~" (tilde) es "-" (menos). Esto me dio una excelente razón para contar la diferencia entre

el código

directo y

adicional , y también por qué para los números de un solo bit (- 0) == 0 y (- 1) == 1, mientras que (~ 0) == 1 y (~ 1) == 0. Y también, para calcular su negación para números de múltiples bits en un código adicional, es suficiente invertirlo en bits y agregar uno: - a == ((~ a) + 1).

Continuación - partes

2.3 ,

2.4 ,

2.5 .

Toda la lección se llevó a cabo bajo Linux, más precisamente bajo Lubuntu 18.04 con Intel FPGA Quartus II instalado en él. Lubuntu se cargó con SSD en los que también se instaló Intel FPGA Quartus II Lite Edition 18.1. Para iniciar desde el SSD solo necesita conectarlo al puerto USB 3.0, encender la computadora y presionar F12. Luego ingrese al menú y diga "cargar desde USB".

Aunque el software de síntesis para FPGA también está disponible en Windows, Linux es bueno por dos razones:

1. Linux puede ejecutarse en computadoras más débiles que Windows. Por ejemplo, tengo una computadora portátil con 2 gigabytes de memoria, por lo que Intel FPGA / Altera Quartus II para Windows se establece y funciona bien en Linux.

2. Todos los desarrolladores adultos de chips masivos en Apple, NVidia y otras compañías electrónicas usan Linux, que ejecuta los programas Synopsys Design Compiler, Synopsys IC Compiler, Synopsys VCS, Cadence IES, etc.

¿Por qué es mejor hacer todo en SSD de arranque y no ponerlos en las computadoras en el aula? Debido a que la instalación de software de compañías FPGA es un proceso bastante triste, y alrededor de Altera Quartus o Xilinx Vivado necesita ejecutar con una pandereta, cambiar archivos en / etc e instalar bibliotecas antiguas de 32 bits para algunos componentes, en particular, para la versión gratuita de Mentor ModelSim. Algunas bibliotecas deben compilarse a partir de códigos fuente. Hay

scripts de Stanislav Zhelnio que lo hacen todo automáticamente, pero incluso con este script, la instalación de todo en una computadora tomará un par de horas.

¿Por qué no hacer todo en máquinas virtuales? Por ejemplo con VirtualBox? Intentamos esto en la Universidad Estatal de Moscú y en otros lugares, pero pueden ocurrir fallas con la extracción de USB allí. Un SSD de arranque con Lubuntu parece la mejor opción.

Para preparar el conjunto de SSD para el taller, debe colocar todo en un SSD y luego clonarlo con un comando que le permita escribir inmediatamente en tres SSD desde uno:

time sudo dcfldd if=/dev/sdb bs=1M of=/dev/sdc of=/dev/sdd of=/dev/sde

Aquí debe saber que no todos los gabinetes SSD son compatibles con Linux, por ejemplo, Kingwin Data Star estropea los discos. Los recintos correctos son Orico y Eluteng.

Además, no recomiendo intentar reemplazar los SSD por unidades flash USB simples y descargables. Aunque también funciona en memorias USB, algunas operaciones son increíblemente lentas, causando molestias e irritación. Pero en unidades SSD cargadas con USB 3.0, todo vuela más rápido que Linux en un disco duro interno.

También intenté pegar una unidad SSD de arranque en la Mac de Apple presionando la tecla Opción en el momento del arranque, pero no funcionó. Ni a través del puerto USB 3.1 ni a través de 3.0. Parece que la Mac en el arranque no quiere entender ni el sistema de archivos Ext4 ni la tabla de particiones. ¿Hay controladores de amapola y linuxoides entre mis lectores? Sería interesante saber qué hacer (además de la opción de usar VirtualBox u otras máquinas virtuales).

Curiosamente, solo 2 estudiantes de todo el grupo usaron Linux antes del seminario. Esto es muy extraño para mí, ya que en el lugar del Ministerio de Educación de Rusia transferiría todas las escuelas rusas a Linux hace 10 años, cuando Ubuntu se volvió fácil de usar. Además de Ubuntu, se podría hacer una versión rusa especial de Linux para la educación. Windows está obstruido con virus, debe pagar regalías por ello, ¿por qué Windows es mejor que Linux para decir cursos de programación de Python? ¿O los documentos de Google no serán suficientes para los escolares, pero se necesita Microsoft Word? Simplemente no lo entiendo.

Incluso el gobierno de Corea del Sur decidió en 2020 cambiar a Linux .

En cualquier caso, en mi seminario, los escolares no tuvieron problemas con Linux, aunque, como dije, la mayoría de los escolares lo usaron por primera vez.

Al comienzo del tercer día llegué tarde porque me invitaron a dar una conferencia a la sucursal rusa de Samsung y el evento se prolongó durante 3 horas (puede descargar las diapositivas de la conferencia:

1 ,

2 ,

3 y

un artículo sobre parte del contenido ), después de lo cual tuve hambre y solo durante comiendo trigo sarraceno y olivier en Mumu (que realmente extraño en California) descubrí que mi lección en el gimnasio comenzaría en 5 minutos.

Luego llamé a Alexander Silantiev desde MIET y le pedí que comenzara la lección sin mí. El día anterior, los estudiantes comenzaron a hacer ejercicio con un indicador de siete segmentos, mostrando una letra. Ahora, si cruza la salida de una letra con un registro de desplazamiento, puede implementar la salida en un indicador dinámico de siete segmentos dinámico de varios bits y, al mismo tiempo, los estudiantes aprenderán a codificar la lógica secuencial en veril.

El plan fue un éxito: cuando ingresé al aula, algunos escolares ya escribían letras lentamente en un indicador dinámico, y para que se fusionaran en palabras, todo lo que se necesitaba era aumentar la frecuencia de generación de la señal de habilitación (habilitar) para el registro de desplazamiento:

Luego pasé la palabra a Stanislav Zhelnio

sparf de IVA Technologies, y brevemente describió cómo pasar de bloques lógicos simples a un procesador pequeño pero completamente real (ver

publicaciones de Stanislav en Habr y

schoolMIPS en GitHub ):

Continuación de la conferencia de Stanislav ZhelnioEl seminario se celebró en la Escuela de Gramática de la Universidad Rusa de Transporte (MIIT). En el seminario y antes, Irina Grunicheva y Gleb Romanov (eNano) ayudaron; Alexey Pereverzev, Alexander Silantiev y Yevgeny Primakov de MIET, Alexander Romanov de HSE MIEM y sus alumnos, Alexei Kochnov de NIIIS, League of Robots (obraz.pro), Pavel Kirichenko (ICST, Intel, autor de los libros

bhv.ru/books/book. php? id = 201192 ), Yegor Kuzmin del

Instituto de Matemáticas Aplicadas , Academia de Ciencias de Rusia, Daria Krivoruchko, una colegiala del SSC, estuvo en LYuP, Timofei Cherkasov (Academia de Tecnologías Digitales de San Petersburgo, Escuela de Ingeniería de Pensamiento LNMO), Alexander Bakerenkov y Julia Shaltaeva de la Pre-Universidad de MEP Vorontsov de MPEI, Evgeny Pevtsov de MIREA, Vitaliy Kravchenko de Nautekh, Arkady Poe Yakov y Sergey Pevchenko de MEI.

Ruslan Tikhonov de Amperka trajo componentes para ejercicios con microcircuitos de un pequeño grado de integración.

El editor Dmitry Movchan, de DMK Press, presentó a cada participante libros útiles: un grueso libro de texto completo de David Harris y Sarah Harris, Circuitos digitales y arquitectura de computadoras, y fácil lectura de A. Hideharu, Electrónica entretenida. Circuitos digitales. Manga

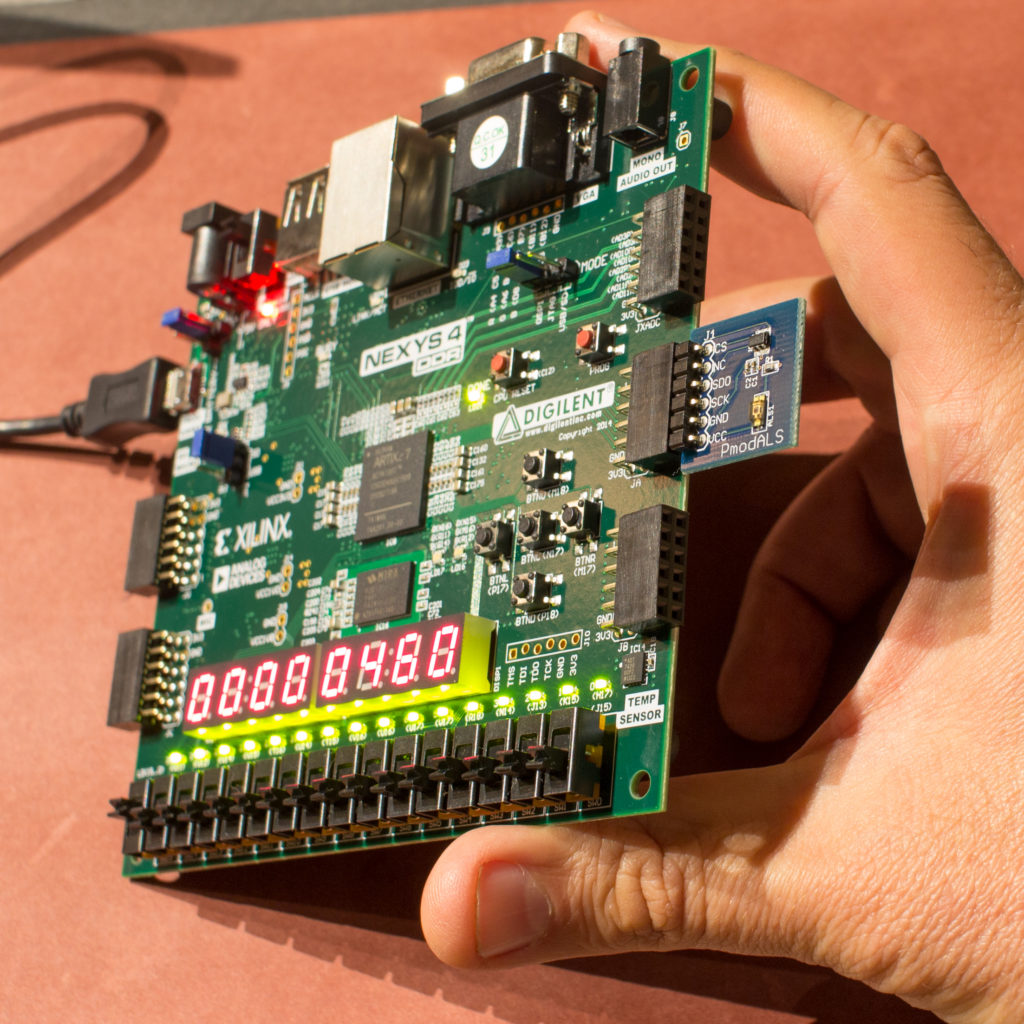

Maxim Maslov, afiliado al Instituto de Física y Tecnología de Moscú, asistió al seminario y donó tableros de FPGA a las escuelas de verano (solían decir que en Rusia hay poca caridad para la educación).

¿Qué pasará después? Y luego habrá dos eventos que ampliarán y profundizarán lo que hicimos en la RTH Grammar School. Del 8 al 26 de julio será la escuela de verano MIET en Zelenograd. Aquí hay una sugerencia para su programa. Sus primeras dos semanas constan de cinco partes:

- Los fundamentos de los circuitos digitales en microcircuitos de un pequeño grado de integración.

- Ejercicios sencillos con lógica combinacional y secuencial en la placa FPGA.

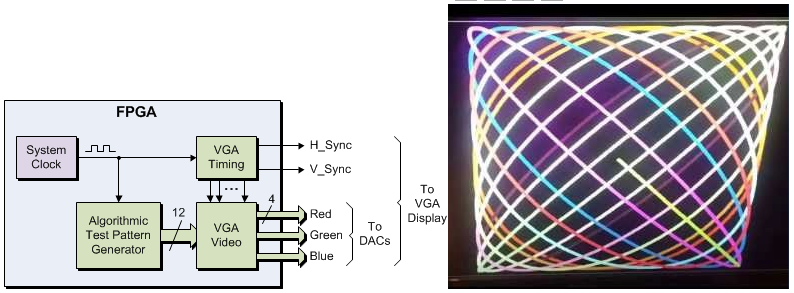

- Usando FPGAs para controlar la pantalla gráfica.

- El dispositivo y la implementación del microprocesador más simple en el FPGA.

- Proyectos individuales para crear juegos a la manera de Angry Birds simplificado, ambos basados en la máquina de estado puramente en el hardware FPGA, y con control de programa desde el procesador más simple sintetizado en el FPGA.

Pero antes de la escuela el 4 de junio habrá un seminario en Las Vegas, en el que no trataremos con el procesador de la escuela, sino con el industrial.

Programa más detallado en Zelenograd:

Semana 1. Conceptos básicos de la lógica digital.

Día 1. Circuitos integrados a pequeña escala, ejercicios de lógica combinatoria.

Día 2. Microcircuitos con un pequeño grado de integración, ejercicios con lógica secuencial.

Día 3. FPGA, ejercicios con botones, interruptores, LED, indicador de siete segmentos

Día 4. FPGA, salida de formas geométricas a VGA

Día 5. FPGA, máquina de estado para Angry Birds

Semana 2. Procesador

Día 1. Programación en lenguaje ensamblador.

Día 2. Procesador de un ciclo de la escuela MIPS.

Día 3. Interacción del procesador con la conclusión de formas geométricas en VGA.

Día 4. Conferencia sobre interrupciones y multitarea. Proyecto individual: un videojuego programado en el procesador con salida a VGA.

Día 5. Conferencia sobre el transportador. Concurso de proyectos individuales.

Semana 1. Día 1. Circuitos integrados a pequeña escala.

1.1. Ejercicios con lógica combinatoria.

1.1.1. Elemento lógico XOR en CD4070, sin botones y registros desplegables: repita la demostración.

1.1.2. Elemento lógico XOR, agregar botones y registros desplegables: repita la demostración.

1.1.3. Tarea individual: por datashit para construir una demostración de uno de los elementos lógicos AND / OR / NOT / XOR / NOR / NAND / XNOR, con dos, tres, cuatro u ocho entradas:

1.1.3.1. CD4081, Quad 2-Input Y

1.1.3.2. CD4071, Quad de 2 entradas O

1.1.3.3. CD4011, Quad 2-Input NAND

1.1.3.4. CD4001, Quad 2-Input NOR

1.1.3.5. CD4073, triple de 3 entradas Y

1.1.3.6. CD4025, triple de 3 entradas NOR

1.1.3.7. CD4082, doble de 4 entradas Y

1.1.3.8. CD4072, doble de 4 entradas O

1.1.3.9. CD4012, NAND dual de 4 entradas

1.1.3.10. CD4002, 4 entradas NOR

1.1.3.11. CD4068, 8 entradas Y NAND

1.1.3.12. CD4078, 8 entradas NOR

1.2. Indicador de 7 segmentos con un cátodo común.

1.2.1 Montar en una placa con resistencias, probar segmentos individuales.

1.2.2. Combinación con controlador de indicador de 7 segmentos, CD4511, BCD a decodificador de 7 segmentos.

1.2.3 Opción - indicador con un ánodo común. Combine con el inversor CD4069, inversor.

1.2.4. Opción: agregue 4 botones con resistencias pull-up a la entrada CD4511.

1.3. Bloques lógicos combinacionales: una tarea individual al final del día o en forma de tarea:

1.3.1. CD4532, codificador de prioridad de 8 bits

1.3.2. CD4051, Interruptor analógico simple de 8 canales, utilizado como decodificador digital

1.3.3. CD4051, Interruptor analógico simple de 8 canales, utilizado como multiplexor digital

1.3.4. CD4052, interruptor analógico dual de 4 canales, utilizado como multiplexor digital

1.3.5. CD4053, interruptor analógico triple de 2 canales, utilizado como multiplexor digital

1.3.6. CD4008, sumador combinacional de 4 bits

1.3.7. CD4063, comparador digital de 4 bits

1.3.8. CD4585, comparador digital de 4 bits

Al final del día, todos muestran quién hizo qué.

Semana 1. Día 2. Ejercicios con lógica secuencial.

1.2.1 Arme un generador de reloj basado en el chip 555. Pruebe diferentes condensadores y resistencias.

1.2.2. D-trigger en el chip CD4013, Dual D-Flip-Flop con Set-Reset.

1.2.3 Proyecto individual:

1.2.3.1. Registro de desplazamiento basado en CD4015, Registro de desplazamiento estático dual de 4 bits, entrada en serie, salida en paralelo.

1.2.3.2. Registro de desplazamiento basado en CD4035, Registro de desplazamiento de 4 etapas, entrada paralela, salida paralela.

1.2.3.3. Registro de desplazamiento basado en CD4014, Registro de desplazamiento de 8 etapas, entrada paralela, salida en serie.

1.2.3.4. Contador con salida LED CD4029, contador binario decimal arriba-abajo.

1.2.3.5. Contador con salida a un indicador de 7 segmentos a través del controlador.

1.2.3.6. Más complejo es una combinación de registros de desplazamiento CD4035 (entrada en paralelo, salida en serie) con el sumador en serie CD4038. Necesita un inversor CD4069. Antes de esto, demostraré el sumador serial CD4032 sin un inversor.

1.2.3.7. Más complejo es una combinación de registros de desplazamiento CD4014 (entrada paralela, salida serial) con el sumador serial CD4038. Necesita un inversor CD4069.

Semana 1. Día 3. FPGA, ejercicios con botones, interruptores, LED, indicador de siete segmentos

1.3.1. Un elemento lógico en la lógica combinacional es la entrada de botones, la salida a los LED.

1.3.2. La salida de una letra en un indicador de siete segmentos.

1.3.3. El multiplexor más simple es la salida de letras dependiendo de la tecla presionada. Implementación utilizando las construcciones "?", "If", "case".

1.3.4. Registro de turnos.

1.3.5. La palabra se muestra en un indicador dinámico de siete segmentos de ocho bits utilizando un registro de desplazamiento.

1.3.6. Proyecto individual, tal vez tarea para el fin de semana:

1.3.6.1. Formas en la matriz LED.

1.3.6.2. Serpiente corriendo en un indicador de siete segmentos.

1.3.6.3. Generación de señal de frecuencia de sonido, órgano de sonido.

1.3.6.4. Entrada desde un teclado de 16 botones.

1.3.6.5. Código de bloqueo: reconocimiento de una secuencia de teclas por una máquina de estado.

1.3.6.6. Integración con un sensor telémetro.

1.3.6.7. Integración con encoder angular.

Día 4. FPGA, salida de formas geométricas a VGA

Día 5. FPGA, máquina de estado para Angry Birds

Semana 2. Procesador

Día 1. Programación en lenguaje ensamblador.

Día 2. Procesador de un ciclo de la escuela MIPS.

Día 3. Interacción del procesador con la conclusión de formas geométricas en VGA.

Día 4. Conferencia sobre interrupciones y multitarea. Proyecto individual: un videojuego programado en el procesador con salida a VGA.

Día 5. Conferencia sobre el transportador. Concurso de proyectos individuales.

Semana 3. Radio programable. El programa de bloques consta de tres partes principales:

- Los fundamentos de la electrodinámica y la propagación de ondas de radio (parte teórica);

- El principio de funcionamiento de la ruta del transceptor (teoría y práctica);

- Los fundamentos del procesamiento de señales digitales: filtrado, análisis espectral (teoría y práctica).

Día 1. Fundamentos teóricos de la electrodinámica y la propagación de ondas de radio. El diagrama estructural de la ruta de transmisión, las funciones de los componentes. Señales (armónicas, rectangulares). Práctica de señales usando NI Elvis.

Día 2. Transferencia de señales a una frecuencia alta. Justificación matemática para la transferencia de frecuencia usando Matlab. Ejercicio práctico en transferencia de frecuencia usando NI Datex.

Día 3. Amplificación y emisión de señales. Practique usando NI Datex. Demostración de la directividad de las antenas.

Día 4. Filtrando la señal. Practique usando NI Datex. Filtrado digital de señales en Matlab

Día 5. Transferencia de señales a baja frecuencia. Practique usando NI Datex. Resumiendo el material cubierto, resumiendo.

Sobre el resto de los días de la escuela, habrá más detalles en una publicación separada, después de discutir esto en el comité organizador de la escuela de verano. Si desea participar en la escuela de verano en MIET en Zelenograd como estudiante o instructor, los

organizadores acaban de publicar los contactos y la inscripción . Si es estudiante, es importante que para julio complete completamente los tres módulos del curso en línea de Rosnanov (

"Del transistor al microcircuito" ,

"El lado lógico de los circuitos digitales" y

"El lado físico de los circuitos digitales" ). La práctica será difícil, y no podremos detenernos para averiguar qué ciclo está el valor en la entrada o salida del disparador D. Esto no cabe en su mente de inmediato, pero si toma un curso en línea, será más fácil para usted.

Algunos detalles

sobre el seminario en Las Vegas el 4 de junio :

No suele suceder que un seminario de ingeniería, desarrollado inicialmente para Rusia y probado en Rusia (incluido MIPT), Ucrania y Kazajstán, comience en Las Vegas, en una conferencia de automatización de diseño electrónico. En Rusia y Ucrania se llamó MIPSfpga Workshop, y en la Design Automation Conference se llamó MIPS Open Developer Day. Ven el 4 de junio en el Centro de Convenciones Embassy Suites by Hilton en 3600 Paradise Road, Las Vegas, y participarás en un espectáculo que estudiantes y maestros de la Universidad Estatal de Moscú, el Instituto de Física y Tecnología de Moscú, el Instituto de Física de Ingeniería de Moscú, Zelenograd MIET, San Petersburgo ITMO, TSU de Tomsk, KPI de Kiev, Almaty AlmaU y parcialmente la Universidad Nazarbayev en Astana.

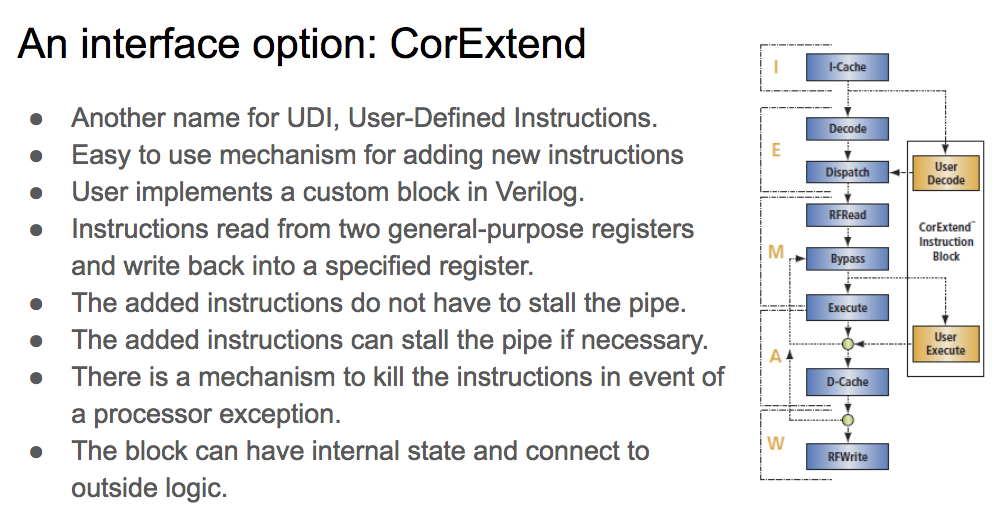

MIPSfpga es un paquete que contiene el núcleo del procesador en el código fuente de Verilog, que puede cambiar, agregar nuevas instrucciones, observar la operación de caché y canalización, construir sistemas multiprocesador, cambiar software y hardware al mismo tiempo, etc. En la nueva versión del seminario, agregará un coprocesador al procesador para acelerar los algoritmos de inteligencia artificial.

Además, en la nueva versión del seminario mostraremos cómo configurar el kernel desde el paquete MIPS microAptiv UP e insertarlo en el enlace MIPSfpga. Cuando se configura, puede crear opciones de procesador exóticas, por ejemplo, un procesador con 16 conjuntos de 32 registros. Puede cambiar automáticamente estos conjuntos al ingresar una interrupción y, por lo tanto, cambiar rápidamente el contexto sin guardar / restaurar el contexto desde la memoria, que en RTOS ordinario toma alrededor de mil ciclos.

MIPSfpga no está destinado a ser inyectado en un objeto desde cero absoluto. Para su uso fructífero, es necesario que el estudiante ya conozca los conceptos básicos de los circuitos digitales, pueda programar en C y en ensamblador, y también presente los conceptos de microarquitectura: transportador, conflictos de tuberías, etc. Esto es lo que se está estudiando en schoolMIPS, que utilizamos en Zelenograd.

Aquí hay una diapositiva sobre el mecanismo para agregar instrucciones al procesador MIPS microAptiv UP:

En un seminario en Las Vegas el 4 de junio, y probablemente en una escuela de verano para jóvenes ingenieros electrónicos, que se llevará a cabo del 8 al 26 de julio en MIET en Zelenograd, mi hija Elizabeth Panchul me ayudará (si recibe una visa a tiempo). Como Elizabeth es semi-rusa-semi-rusa / ucraniana, solo habla inglés. Por lo tanto, los instructores rusos (estudiantes o estudiantes graduados del Instituto de Física y Tecnología de Moscú, la Universidad Estatal de Moscú, etc., que están listos para ayudarnos con Elizabeth y el MIET en la conducción de la escuela) pueden aprender el acento correcto del inglés de ella, y ella de ellos, los conceptos básicos del ruso. Además de estudiar Verilog, MIPS, arquitectura, microarquitectura y organizar DMA en la memoria cuando se muestra en una pantalla gráfica:

¡Te esperamos en todos los seminarios, así como en los comités para la creación de sus programas!