Posible foto de 10 nm IceLake. Fuente

Posible foto de 10 nm IceLake. FuenteEstán sucediendo cosas extrañas en el mercado de procesadores. El líder mundial en la persona de Intel ha estado luchando por quinto año en intentos de cambiar al proceso de fabricación de 10 nm. Inicialmente, anunciaron la transición a 10 nm en 2015, luego en 2016, 2017 ... En el patio de 2019, y a 10 nm de Intel en la serie todavía no está allí. Bueno, no, hay algunas muestras experimentales / de ingeniería, pero un alto rendimiento es un problema.

Ya se espera

una transición real

antes de 2022 .

En realidad, esta fue la razón de la escasez de procesadores Intel en el mercado. Para superarlo, la compañía amplía la producción de procesadores modificados de 14 nm (el mismo lago solo de perfil) e incluso vuelve a 22 nm. Parece que la regresión es obvia. En este momento, Samsung coreano, TSMC taiwanés y AMD, que se unieron a ellos con la plataforma ZEN 2, informan sobre la introducción de hasta 7 nm y están a punto de cambiar a 5 nm. Sacaron la "Ley de Moore" del polvoriento gabinete y la declararon más viva que todos los vivos. Pronto habrá 3 nm, y 2 nm, e incluso 1 nm (

sic! ) - pourquoi pas?!

Que paso ¿

Asiáticos realmente

astutos vencieron a los

malditos pendos en una industria clave?

¿Puedo abrir champaña?Descargo de responsabilidad: Encontré

este artículo por accidente y me sorprendió mucho cuán competente y detalladamente revela los problemas de la microelectrónica moderna, en particular, la muerte de la ley y el marketing de Moore. Una vez yo mismo incursioné en escribir artículos sobre la

fabricación de chips , y

en la serie de artículos "Inside Look" incluso miré dentro de ellos, es decir, El tema es extremadamente interesante para mí. Naturalmente, me gustaría que

el autor del artículo original lo publicara en Habré, pero en relación con el empleo, me permitió transferirlo aquí. Desafortunadamente, las reglas de Habr no permiten copiar y pegar directamente, así que agregué enlaces a fuentes, imágenes y un poco de mordaza e intenté enderezar un poco el texto. Sí, y conozco y respeto los artículos (

1 y

2 ) sobre este tema de

amartology .

Entonces, resolvamos el problema juntos. Intentaremos tanto como sea posible profundizar en la física y la tecnología, y no profundizar en los matices (¡cuyo nombre es legión!). La descripción a continuación es simplificada y algunas veces esquemática. Escribir comentarios, trataremos de discutir constructivamente.

Prólogo

"No todo es tan sencillo ..." solía decir la hija de un oficial. Si nos fijamos en la densidad de los transistores, es casi lo mismo en la tecnología de 14 nm de Intel y en la tecnología de 7 nm de TSMC (

¡oh! ). E incluso el retroceso de Intel a 22 nm no tuvo un gran impacto en el rendimiento. Que diablos Según todas las reglas, la transición de la tecnología de 14 nm a 7 nm debería aumentar la densidad de los transistores hasta 4 veces. ¡Y esto está de acuerdo con los preceptos de Gordon Moore, cuyo

50 aniversario de la ley se celebró recientemente, y en la nariz está el 55 aniversario!

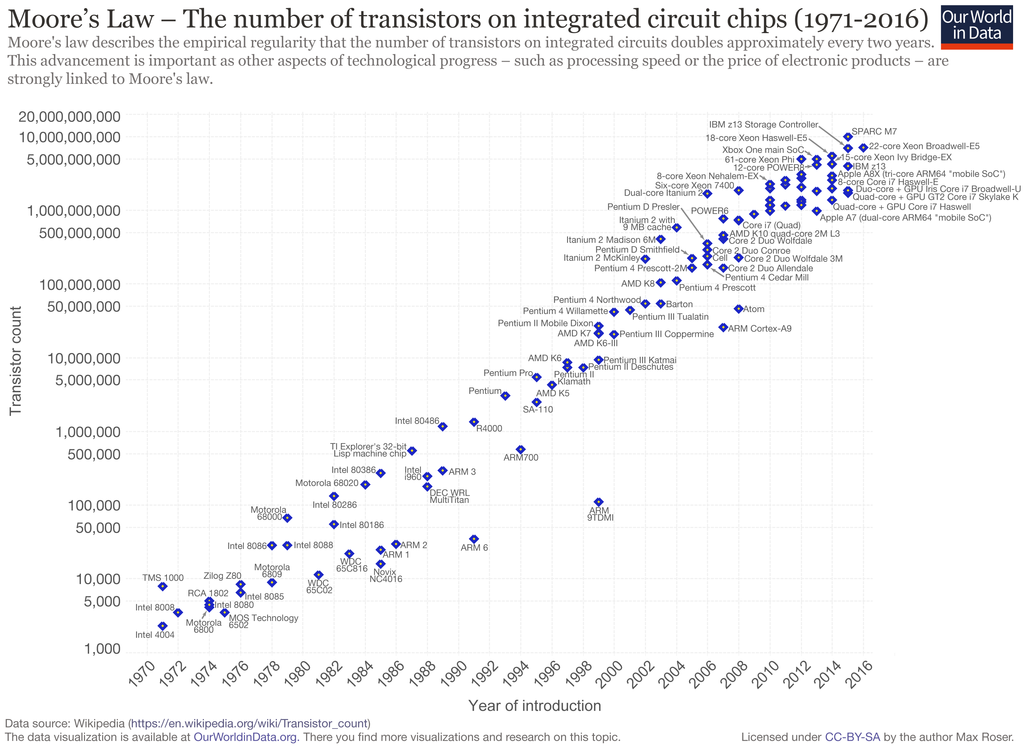

La ley de Moore fundida en hierro. Como puede ver, hemos estado "marcando" en el lugar durante unos 5 años.

La ley de Moore fundida en hierro. Como puede ver, hemos estado "marcando" en el lugar durante unos 5 años.Al mismo tiempo, se están haciendo declaraciones mixtas. Algunos sostienen que la "Ley de Moore" es más relevante que nunca, y la microelectrónica se desarrollará como antes. Científicos, diseñadores e ingenieros brillantes superarán cualquier limitación, incluso las leyes de la física. Las personas requieren nuevos logros y no tardarán mucho.

Otros dicen que todos los muchachos han alcanzado los límites físicos, vamos a lamer lo que es, pero esto es normal. Esto ha sido advertido por mucho tiempo. Entonces, el jefe de NVIDIA

dijo durante CES 2019 que la ley de Moore está muerta y que ahora el vector (Huang no debería ser un vector, sino un tensor) del desarrollo debe ser cambiado. El especialista en litografía de AMD y GlobalFoundries

está de acuerdo con él.

De hecho, todos estos estándares tecnológicos de unidades y decenas de nanómetros se han divorciado de las dimensiones físicas y se han convertido en más elementos de marketing. Al menos los últimos 15 años: después de la transición de 130 nm a 90 nm. Fue entonces cuando por primera vez se enfrentaron limitaciones no tecnológicas, sino físicas básicas. Los expertos, por cierto, hablaron de esto, pero su voz apagada fue ahogada por las transmisiones de bravura de los vendedores que pretendían que no había pasado nada, que todo iba a su manera, de acuerdo con los preceptos de

Leni ... Dr. Moore.

Desafortunadamente, para los especialistas en marketing, y quizás afortunadamente para nosotros, la ley de Moore no es una ley de la naturaleza, sino una observación empírica formulada en 1965 por uno de los fundadores de Intel, Gordon Moore. Según sus observaciones, surgió una nueva serie de microcircuitos con un intervalo de un año, mientras que el número de transistores en ellos aumentó aproximadamente 2 veces. En 1975, la ley fue enmendada; según ella, la duplicación debería ocurrir cada 24 meses. Desde entonces, durante casi 40 años, la ley de Moore se ha elevado al rango de icono y pancarta para los fabricantes de microelectrónica digital, que a veces se tuercen (24 meses se convirtieron en 36, ahora estancados, ver la imagen de arriba).

En el camino, surgieron varias limitaciones tecnológicas que ralentizaron el proceso (la misma transición a través del límite de difracción). O avances que dieron un fuerte aumento en la miniaturización. Para un observador externo, todo parecía un crecimiento estable en pleno cumplimiento de la ley de Moore, y no menos importante los esfuerzos de los vendedores.

Física de "Su Majestad Silicio"

Comenzaré con la oda de silicio.

El silicio es el regalo del cielo para los fabricantes de microelectrónica. No solo eso, literalmente, bajo los pies, el silicio también es un buen semiconductor con parámetros muy adecuados (en términos de la combinación de características eléctricas, energéticas y físicas). El silicio puro es casi un dieléctrico; la conductividad está completamente determinada por la concentración de impurezas. Tiene una alta conductividad térmica, es tecnológicamente avanzado y es resistente a ambientes agresivos.

Likbez para principiantesEl silicio a temperaturas normales es un semiconductor con una red cristalina cúbica. 4 electrones externos de átomos de silicio están "socializados", es decir Pertenecen a todos los átomos de la red cristalina. No son libres, pero no están rígidamente unidos a su átomo. Esta es una característica de los semiconductores. Durante un tiempo, estos electrones giran alrededor de su átomo, luego se transfieren al vecino y los vecinos entran en su lugar. Por lo tanto, los electrones externos (de valencia) viajan aleatoriamente de un átomo a otro a través del cristal (

nota: no es así, los electrones en sí no viajan, solo transfieren energía a través de la interacción entre ellos ). Ocasionalmente, algún tipo de electrón se separa por completo del átomo y comienza (casi) a moverse libremente entre la red cristalina. En su lugar, permanece un ion de silicio positivo con una vacante de electrones sin llenar: un "agujero". La próxima vez que los electrones se envían desde un vecino, la vacante se llena, pero aparece en el vecino, luego en su vecino, etc. El agujero también comienza a viajar al azar a través del cristal.

Si ahora aplicamos un campo eléctrico, un electrón libre volará de menos a más. Los electrones de valencia también están sujetos a la acción del campo y comienzan a llenar rápidamente las vacantes hacia el lado positivo, y las vacantes de los agujeros fluirán hacia el lado negativo. Este comportamiento parece que un agujero es un portador de carga libre, como un electrón libre, solo con una carga positiva. El comportamiento del agujero se describe mediante las mismas fórmulas que el electrón, corregido para

una "

masa efectiva " mayor. Por lo tanto, a menudo no se vaporizan y, por simplicidad, consideran que los agujeros son partículas elementales ordinarias con una carga positiva.

A temperatura ambiente, un par de agujeros de electrones por billón de átomos de silicio (concentración

10-12 ), el silicio puro a temperatura ambiente es un aislante (condicionalmente: los electrones y los agujeros se aniquilan entre sí demasiado rápido, sin tiempo para llegar al final del cristal).

Si un átomo con 5 electrones externos, por ejemplo, fósforo, se introduce en la red de silicio, entonces se incluye en el intercambio de 4 electrones, y el quinto electrón se libera. Obtenemos iones de fósforo positivos y un "gas de electrones" incrustado en silicio a partir de electrones libres. La conductividad del silicio con tal impureza aumenta linealmente; las concentraciones de un átomo de fósforo por millón de átomos de silicio (

ppm ) ya cambian drásticamente las propiedades eléctricas. Una mezcla de fósforo se llama donante, y el semiconductor en sí se llama

conductividad de tipo N. Además del fósforo, puede ser arsénico o antimonio.

Ahora agregamos átomos de silicio puro con 3 electrones externos, por ejemplo, boro. También se incluye en el intercambio de 4 electrones, pero solo puede dar 3 electrones. En los átomos de silicio vecinos, aparece un "agujero" y comienza un viaje a través del cristal. Obtenemos iones de boro negativos y un gas de pozo cargado positivamente. Tal impureza se llama aceptor, y el semiconductor es

de tipo P. Además del boro, los aceptadores son aluminio, galio e indio.

Por cierto, el silicio extremadamente puro (por lo que es un aislante) es increíblemente difícil de obtener. La presencia de boro

siempre convierte al silicio en un semiconductor de tipo p.

Una ventaja para el silicio es su óxido - dióxido de silicio SiO

2 . Es un dieléctrico casi perfecto, con alta resistencia y dureza, resistente a todos los ácidos excepto el fluorhídrico (HF). Al mismo tiempo, el ácido fluorhídrico no disuelve el silicio en sí mismo, no puede tener miedo de encurtir el exceso. Se forma una delgada película de óxido en la superficie del silicio incluso a temperatura ambiente (naturalmente, en el aire). Para obtener películas de óxido gruesas, se calienta silicio o se usa deposición a baja temperatura de un gas que contiene silicio. La precipitación se usa cuando las capas ya están depositadas en el cristal, y el calentamiento dará como resultado una "mancha" de la topología.

Tedio de un químico, una vez al año del Sistema Periódico: un paso a la derecha - P, fósforo, óxido forma ácido fosfórico, a la izquierda - Al, aluminio, metal, arriba - C, carbono, óxido - gas, abajo - Ge con una baja prevalencia en la corteza terrestre (kilo ahora cuesta ~ 1k $).

A pesar de las constantes conversaciones sobre el final inminente de la era del silicio y la transición a otros semiconductores, por ejemplo, las estructuras A

3 B

5 (aresenida de galio, fosfuro de galio o nitruro de galio), carburo de silicio, diamante,

grafeno y otros, ya que tienen una movilidad de electrones más efectiva y agujeros, menor dependencia de la temperatura, mayor conductividad térmica, reina el silicio en microelectrónica de masas.

Sí, para A

3 B

5 es posible crear

heterouniones . Esto es cuando las áreas dentro del transistor difieren no solo en el tipo de conductividad, sino también en la estructura física, lo que brinda oportunidades adicionales. En igualdad de condiciones, los microcircuitos de nitruro de galio pueden funcionar a una frecuencia más alta, son resistentes a altas temperaturas y proporcionan una mejor disipación de calor. Pero aunque estos materiales se usan solo para elementos discretos y pequeños microcircuitos. Para microcircuitos grandes, la complejidad de la tecnología hace que sus precios sean más altos que el silicio. Sí, y no se obtiene "otro igual". Por lo tanto, los microcircuitos alternativos sin silicio tienen una especialización estrecha.

MOSFET

Considere el ladrillo principal de los microcircuitos digitales: un transistor de campo plano (plano) con un canal inducido. Él es

MOS (semiconductor de óxido de metal), él es MIS (semiconductor de dieléctrico de metal), él es MOS (semiconductor de óxido de metal), él es

MOSFET .

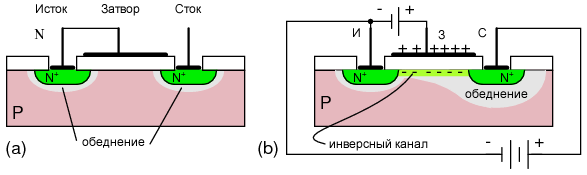

Vista esquemática en sección de un transistor de canal n

Vista esquemática en sección de un transistor de canal nDescripción de los principios del trabajo.Tenemos un sustrato de silicio de conductividad tipo p. Creó 2 capas de tipo n: fuente y drenaje. Análogos del emisor y colector en

transistores bipolares . Entre ellos, un electrodo separado del silicio por una capa dieléctrica (generalmente óxido de silicio) es una puerta. El área debajo del obturador se llama base. Si aplicamos un voltaje entre la fuente y el drenaje, no habrá corriente, ya que habrá una

unión pn con polarización inversa entre ellos: el transistor está cerrado. Esquemáticamente, este es un análogo de un diodo de bloqueo. Cuando se conecta correctamente, esta es una transición entre la base y el drenaje.

Ahora aplique un voltaje positivo a la puerta. Un campo eléctrico atraviesa el óxido, penetra el silicio, repele los agujeros (+) de la capa superficial del agujero y atrae los electrones libres (-). El último en el sustrato de tipo p, aunque pocos, están presentes. A cierto voltaje en la puerta, en la capa superficial de electrones se convierte en algo más que agujeros. Se produce la inversión y aparece un canal de tipo n debajo de la capa de óxido. Una corriente fluirá a través de él desde la fuente hasta el drenaje: el transistor está abierto. Un transistor abierto es una unidad lógica, una cerrada es un 0. lógico Bueno, o viceversa, dependiendo de la implementación.

Para los transistores de canal p, las regiones n y p se intercambian y el transistor se abre a un voltaje de puerta negativo.

Las ventajas de los transistores MOS son la compacidad. Pero también hay un serio inconveniente: el alto consumo de energía, ya que en estado abierto una corriente pasa a través del transistor. Por lo tanto, desde la década de 1970,

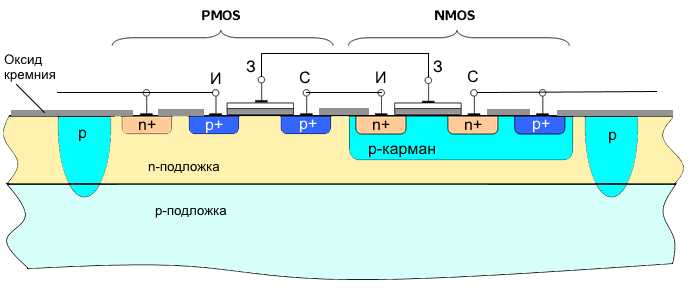

los transistores CMOS (

MOS complementarios ) han dominado la tecnología digital. Estos son transistores de canal p y canal n conectados en serie, con puertas combinadas. Usualmente hecho en una celda.

Si alimentamos las puertas plus, el transistor del canal n está abierto, el canal p está cerrado. No hay corriente directa, menos en la salida. Si alimentamos la puerta con un signo menos: el transistor del canal n está cerrado, el canal p está abierto. No hay corriente continua de nuevo, más salida. Es decir El elemento también funciona como un inversor.

Esta es la tecnología con mayor eficiencia energética. En un estado estático, el elemento no consume nada (excepto la corriente de fuga parásita), solo se consume la corriente de conmutación. El consumo de energía es casi directamente proporcional a la frecuencia del chip (el número de ciclos de recarga). El bajo consumo de energía y la compacidad determinaron el dominio de la tecnología CMOS en la electrónica digital.

Los circuitos de transistores bipolares inicialmente proporcionaron un mayor rendimiento, pero fueron más complejos, ocuparon más espacio y consumieron un orden de magnitud más energía. Debo decir que la elección a favor de CMOS valió la pena. Sería casi imposible obtener características como los procesadores actuales en otras tecnologías. Y aunque las alternativas no son visibles en el horizonte.

Características de topología

La topología del chip puede representarse convencionalmente como una hoja de papel grande en una celda, donde los límites de las regiones se dibujan a lo largo de las líneas, y el tamaño tecnológico es el tamaño de la celda. De hecho, para elementos no críticos, también puede sangrar media celda (la regla de dos lambdas), pero estos son matices.

Diseño detallado de topologíaVolvamos mentalmente a fines de la década de 1980, cuando las tecnologías aún eran simples y comprensibles. Considere un par real de transistores CMOS. Windows n + y p + están altamente dopados (1 átomo de impureza por varios cientos o incluso decenas de átomos de silicio), es decir el nivel de impurezas es un orden de magnitud mayor que solo n y p.

Supongamos que nos dieron TK para dibujar la topología de un par de transistores en un bolsillo aislado. Como no habrá grandes corrientes a través de los transistores, calcularemos en función del tamaño tecnológico más pequeño posible, la llamada autorización técnica. Llámalo d.

Perfil

Perfil Vista superior

Vista superiorComencemos con la ventana de contacto para la fuente del transistor de canal n

(1) . Lo hacemos lo más pequeño posible

d * d .

La fuente

(2) tendrá el tamaño

3d * 3d (debe retroceder al menos desde los bordes de la ventana).

La base

(3) está hecha del ancho mínimo

d .

Además, el stock

(4) con su ventana de contacto, también

3d * 3d .

El último elemento es la zona de alta aleación

(5) para el contacto con la base p, y también

3d * 3d . Es necesario para igualar el voltaje de la fuente y la base, de modo que no se produzca la aparición espontánea del canal.

Dibuje los bordes del bolsillo p

(6) , otro

d de las ventanas dibujadas. El tamaño de la ventana p es

5d * 13d .

A continuación dibujamos un transistor de canal p. Hacemos este arreglo para aproximar todo el elemento a una forma cuadrada; es más fácil de ensamblar.

Cambiamos la ubicación de la fuente y el drenaje. Esta disposición minimiza la longitud de las pistas metálicas de contacto. Comencemos con la ventana de contacto para el drenaje

(7) , el tamaño es mínimo -

d * d .

El drenaje

(8) será

3d * 3d , la base

(9) es de ancho

d y está en línea con la base del transistor de canal n. La fuente

(10) y el área de contacto altamente aleada a la base

(11) también serán

3d * 3d .

El último tamaño es la sangría mínima a la ruta de división

(12) , otro

d .

Total recibió el tamaño del par de transistores

11d * 15d . La pista separada en nuestro caso es otra región de tipo p, que con un sustrato n forma una unión pn con polarización inversa.

Hay otra opción para el aislamiento con un dieléctrico: dióxido de silicio SiO

2 o zafiro Al

2 O

3 . La última opción es preferible, pero notablemente más cara. En este caso, las áreas se pueden formar cerca de la ruta de división y la corriente de fuga entre las celdas será cero. Típicamente, el ancho de la pista de separación es ligeramente mayor que el grosor de la capa epitaxial (más sobre esto a continuación) y es igual a

2d .

El tamaño efectivo total de la celda en el medio de las rutas divisorias es

13d * 17d .

Luego, encima del óxido, dibuje un obturador

(1) , retire el área de contacto

(2) del obturador más cerca de la ruta divisoria y forme una ventana de contacto

(3) .

La etapa final es la metalización y las rutas de contacto

(4) . El aluminio se usó originalmente como material de la puerta y las rutas de contacto (aunque el aluminio todavía se usa

en algunos dispositivos ), luego la puerta se hizo de silicio policristalino altamente aleado y las rutas de contacto de cobre.

Supongamos que vivimos en una tecnología de proceso de

3 micras . Entonces, nuestras dos celdas de transistores

11d * 15d , como se muestra arriba, tendrán un tamaño de

33 * 45 micras . Pero luego tuvimos problemas, cambiamos a una nueva tecnología de proceso de

1,5 micras . El tamaño de nuestra celda se convirtió en

16.5 * 22.5 micras . Y donde solía caber una celda, ahora caben hasta cuatro. , ( ). , . . .

, . .

( )? .

(

). , (

.: , () , , , , .

CorneliusAgrippa :

, , (, ). , ). (boule) 200 300 , (

aka wafers ) 0,5-0,7 . . 450 , . ( , ).

, — . : , (SiCl

4 ). . , . p- n-. n- p-. .

, , p-, . , , , .

.

, 700 .

, , . . , , . , . , .

. , , . , . , , . .

, . , , . . , . , , .

, , ,

.

tnenergy .

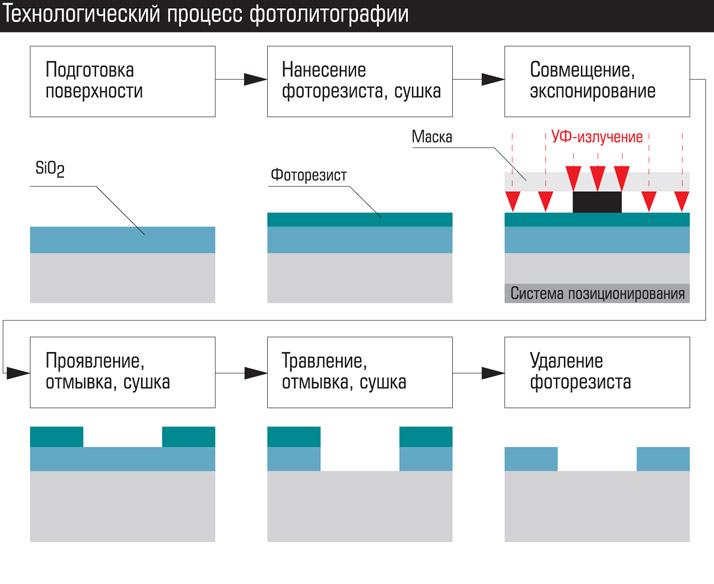

– . . ().

:

- .

- – . , .

- . – . , , p- . ( .: -) .

- . . , ( ) ( ). .

- – .

- . . , , ( shadowing effect).

- .

Al final de la operación, obtenemos una placa con porciones de óxido eliminadas, que pueden enviarse para difusión, implantación de iones o deposición de metal (

nota: o electrodeposición). Después de crear la capa, el óxido generalmente se graba en toda el área de la placa y se deposita una nueva.

Windows crea de ancho a estrecho. En nuestro caso, la secuencia será la siguiente: áreas de separación, bolsillos p, capas p +, capas n +, ventanas de contacto con metalización, aplicación del obturador, áreas de contacto del obturador, la primera capa de pistas metálicas con áreas de contacto debajo de la segunda capa, la segunda capa de metalización, etc. . En los procesadores modernos, la metalización es de hasta 10-15 capas.

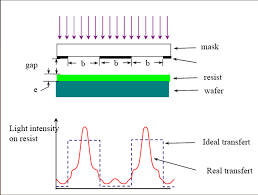

La fotolitografía de contacto se utilizó en los albores de la microelectrónica. Ahora lo principal es la fotolitografía de proyección. Esto es cuando se colocan un sistema de lentes y espejos entre la fuente de radiación y la fotomáscara para crear un haz de fotones cada vez más estrecho. En la figura a continuación se muestran esquemáticamente diferentes métodos de fotolitografía: fotolitografía de contacto, con un espacio, proyección a través de lentes, espejo de proyección.

Las ventajas de la fotolitografía son alta velocidad y bajo costo. Toda el área de la placa con todos sus microcircuitos se expone a la vez, y el proceso lleva varios minutos. O un cuadrado de varios microcircuitos seguido de un cambio de placa.

Además de la fotolitografía, existen otros tipos: electrónicos, de rayos X e iónicos. Lo más interesante es la litografía electrónica (por ejemplo, el proyecto Mapper, sobre el que

escribió BarsMonster ).

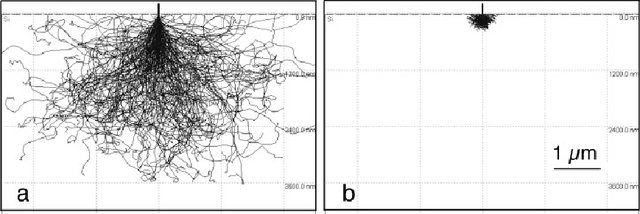

Con la litografía electrónica, la exposición de la resistencia no se realiza por la luz, sino por un haz de electrones. En su forma más simple, se asemeja a la formación de imágenes en tubos de imágenes

CRT . De todos los tipos de litografía, es la litografía electrónica que proporciona la imagen más clara y la resolución más alta. La desventaja es el largo tiempo de exposición. En las tecnologías modernas, el haz de electrones tiene un grosor de unos pocos nanómetros e incluso fracciones de nanómetro, y el diámetro de la placa es de 300 mm. Naturalmente, no se usa un solo paquete, sino decenas de miles controlados por una computadora. Pero se requiere un flujo de electrones total muy poderoso. A modo de comparación, la energía de la radiación UV cuántica es de varios

eV , la energía del electrón en el haz es de varios miles de voltios de electrones.

Además, los electrones están cargados eléctricamente y se repelen entre sí, lo que conduce a una divergencia del haz. Por supuesto, es posible aumentar la velocidad de los electrones, pero luego perforarán la resistencia o se reflejarán a alta velocidad en direcciones arbitrarias, causando radiación secundaria (

electrones secundarios ) y, en consecuencia, exposición. Todo esto limita el uso de la tecnología.

La litografía electrónica se usa para crear fotomascaras. El tiempo de exposición para una fotomáscara es de varios días. Por lo tanto, la fotolitografía domina en la producción de microcircuitos.

Un conjunto moderno de máscaras fotográficas para un procesador cuesta decenas de millones de dólares. No es sorprendente, dado que los procesadores modernos contienen miles de millones de transistores, y hay cientos de procesadores en la placa. Además, las ventanas en la moderna máscara de fotoma no son solo agujeros en el material, sino a menudo otros materiales con propiedades ópticas específicas. Un conjunto real de máscaras fotográficas consta de docenas de máscaras. En los últimos procesos de fabricación, más de 50 (

sic! ).

Pero te permiten estampar microchips como pasteles calientes. Durante su vida útil, un conjunto de plantillas de fotos le permite obtener cientos de miles o incluso millones de microchips en la salida.

Entonces, ¿qué limita el tamaño de la tecnología de proceso?

Se pueden distinguir 4 grupos de factores condicionalmente:

- Hardware y tecnología. Asociado con la resolución de hardware.

- Física de procesos tecnológicos. Está determinado por las limitaciones físicas de un proceso en particular, que puede ser eludido por un cambio en la tecnología o los materiales.

- Física Estas son limitaciones que no se pueden eludir, pero su impacto se puede minimizar.

- Extrema física

Limitaciones de hardware y tecnología

Este tipo de limitación fue decisivo en las primeras etapas de la microelectrónica. Principalmente se refiere a la producción de "salas limpias", equipos sofisticados para procesos técnicos, instrumentación (que es importante para el control de calidad de los productos). Por ejemplo, la fotolitografía requiere una óptica ultraprecisa, microscopios potentes, mecanismos para combinar máscaras y placas con una precisión de fracciones de nanómetros, una atmósfera ultrapura o vacío durante la exposición, etc. Es necesario resistir con precisión los parámetros de los procesos tecnológicos: temperatura, duración, composición de la atmósfera, potencia de radiación, preparación de la superficie.

Ahora la precisión del equipo no es un factor limitante. No porque sea un problema simple. Es suficiente mirar un diagrama de una proyección moderna o una fotolitografía de espejo para comprender el nivel de complejidad. Pero aquí es realmente el caso cuando no hay barreras para diseñadores e ingenieros talentosos.

Los problemas con la tecnología suelen ser relevantes en la primera serie. Con un cambio en la norma del proceso técnico, cambian no solo las dimensiones horizontales, sino también las verticales, y la concentración de impurezas, y las proporciones de las zonas activas. Y ahora, con cada nuevo paso, la física de los procesos también está cambiando. Naturalmente, todos los parámetros se calculan y modelan preliminarmente, pero la realidad siempre hace ajustes. Por lo tanto, para la primera serie, el rendimiento del 3% de los circuitos adecuados (97% defectuoso) se considera la norma. Gradualmente, los procesos tecnológicos se optimizan y el porcentaje de rendimiento adecuado para la última serie supera el 90%.

Física de procesos tecnológicos.

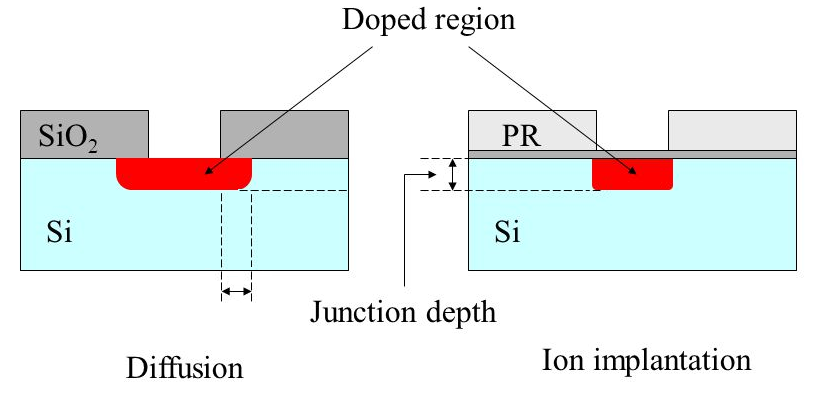

Durante más de 30 años, hasta hace poco, estos factores fueron los limitantes. Ya he enumerado algunas de estas limitaciones: la entrada de impurezas debajo del óxido durante la difusión, roer el óxido debajo de la fotorresistencia durante el grabado y la erosión de las capas ya depositadas durante los procesos térmicos.

Los métodos de solución también se describen parcialmente.

La difusión fue reemplazada por implantación de iones. Además, para las capas más pequeñas, se cambió el material de impureza: en lugar de fósforo, se usa arsénico, en lugar de galio boro. Sus átomos son más grandes y pesados, por lo tanto, se disuelven peor en silicio a las mismas temperaturas (y lo más importante, ¡es más difícil que se difundan!). Para la implantación de iones, esto no es importante, pero con el calentamiento posterior, tales capas se erosionan mucho más débilmente.

La producción de óxido por calentamiento ha reemplazado la deposición catalítica a baja temperatura del gas. Se usa calefacción, pero solo al principio, mientras el cristal está limpio. En algunas operaciones, se utilizan nitruro de silicio (Si

3 N

4 ) o capas sucesivas de óxido y nitruro en lugar de óxido.

El grabado ácido líquido se cambió por grabado iónico. El ácido se usa solo para eliminar el óxido de toda el área.

Otro problema fue la producción de óxido ultra puro para un dieléctrico de compuerta. Este óxido permanece como un elemento de trabajo en el chip y tiene altos requisitos de pureza y uniformidad. El espesor del óxido en algunos lugares es inferior a 10 capas atómicas. Un pequeño defecto conduce a un pinchazo o avería. Esto da un cierre eléctrico del obturador a la base y la falla del elemento. Durante algún tiempo, se usó una alternancia de una capa de óxido y nitruro de silicio. En la tecnología de 90 nm, se utilizó óxido de hafnio HfO

2 como dieléctrico de puerta.

Por cierto, durante la URSS fueron precisamente los problemas con la obtención de óxido de alta calidad lo que ralentizó la transición a CMOS. De ahí la búsqueda de caminos alternativos y el retraso general en la microelectrónica digital.

La operación más crítica es la fotolitografía. Tanto es así que hasta ahora muchos han puesto un signo igual entre la resolución de todo el proceso técnico y la resolución de la fotolitografía. Y el principal problema de la fotolitografía desde fines de la década de 1980 es la difracción de la luz. Más precisamente, la radiación ultravioleta, aunque el principio es el mismo. No sería una exageración decir que durante 30 años la lucha para reducir el tamaño de los procesos tecnológicos fue principalmente una lucha contra la difracción.

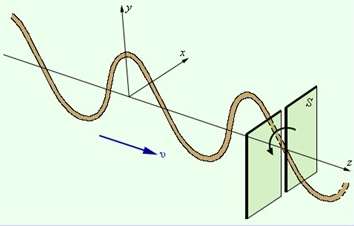

La difracción de la luz fue descubierta en el siglo XVIII por los padres de los fundadores de la óptica:

Al penetrar en el agujero, los rayos de luz y cualquier otra radiación electromagnética (EMP) se desvían del camino recto, divergen y penetran en el área de sombra. El fenómeno se observa en tamaños de orificios cercanos a la longitud de onda. Cuanto más pequeño es el agujero en comparación con la ola, más fuerte es la dispersión. La regla es válida hasta espacios de un cuarto de longitud de onda. El orificio tiene menos de un cuarto de la longitud de onda, el haz EMP simplemente "no ve" y se refleja desde la superficie con espacios tan pequeños como los sólidos.

La longitud de onda de los LED de silicio es de aproximadamente 1 μm (infrarrojo cercano), la longitud de onda de la luz visible de 780 nm (rojo) a 380 nm (púrpura). Menos de 380 nm, comienza la radiación ultravioleta (UV). Los emisores utilizados hoy en fotolitografía tienen una longitud de onda de 248 nm y 193 nm, esta es la radiación de los láseres excimer (por ejemplo,

en XeF 2 ). En consecuencia, los problemas de difracción alcanzaron su altura máxima después de superar la barra de tecnología de 3 micras, y después de 800 nm se hicieron dominantes. Debido a la difracción durante la exposición, el UVI ingresa al área debajo de una máscara opaca e ilumina la fotorresistencia en la sombra. Como resultado, en lugar de un cuadrado claro, obtenemos un panqueque borroso.

Además de la erosión de las ventanas, existe el efecto de la superposición de ondas laterales (interferencia) para ventanas muy cercanas. Los picos acampanados aparecen muy por debajo de la parte reflectante de la fotomáscara

Óptica: sin corazón ...¿Qué métodos se utilizan para combatir este fenómeno?

Óptica: sin corazón ...¿Qué métodos se utilizan para combatir este fenómeno?El primer paso fue utilizar la fotolitografía de proyección. Si se simplifica enormemente, se instala una lente entre la fotomáscara y la placa, que recoge los rayos divergentes y los enfoca en la fotorresistencia.

Otro método fue reducir la longitud de onda de la radiación de exposición. En un momento, comenzaron con lámparas de arco de mercurio con una longitud de onda de radiación de 436 nm, esto es luz azul. Luego 405 nm (violeta), 365 nm (casi ultravioleta). En esto, la era de las lámparas de mercurio terminó, comenzó el uso de láseres excimer. Primero, 248 nm (ultravioleta medio), luego 193 nm (ultravioleta profundo). En este proceso y estancado.

El hecho es que alcanzaron los límites de transmisión de la óptica de cuarzo. Las olas más cortas absorben el cuarzo. Era necesario cambiar a sistemas de espejo o usar lentes de otros materiales. Se realizaron instalaciones experimentales a 157 nm basadas en óptica de fluoruro de calcio. Sin embargo, nunca entraron en la serie. Dado que había formas de optimizar la litografía de 193 nm.

Infografía visual en láser.

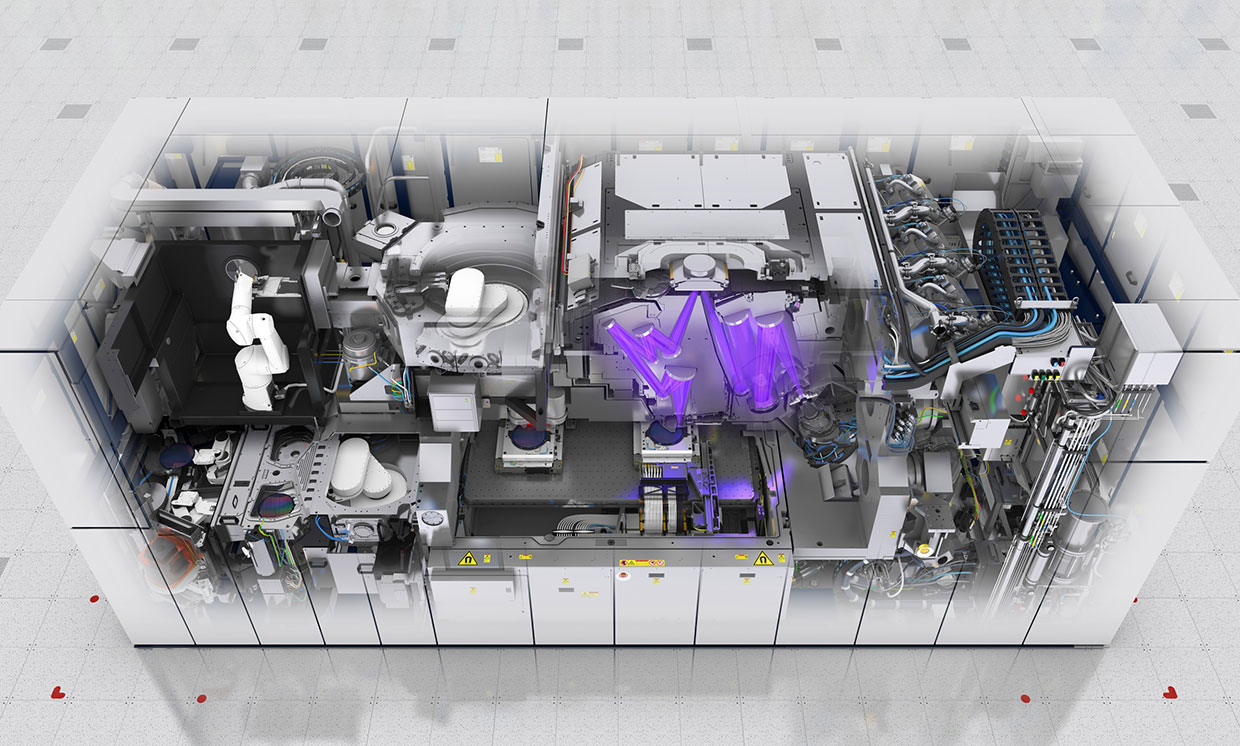

FuenteLitografía EUV

A mediados de la década de 1990, desarrollaron una fotolitografía estándar en ultravioleta extrema (

litografía EUV ) con una longitud de onda de 13.5 nm. Esta longitud de onda hizo posible dar una resolución en unidades de nm.

A principios de la década de 2000, aparecieron las primeras muestras experimentales.

A fines de la década de 2000, se suponía que la tecnología entraría en una serie. Y finalmente, llegó la noticia de que en 2019 Samsung y TSMC taiwaneses cambiarán a la litografía EUV. Han pasado menos de 15 años (

¡sic! ). Intel se convirtió en el principal antagonista de la litografía EUV, aunque originalmente fue uno de los iniciadores. Reconociendo que todo lo posible fue exprimido de la UVI de 193 nm, anunciaron la transición a 126 nm (¡ja, ja!).

¿Cuál es la razón de este rechazo?El hecho es que 13.5 nm ya es prácticamente radiación de rayos X. El límite entre UVI y rayos X se considera convencionalmente 10 nm, pero el ultravioleta no es diferente de los rayos X blandos en el comportamiento de 13,5 nm. Por lo tanto, la litografía EUV es más como una radiografía. Las lentes para tal longitud de onda

no existen en la naturaleza, por lo tanto, es necesario cambiar a espejos de capas heterogéneas de metal.

Además de producir una estructura muy delgada y compleja, los espejos metálicos absorben la mayor parte de la radiación. Las unidades de porcentaje de la potencia de radiación inicial alcanzan la fotorresistencia. Si tenemos en cuenta que la eficiencia del emisor en sí es también un pequeño porcentaje, entonces para obtener un tiempo de exposición normal, se

necesita una alta potencia y un alto consumo de energía (

¡vaya! ).

Este es el escáner ASML EUV

Este es el escáner ASML EUVLa fuente de radiación es el plasma. Una sustancia muy caprichosa, de la que es difícil lograr un flujo uniforme sin pulsaciones. Incluso el aire absorbe activamente 13.5 nm, por lo que la exposición solo puede llevarse a cabo al vacío.

El problema con la selección de fotorresistencia. Cuanto más corta es la longitud de onda, mayor es la energía del fotón. Fuentes anteriores dieron energía en unidades de electronvoltios, esta es la energía habitual de las reacciones químicas. La energía del fotón para una onda de 13.5 nm es de 92 voltios de electrones. Esta es la energía de enlace de los electrones profundos. Al absorber dicho fotón, el electrón se calienta mucho, comienza a precipitarse, irradia un exceso de energía y provoca una exposición secundaria lejos de la ventana. Por lo tanto, la selección de una fotorresistencia con el conjunto de parámetros deseado también es una tarea difícil.

Resultados de la simulación de Monte Carlo del viaje de electrones en silicio con energías de 20 y 5 eV. Fuente

Resultados de la simulación de Monte Carlo del viaje de electrones en silicio con energías de 20 y 5 eV. FuenteEstas dificultades determinaron las razones por las que pospusieron la transición a EUV hasta el final.

Métodos reales para combatir la difracción.

Entonces, hasta hace poco, se usaba la misma UVI con una longitud de onda de 193 nm como fuente de radiación. Hasta la tecnología de 10 nm y 7 nm. Y ahora recordamos que la radiación no puede penetrar en el espacio si su ancho es inferior a un cuarto de la longitud de onda. Para 193 nm es 48 nm. Surge la pregunta:

¿CÓMO?Este es el pequeño milagro que hicieron los ingenieros. Utilizaron el método de polarización por radiación.

Tomamos un espacio estrecho rectangular (con un ancho de menos de un cuarto de la longitud de onda) y dirigimos la luz hacia él, polarizada a lo largo del eje. La luz pasará a través del espacio; incluso la difracción en la dirección transversal será insignificante.

Y ahora tomamos 2 ranuras perpendiculares: horizontal y vertical. Primero, irradiamos una fotorresistencia de dos componentes con luz polarizada a través de una rendija vertical, y luego a través de una horizontal. Solo aparece el área irradiada 2 veces. Como todos los ingeniosos.

Es cierto que tendrá que usar 2 veces más plantillas de fotos y 2 procesos de exposición para crear una ventana. Pero puede usar la buena óptica de cuarzo y los fotorresistentes probados durante años.

Esto es un giro!Hay otras formas de combatir la difracción ...

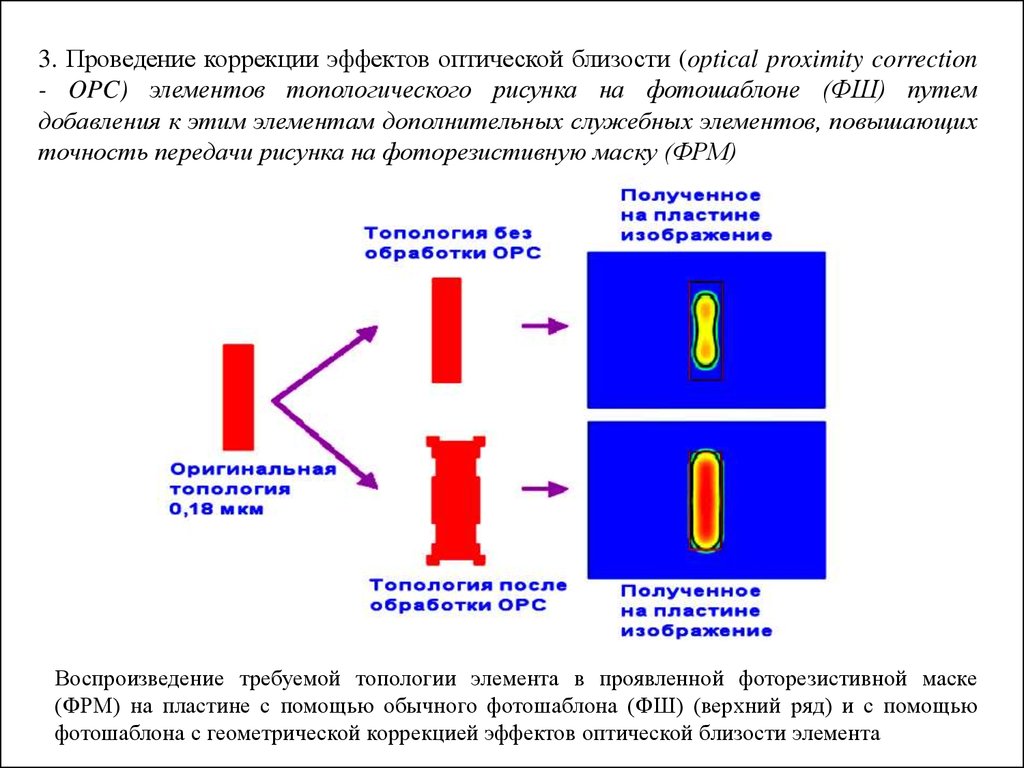

Corrección óptica de proximidad. La forma de las ventanas de la fotomáscara se hace no rectangular para compensar los defectos durante la difracción.

El método de corrección de proximidad óptica es esquemático ...

El uso de máscaras de cambio de fase. En los lados de la ventana principal de la fotomasca auxiliar, cuyo material cambia la fase de la onda. Cuando se aplican ondas (

interferencia ), cortan parcialmente los desplazamientos laterales entre sí.

Iluminación fuera del eje.

Iluminación fuera del eje. El rayo no cae perpendicular a la superficie de la placa, sino desde dos fuentes en un ligero ángulo. Al aplicar fuentes, los desplazamientos laterales se compensan parcialmente.

Exposición múltiple Por ejemplo, necesitamos exponer seis ventanas cercanas. Primero manejamos la exposición de 1, 3 y 5 ventanas. Y luego 2, 4 y 6. Esto aumenta el número de ciclos de exposición y plantillas de fotos en 2 veces, pero aún mejor que nada. Dada la polarización horizontal y vertical, obtenemos 4 ciclos de exposición para crear una capa.

Por lo tanto, si nos fijamos en la moderna máscara fotográfica, no veremos las áreas del microcircuito en forma explícita. Habrá un conjunto de figuras horizontales y verticales que, cuando se superponen, darán una imagen. En realidad, caracteres chinos sólidos: ¿quizás es por eso que los chinos ocuparon la producción de microelectrónica?

Después de 45 nm, cambiaron a fotolitografía de inmersión. Esto es cuando el espacio entre la lente extrema y la fotorresistencia se llena de líquido. Al principio era agua. Ahora fluidos especiales con un alto índice de refracción (hasta 1,8). El líquido reduce la longitud de onda efectiva y neutraliza la refracción de la luz en la interfaz de los medios.

Así es como llegaron a la resolución de ~ 10 nm. Pero este parece ser el límite para la litografía de 193 nm.

Foto de la primera capa de metalización para tecnología de 24 nm. A la izquierda, creado por litografía de 193 nm, a la derecha 13.5 nm experimental (EUV). Como puede ver, de las formas rectangulares claras anteriores solo hay recuerdos. Aún funciona

Foto de la primera capa de metalización para tecnología de 24 nm. A la izquierda, creado por litografía de 193 nm, a la derecha 13.5 nm experimental (EUV). Como puede ver, de las formas rectangulares claras anteriores solo hay recuerdos. Aún funcionaSobre las limitaciones físicas, cómo afectan y cómo cambiaron la producción

en la segunda parte en un par de días, ¡estad atentos!

No te olvides de suscribirte al

blog : no es difícil para ti. ¡Estoy satisfecho!

Y sí, escriba sobre las deficiencias observadas en el texto en el primer ministro.