En la

primera parte, examinamos brevemente la física del silicio, la tecnología microelectrónica y las limitaciones tecnológicas. Ahora hablemos de las limitaciones físicas y los efectos físicos que afectan el tamaño de los elementos en un transistor. Hay muchos de ellos, así que veamos los principales. Aquí tienes que entrar en física, de lo contrario nada.

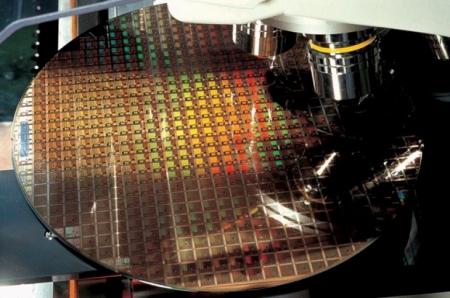

Descargo de responsabilidad: Había una vez que escribí artículos sobre la

fabricación de chips , y

en la serie de artículos "Inside Look" incluso miré dentro de ellos, es decir El tema es extremadamente interesante para mí. Naturalmente, me gustaría que

el autor del artículo original lo publicara en Habré, pero en relación con el empleo, me permitió transferirlo aquí. Desafortunadamente, las reglas de Habr no permiten copiar y pegar directamente, así que agregué enlaces a fuentes, imágenes y un poco de mordaza e intenté enderezar un poco el texto. Sí, y conozco y respeto los artículos (

1 y

2 ) sobre este tema de

amartology .

Efectos físicos en microelectrónica.

El orden de las cantidades básicas para silicio

La concentración de átomos de silicio en el cristal es 10

22 cm

-3Concentración de electrones intrínsecos y agujeros a temperatura ambiente - 10

10 cm

-3Concentración de átomos de impurezas de regiones ligeramente dopadas - 10 16-10

18 cm

-3Concentración de átomos de impurezas de regiones muy dopadas - 10 19-10

20 cm

-3La concentración de átomos de impurezas en regiones muy fuertemente dopadas es 10

21 cm

-3 . En este caso, uno ya habla de un

semiconductor degenerado , ya que dicha concentración (un átomo de impureza por 10 o menos átomos de silicio) cambia la estructura de energía del cristal.

Dependencias de temperatura de las características del silicio.

Desde la primera parte recordamos que a temperatura ambiente el silicio puro es un dieléctrico. Un par de electrones surge solo en uno de un billón de casos, pero esta fracción aumenta exponencialmente con el aumento de la temperatura. Existe tal cosa: la temperatura de duplicar la concentración de los portadores de carga propios. Para el silicio, son unos 9 grados.

Es decir aumentar la temperatura en 9 grados, el porcentaje de átomos de silicio en descomposición aumenta en 2 veces; 18 grados - 4 veces; 27 grados - 8 veces; 36 grados - 16 veces; 45 - 32 veces; 90 - 1024 veces; 180 - 10

6 veces; 270 - 10

9 veces.

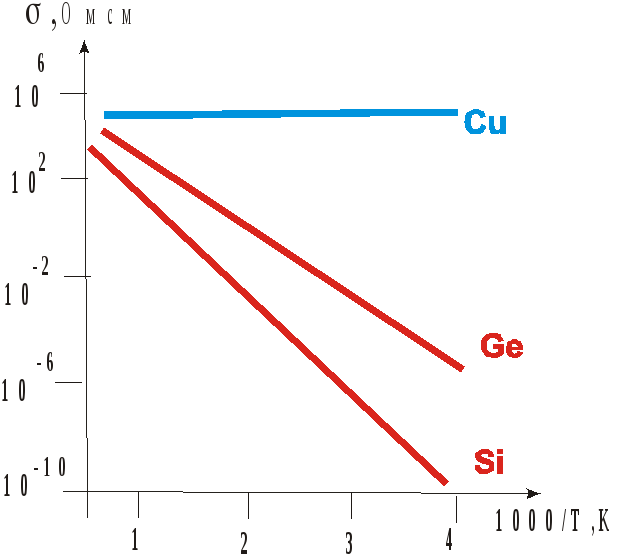

Comparación de la conductividad térmica de cobre, silicio y germanio. Fuente

Comparación de la conductividad térmica de cobre, silicio y germanio. FuenteObtenemos que cuando se calienta a 200 grados (~ 2.1 en el gráfico anterior), la concentración intrínseca de los pares de electrones se convierte en 10

16 , que es igual a la concentración de impurezas de las capas ligeramente dopadas. A 300 grados (~ 1.75) ya 10

19 , esta es la concentración de capas muy dopadas (n + y p +). A esta temperatura, el silicio se convierte en un conductor y los transistores pierden capacidad de control.

Los problemas comenzarán mucho antes. La temperatura en el chip es desigual. Hay zonas de calentamiento local, generalmente en el medio del chip. Si la temperatura en un área pequeña excede los 200 grados, entonces debido a un aumento en la conductividad intrínseca del silicio, la corriente de fuga comienza a aumentar. Esto conduce a un calentamiento aún mayor, y esto aumenta aún más la corriente de fuga y expande el área de sobrecalentamiento. El proceso se vuelve irreversible y ... boom. E irrevocablemente. Por lo tanto, en todos los microcircuitos grandes, se establece la protección automática contra el sobrecalentamiento.

Por eso es tan importante no permitir un fuerte calentamiento del cristal.

A modo de comparación, la concentración de electrones intrínsecos y agujeros en el nitruro de galio a temperatura ambiente es varios órdenes de magnitud menor, y la temperatura de duplicar el número de portadores de carga intrínseca es de aproximadamente 25 grados. Los problemas descritos anteriormente en nitruro de galio comienzan a aproximadamente 600-700 grados.

Corriente del túnel

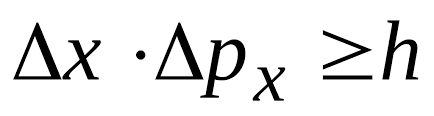

Este fenómeno es complejo y simple al mismo tiempo. Las raíces se encuentran en la naturaleza cuántica del electrón. Un electrón vive según las leyes de la mecánica cuántica, que no siempre se entienden desde el punto de vista de la física clásica. De acuerdo con estas leyes, un electrón no es solo una partícula, sino también una onda, y su comportamiento solo puede calcularse con cierta probabilidad. Existe tal fórmula de Heisenberg:

También se llama

relación de incertidumbre de Heisenberg . De la fórmula se deduce que los parámetros espaciales del electrón no pueden determinarse con una precisión mayor que un cierto valor (constante de Planck). En casos extremos de la ecuación, si conocemos la ubicación exacta del electrón, no sabremos nada sobre su velocidad y dirección de movimiento. Si conoce exactamente la velocidad y la dirección, entonces no se sabrá nada sobre su paradero. Resulta que el electrón es una partícula borrosa en el espacio con picos de probabilidad de ser. En cualquier momento, un electrón puede estar en cualquier parte del Universo sin ninguna influencia externa. Es cierto que la probabilidad de su aparición está muy lejos de la ubicación actual es muy pequeña.

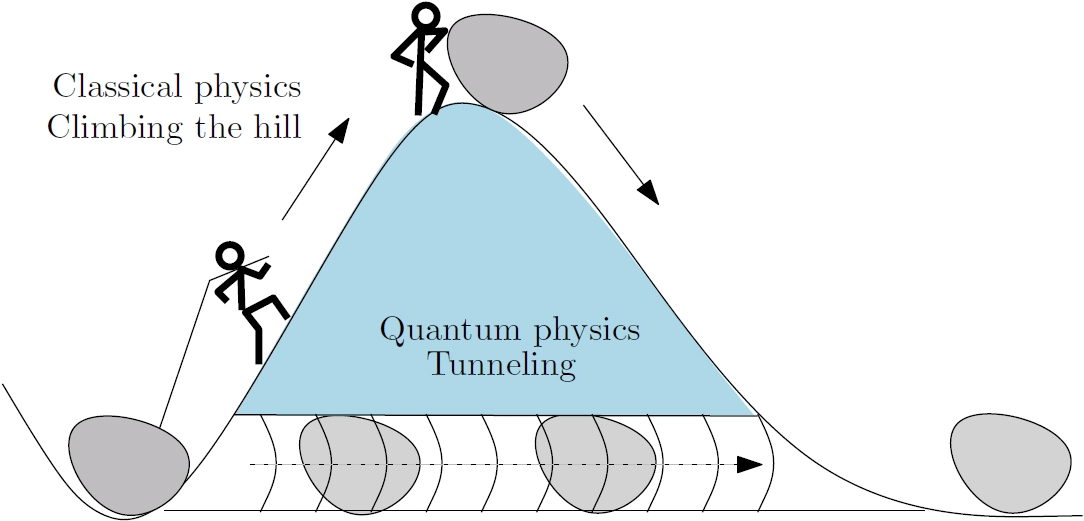

Ahora imagine la estructura del metal - dieléctrico - semiconductor tipo n (MIS). En un metal, la concentración de electrones libres es aproximadamente igual a la concentración de átomos (10

22 / cm

3 ). No pueden penetrar en un dieléctrico, porque para los electrones de un metal, esta es una región de energías prohibidas. Dentro del dieléctrico, una onda de electrones con energía como en un metal comenzará a interferir (autodestruirse). Pero pueden materializarse en un semiconductor de tipo n, donde para ellos hay una zona de energías permitidas. Los electrones pasan de un metal a un semiconductor a través de una capa de óxido sin ninguna influencia externa, simplemente debido a su naturaleza probabilística. Esta es la

corriente del

túnel . El proceso en sí se llama túnel o túnel cuántico (¡suena más genial!).

La energía adicional que tendría que agregarse al electrón para la penetración "clásica" en el óxido se denomina barrera potencial. Esquemáticamente, un electrón roe a través de un túnel a través de una barrera potencial.

Hay un flujo en la dirección opuesta: de un semiconductor a un metal. Pero como la concentración de electrones libres en el semiconductor es varios órdenes de magnitud menor, el flujo inverso es proporcionalmente menor.

Un semiconductor de tipo p para electrones de un metal también es una banda de energías prohibidas. Sin embargo, el proceso inverso es posible aquí: el túnel de electrones de valencia de un semiconductor a un metal con la apariencia de agujeros en el silicio. Parece que los agujeros están haciendo túneles desde el metal. La intensidad, en igualdad de condiciones, es aproximadamente 10 veces menor que el túnel de electrones libres.

La corriente de túnel para distancias superiores a 1 μm puede ser descuidada. Muy baja probabilidad y transiciones muy raras. A medida que disminuye la distancia, la probabilidad de transiciones espontáneas aumenta bruscamente. A distancias de unidades de nm, la corriente de túnel crece 10 veces cuando se acerca a 0.2 nm.

Un mecanismo similar funciona para las capas de silicio npn. Para un electrón libre de la región n, la región p es una banda de energías prohibidas, no se producen transiciones. Pero si el ancho de la base p se establece demasiado estrecho, los electrones comienzan a formarse un túnel directamente desde la fuente hasta el sumidero. Esto limita el ancho de base máximo teórico a 8 nm. En tamaños más pequeños, debido a la corriente de túnel, el transistor de drenaje de fuente se vuelve en principio incontrolable.

Para estructuras pnp, la situación es similar, pero los agujeros (electrones de valencia) hacen un túnel.

En los semiconductores degenerados (muy dopados) en la banda de energías prohibidas hay islas de energías permitidas. Para ellos, la opción de hacer túneles a través de estas islas es posible. Sobre cómo superar una corriente saltando sobre rocas pegadas.

Región de carga espacial (SCR)

La región de carga espacial (SCR), también es la región de agotamiento, también es la región de carga espacial: es una capa cargada eléctricamente que se forma en el límite de las regiones n y p.

Conecte mentalmente 2 piezas de silicio, una de tipo n y la otra de tipo p. En la capa n hay muchos electrones libres, en la capa p hay muchos agujeros; se mueven al azar. Parte de los electrones libres va a la capa p, parte de los agujeros a la capa n. Como resultado, los iones positivos no compensados permanecen en la capa n, y los iones negativos no se compensan en la capa p. Aparece un campo eléctrico local a lo largo del límite de las regiones, que comienza a impedir nuevas transiciones. La intensidad del campo es máxima en el límite y disminuye gradualmente con la distancia. Al final, la intensidad de campo se vuelve tal que cesa la transferencia de agujeros y electrones y se establece un estado de equilibrio. Para el silicio, el voltaje de dicho campo interno es de aproximadamente 0,5 voltios. Depende de la concentración de impurezas en ambos lados. La dependencia es débil, alrededor de 0.1 voltios cuando la concentración cambia 10 veces.

Además de la aparición de un campo eléctrico en el límite, hay una disminución en la concentración de electrones y agujeros libres. Directamente en el límite de las capas a cero. De ahí el segundo nombre: "región agotada". El ancho de esta región depende del voltaje en la transición y la concentración de impurezas. La dependencia de la concentración de impurezas es inversamente cuadrática, es decir. Con un aumento de la concentración en un factor de 100, el ancho de la SCR disminuye en un factor de 10 (en realidad, un poco menos, porque el voltaje en la unión aumenta).

Este es un estado donde el voltaje externo no se aplica a la estructura.

Si aplica un voltaje externo, entonces se vectoriza con el interno.

Aplicamos un pequeño voltaje directo a la unión, es decir más (+) a la capa p, menos (-) a la capa n. Los campos externo e interno se dirigen en diferentes direcciones y comienzan a compensarse entre sí. El voltaje de transición y el ancho SCR se reducen. Cuando el voltaje del campo externo se vuelve más alto que el interno, el SCR desaparece, la unión pn se abre por completo. Para los diodos semiconductores, incluso existe tal parámetro: voltaje umbral. Este es el voltaje directo al que el diodo se abre por completo.

Ahora aplique el voltaje inverso: menos (-) a la capa p, más (+) a la capa n. Los campos externos e internos se suman, el voltaje en la unión y el ancho del SCR aumentan.

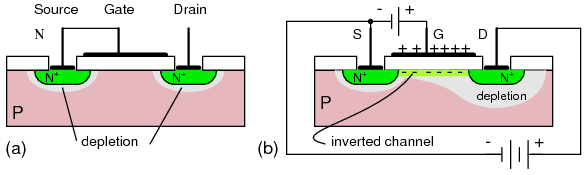

Si transferimos este modelo a nuestro transistor de efecto de campo, obtenemos la siguiente imagen:

Rosa claro denota áreas agotadas (SCR). Obtenemos que el ancho real de la

base activa , que está controlada por el voltaje de la puerta, es menor que la distancia de drenaje de la fuente. Es decir, el tamaño de la base menos el ancho de las transiciones SCR. En ausencia de tensión de alimentación, el ancho de la SCR de la fuente y el drenaje son los mismos. Si aplica el voltaje de funcionamiento, el ancho de la SCR del drenaje aumenta, ya que está bajo polarización inversa. La base activa se está reduciendo aún más:

Si la base es demasiado corta, la SCR del drenaje y la fuente están conectadas. El ancho de la base activa se convierte en 0, una corriente pasante fluye desde el drenaje a la fuente, el transistor se abre. Independientemente del voltaje en el obturador. El transistor se vuelve incontrolable. El efecto se llama "punción base" (

nota: como F376 señaló correctamente , lo más probable es que estemos hablando de "desglose base").

Todavía hay una opción intermedia cuando el SCR no se cierra, pero la distancia desde la fuente hasta el límite del SCR de la escorrentía es inferior a 8 nm. Luego, en el SCR, los electrones comienzan a formarse un túnel desde la fuente. Una vez en el SCR, son arrojados al desagüe por un campo eléctrico. En pocas palabras, una corriente de túnel decente fluirá desde la fuente hasta el drenaje.

Desglose de avalanchas

Si el campo eléctrico dentro del SCR se vuelve demasiado alto, entonces un electrón que accidentalmente vuela hacia él acelera tanto que elimina el electrón de un átomo neutro. Aparecen 2 electrones, nuevamente aceleran y quitan los electrones de lo siguiente, etc. El proceso se asemeja a una avalancha, de ahí el nombre. Aparece un canal conductor en el SCR a través del cual fluye la corriente. El transistor se abre espontáneamente.

Una situación similar puede ocurrir en la puerta dieléctrica. Si la intensidad del campo está por encima del umbral, un electrón "rápido" que sale del metal se acelera y provoca una avalancha.

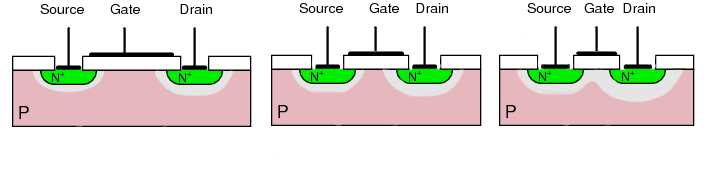

Una comparación clara de los diferentes tipos de desglose. Fuente

Una comparación clara de los diferentes tipos de desglose. FuentePara evitar tal colapso de avalancha, es necesario evitar un exceso de intensidad de campo por encima del valor de colapso. Fuerza de campo = Tensiones / Longitud. Es decir Es necesario reducir el voltaje y aumentar el ancho del SCR (o el grosor del dieléctrico).

Áreas de resistencia eléctrica

Esto ya es una ingeniería eléctrica clásica. Y el drenaje, y la fuente, y el canal, e incluso las pistas metálicas conductoras tienen su propia resistencia eléctrica. La resistencia es mayor, cuanto mayor es la longitud de la gráfica y más pequeña es el área de la sección transversal.

Supongamos que todos los elementos del transistor se reducen proporcionalmente en 2 veces. Al reducir la longitud, la resistencia de la sección

se reduce 2 veces , y al reducir el ancho y la altura

aumenta 4 veces . En total, esto

aumenta la resistencia del elemento en 2 veces . Con el paso de la corriente, la resistencia provoca una caída de voltaje. Para voltajes de transistores en la región de 1 V y menos, incluso una pequeña caída de voltaje será crítica.

Para la metalización, esta pregunta se resolvió simplemente: la primera capa estrecha de metal conecta solo los elementos dentro de la celda. Todo lo demás se lleva a los niveles superiores de metalización: allí la capa de óxido se hace más gruesa y las pistas más anchas. Sin embargo, el tamaño de las ventanas de contacto y las pistas de metalización no se puede reducir infinitamente.

Para áreas de silicio, un aumento en la resistencia fue compensado por un aumento en la concentración de impurezas. Al menos hasta hace poco, hasta que los efectos del túnel y la descomposición comenzaron a afectar.

Otra forma era la tecnología de "silicio estirado" o "silicio colado". Su esencia es que una capa de germanio se deposita sobre un sustrato de silicio. El germanio es un elemento del mismo grupo que el silicio, similar en estructura cristalina. Sin embargo, los átomos de germanio son mayores, respectivamente, la distancia entre ellos en la red cristalina es mayor. Luego, se forma una delgada película de silicio epitaxial sobre germanio. El silicio en la película comienza a repetir la estructura cristalina del germanio, el paso de la red cristalina será tanto en germanio como mayor que en el silicio ordinario. Resulta que el silicio se estira, por así decirlo, en todas las direcciones. De ahí el nombre. Esto da un aumento en la movilidad de electrones y agujeros.

El efecto combinado de los efectos físicos.

Ahora considere los efectos de estos efectos juntos.

La principal amenaza en la miniaturización de los transistores es una base de punción. Para eliminarlo, debe reducir el ancho del SCR. Se puede reducir reduciendo el estrés externo y aumentando la concentración de impurezas en la base.

El voltaje de suministro no tiene ningún lugar para reducir, ya está en la región de 1V, aproximadamente dos umbrales. Si hacemos aún menos, corremos el riesgo de que los transistores se abran "con dificultad" debido a la resistencia eléctrica.

Puede aumentar la concentración de impurezas en la base de datos, pero luego obtenemos:

- un fuerte aumento en la corriente de fuga de túnel desde el drenaje a la base;

- mayor riesgo de sufrir un colapso de avalancha en la transición;

- aumentando el umbral de voltaje para inducir el canal, con el riesgo de sufrir una ruptura del dieléctrico de la puerta.

Debido a estas limitaciones, la

concentración de impurezas en la base se fija en 10 18-10 19 .

Todos estos y otros factores sin nombre restringen el

ancho mínimo de base para los transistores MOS de silicio en la región de 25 nm . Es posible menos, pero la corriente de fuga se vuelve inadecuada y la probabilidad de falla aumenta exponencialmente.

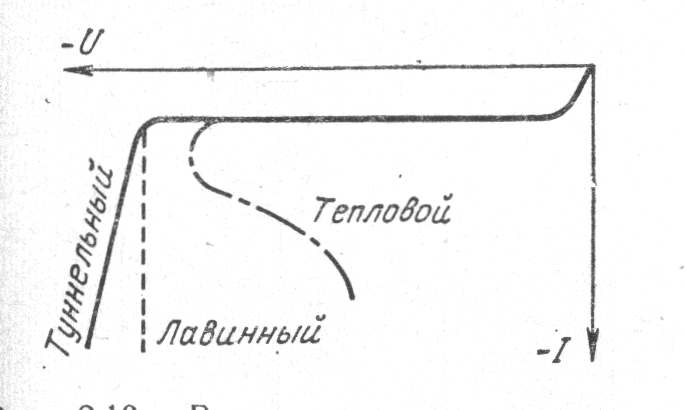

Micrografía de transistores realizada con tecnología de proceso de 90 nm y 32 nm. El zoom y la escala son idénticos. Fuente

Micrografía de transistores realizada con tecnología de proceso de 90 nm y 32 nm. El zoom y la escala son idénticos. FuenteComo podemos ver, el tamaño de los contactos metálicos se ha vuelto mucho más pequeño, pero el ancho de la base no ha cambiado. De todos modos, 25 nm. Además, para los transistores que utilizan la tecnología de 14 nm, 10 nm y 7 nm, es lo mismo (

¡Uy! ).

Esto se encontró por primera vez al pasar de 130 nm a la primera serie de 90 nm. Luego, por primera vez, no pudieron reducir el ancho de la base en proporción a todos los demás tamaños, permaneció aproximadamente a 35 nm. Más tarde, todavía se redujo a 25 nm, pero desde entonces el ancho de la base ya no ha estado sujeto a las proporciones de la tecnología. Y cuanto más pequeños se volvían los transistores, más se manifestaba.

Era necesario cambiar los criterios de los procesos técnicos. Que has hecho La mayoría no hizo nada. Continuaron emitiendo permisos de fotolitografía como la norma del proceso tecnológico. O el ancho mínimo de la ruta de metalización como una manifestación de la operación más simple e intuitiva. Y luego pasamos al marketing ...

Los vendedores más creativos vinieron de Intel. Comenzaron a calcular la velocidad del proceso técnico a partir del tamaño de los elementos, por ejemplo, en función del área de la celda de seis transistores de memoria estática. En tecnología con una resolución de litografía de 65 nm, era de 0,77 μm

2 , y a una resolución de 40 nm se convirtió en 0,37 μm

2 . Si los tamaños de los transistores se redujeron proporcionalmente como antes, esto corresponde a la tecnología de 45 nm. Asumiremos que tenemos tecnología de 45 nm. Aquí es de donde provienen las discrepancias entre la tecnología Intel y otras: 28 nm para todos, 32 nm para Intel; 20 nm para todos, 22 nm para Intel; 10 nm para todos, 14 nm para Intel.

Como lo demostró la historia posterior, Intel terminó siendo más honesto que sus competidores.

Efecto de las corrientes de fuga.

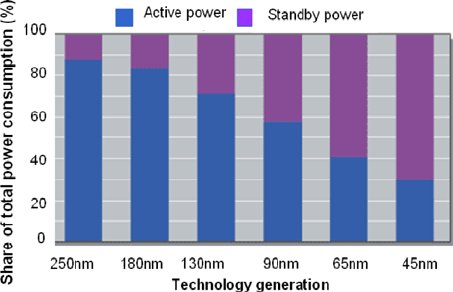

Hay un calendario maravilloso de un artículo ya en 2010:

Fuente

FuenteEl gráfico muestra el porcentaje de trabajo y consumo de energía espuria. Azul: liberación de energía como resultado de las corrientes de recarga (corriente de funcionamiento), púrpura: el resultado de las corrientes de fuga (corriente parásita). Esto tiene en cuenta las medidas que se han tomado para reducir las corrientes parásitas.

La razón por la cual el crecimiento de las velocidades del reloj del procesador se detuvo es claramente visible. Los primeros procesadores en 3 GHz (

Pentium 4 , por ejemplo) aparecieron a principios de la década de 2000. Así que a este nivel y se quedó. Por lo general, esto se explica por el hecho de que el número de núcleos ha aumentado, la lógica se ha vuelto más complicada, la canalización se ha profundizado, por lo que los requisitos de estabilidad y, en general, la felicidad en gigahercios han aumentado. Parcialmente cierto

Pero! - .

, . , 2 , 4 , 6-7 . , , -. . , .

.

180 130 . , , .

. - , , . , 45 .

, 2000- .

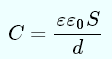

, — .High-k . , NiSi. - .

High-k. . , . , , . – – .

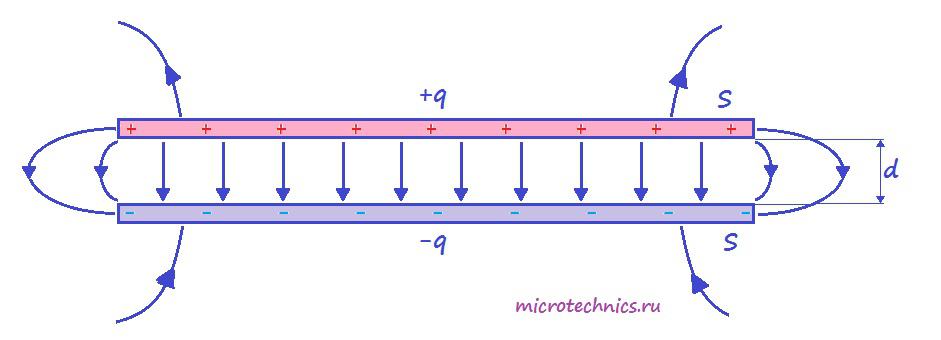

— . . , . . . :

S – ,

d – ,

ԑ – , 1, 1,

ԑ

0 – .

, . , . 1,2 (

sic! ). 6

(!!!) . . 5 , .. 1 , 10 (

!!! ) ( 10 0,2 ). .

– . — High-k . HfO

2 Ta

2 O

5 . 3.9, High-k 25-30. , , - .

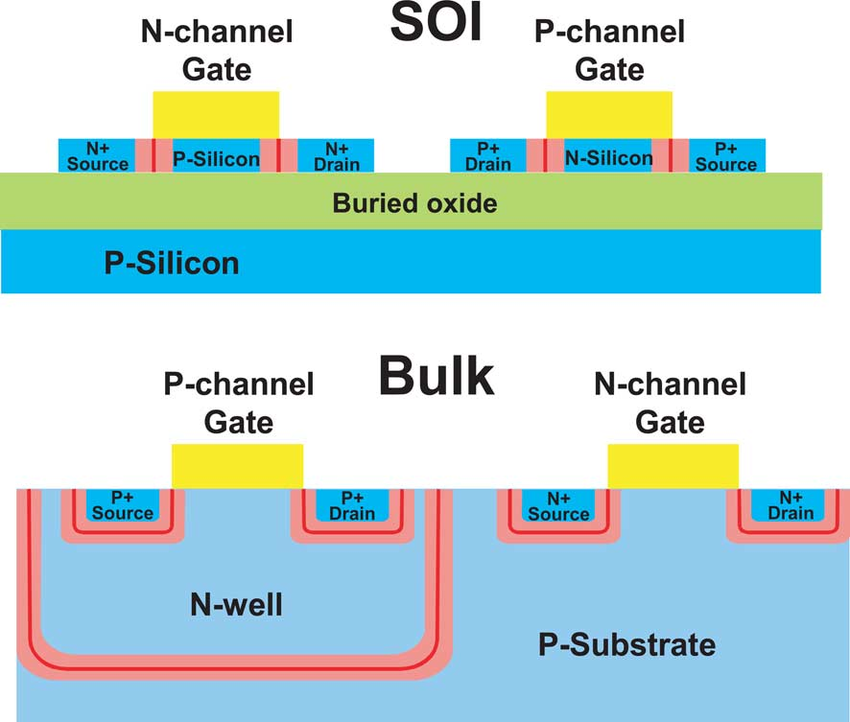

(SOI)

, , SOI, . : , (

UPD: , ,

SIMOX Smart Cut ).

SOI-

SOI-.

. . , - , . . . , .

Al

2 O

3 , . , . High-k 15 . .

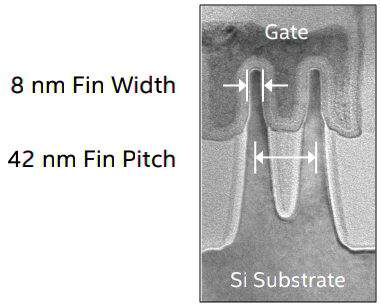

FinFET

Fin – , . 22 . , , .

UPD: FinFET

a5b , «».

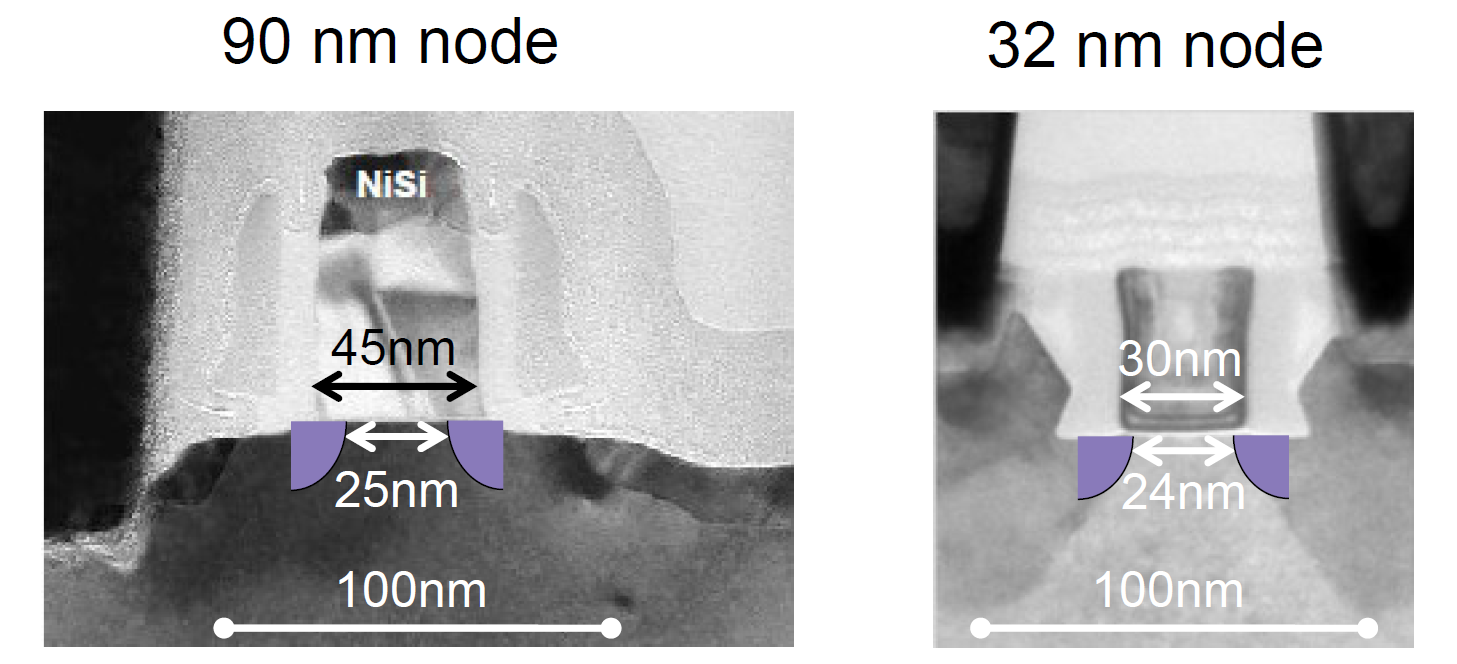

, . Fuente

, . Fuente — . Fuente

— . Fuente. , () , . , , , . , .

- () . , .

Fuente

Fuente

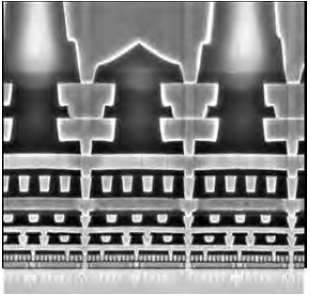

. 6 , 3 n-, 3 p- ( Fin ), (Gate), . , , ( 25 ), . . , 22 54 , 14 – 42 , 10 – 34 . .

3 , . Intel, Samsung TSMC. AMD – GlobalFoundries – . AMD TSMC Samsung.

, . , --. . , . . . , – , . , .

?! , . FinFET . High-k , , . . . Es decir .

Es decir . , 7 22 . FinFET 22 , 7 3 , . , , 10 7 1,8 . …

? . , Samsung GAAFET 5 .

CMOS, FinFET GAAFET . Fuente

CMOS, FinFET GAAFET . FuenteEs decir , . : ? — .

UPD: F376 , FinFet . Gate-All-Around FET , .

, . FinFET SOI. , , .

.

Entonces, los tres líderes se destacaron: Intel, Samsung y TSMC. Intel produce bajo sus propias marcas, el resto es principalmente por encargo. Bajo las marcas AMD, NVIDIA, Qualcomm, Apple, IBM se esconden chips fabricados en las fábricas TSMC o Samsung. Algunos viejos líderes se cayeron o se encontraron con una barrera. Los chinos están tratando de entrar en la gran liga, pero hasta ahora no tienen mucho éxito: carecen de su propia base tecnológica y los líderes mundiales en la producción de equipos mantienen las últimas líneas tecnológicas para los chinos.

El optimismo de los expertos está asociado con la transición a estructuras masivas y el comienzo del uso de la litografía EUV. Samsung y TSMC comenzaron a usarlo en un grado limitado, para las estructuras más delicadas. Esto les da la oportunidad de informar sobre el logro de estándares de 7 nm y en el futuro hasta 5 nm. Aunque, como ya se describió, estos números realmente tienen poco efecto. El mismo Intel generalmente abandonó EUV. Aparentemente, no creen que esto mejorará en gran medida el rendimiento.

Por otro lado, las personas en el tema entienden que la era de Moore ha terminado, y cada nuevo paso en el crecimiento de la productividad requerirá más esfuerzo y tiempo. El rápido crecimiento de la microelectrónica termina (

¡sollozo! ). ¿Cómo sucedió esto una vez en la industria automotriz y la aviación? Después de un crecimiento explosivo, sigue un desarrollo lento.

Entre los puntos de avance prometedores, uno puede destacar la transición a otro material (no silicio) y la creación de microcircuitos multicapa (integración 3D - hola a las ideas de AMD). Para la integración 3D, tendrá que reducir drásticamente la generación de calor o mejorar la disipación de calor.

Eso es todo para tamaños de transistores. Hay otras reservas de crecimiento de la productividad en otro. En la optimización de la arquitectura, por ejemplo. Incluso puede hacer un movimiento de marketing, diciendo que un nuevo procesador con una arquitectura mejorada funciona como si fuera uno antiguo con tecnología de 0,5 nm. Por lo tanto, lo marcamos como 0.5 nm. E higos con él que las dimensiones de los transistores son las mismas.

Es posible crear nuevos tipos de células a partir de combinaciones de transistores. Por ejemplo, en lugar de 6 células de memoria de transistores, haga 2 estructuras de transistores con física compleja de influencia mutua. Las estructuras volumétricas aquí brindan muchas oportunidades.

Límites físicos

Alguien puede decir que el pesimismo del autor no está justificado. Encuentran formas de sortear las restricciones. Quizás no tan rápido como antes, pero no obstante.

El hecho es que todavía hay procesos físicos que no pueden pasarse por alto. Los principales son materia compuesta de átomos, y los portadores de carga son electrones. Crear un transistor más pequeño que un átomo no funciona. No funcionará crear incluso menos de 1000 átomos. Porque hay un electrón y la relación de incertidumbre de Heisenberg. Un electrón es una partícula muy inestable, un comportamiento más o menos estable solo es posible para una matriz de miles y millones de electrones. En un electrón, solo puedes destruir al gato Schrödinger.

Nota: aunque hay desarrollos en transistores de un solo electrón (

1 ,

2 y

3 )

Incluso en los tamaños actuales, se producen colisiones debido al funcionamiento espontáneo de los transistores. Si la probabilidad de una colisión es de 10 a

9 (uno por mil millones), entonces, con el número de elementos en miles de millones y frecuencias en GHz, esto da un promedio de 1 colisión por ciclo, o varios miles de millones de colisiones por segundo. Para atraparlos, existen sistemas para monitorear la integridad de las operaciones, y se envía una operación sospechosa para volver a ejecutarla.

Con la miniaturización, el número de colisiones comienza a aumentar muy bruscamente. Como resultado, llegamos a una situación de cero o incluso efecto negativo de la miniaturización. Es decir los transistores producían menos, se ajustaban más al cristal, pero debido al crecimiento de colisiones y ciclos de reprocesamiento, la productividad total no aumentó. O tal vez incluso se cayó. Y este umbral está bastante en el horizonte.

Algunas palabras sobre microelectrónica digital doméstica

Contrariamente a la creencia popular, hasta 1985 el retraso de la URSS por parte de los líderes no fue tan grande. Cerca de 3-4 años. Esto es si tomamos las empresas

líderes en Zelenograd (nota:

BarsMonster escribió sobre Micron

en ese momento ). Según la ley de Moore, incluso un retraso de 3-4 años afectó en gran medida el rendimiento. Hubo problemas con la obtención de óxido de alta calidad, con la claridad de las uniones pn. Si a esto le sumamos una política conservadora con el empaque de chips en un estuche (las líneas de contacto largas no aumentaron la productividad de los dispositivos), así como los estándares soviéticos para la producción de tableros y estuches con un montón de hierro (los que desmontaron las grabadoras soviéticas lo entenderán), recibimos una broma sobre el chip soviético con hierro fundido asas para llevar.

Hay muchas razones para el retraso. Startanuli posterior, recursos limitados, recursos de pulverización. Cuando los estadounidenses se centraron en CMOS, los nuestros continuaron experimentando con varias tecnologías. Trabajaron bastante activamente con alternativas de silicio, principalmente con materiales A

3 B

5 . Bueno, la relajación general de los últimos institutos de investigación soviéticos.

Después de 1985, los estadounidenses comenzaron abruptamente y comenzamos a tener problemas. Luego, en la década de 1990, cuando la vida en la industria era cálida por la inercia. Como resultado, entraron en el siglo XXI con tecnología de 800 nm, cuando los líderes ya habían asaltado 130 nm. La segunda vida de la industria fue dada por la chipización masiva de tarjetas y órdenes gubernamentales. La producción principal de acero: chips para tarjetas SIM, tarjetas bancarias, tarjetas de pago, transporte y tarjetas de descuento y otros bienes de consumo. No se necesitan grandes gigahercios ni nanómetros pequeños allí.

Nota: por cierto, mientras que en el tiempo de Moscú hay boletos únicos (comprados, usados, desechados, cargados con una fábrica), en la misma China están promoviendo activamente tecnologías de ahorro de recursos, en particular, el uso reutilizable del "token" en el metro (incluso para un viaje corto) .

Video sobre el metro de Shenzhen

Sin embargo, hay un intento de ingresar a la "gran liga" de la microelectrónica. El desarrollo va en cuatro direcciones principales.

- Procesos técnicos "soberanos". Un intento de crear un ciclo de producción completo en equipos domésticos y nuestros propios procesos tecnológicos. Seguimos el mismo camino que los líderes tomaron hace 20 años, pero teniendo en cuenta el rastrillo encontrado y las soluciones. De lo último, lo que estaba en código abierto es 250 nm en la serie y 150 nm en el proceso de implementación. Esto también incluye un intento de crear nuestras propias instalaciones de litografía EUV a 13.5 nm y, por lo tanto, salir inmediatamente, si no en las grandes ligas, y luego cerca de ellas.

- Compra de líneas tecnológicas a fabricantes líderes. El problema aquí es que las instalaciones más modernas no nos fueron vendidas incluso en los mejores años. Usualmente venden líneas obsoletas que han sido descontinuadas. Ahora, en relación con las sanciones, aún más. Aquí podemos recordar la épica con la compra por parte de Angstrom del equipo de la planta de AMD Dresden en 2007, bajo el proceso de fabricación de 180 nm. O la compra de la línea Micron de 90 nm de la STMicroelectronics francesa, seguida de una actualización a 65 nm. Si bien este es el proceso de fabricación más delgado en Rusia, lograron arrebatar antes de las sanciones. Es cierto que ahora hay una solución alternativa: la adquisición a través de China.

- Solicite la producción en fábricas en China o Taiwán. Al mismo tiempo, la arquitectura y la topología están completamente desarrolladas con nosotros,

ahora incluso hacemos nuestras propias máscaras fotográficas . Los chinos solo pueden reproducir los procesos tecnológicos en sus fábricas. Obtenemos procesadores productivos más avanzados y desarrollamos competencia en el desarrollo de los sistemas de procesadores más modernos. Aquí, no está involucrado un grupo de científicos de Kulibin, sino grandes equipos de diseño. Solo la última sección, producción, se elimina del ciclo completo.

Nota: Baikal se fabrica de acuerdo con los estándares de 28 nm en la fábrica de TSMC. Un artículo sobre la salida de Baikal y su análisis.

- El desarrollo de tecnologías alternativas. Este es el desarrollo de tecnologías prometedoras que pueden generalizarse en el futuro. Esto incluye el trabajo en compuestos A 3 B 5 y heteroestructuras, principalmente arseniuro y nitruro de galio. Además de los intentos de optimizar el haz de electrones y la litografía de rayos X para la producción en masa, lo que generalmente elimina las limitaciones de la litografía.

Nota: heredamos una escuela sólida en heteroestructuras del difunto Alferov, pero incluso con el apoyo estatal, OptoGaN no lo extendió , el mercado y las condiciones del mercado están fallando.

En general, la situación no es brillante para la microelectrónica rusa. Pero hay esperanza de que los líderes inevitablemente disminuyan su velocidad debido a limitaciones físicas, y aquí, lentamente, nos apuramos.

El acorde final sobre la memoria y las ventanas de oportunidad en la tercera parte en un par de días: ¡estad atentos!

No te olvides de suscribirte al

blog : no es difícil para ti. ¡Estoy satisfecho!

Y sí, escriba sobre las deficiencias observadas en el texto en el primer ministro.