Hablemos del diseño de las vías: para la electrónica seria, su calidad es muy importante. Al comienzo del artículo, destaqué los factores que afectan la integridad de la señal, y luego mostré ejemplos de cálculo y ajuste de la impedancia de las vías individuales y diferenciales.

Hola a todos, mi nombre es Vyacheslav. He estado desarrollando placas de circuito impreso durante 5 años, y durante este tiempo no solo leí muchas reglas y recomendaciones para el rastreo, sino que también encontré la fuente y trabajé con ellas.

En los sofisticados sistemas informáticos que YADRO está desarrollando, las señales de alta velocidad en el camino desde el transmisor al receptor viajan largas distancias, atraviesan varias placas y realizan docenas de transiciones entre capas. En tales condiciones, cada vias descuidadamente diseñada hará una pequeña contribución a la degradación de la señal y, como resultado, la interfaz puede no funcionar.

Integridad de señal

Las vías (en adelante p / o, inglés vía) son heterogeneidades en la línea de transmisión. Como otras heterogeneidades, estropean la señal. Este efecto es débilmente pronunciado a bajas frecuencias, pero aumenta significativamente al aumentar la frecuencia. A menudo, los desarrolladores prestan una atención inmerecida a la estructura de las vías: pueden copiarse de un proyecto "vecino", tomarse de una hoja de datos o no especificarse en absoluto en CAD (la configuración predeterminada).

Antes de usar la estructura calculada, ¿es necesario entender por qué se hizo así? La repetición ciega solo puede hacer daño.

La integridad de la señal en el canal cuando pasa a través de las vías se ve afectada principalmente por los siguientes factores:

- reflexión de señal debido a cambios en la impedancia de onda;

- degradación de la señal debido a la capacitancia y la inductancia parásitas;

- reflexiones de un tramo de semi-plástico no utilizado durante la transición a la capa interna (en adelante denominado trozo del inglés a través del trozo);

- diafonía (charlas cruzadas en inglés);

- interferencia en buses de potencia.

Consideremos con más detalle las causas de estos efectos y los métodos para su eliminación.

Factor 1. Impedancia de onda p / o

En una placa de diseño ideal, la impedancia no cambia a lo largo del camino, incluso cuando se cambia a otra capa. En realidad, generalmente se ve así:

Figura 1. Cambio en la impedancia de onda tras la transición a otra capa.

Figura 1. Cambio en la impedancia de onda tras la transición a otra capa.Cuanto mejor coincidan las resistencias de las ondas, menos se reflejará la señal. ¿Cómo influir en esto?

Considere la estructura de p / o en el tablero [1].

Figura 2. Estructura p / o en el tablero.

Figura 2. Estructura p / o en el tablero.Al cambiar los elementos p / o, cambiamos la resistencia de onda de la transición. Nuestro objetivo es hacer coincidir la impedancia de la estructura de transición con la impedancia de los conductores para minimizar los reflejos. Consideremos cómo cambia la impedancia cuando cambian los elementos de la estructura p / o.

Factor 2. Inductancia espuria y capacitancia

Los conductores en una placa de circuito impreso se pueden hacer con una resistencia de onda en un amplio rango, pero la mayoría de las veces es de 50 ohmios. Por un lado, esto se debe a la continuidad histórica: la impedancia de 50 ohmios se estandarizó para cables coaxiales como un compromiso entre el nivel de carga del controlador y la pérdida de energía de la señal. Por otro lado, un conductor de 50 ohmios es fácil de fabricar en una placa estándar.

Para el desarrollador, es importante no tanto el valor específico de la resistencia de onda como su constancia en toda la línea de transmisión.

Para hacer una línea de transmisión con un valor fijo de impedancia de onda, el desarrollador selecciona el ancho de la pista y la distancia a la capa de referencia, es decir. cambia la capacidad lineal y la inductancia de la línea de transmisión a un

cierto valor.

En p / o, el componente inductivo es bastante significativo. En una primera aproximación, debemos, dentro de un marco razonable, minimizar la inductancia parásita tanto como sea posible, y luego cambiar los parámetros de p / o para lograr una capacitancia

dada y, por lo tanto, la impedancia.

Una disminución excesiva en la capacitancia de una media onda causará un aumento local de la impedancia y, como consecuencia, reflejos de la señal.

Factor 3. Vía trozo

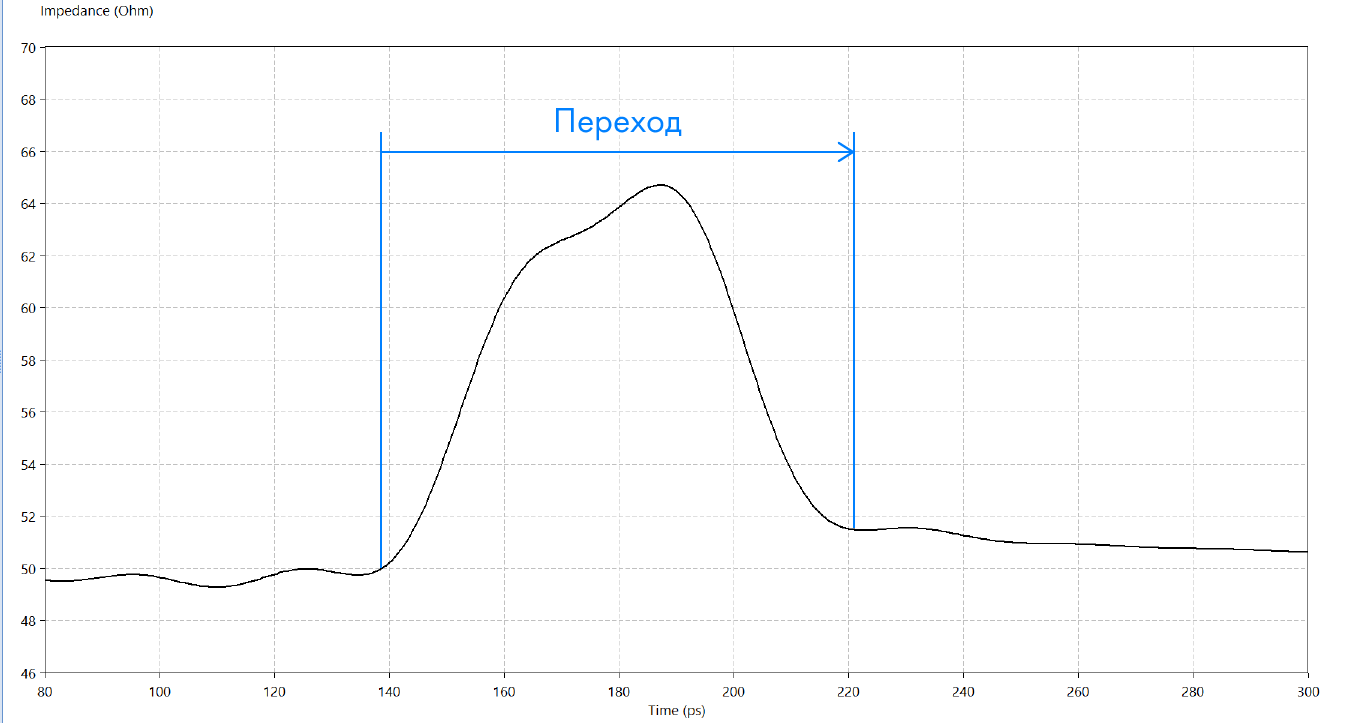

¿Qué sucede cuando una señal pasa a través de un trozo a través del orificio?

Figura 3. Agujero de transición con trozo, resonancia a ¼ de longitud de onda.

Figura 3. Agujero de transición con trozo, resonancia a ¼ de longitud de onda.En nuestro ejemplo, la señal se propaga de arriba a abajo desde la capa superior. Una vez alcanzada la capa de señal interna, la señal se separa: parte se mueve a lo largo del camino en la capa interna y parte continúa bajando por las vías, luego se refleja desde la capa inferior. Después de que la señal reflejada alcanza la capa interna, se separa nuevamente, parte se mueve a lo largo del camino y parte vuelve a la fuente.

La señal reflejada se sumará con el original y la distorsionará, lo que se expresará al reducir la ventana en el diagrama del ojo y aumentar el nivel de pérdida de inserción (pérdida de inserción ing.).

En el peor de los casos, el segmento TD será igual a ¼ de la longitud de onda de la señal, luego la señal reflejada alcanzará el camino en la capa interna con un retraso de la mitad del período, superponiendo la señal original en antifase.

Al analizar la integridad, se recomienda considerar el ancho de banda con un ancho de 5 frecuencias de Nyquist. Una buena aproximación se consideraría un trozo aceptable, dando una resonancia a 7 armónicos y superiores [2].

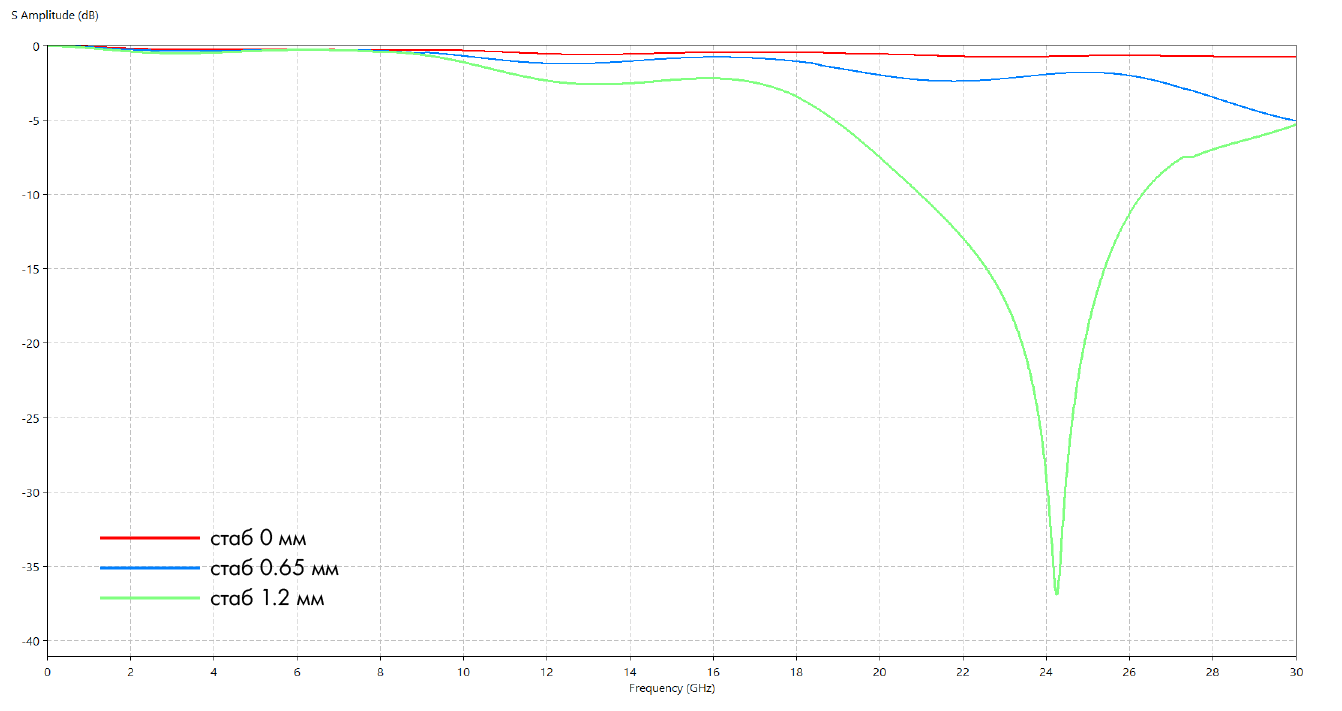

Figura 4. Gráfico del nivel de pérdida de inserción para p / o con trozos de 0, 0.65, 1.2 mm.

Figura 4. Gráfico del nivel de pérdida de inserción para p / o con trozos de 0, 0.65, 1.2 mm.La Figura 4 muestra una gran resonancia a frecuencias de alrededor de 24 GHz. Podemos concluir que si nuestra señal funciona a una frecuencia de 2-3 GHz, podemos darnos el lujo de no eliminar el trozo, porque dentro de 7 armónicos "todo está en calma".

Puede hacer una evaluación rápida de la criticidad del trozo en

la calculadora Polar :

Figura 5. Imagen de polarinstruments.com . Una longitud de trozo de 2.5 mm es aceptable para señales con tiempos de subida de más de 500 ps.

Figura 5. Imagen de polarinstruments.com . Una longitud de trozo de 2.5 mm es aceptable para señales con tiempos de subida de más de 500 ps.Las fórmulas dadas en [2] dan un resultado un poco más preciso. Tienen en cuenta la geometría p / o y permiten calcular la corrección para la constante dieléctrica del dieléctrico a lo largo del eje Z.

Puede eliminar el trozo utilizando la operación de "perforación posterior" (perforación en inglés) o micro-transiciones (vias ocultas y ocultas en inglés). La elección depende de las características del proyecto. La perforación inversa es más fácil y más barata. Después de fabricar el tablero, con un taladro de mayor diámetro, el trozo se perfora a una profundidad predeterminada. Se requiere que el desarrollador establezca una sangría adicional de la topología en la zona de perforación, y también está disponible para que el fabricante especifique los requisitos de perforación en la documentación de diseño. Los sistemas CAD modernos admiten esta funcionalidad.

Las microuniones están destinadas principalmente a tableros de alta densidad (HDI en inglés), pero en algunos casos pueden usarse nivelando el alto costo de negarse a perforar y reducir el número de capas en el tablero. Al desarrollar placas HDI, hay algunas cosas a tener en cuenta:

- cada nuevo tipo de nómina aumenta el costo del tablero;

- Para la perforación con láser, se utilizan preimpregnados optimizados especiales, cuyas propiedades pueden variar;

- La metalización de agujeros ciegos aumenta el grosor del cobre en las capas internas.

Se recomienda encarecidamente que la estructura del tablero se acuerde con el fabricante por adelantado.

Factor 4. Diafonía

Diafonía: transmisión de señal no deseada de una línea a la siguiente. Esta transferencia ocurre porque dos conductores estrechamente espaciados tienen acoplamiento capacitivo e inductivo.

La naturaleza de la diafonía de los conductores de señal y p / o es ligeramente diferente.

La señal no tiene una capa de referencia en el n / a, las corrientes de retorno fluyen a lo largo del n / a adyacente, formando un gran bucle. Diafonía de señales en el n / a debido al componente inductivo.

El mayor efecto en la minimización de la diafonía se puede lograr aumentando la distancia entre p / o. Sin embargo, a menudo el topólogo no tiene mucho espacio.

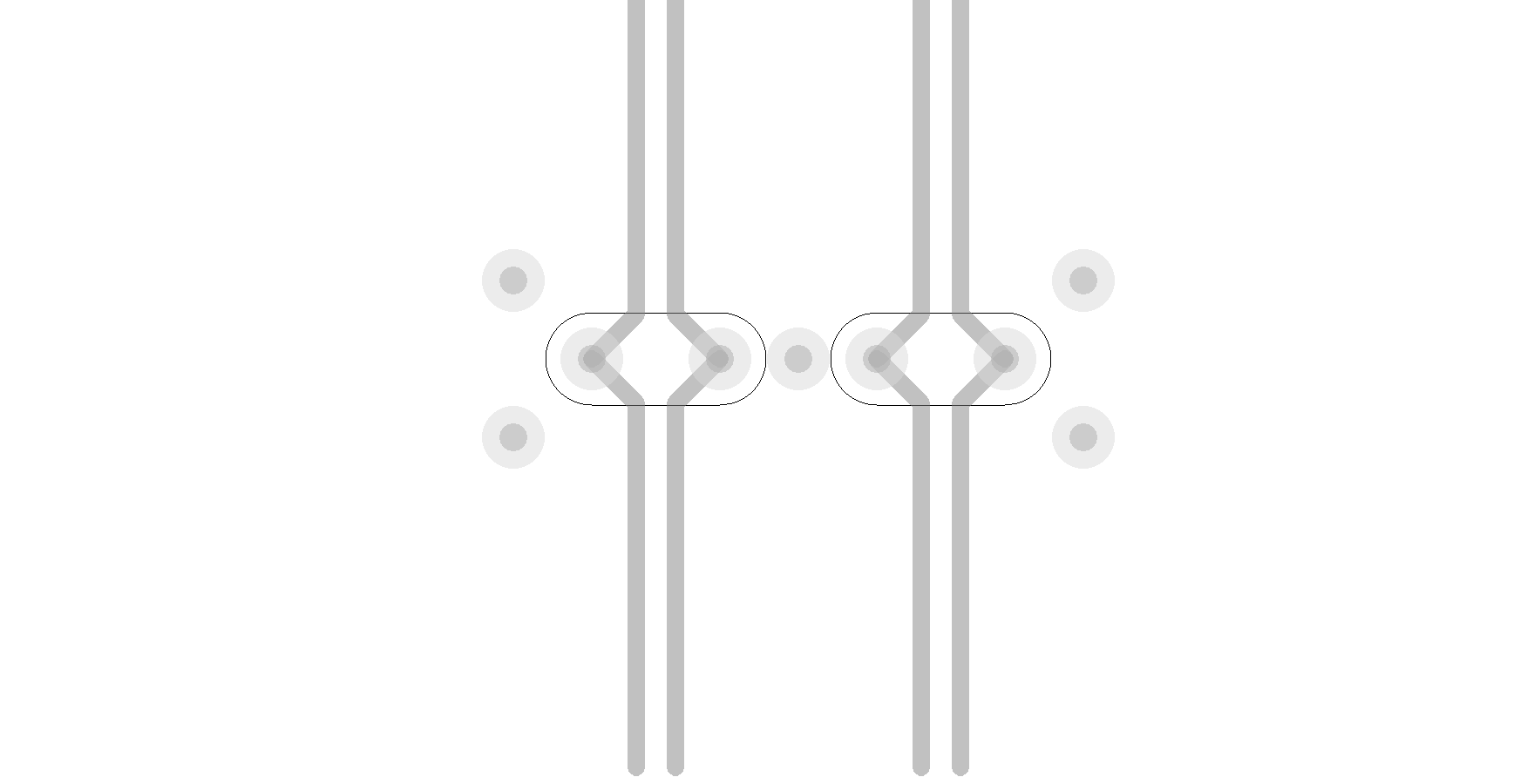

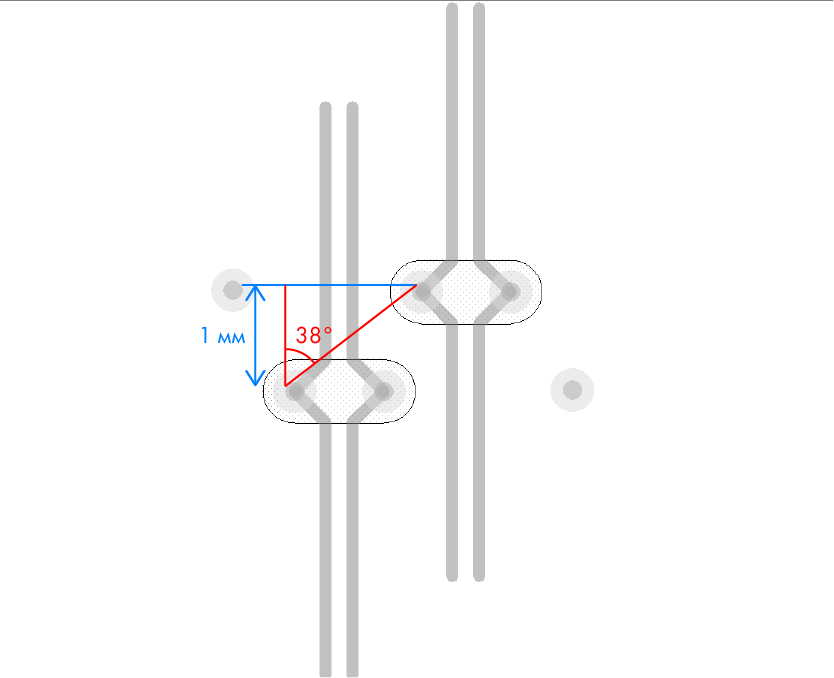

La convergencia de p / o en el par diferencial no solo reduce el área ocupada, sino que también tiene un efecto positivo sobre la inmunidad al ruido [3].

Una forma común de minimizar la diafonía entre señales adyacentes p / o es colocar una protección p / o entre ellas. Con este método, será necesario realizar señales en incrementos de aproximadamente 2 mm (Figura 6). Si no hay suficiente espacio, puede usar un paso más pequeño con un cambio (patrón escalonado en inglés), como en la Figura 7. Usando la simulación, puede seleccionar el ángulo ideal de cambio [4].

Figura 6. Minimización de la diafonía mediante la protección de medio cable.

Figura 6. Minimización de la diafonía mediante la protección de medio cable. Figura 7. Minimizando la diafonía utilizando un cambio diagonal de "tablero de ajedrez".

Figura 7. Minimizando la diafonía utilizando un cambio diagonal de "tablero de ajedrez".La diafonía también puede reducirse mediante métodos exóticos, por ejemplo, mediante un trozo largo (debido al desplazamiento del equilibrio inductivo-capacitivo p / o) [5]. Además, la interferencia puede reducirse en la etapa de diseño de la carcasa del microcircuito [6].

Factor 5. Interferencia del bus de potencia

Además de los circuitos de señal adyacentes, la calidad de la señal puede verse afectada por la interferencia de las capas internas.

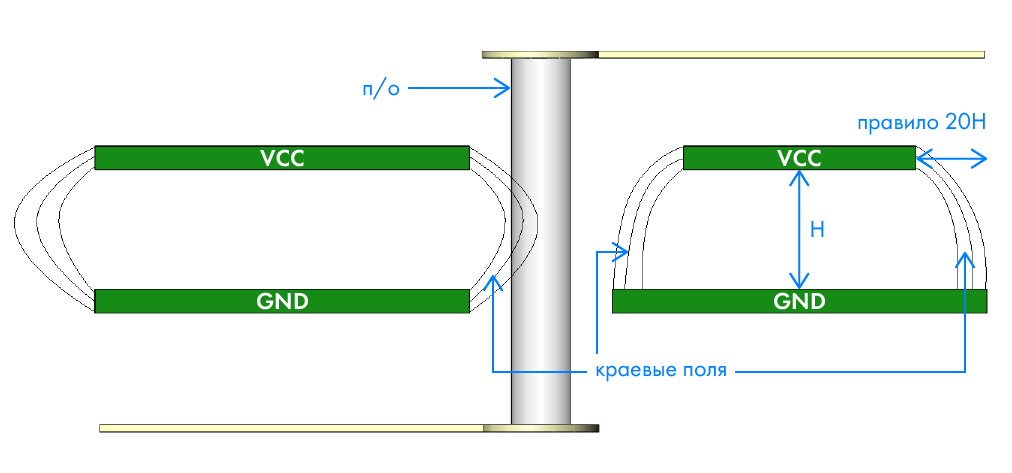

Grandes corrientes pueden fluir a través de los sitios de prueba de alimentos. Debido al aumento de la inductancia en los bordes de los polígonos, las corrientes que fluyen forman campos de borde (campos de franjas inglesas) a lo largo de todos los límites del polígono, incluidos los recortes. Los campos de borde son una fuente de radiación electromagnética (emisión nacida por disparo de borde) en el espacio. Para reducir la emisión de radiación electromagnética, se aplica la regla 20H (Figura 8), que consiste en reducir el área de suministro de energía en relación con el área terrestre.

Figura 8. Campos de borde y la regla 20H.

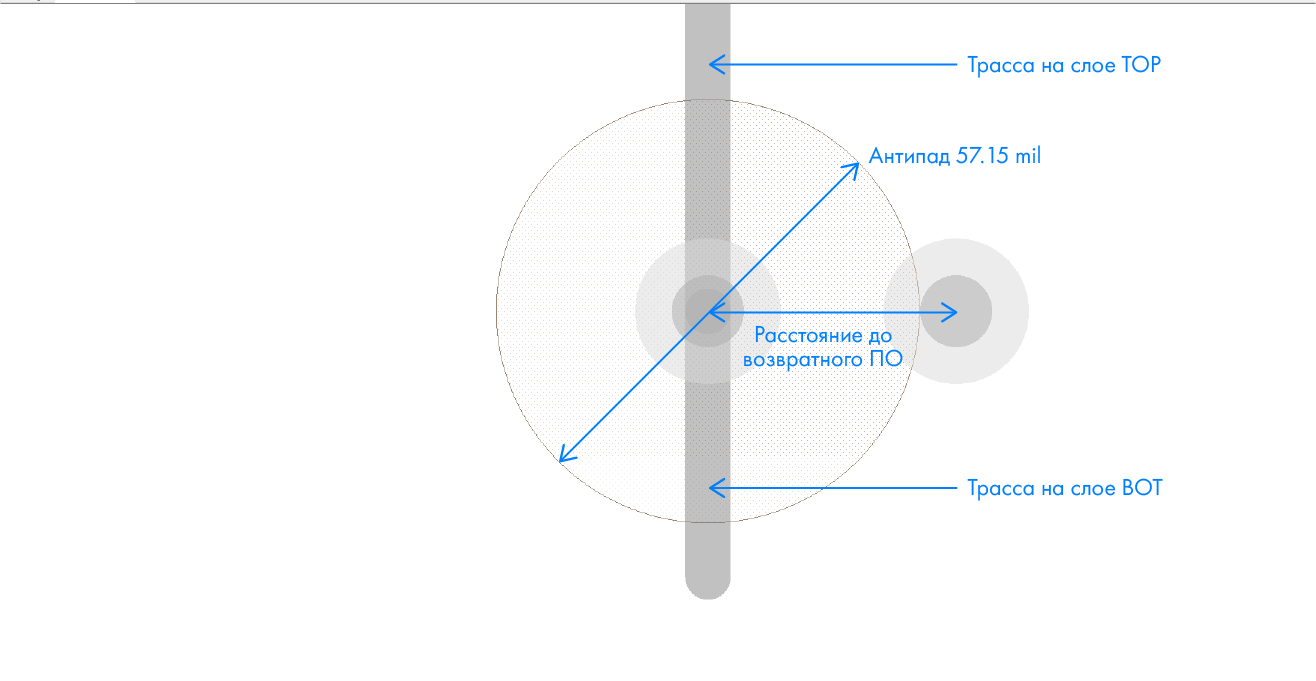

Figura 8. Campos de borde y la regla 20H.Para proteger el p / o de la interferencia, si es posible, es necesario aumentar el antipad en los rangos de alimentos. La regla 20H para p / o es difícil de proporcionar, e innecesariamente, generalmente se recomienda un anti-caída con un diámetro de aproximadamente 2 mm (Figura 9).

Figura 9. Anticaída mejorada en capas de alimentos

Figura 9. Anticaída mejorada en capas de alimentosCálculo de impedancia de vias simple

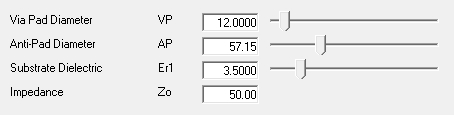

Con base en el conocimiento sobre el efecto de los elementos de p / o en la impedancia, podemos diseñar nuestro p / o ideal. Un buen comienzo es calcular la impedancia en la calculadora.

A los ingenieros de

diseño de PCB les gustan las calculadoras como el

Saturn PCB Design Toolkit y el

Polar Instruments Si9000e . Ambos le permiten calcular rápidamente la impedancia de un solo p / o.

El resultado obtenido en estas calculadoras es muy diferente entre sí. Esto se debe al hecho de que estas herramientas tienen un enfoque diferente.

Polar calcula la impedancia en un plano bidimensional, donde la línea de suministro de energía cruza el rango de potencia. No se dan fórmulas de cálculo. Se estableció experimentalmente que el cálculo se realiza de acuerdo con la fórmula de impedancia del cable coaxial:

Figura 10. Imagen de polarinstruments.com

Figura 10. Imagen de polarinstruments.comLa ilustración muestra un valor bastante bajo de la constante dieléctrica Er1, en comparación con el estándar. Esto se debe a la heterogeneidad de la estructura dieléctrica: consiste en resina (Er 3.2) y filamentos de fibra de vidrio (Er 6.1), y por lo tanto tiene una constante dieléctrica promedio de aproximadamente 4.1. Este valor puede variar bastante localmente. Entonces, la resina prevalece cerca del subsuelo, por lo tanto, la constante dieléctrica se recalcula hacia abajo [7].

Saturn PCB calcula la impedancia mediante la fórmula:

Cuando la longitud de p / o cambia, los valores de inductancia y capacitancia cambian desproporcionadamente, la impedancia cambia. Impedancia de exactamente la misma longitud de p / o 1.6 mm, Saturn PCB calcula como 128 Ohm! (Figura 11)

Figura 11. Cálculo de software en Saturn PCB Design Toolkit.

Figura 11. Cálculo de software en Saturn PCB Design Toolkit.La pregunta surge de inmediato: ¿a quién creer?

Simulamos en un solucionador tridimensional de campos electromagnéticos (English 3D Solver) cómo se verá en una placa real de 8 capas de 1,6 mm de espesor (Figura 12)

Figura 12. La estructura de la transición entre las capas con un agujero para la corriente de retorno.

Figura 12. La estructura de la transición entre las capas con un agujero para la corriente de retorno.En nuestro caso, la impedancia es de aproximadamente 70 ohmios. Al aproximar el retorno p / o, puede lograr una disminución de otros 5 ohmios. Después de "jugar" con el tamaño del antipad, puede ajustar con bastante precisión la impedancia al valor objetivo (Figura 13).

Figura 13. La impedancia del circuito con media onda en el diagrama de tiempo.

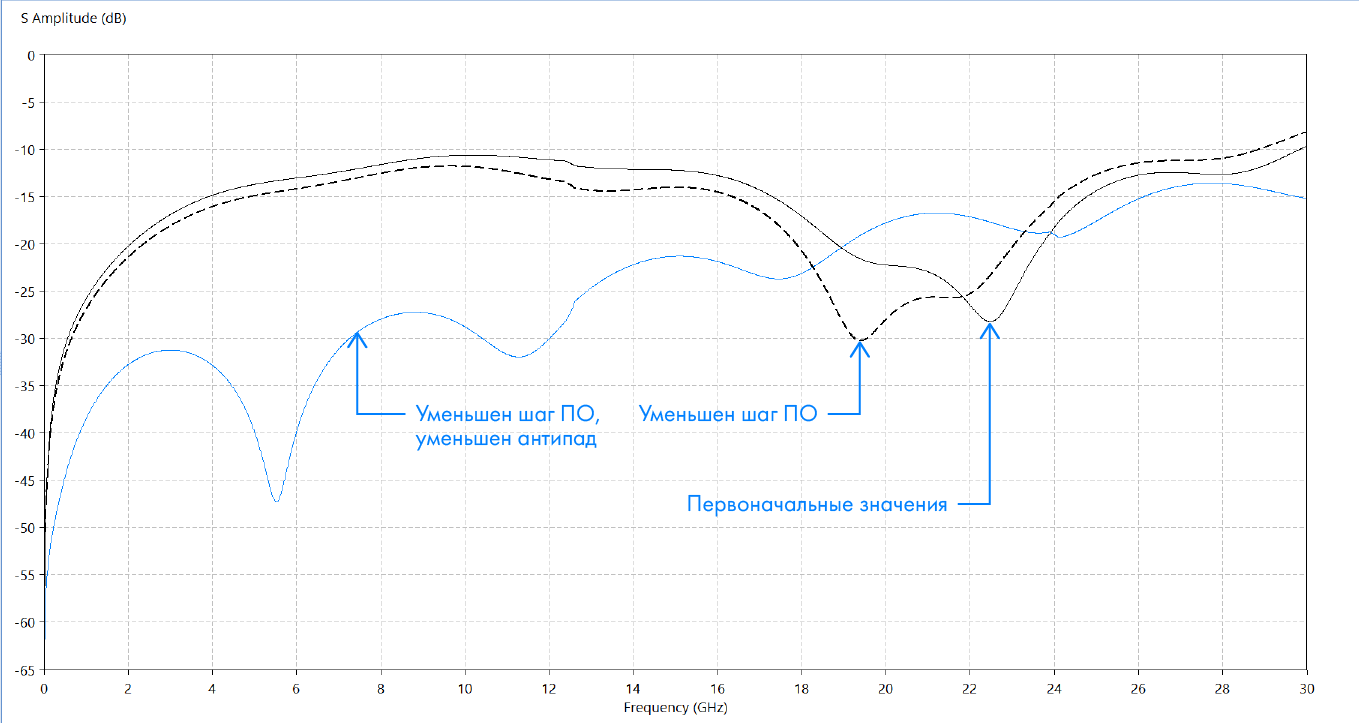

Figura 13. La impedancia del circuito con media onda en el diagrama de tiempo.En el dominio de la frecuencia, los "mejores" parámetros se expresan en un valor más bajo del coeficiente de reflexión de la entrada (Figura 14).

Figura 14. Parámetros de p / o único en el dominio de frecuencia.

Figura 14. Parámetros de p / o único en el dominio de frecuencia.El cálculo Polar estaba más cerca del resultado. Quizás, para obtener un resultado adecuado en Saturn PCB, se requieren correcciones. Si alguien tiene una experiencia positiva calculando la impedancia en Saturno, ¡comparta en los comentarios!

Cálculo de impedancia de vias diferencial

El cálculo del diferencial p / o es similar al simple, excepto que ahora no tenemos una calculadora: las herramientas anteriores no consideran diferencial p / o. Además, ahora también podemos cambiar el paso p / o en el diferencial. pareja

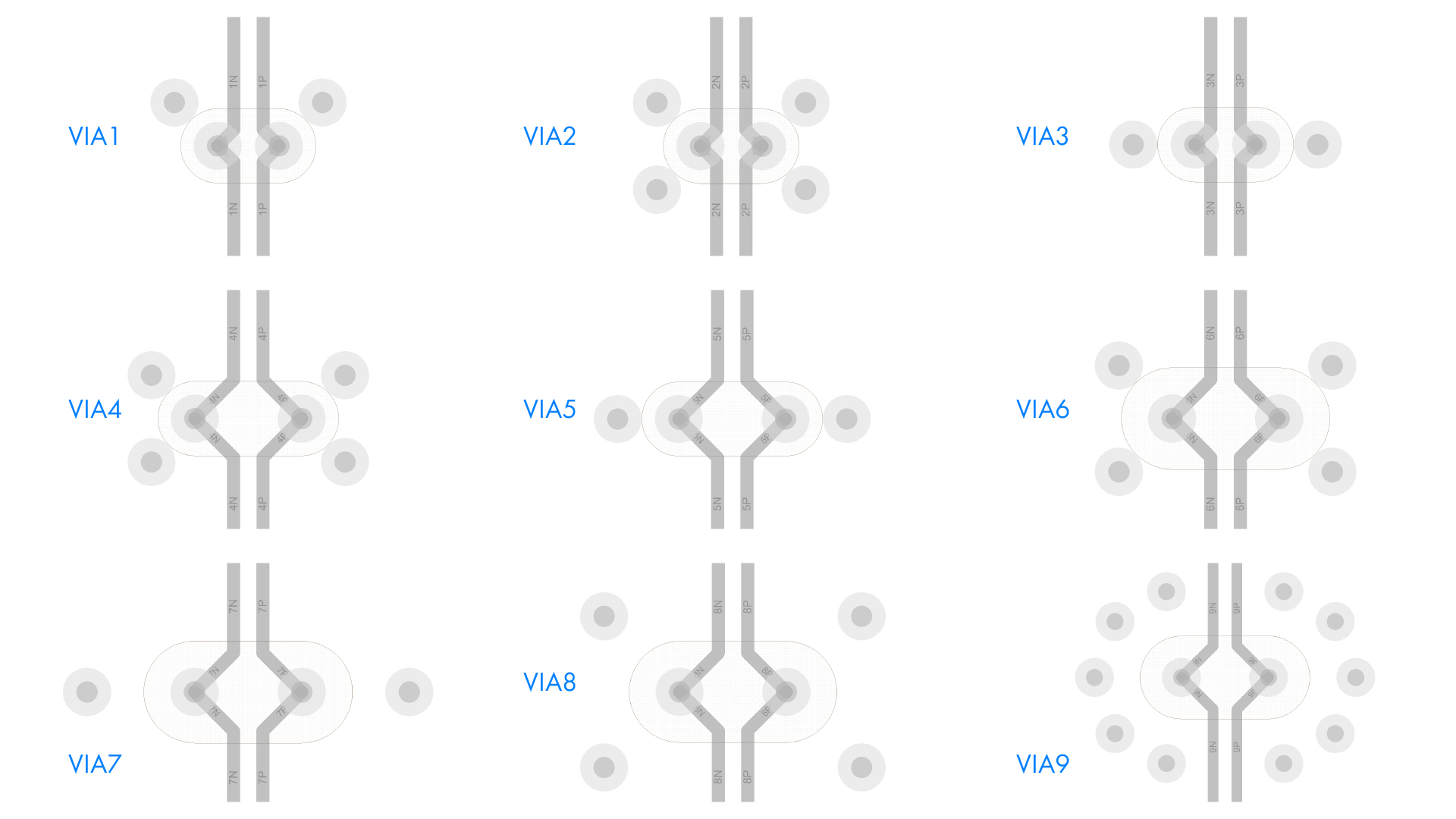

Tome la misma estructura: una tabla de 8 capas de 1,6 mm de espesor. Considere 9 configuraciones del software (Figura 15).

Los primeros 3 p / o tienen espacios de 0,125 mm y difieren solo en la ubicación de los agujeros para la corriente de retorno. Todos los p / o con 4 en adelante tienen un paso de 1 mm. P / o desde 6 en adelante tienen un aumento de anti-caída (0.250 mm) y se distinguen por la sangría de los agujeros para la corriente de retorno.

Figura 15. vias.

Figura 15. vias.Considere el gráfico de impedancia (Figura 16).

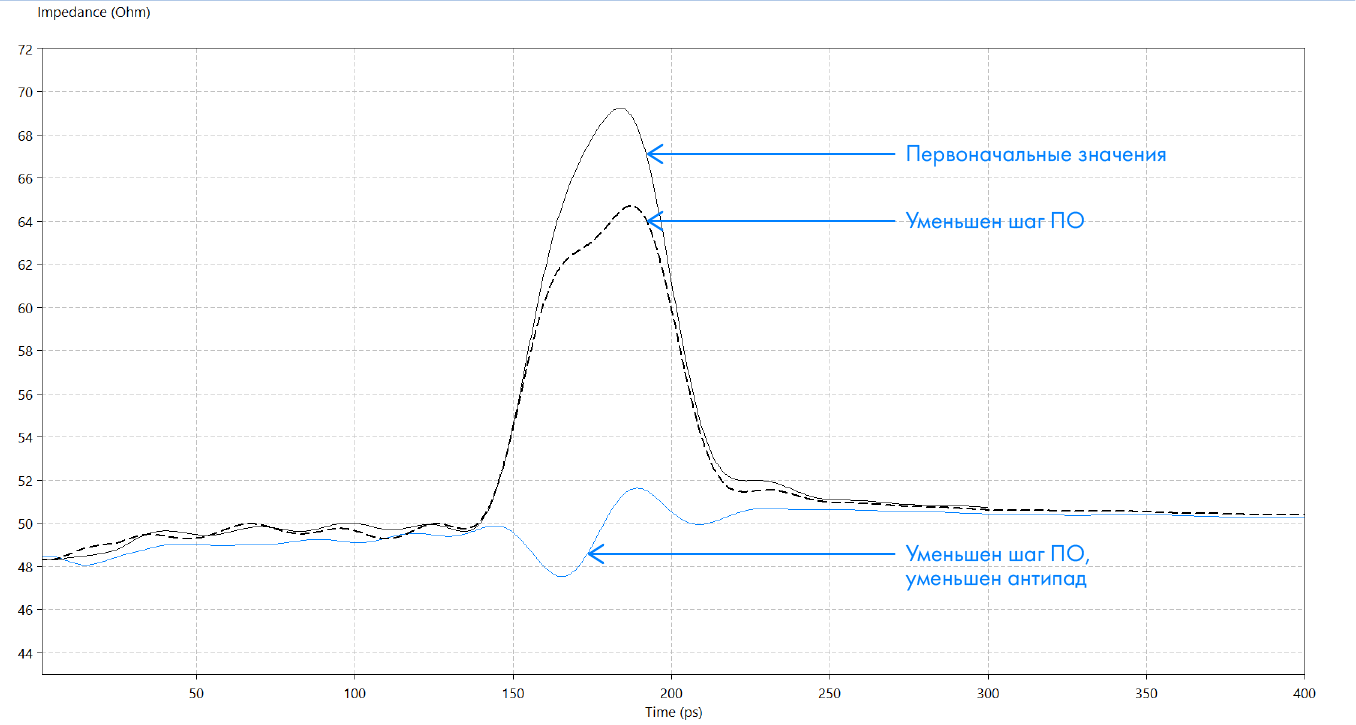

Figura 16. Impedancia p / o en el dominio del tiempo.

Figura 16. Impedancia p / o en el dominio del tiempo.En el gráfico, la "joroba" es claramente visible, lo que corresponde a la sección vertical de la media concha: el "vidrio" (inglés Via barril).

Después de examinar la dependencia de la frecuencia del coeficiente de reflexión VIA1-3 (Figura 17), vemos que a pesar del buen rendimiento a la frecuencia objetivo de 6 GHz, hay resonancia a frecuencias más bajas. Es preferible mejorar via7-9, y si no funciona, entonces via4-5 para reducir la "joroba" debido al desplazamiento de los gráficos hacia la derecha.

Figura 17. El coeficiente de reflexión de la entrada p / o.

Figura 17. El coeficiente de reflexión de la entrada p / o.Reduzca el anti-caída en VIA9 para obtener espacios de 0,125 mm. Para VIA4, reducimos el paso p / o a 0,75 mm y consideramos el resultado obtenido (Figura 18).

Figura 18. Comparación de la impedancia del p / o modificado.

Figura 18. Comparación de la impedancia del p / o modificado.En el dominio de la frecuencia, es visible un desplazamiento del gráfico del coeficiente de reflexión desde la entrada a la derecha (Figura 19).

Figura 19. Comparación del coeficiente de reflexión del software modificado.

Figura 19. Comparación del coeficiente de reflexión del software modificado.Recomendaciones finales

Vias en placas de circuito impreso es una estructura compleja y heterogénea. Para el cálculo correcto de los parámetros, se requieren costosos solucionadores 3D, competencias y costos de tiempo significativos.

Si no es posible evitar el uso de transiciones de señales críticas a otras capas, primero es necesario evaluar el grado de influencia de las inhomogeneidades que surgen en la integridad de las señales. Si la heterogeneidad es eléctricamente corta (el tiempo de retraso es inferior a 1/6 del frente), el trozo resuena en frecuencias fuera de la banda de paso; no tiene sentido perder tiempo y dinero en la optimización.

En una primera aproximación, es conveniente usar estructuras preparadas de hojas de datos o tableros anteriores, pero recuerde las características del proyecto actual.

Las calculadoras le permiten evaluar rápidamente los parámetros del software, pero utilizan modelos altamente simplificados que afectan negativamente el resultado.

Referencias- Mentón, T. Pares diferenciales: cuatro cosas que debes saber sobre las vías. Recuperado de la comunidad TI E2E: https://e2e.ti.com/blogs_/b/analogwire/archive/2015/06/10/differential-pairs-four-things-you-need-to-know-about-vias#

- Simonovich, B. A través de trozos desmitificados. Recuperado de las notas de diseño de Bert Simonovich: https://blog.lamsimenterprises.com/2017/03/08/via-stubs-demystified/

- Desmitificación de vías en diseño de PCB de alta velocidad. Recuperado de Keysight Technology: https://www.keysight.com

- K. Aihara, J. Buan, A. Nagao, T. Takada y CC Huang, "Minimizando la diafonía diferencial de las vías para la transmisión de datos a alta velocidad", en Proc. Decimocuarto elegido. Realizar. Electrón Paquetes y sistemas, Portland, OR, octubre. 2014.

- CM Nieh y J. Park, "Cancelación de diafonía de extremo lejano utilizando Via Stub para el canal de memoria DDR4", en Proc. 63ª Conferencia de Componentes y Tecnología Electrónica, Las Vegas, NV, mayo de 2013, pp. 2035-2040.

- H. Kanno, H. Ogura y K. Takahashi, "Paquete de polímero de cristal líquido de montaje en superficie con inductancia de cable de compensación de transición vertical hasta la banda V", en IEEE MTT-S Int. Microondas Symp. Dig., Philadelphia, PA, junio de 2003, págs. 1159-1162.

- Vía Pad / Cálculo de impedancia anti-pad. Recuperado de los instrumentos polares https://www.polarinstruments.com/support/si/AP8178.html