Hoy en día, hay más de un tipo de memoria, cada una de las cuales se utiliza para una tarea en particular. Cumplen con sus tareas bastante bien, pero hay una serie de deficiencias que no permiten llamar universal a ninguna de estas opciones de memoria. Si agregamos aquí el problema del crecimiento colosal de datos en todo el mundo y la sed de la humanidad por la conservación de la energía, entonces es necesario crear algo completamente nuevo. Hoy nos reuniremos con un estudio en el que los científicos introdujeron un nuevo tipo de memoria que combina las ventajas de la memoria flash y la memoria DRAM. ¿Qué “ventajas” tiene esta innovación, qué tecnologías se utilizaron para crearla y cuáles son las perspectivas? Aprendemos sobre esto del informe del grupo de investigación. Vamos

Base de estudio

Hay muchos tipos de memoria, y todos fueron creados para una tarea específica: SRAM (memoria de acceso aleatorio estático) para caché, DRAM (memoria de acceso aleatorio dinámico) para memoria activa, memoria flash para almacenamiento de datos, etc. Sin embargo, como se esperaba, cada uno de los tipos de memoria anteriores tiene sus propios defectos personales.

Por ejemplo, memoria flash, que es una colección de transistores MOS (semiconductores de óxido de metal) con una puerta flotante (FG) para almacenar carga. Los datos se presentan en una realización tal como la cantidad de carga contenida en el FG, que está aislado por capas de óxido.

La desventaja, según los científicos, es que para grabar y borrar, se requiere un voltaje suficientemente alto para el control mediante un obturador de control (CG), generalmente alrededor de ± 20 V

2 . Este proceso es lento y el mecanismo de falla inducido por una sobrecarga de energía conduce a una reducción en la vida útil del dispositivo.

A pesar de este inconveniente, hay una ventaja bastante impresionante: los datos se leen al verificar la conductividad del canal, que requiere muy poco voltaje. Debido a esto, los datos permanecen intactos, lo que se denomina lectura no destructiva.

DRAM, a su vez, es mucho más rápido que la memoria flash, por lo que se utiliza para procesos informáticos activos, por así decirlo. La desventaja de DRAM es que los datos se pierden de las celdas cuando se leen. Además, se producen fugas de carga de los condensadores utilizados para almacenar datos.

SRAM también es un tipo de memoria bastante rápido y los datos no se pierden tanto como en DRAM. Sin embargo, como regla general, se usan 6 transistores por celda, es decir, necesita mucha área en el chip.

Después de presentar las deficiencias descritas anteriormente de los tipos clásicos de memoria, los científicos enfatizan la importancia de encontrar una opción alternativa o híbrida que esté libre de tales problemas, al tiempo que combinan todas las ventajas de sus predecesores.

En este trabajo, los investigadores presentan a su atención su visión de un nuevo tipo de memoria: un nuevo dispositivo de memoria de baja tensión, semiconductor, basado en carga y no volátil de forma compacta, que funciona a temperatura ambiente. Los investigadores denominaron a su descendencia una "memoria universal" (simple, pero de buen gusto).

El dispositivo es una memoria con una puerta flotante, creada sobre la base de las heteroestructuras de InAs / AlSb / GaSb, donde InAs se utiliza como una puerta flotante y como un canal sin transiciones.

Los científicos han proporcionado simulación y resultados de pruebas reales para un prototipo de célula única.

Resultados de la investigación

Imagen No. 1

Imagen No. 1La imagen de arriba muestra una vista esquemática de un dispositivo y una imagen de un PREM (microscopio electrónico de transmisión).

Como en el caso de la memoria flash, en este dispositivo la carga se almacena en FG, pero al mismo tiempo no hay barreras de óxido. En cambio, se utilizó un desplazamiento de la banda de conducción en la llamada familia de semiconductores 6.1-Å. Es decir, el dispositivo subyacente a la célula de memoria se parece más a un transistor de alta movilidad de electrones (HEMT) que a un transistor MOS. InAs forma un canal que no contiene transiciones. Sin embargo, el n-doping se utilizó para compensar el dopaje de fondo no intencional y para mantener las vacantes de Ga en el GaSb subyacente. Ambas tareas, naturalmente, forman capas de tipo p.

La unión pn * es el área de contacto de dos semiconductores con diferentes tipos de conductividad: p (agujero) yn (electrónica).

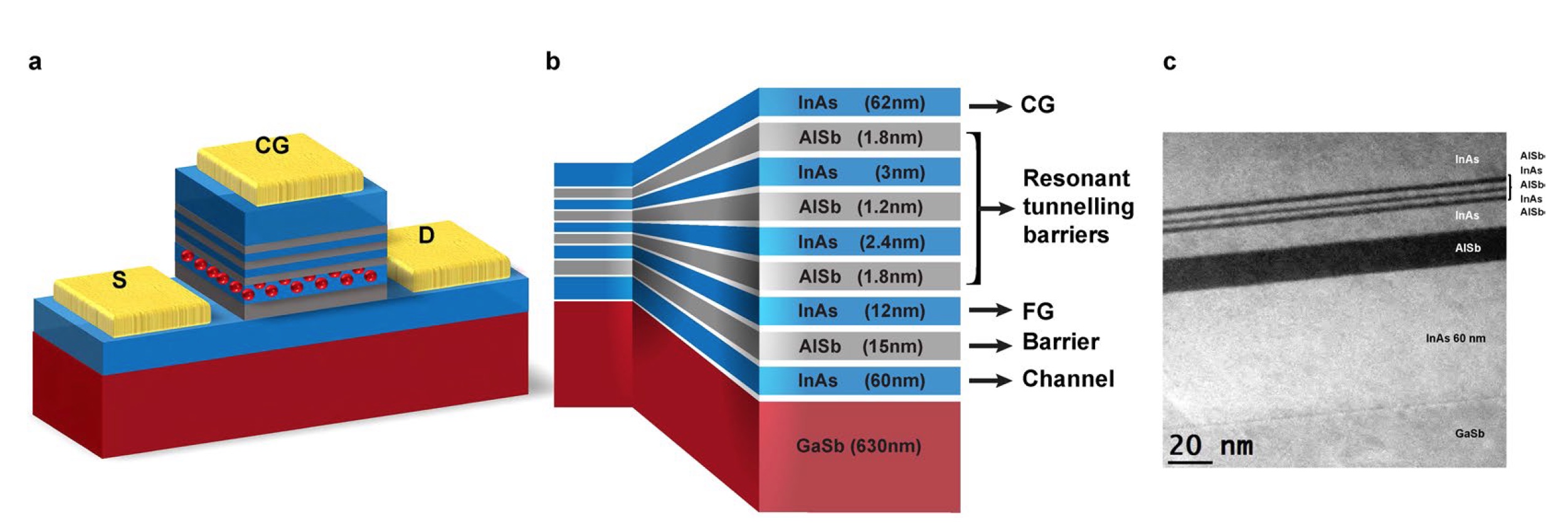

Imagen No. 2

Imagen No. 2El gráfico

2a muestra la alineación simulada de las bandas de energía, así como la densidad de electrones y agujeros en las capas en ausencia de sesgo. Los datos teóricos, junto con la simulación, demuestran que la banda de conducción de InAs está por debajo de la banda de valencia GaSb en la interfaz InAs y GaSb. Y esto lleva a la transferencia de electrones desde la capa GaSb a la capa InAs, después de lo cual los agujeros permanecen en GaSb.

El agujero * es un enlace de valencia sin llenar, que se manifiesta como una carga positiva igual a la carga de un electrón.

Los electrones / agujeros acumulados son visibles en la interfaz entre InAs y GaSb, pero los electrones en el canal InAs no están conectados a la interfaz InAs / GaSb, y su densidad se observa en todo InAs. La conductividad de todo el canal está dominada por electrones en InAs, que tendrán mayor movilidad y mayor densidad que los agujeros en GaSb.

El FG interno de la capa InAs está aislado del canal InAs por una barrera AlSb (15 nm). Al mismo tiempo, los

pozos cuánticos dobles

* InAs y tres barreras AlSb actúan como una barrera de túnel resonante entre los InAs FG y CG con n-doping.

Pozo cuántico * : limita el movimiento de partículas en la dimensión bidimensional (en lugar de tridimensional), por lo que solo pueden moverse en una capa plana.

Por lo tanto, en el dispositivo en estudio, los electrones almacenados en el FG de la capa InAs están aislados por un espacio anómalamente grande en la banda de conducción con AlSb. Esto significa que puede obtener un sistema de limitación de carga, que tendrá un tiempo de almacenamiento a temperatura ambiente igual a 1014 años.

El aspecto más importante del funcionamiento del dispositivo en estudio es el hecho de que dos pozos cuánticos (QW1 y QW2) en la barrera de túnel de triple resonancia tienen espesores diferentes, es decir, se producen estados limitados con diferentes energías (

2a ). Dado que QW2 es más delgado que QW1, el único nivel de energía disponible para electrones en QW2 tiene una energía más alta que el equivalente en QW1. Además, el estado en QW1 tiene una energía significativamente más alta que el estado en la región vecina de CG. De esta manera, se evita el túnel directo de electrones entre CG y FG, y la barrera de transferencia de electrones de CG a FG (o viceversa) se determina mediante un cambio de la banda de conducción de InAs / AlSb en 2.1 eV, es decir, la carga no fluirá hacia / desde FG.

Los estados excitados de tierra y primarios en la puerta flotante (FG) se encuentran muy por debajo de los estados de energía dentro de ambos QW. Por lo tanto, cuando no se aplica voltaje, los electrones se bloquean dentro del FG, es decir. La barrera de túnel de triple resonancia se vuelve insuperable para los electrones hacia / desde FG. Por lo tanto, se logra la no volatilidad.

Si se aplica un voltaje insignificante a la puerta de control (CG), entonces es posible ajustar el acoplamiento de los estados de energía dentro de la barrera de túnel resonante, lo que permitirá que los electrones pasen libremente desde (

2b ) o (

2c ) la puerta flotante.

Durante los experimentos, todas las operaciones de lectura, escritura y borrado se llevaron a cabo en varias celdas (tamaño de obturador 10 x 10 μm) en una caja oscura protegida de electrostática a temperatura ambiente. Todas las operaciones, incluidas la grabación y el borrado, se realizaron a un desplazamiento de ≤ 2.6 V, que es aproximadamente un orden de magnitud menor que el necesario para una operación completa con una celda de memoria flash, enfatizan los investigadores. El borrado se realizó desplazando la puerta de control (V

E CG-S ) en +2.5 o +2.6 V entre el CG y la fuente, lo que condujo al estado "0".

La figura

2b muestra una alineación simulada de bandas de energía obtenidas con un voltaje de borrado de +2.6 V. En tales circunstancias, el nivel de energía de electrones calculado en QW1 es más bajo que el nivel en QW2, mientras que ambos están por debajo del primer estado excitado y están cerca del nivel de energía estado fundamental en FG. El resultado es una eliminación, es decir, un flujo de electrones de FG a CG seguido por el agotamiento de FG. El mismo principio funciona para la operación de escritura: V

W CG-S = -V

E CG-S para aumentar la carga en FG (estado "1").

El gráfico

2c es una zona de energía simulada cuando la compensación de compuerta de control se usa para escribir datos: V

W CG-S = −2.6 V. En este caso, los niveles de energía en QW1 y QW2 prácticamente coinciden, lo que conduce a un fuerte acoplamiento de estos estados, túnel resonante y flujo electrones de CG a FG.

Debido al acoplamiento capacitivo, la conductividad del canal depende de la cantidad de carga almacenada en el FG, por lo tanto, los datos se leen midiendo la corriente de la fuente de la puerta a un voltaje fijo de la fuente de la puerta.

Aumento de carga en FG, es decir estado "1", reduce la carga en el canal, lo que conduce a una disminución de su conductividad. En el caso del estado "0", se produce el proceso inverso. Los datos se pueden leer sin ningún sesgo en CG, pero el voltaje es necesario para la selección individual de dispositivos en una matriz de celdas. Además, el voltaje debe generar un campo eléctrico a través de la barrera de túnel resonante, lo que permitirá transferir la carga de / a FG. Para lograr estas tareas, solo se requieren ~ 2.5 V.

Funciones de memoria universal

Durante las pruebas prácticas, la lectura se realizó con un desplazamiento cero por CG y V

SD = 1.0 V. Sin embargo, según los científicos, fue posible aplicar menos voltaje para una lectura exitosa.

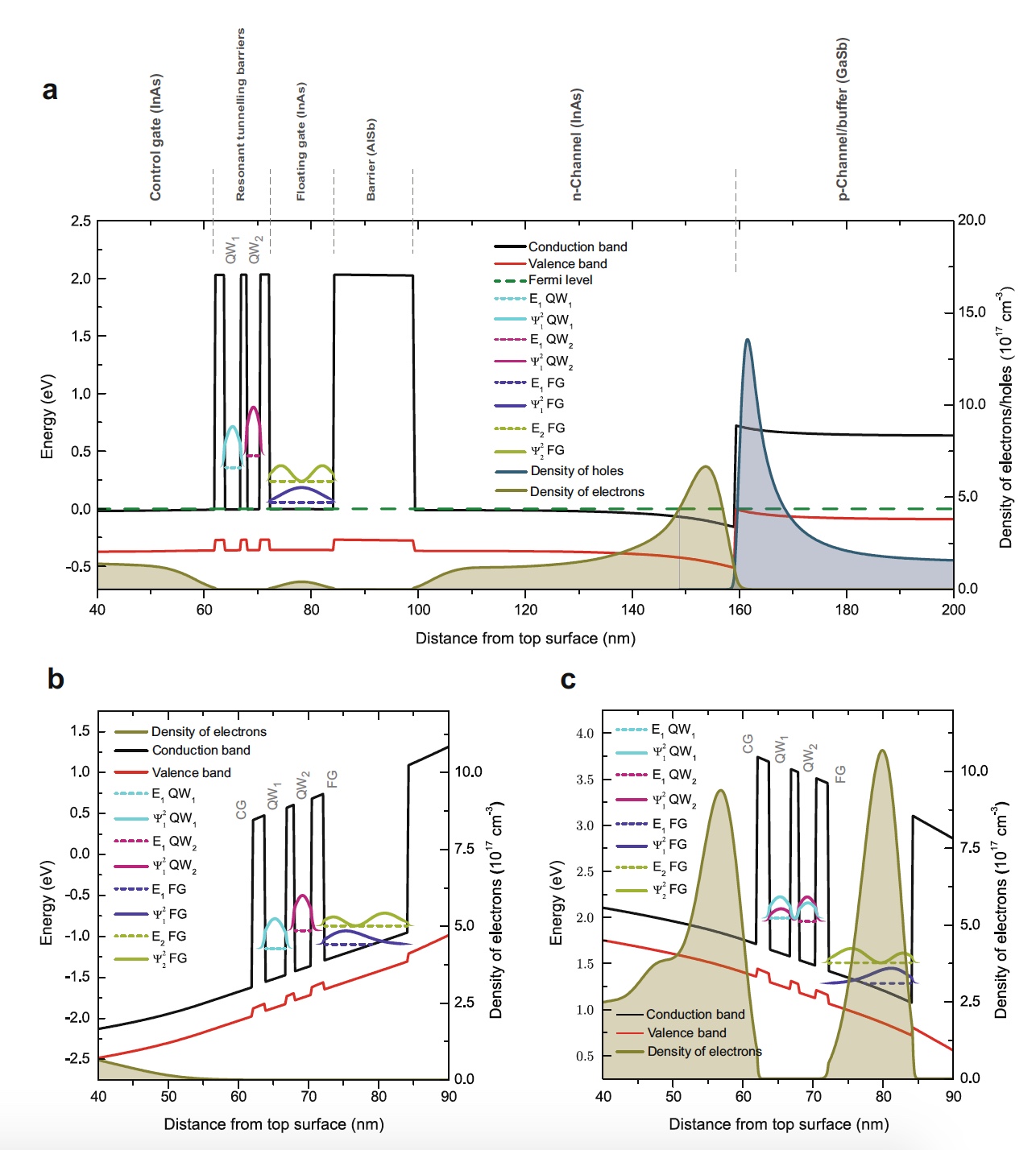

Imagen No. 3

Imagen No. 3La Figura

3a muestra el proceso de borrado-lectura-escritura-lectura. La característica principal de la secuencia es la operación de lectura después de cada paso de borrado o escritura.

La Figura

3b muestra una secuencia más complicada en la que después de cada operación de borrado y escritura no hay una operación de lectura, sino varias. De esta manera, los investigadores demuestran que la operación de lectura no es destructiva.

Entre el estado "0" y "1" hay una clara diferencia en todas las secuencias. Sin embargo, en

3b hay signos de un cambio simétrico hacia arriba en I

SD a medida que aumenta el número de operaciones. Si bien la razón de este comportamiento no está clara, los científicos tienen la intención de explorar este aspecto en futuros trabajos. Pero en

3a esto no se observa, ya que el voltaje para borrar / escribir es ligeramente menor.

Después de varios cientos de operaciones de escritura y borrado, así como muchas operaciones de lectura durante varias pruebas prácticas, los científicos no encontraron signos de daños en el dispositivo.

Una característica importante de todos los tipos de memoria, que se basan en el almacenamiento de carga, es la energía de conmutación determinada por la energía de carga del condensador.

La similitud de los principios fundamentales de la tecnología de memoria flash y la memoria universal en estudio sugiere una comparación de estos dos tipos de memoria. Si suponemos que los dos dispositivos de estos dos tipos tienen la misma capacidad con el mismo tamaño de obturador, la energía de conmutación de la memoria universal será 64 veces menor que la de la memoria flash. Estos números asombrosos también muestran la superioridad de la memoria universal sobre DRAM.

Según las estimaciones teóricas, la capacitancia CG-FG es del orden de

10-12 F para un dispositivo que mide 10 x 10 μm, y la energía de conmutación es de aproximadamente 2 x

10-12 J. La reducción del tamaño físico del dispositivo reduce drásticamente la energía de conmutación a

10-17 J para un dispositivo de tamaño 20 nm, y esto es 100 veces menos que para DRAM, y 1000 veces menos que para memoria flash. Y esto, según las audaces declaraciones de los investigadores, es una característica muy singular.

La imagen

3c muestra algunas operaciones de borrado de escritura de

3b , donde las diferencias entre el estado "0" y "1" son visibles: las mediciones de lectura consecutivas después del borrado dan una I

SD ligeramente más baja para el estado "0". La situación opuesta se observa con mediciones de lectura secuenciales después de la grabación, o más bien, I

SD es ligeramente más grande.

Los científicos atribuyen este efecto a la variabilidad (volatilidad) de los datos. Para estudiar esto, los científicos realizaron una secuencia de operaciones de lectura durante un largo período de tiempo para cada estado de la memoria (imagen No. 4).

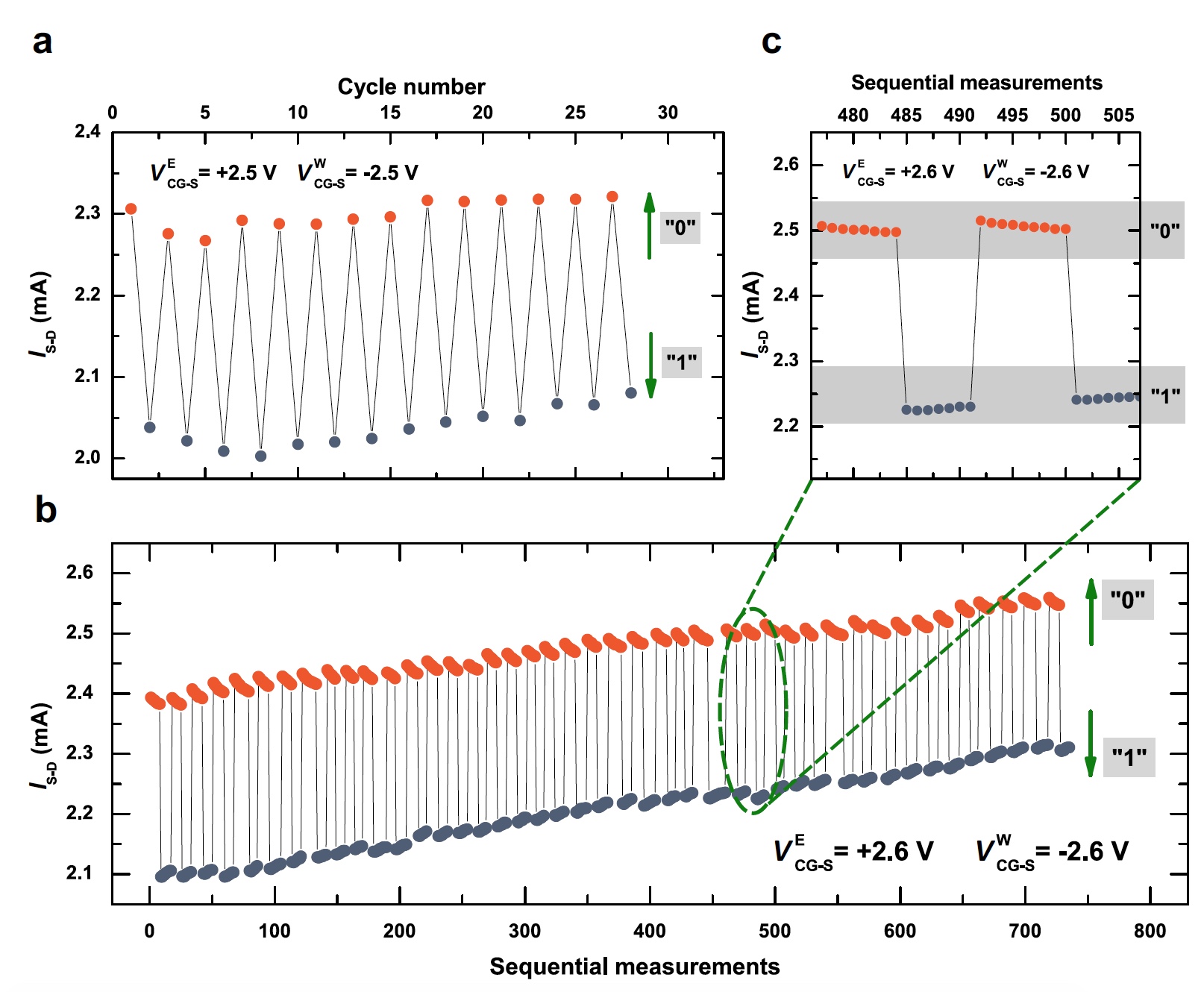

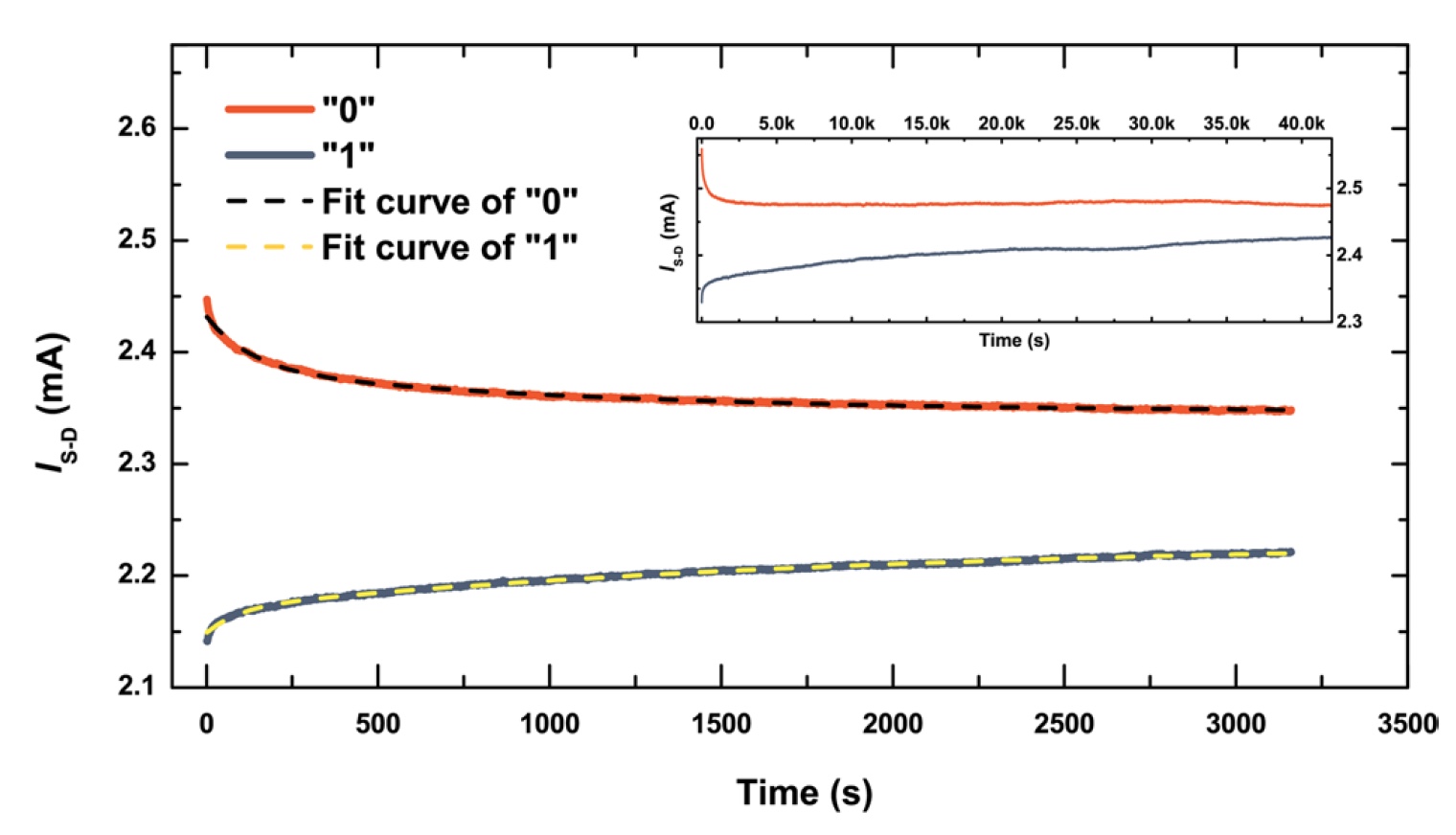

Imagen No. 4

Imagen No. 4Ambos estados "0" y "1" mostraron una disminución rápida inicial, que es consistente con lo que se ve durante

3 segundos . Pero después de esto, se producen cambios mucho más lentos, de modo que durante todo el tiempo de observación los estados correspondientes "0" y "1" se distinguen claramente.

También se llevó a cabo otro experimento (insertar en la imagen Nº 4), que muestra la saturación limitante de la atenuación exponencial y los estados distinguibles "0" y "1" en el tiempo.

La existencia de una atenuación exponencial doble significa que varios mecanismos subyacen a la degradación de los estados a la vez. Entre las posibles opciones, los científicos distinguen el túnel a través de estados defectuosos en las barreras de AlSb, la excitación térmica de los electrones a través del estrecho intervalo de banda de InAs y la recombinación con agujeros generados térmicamente.

La evaluación de la capacitancia del dispositivo y el voltaje aplicado para grabar / borrar indica que se transfieren aproximadamente 107 electrones desde / hacia la puerta flotante durante la operación de escritura y borrado. Esto es bastante, pero prácticamente no se observa influencia negativa.

Para conocer más detalladamente los matices del estudio, le recomiendo que consulte el

informe del grupo de investigación .

Epílogo

Los científicos lograron no solo desarrollar un nuevo tipo de memoria, sino también realizar exitosas primeras pruebas prácticas de un dispositivo no volátil, basado en la carga, de tamaño compacto a temperatura ambiente. Los científicos también lograron combinar la no volatilidad y la conmutación de bajo voltaje por las propiedades mecánico-cuánticas de una barrera de túnel asimétrica de triple resonancia. Los investigadores dicen que su dispositivo se puede escalar sin perder su dignidad.

Los tiempos están cambiando, también lo son las tecnologías. La memoria flash, SRAM y DRAM han mantenido durante mucho tiempo una posición dominante entre los dispositivos de memoria, pero esto podría cambiar si el desarrollo de la memoria universal continúa con el mismo éxito que en este estudio. Esta tecnología reducirá en gran medida el consumo de energía de los dispositivos equipados con ella, además de extender su vida útil y aumentar la productividad.

Otros estudios planeados por los autores mostrarán cuán revolucionaria es la memoria, tan orgullosamente llamada universal por los científicos.

¡Gracias por su atención, sigan curiosos y tengan una buena semana de trabajo, muchachos!

Gracias por quedarte con nosotros. ¿Te gustan nuestros artículos? ¿Quieres ver más materiales interesantes?

Apóyenos haciendo un pedido o recomendándolo a sus amigos, un

descuento del 30% para los usuarios de Habr en un análogo único de servidores de nivel de entrada que inventamos para usted: toda la verdad sobre VPS (KVM) E5-2650 v4 (6 núcleos) 10GB DDR4 240GB SSD 1Gbps de $ 20 o cómo dividir el servidor? (las opciones están disponibles con RAID1 y RAID10, hasta 24 núcleos y hasta 40GB DDR4).

Dell R730xd 2 veces más barato? ¡Solo tenemos

2 x Intel TetraDeca-Core Xeon 2x E5-2697v3 2.6GHz 14C 64GB DDR4 4x960GB SSD 1Gbps 100 TV desde $ 199 en los Países Bajos! Dell R420 - 2x E5-2430 2.2Ghz 6C 128GB DDR3 2x960GB SSD 1Gbps 100TB - ¡desde $ 99! Lea sobre

Cómo construir un edificio de infraestructura. clase utilizando servidores Dell R730xd E5-2650 v4 que cuestan 9,000 euros por un centavo?