En este artículo quiero presentar mi experiencia en el uso de un fotodetector CCD lineal. Tal línea CCD se puede usar en el diseño de un espectrómetro improvisado, lector de código de barras, sensor de posición o desviación del rayo láser, un escáner para fotografía o película, y mucho más. En mi caso, era un escáner láser, que no puedo describir en la red.

¿Qué es un dispositivo de carga acoplada?Muy a menudo, cuando se habla de CCD, se refieren a varios fotodetectores. Con menos frecuencia, estos son dispositivos de memoria: registros de desplazamiento, líneas de retardo. En esencia, este dispositivo recuerda de alguna manera la memoria en dominios magnéticos cilíndricos, solo en silicio, con la ayuda de una onda viajera de un campo eléctrico creado por un sistema de electrodos, grupos de portadores de carga que de alguna manera se han formado en él antes se mueven a través del semiconductor. Por lo tanto, obtenemos un registro de desplazamiento que tiene una estructura extremadamente simple y es capaz de recordar no solo una secuencia de unidades digitales y ceros, sino también una señal analógica.

En los receptores de imágenes CCD, es precisamente esta capacidad de esta estructura la que se utiliza para emitir secuencialmente las cargas acumuladas debajo de cada uno de los píxeles de la estructura. Además, el mismo sistema de compuerta que se usa para mover las cargas durante la exposición crea pozos potenciales en los que se acumulan estas cargas (o estos agujeros se crean durante la formación de la estructura, similar a los canales incorporados e inducidos del transistor MOS). Las estructuras más complejas incluyen una puerta resistiva a lo largo de la cual se forma una pendiente de potencial suave (así es como se organizan las líneas CCD Hamamatsu S11155), así como la separación de la acumulación de carga y las zonas de transferencia: las cargas acumuladas de toda la línea se transfieren primero a la línea de amortiguación y luego avanzan salir por la última.

La simplicidad de la estructura interna se traduce en la complejidad de administrarla. Incluso la versión más simple de la línea CCD requiere la generación de una señal de dos o tres fases de forma compleja con diferentes niveles de voltaje con bordes empinados (con una alta capacitancia de entrada de 1000 pF o más), desplazados uno con respecto al otro. Las reglas de tipo Hamamatsu S11155 requieren hasta ocho señales diferentes con diferentes niveles de alto y bajo voltaje en ambos lados de cero.

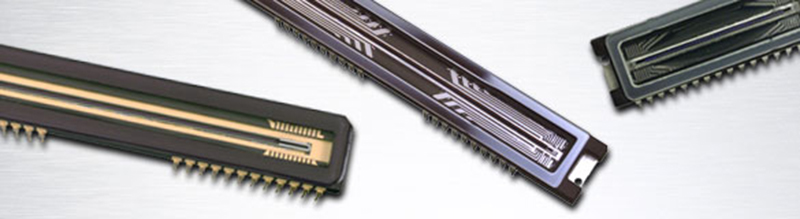

Afortunadamente, algunas compañías (por ejemplo, Sony) lanzaron una línea en la que toda esta complejidad se forma directamente en el chip. Y para su trabajo, solo necesita generar dos señales: el obturador electrónico que se abre durante la exposición y el reloj. En nuestro diseño, esta es exactamente la línea ILX554: (como regla, usada, pero bastante funcional) es fácil de comprar a los chinos en Aliexpress.

Veamos la hoja de datos.Y vemos que solo 6 de los 22 pines están involucrados. Estas son fuentes de alimentación de + 5V, señales de entrada ROG y CLK, señal de salida Vout, entrada de selección de modo SHSW y tierra. Y eso es todo.

ROG es el control de obturador electrónico (y el inicio de la transferencia de carga desde la línea fotosensible al registro de desplazamiento directo). Tiene un nivel activo: cero. Para exponer la matriz, debe presionarse a cero y mantenerse durante el tiempo que sea necesario, desde 5 μs hasta varios segundos. Y luego, dejándolo ir, espere al menos 3 μs (durante este tiempo, el circuito de transferencia de carga funciona). Todo este tiempo en la entrada de CLK mantenemos un alto nivel. Y luego puede leer la línea, aplicando a la entrada CLK un meandro con una frecuencia de varias decenas de kilohercios a 2 MHz. En este caso, en cada diferencia de unidad a cero, el siguiente píxel será empujado a la salida. Hay 2088 de esos píxeles en la alineación, de los cuales 2048 están funcionando, fotosensibles (en realidad, hay varios más, pero los píxeles más externos están parcialmente oscurecidos). Datashit recomienda aplicar al menos 2090 pulsos CLK a la matriz para un funcionamiento correcto.

Y cómo se empujará depende de lo que esté en la entrada de SHSW. Si es una unidad lógica, la salida producirá una señal bastante compleja:

Además, cuando el CLK pasa de cero a uno, se produce un restablecimiento y de la unidad a cero, la emisión de una señal útil.

Y a cero en la entrada SHSW, el circuito de almacenamiento de muestreo incorporado se activa, lo que simplifica esta señal a una señal de video simple paso a paso, donde con cada nueva transición de CLK a cero, el nivel de señal del siguiente píxel simplemente aparece y se mantiene durante todo el período de la señal CLK.

El rango útil de la señal de salida proviene de un cierto nivel oscuro, que según la hoja de datos es de 2.85 V, pero en realidad puede ser diferente (en mi línea, aproximadamente 3 V), y cuando está saturado, el nivel de la señal de salida cae a 1.5-2 B.

En general, eso es todo lo que necesitamos saber sobre esta línea.

Circuito de inclusiónEs simple y obvio. Generamos señales CLK y ROG mediante programación usando MK, y los disparadores Schmitt en la entrada son la forma más sencilla de cambiar de 3.3 V a 5 V. El hecho es que no hay buffers en estas líneas en la línea, y que los circuitos internos de la matriz funcionen correctamente. debe enviarles un meandro con una escala completa de cero a cinco voltios y una buena inclinación de los frentes. Los NC7SZ14M5X indicados en el diagrama son disparadores de inversión Schmitt individuales muy convenientes con frentes empinados y mayor capacidad de carga, y los uso a menudo en mis proyectos.

Usando DA1, el nivel de señal de video de la línea "acelera" al rango en el que opera el ADC, mientras que se elimina el "soporte" de aproximadamente 1.5 V correspondiente al nivel de saturación. Dado que la diferencia entre la amplitud de la señal y el valor de "soporte" varía mucho entre los diferentes conjuntos de líneas CCD, las resistencias R1 y R3 deben seleccionarse "colocando" la señal de salida en el rango requerido. Debe tenerse en cuenta que no solo el desplazamiento, sino también la ganancia dependen de la resistencia R1, por lo que primero debe seleccionarlo.

L1 y L2 son perlas de ferrita o pequeños estranguladores para 1-2 μG de tamaño de marco 0805 o 0603. Se utilizan resistencias y condensadores del mismo tamaño. El circuito se ensambla en una placa de doble cara mediante montaje en superficie. No traigo el diseño del tablero, ya que todavía tengo muchas cosas en él.

Implementación de software en MKLa tarea MK es generar una señal ROG de alto nivel (¡no se olvide de los inversores!) De la duración requerida, luego una pausa corta (3-10 μs), y luego una secuencia de 2090 pulsos de alto nivel separados por pausas iguales en duración. Durante estos pulsos (o pausas), algún tiempo después del frente, el valor de iluminación de píxeles se toma usando un ADC interno o externo. Después de leer el cuadro, también debe pausar hasta que aparezca un nuevo pulso ROG, los mismos 3-10 μs. Después de encender la alimentación y, como resultó, después de un largo (más de 100 ms) no uso de la regla, debe "limpiarla" aplicando un tren de pulsos estándar gratuito al CLK un par de veces.

En STM32, es aconsejable hacer todo esto en una interrupción del temporizador. Al configurar el temporizador para generar interrupciones con una frecuencia correspondiente a la frecuencia de píxeles duplicados, obtenemos cada operación del temporizador en una interrupción, donde alternativamente emitimos cero o uno al puerto, y cuando emitimos cero, leemos las lecturas del ADC. Y después de contar 2090 ciclos, detenemos el temporizador. Para leer el siguiente cuadro, debe restablecer el contador de ciclos a cero, iniciar el temporizador y esperar hasta que se cuente todo.

Algo como esto, como se muestra en estos fragmentos de código.

bool clkState = false; bool frameOk = true; uint16_t pixCount = 0; uint16_t ccdFrame[2090]; inline uint16_t readADC1(void)

Y aquí está el resultado.El resultado no es malo. A pesar de que el ADC incorporado no tiene ninguna característica, sus características de ruido corresponden totalmente al ruido de la línea CCD. La pista de ruido de la señal oscura con un tiempo de acumulación de aproximadamente 1 ms resulta ser de ~ 3-4 niveles de cuantificación, y cuando se usa un ADC externo de 14 bits con excelentes características, los resultados son solo ligeramente mejores. Con el aumento de la iluminación, el ruido aumenta por una simple razón: el número de fotoelectrones en cada uno de los píxeles no es tan grande (según mis cálculos, alrededor de 30 mil en la saturación). Para los mejores dispositivos, este valor alcanza los 200 mil.

En el cuadro a continuación hay un ejemplo de una "imagen" registrada por la regla, en la cual, contra el fondo de la pared iluminada, hay un soporte oscuro en el que una bola hueca de vidrio con un diámetro de 1 cm fijo en su interior se llena con una solución negra. Un pico es un reflejo de la superficie exterior de esta bola. El ruido en las áreas brillantes es la estructura de la pared misma, reforzada por motas del láser, de cuadro a cuadro permanece estacionaria. El ruido real de la línea es mucho menor.

Otras lineas similaresAlgunas otras líneas CCD SONY en blanco y negro de 2048 píxeles de ILX511, ILX551 (esta última tiene un pinout diferente y requiere dos voltajes de alimentación: 5 y 9 V), que difieren en el tamaño de píxel transversal (de 14 a 200 micras) funcionan exactamente de la misma manera. y sensibilidad espectral (ILX554A es sensible al rojo e IR, similar al índice B tiene una sensibilidad reducida en la región IR y tiene una sensibilidad cercana al ojo, e ILX511B es más sensible al azul). Sus características dinámicas son diferentes: el rango dinámico del ILX551B debido al pequeño tamaño de píxel alcanza los 6000 (nuestra línea alcanza este DD con velocidades de obturación cortas de aproximadamente 10 μs).

* * *

Este artículo discute la conexión de quizás la línea CCD más fácil de usar. Esta simplicidad se debe al hecho de que toda la complejidad está oculta en ella debajo del capó. Si no fuera por los controladores integrados, tendría que generar muchas señales multinivel.

Desafortunadamente, según los estándares modernos, una línea CCD con controladores incorporados no tiene las mejores características. Entonces, en esta línea, el rango dinámico, definido como la relación de la señal de saturación a la señal oscura, es 333: 1, y se define como la relación de la señal de saturación a la señal mínima detectada en el fondo del ruido, aproximadamente 1000: 1. Pero tales dispositivos no solo son difíciles de usar, sino que a menudo son difíciles de acceder (el mismo Hamamatsu requiere formalidades burocráticas complicadas al comprar sus conjuntos CCD y otros fotodetectores debido al doble propósito de estos productos). Sin embargo, no siempre se requiere un rendimiento tan alto, y para muchos propósitos los parámetros de estos dispositivos son bastante aceptables.