Decidí escribir esta nota sobre Habré en ruso y en inglés para distribuir un enlace en foros y grupos en inglés y ruso. El texto en ruso no es una traducción del inglés y viceversa: acabo de escribir una nota dos veces (odio traducir). Aquellos que quieran criticar mi inglés son enviados inmediatamente al final de la publicación, donde se sorprenderán por mi acento en un video de largas horas de duración. Veo mi énfasis no como un error, sino como una característica. Todos sabemos que muchos estadounidenses encuentran, por ejemplo, un acento británico nasofaríngeo atractivo. Es hora de dar el mismo estatus a un severo acento ruso. Para hacer esto, tantos rusos como sea posible deben pronunciar discursos en varios eventos internacionales. Nuestra contraseña es "años de mi hablar de May Hart".

Pero primero sobre la exposición.

Millones de consumidores de dispositivos en todo el mundo están viendo el Consumer Electronics Show (CES), que se llevará a cabo en Las Vegas en enero. Ellos, que nunca supieron qué es un D-trigger, argumentan que cuatro gigahercios es mejor que tres en los últimos procesadores de AMD y Qualcomm. Pero hay una exposición centrada no en los consumidores, sino en los desarrolladores de electrónica. Esta exposición se llama Design Automation Conference (DAC), y en algunos años también tiene lugar en Las Vegas, pero no en diciembre, sino en junio.

Millones de amantes de los dispositivos ven cada año el Consumer Electronics Show (CES) que se realiza en Las Vegas en enero. Esas personas, que nunca aprendieron la función de un D-flip-flop y cómo se calcula el tiempo estático, discuten frecuencias de gigahercios después de leer los últimos artículos en la revista Wired que perciben como una publicación técnica. Sin embargo, hay otra conferencia, no para los consumidores, sino para los creadores de productos electrónicos. Esta conferencia se llama Design Automation Conference (DAC) y también tiene lugar en Las Vegas, aunque no todos los años, y no en enero, sino en junio.

La industria de la automatización del diseño electrónico (EDA) crea software para diseñadores de hardware. EDA está controlada por tres grandes empresas: Synopsys, Cadence y Mentor Graphics (ahora parte de Siemens). Tanto Synopsys como Cadence tienen un conjunto completo de productos, necesarios para diseñar y simular un chip digital en múltiples niveles. El flujo de diseño, llamado RTL2GDSII, comienza desde la especificación y codifica el comportamiento del ciclo del circuito en lenguaje de descripción de hardware (Verilog o VHDL), continúa sintetizando esta descripción en un gráfico de elementos lógicos (netlist), luego continúa colocando la netlist en un físico plano del chip y enrutamiento de los cables en el chip para conectar las celdas estándar, los componentes básicos de los ASIC (Circuitos integrados específicos de la aplicación).

Tres grandes empresas dominan la industria de la automatización del diseño electrónico: Synopsys, Cadence y Mentor Graphics (que Siemens compró hace un par de años). Synopsys y Cadence han creado un software que cubre toda la ruta de diseño RTL2GDSII. Describí brevemente esta ruta en mi

artículo anterior de DAC hace cuatro años:

En los últimos 25 a 30 años, el diseño del microcircuito se escribe con mayor frecuencia en el lenguaje de descripción del equipo Verilog (en Europa y entre los militares - VHDL), después de lo cual un programa especial (síntesis lógica) convierte el diseño en un gráfico de cables y primitivas lógicas, otro programa (análisis de tiempo estático) le dice al diseñador si se ajusta al presupuesto de velocidad, y el tercer programa (colocar y encaminar) presenta este diseño en el sitio del chip.

Cuando el diseño pasa por todas las etapas: codificación en un veril, depuración, verificación, síntesis, análisis de tiempo estático, planificación del piso, lugar-n-ruta, extracción de parásitos, etc. - resulta un archivo llamado GDSII, que se envía a la fábrica, y la fábrica hornea chips. Las fábricas más famosas de este tipo son propiedad de Taiwan Semiconductor Manufacturing Company o TSMC.

John Sanguinetti, un gurú de Verilog desde 1980. John fue fundador de una empresa llamada Chronologic Simulation que, en la década de 1990, creó VCS, un simulador de código compilado Verilog. Este simulador ahora es propiedad de Synopsys. VCS es utilizado por la mayoría de las grandes compañías electrónicas. VCS trajo a Synopsys mil millones de dólares en ingresos.

Al costado de la sala de exposición está John Sanguinetti, uno de los primeros gurús del verilogue de la década de 1980 y fundador de Chronologic Simulation. Esta compañía le dio al mundo el rápido simulador de código compilado Verilog (VCS), que ahora es propiedad de Synopsys. Este simulador es utilizado por la mayoría de los principales desarrolladores de chips. VCS trae miles de millones de dólares de Synopsys:

Mentor Graphics ahora es parte de Siemens, la tercera compañía EDA más grande. A diferencia de Synopsys y Cadence, Mentor Graphics no tiene una línea completa de herramientas RTL2GDSII. Sus dos fuentes de ingresos más reconocidas provienen de Calibre, un conjunto de herramientas de verificación de diseño físico, y Veloce, un emulador de hardware. Calibre incluye, por ejemplo, una herramienta que verifica las reglas de diseño geométrico (ancho, espacio, cerramiento) en los "planos" finales del chip. Veloce utiliza chips similares a FPGA que

simulan emular diseños de Verilog realmente rápido.

Mentor Graphics, la tercera compañía más grande en la industria de EDA, a finales de 2016 se convirtió en parte de Siemens. A diferencia de Sinopsis y Keydens, Mentor no tiene toda la cadena de programas que cubren la ruta RTL2GDSII. Dos fuentes principales de ingresos para Mentor son el paquete de software Calibre, que realiza verificaciones en la etapa final del diseño del microchip, y el emulador Veloce (pronunciado Velochi). Un ejemplo de verificación en Calibre es la distancia mínima entre las pistas en el chip

para que no haya efectos de antena .

UPD: corregido sobre la base del comentario de amartología : la antena generalmente se trata de otra. Ocurre cuando una pista se vuelve tan grande que comienza a funcionar como una antena, recibiendo una señal a la frecuencia de las oscilaciones de plasma para grabar durante la producción.Y el emulador Veloce utiliza ASIC en forma de FPGA para

simular rápidamente emulaciones de circuitos descritos en el nivel lógico, es decir, en el veril.

Además de los proyectos altamente rentables de Calibre y Veloce, Mentor siempre tuvo una gran cantidad de otros proyectos, productos, servicios, capacitaciones y programas educativos. Por ejemplo, Mentor está cultivando el campo de la verificación funcional, una parte muy importante del flujo de trabajo del diseño digital.

Además de proyectos altamente rentables como Calibre y Veloce, Mentor tiene muchos otros proyectos, productos, servicios, proyectos de investigación y programas educativos. Por ejemplo, en Mentor, se dedican a la verificación funcional, una parte crítica del proceso de producción:

Varias pequeñas empresas, incluidas Doulos, Willamette HDL y Sunburst Design, venden capacitación en verificación de hardware a grandes y medianas empresas electrónicas. Tal nicho existe porque las universidades no enseñan el arte de la verificación funcional adecuadamente y no adoptan nuevas tecnologías, como SystemVerilog, UVM, verificación formal usando afirmaciones concurrentes, estímulo portátil, etc.en su currículo durante décadas. Incluso Stanford no lo tiene en su plan de estudios hasta donde yo sé por hablar con sus graduados.

La verificación funcional alimenta a varias pequeñas empresas que venden capacitaciones de SystemVerilog y UVM a grandes corporaciones a precios refrescantemente altos, como un par de miles de dólares por persona. Estos incluyen Doulos, Willamette HDL, Sunburst Design y otros:

Otra pequeña empresa llamada Verific. Tienen solo un puñado de personas, pero tienen mucho éxito en su nicho. Verific vende analizadores SystemVerilog adoptados por importantes compañías de EDA, tanto grandes como pequeñas.

Aquí hay otra pequeña empresa, solo unas pocas personas, pero muy exitosa de este tipo llamada Verific. Ella vende el analizador de Verilog, que muchas compañías de EDA usan:

El fundador de Verific da una entrevista a un popular sitio web de EDA llamado EDA Cafe. Hay varios otros sitios web populares de EDA, incluido deepchip.com de John Cooley, pero esta vez no conocí a John Cooley en el piso de DAC.

Aquí está el fundador de Verific dando una entrevista a EDA Cafe, un sitio web popular en la industria:

Ahora hablemos de FPGA.

Ahora hablemos de los FPGA, son PPVM (ahora me corregirán), son FPGA.

De qué se trata, también describí brevemente en mi

artículo anterior de DAC hace cuatro años:

En la versión más simple, un FPGA consiste en una matriz de células homogéneas, cada una de las cuales se puede cambiar a la función utilizando multiplexores conectados a los bits de la memoria de configuración. Una celda puede convertirse en una puerta AND con cuatro entradas y una salida, otra: un registro de un solo bit, etc. Cargamos una secuencia de bits de la memoria en la memoria de configuración, y el circuito electrónico dado se forma en el FPGA, que puede ser un procesador, controlador de pantalla, etc.

Los FPGA / FPGA no son procesadores, "programando" los FPGA (rellenando la memoria de configuración de FPGA) crea un circuito electrónico (hardware), mientras que al programar un procesador (hardware fijo) desliza una cadena de instrucciones de programa secuenciales escritas en él (software)

Los dos mayores productores de FPGA son Xilinx y Altera, ahora parte de Intel.

Las dos compañías más grandes que producen FPGA son Xilinx y Altera, ahora parte de Intel:

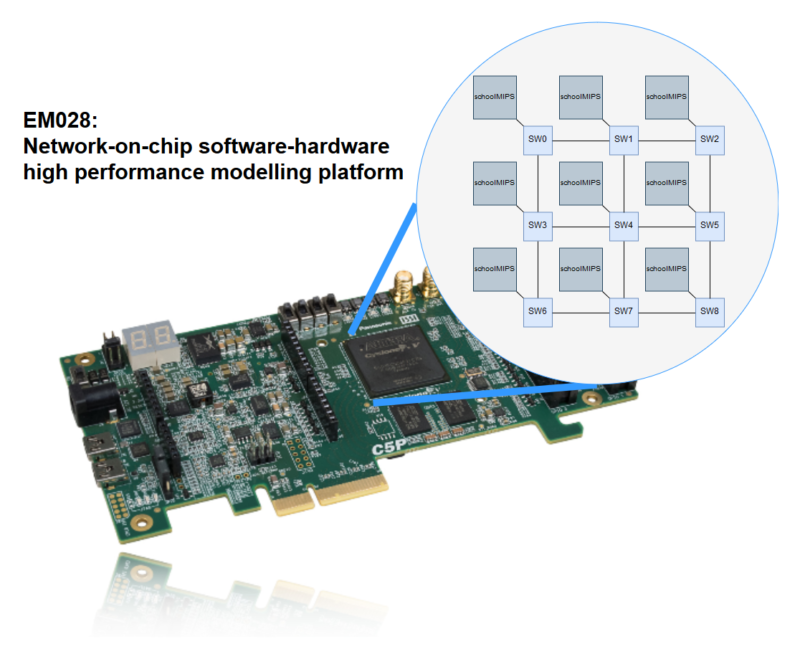

Esta semana, Intel recoge votos para la primera ronda del concurso Innovate FPGA. Una de las entradas rusas utiliza una malla de pequeños núcleos de procesador schoolMIPS.

schoolMIPS implementa un subconjunto de la arquitectura MIPS. Existe en varias variantes, incluido el ciclo único sin memoria de datos (el más simple), una versión con interrupciones, una versión canalizada, etc.

Por cierto, esta semana Intel está votando en el concurso Innovate FPGA, en el que

también participan

equipos rusos . Un proyecto es el

prototipo del sistema de multiprocesamiento basado en NoC . Este es un prototipo de red en un chip con una gran cantidad de nodos basados en procesadores de Stanislav Zhelnio

sparf (basado en el libro de Harris & Harris "Síntesis digital y arquitectura de computadoras")

https://github.com/MIPSfpga/schoolMIPS . Hace estudiante de 4 años en MIEM NRU HSE:

El mundo de los FPGA no se limita a Xilinx y Altera / Intel. Hay varios proveedores mucho más pequeños, como Lattice y Microsemi / Actel, e incluso pequeñas empresas que no diseñan los chips finales en sí mismos, licencian el diseño de bloques de celdas FPGA a compañías ASIC. Una aplicación útil sería crear un coprocesador reconfigurable conectado a un núcleo de CPU fijo de alta frecuencia. Otra aplicación es la seguridad: algunas empresas quieren ocultar sus secretos en una lógica reconfigurable en lugar de mostrar el diseño de su lógica fija a un investigador motivado con microscopio electrónico y mucho tiempo.

Pero hay menos jugadores en el mundo de FPGA, por ejemplo, aquí hay dos compañías que licencian el diseño de bloques de FPGA que pueden integrarse en circuitos fijos de múltiples corridas para darles flexibilidad.

Cada DAC tiene varios proveedores de placas FPGA. No los vendedores de tableros de estudiantes baratos como Digilent y Terasic, que comienzan desde $ 55, sino tableros FPGA para prototipos ASIC que pueden costar $ 30,000, $ 100,000 o más.

El DAC es atendido tradicionalmente por los fabricantes de placas FPGA. No venden tarjetas de estudiante baratas por $ 55 dólares, sino tableros FPGA serios por $ 55 _ mil dólares y más. Su cliente no es un estudiante, sino un equipo severo de desarrollo de ASIC que utiliza tableros grandes para la creación de prototipos.

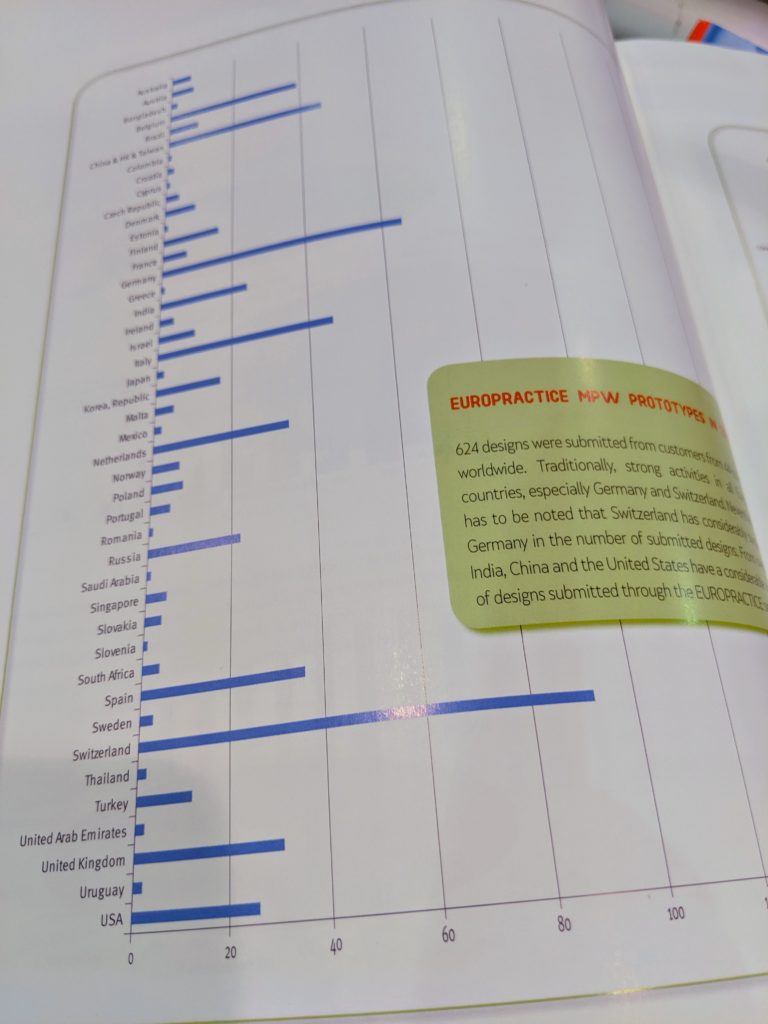

¿Qué pasa si un investigador hizo alguna prueba de concepto usando FPGA y ahora quiere fabricar su propio ASIC? Un pedido comercial típico para fabricar un ASIC generalmente requiere el pago inicial de ~ $ 300K a ~ $ 3,000,000 dependiendo de la tecnología del proceso. Sin embargo, hay empresas especializadas, Europractice en Europa y MOSIS en EE. UU., Que venden servicios de "transporte" en pequeñas cantidades o servicios de obleas multiproyecto (MPW), comenzando con solo $ 3000 por tecnología de 180 nm o solo decenas de miles de dólares por algo moderno, como 28nm.

Pero, ¿qué pasa si un estudiante o una empresa dura quisiera hacer un ASIC real en una fábrica y hay poco o poco dinero? O, si no lo siente, ¿es un chip de prueba o un lote muy pequeño? Para hacer esto, en Estados Unidos hay una empresa MOSIS, y en Europa: Europractice. Unos pocos miles de dólares, y tiene en sus manos el chip que diseñó para tecnología como 180 nanómetros. Un par de decenas de miles, y tiene en sus manos su chip con tecnología más reciente, por ejemplo 28 nanómetros, como el quinto iPhone. Observo que para la producción comercial en masa, el pago inicial a la fábrica es de cientos de miles de dólares por tecnologías antiguas a dos o tres millones por tecnologías nuevas.

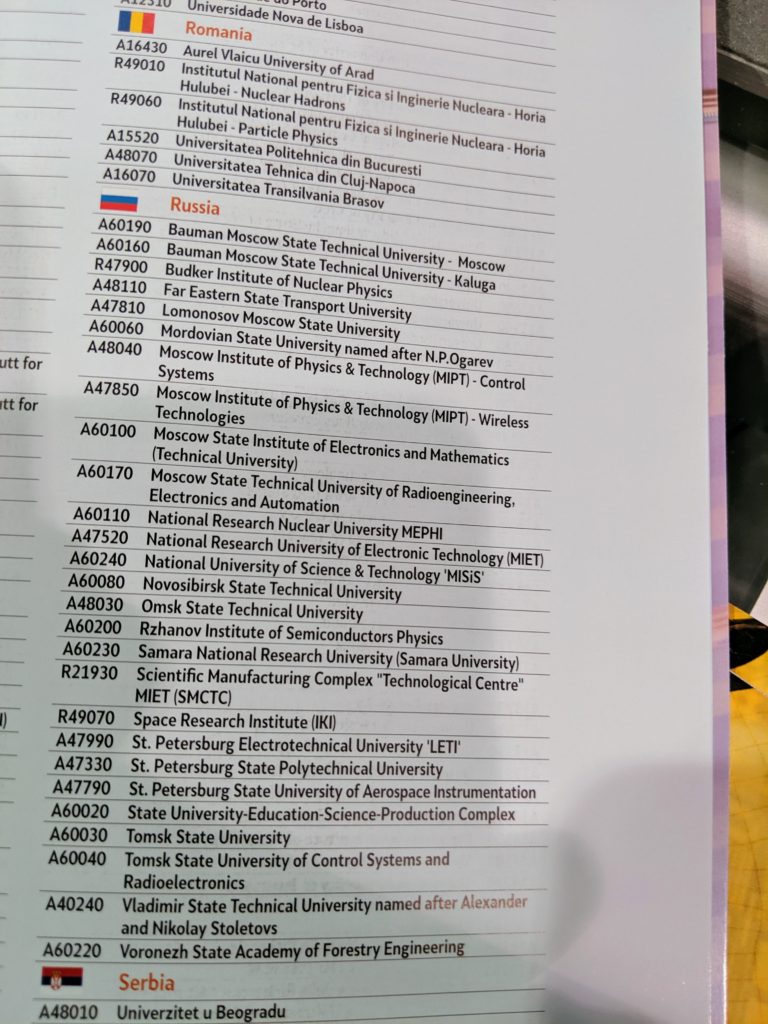

Es interesante que Europractice tenga clientes en Rusia, incluso en Omsk. Admita quién diseña los ASIC en Omsk.

Europractice tiene una serie de empresas rusas, incluida alguien en Omsk:

Hay empresas con modelos de negocio que son algo misteriosos para mí. Por ejemplo, no entiendo cómo esta compañía a continuación puede sobrevivir en un nicho de complemento Eclipse. Supongo que obtienen la mayoría de los ingresos vendiendo algunos servicios de consultoría.

Hay empresas sobre las que no entiendo cómo ganan. Por ejemplo, este está vendiendo un complemento Eclipse muy especializado. Seguramente no viven de él, sino de algún tipo de consulta.

Otra empresa de nicho con modelo de negocio no obvio. Traducen una descripción de registros visibles por software en lógica de pegamento Verilog y otros archivos de interfaz. Supongo que esta compañía puede tener algún gran cliente de tipo Cisco que se enganchó a su tecnología hace mucho tiempo y les paga desde entonces.

Otra empresa de nicho con un modelo de negocio no obvio. Traducen la descripción de los registros disponibles para el programador en verilog y archivos de interfaz. Probablemente tengan algún cliente importante como Cisco, que hace muchos años se enamoró de su herramienta, y desde entonces ha estado pagando, ya que es un fastidio contratar a un cliente para administrar a su ingeniero.

Un caballero melancólico de Huawei describió sus logros en chips de red. Huawei obviamente depende de las herramientas EDA de EE. UU., Incluso más que en el mercado de Android y los núcleos de CPU ARM. La cantidad de dinero y la cantidad de expertos técnicos necesarios para desarrollar un equivalente del compilador Synopsys IC es, en mi opinión, mucho mayor que los recursos necesarios para diseñar un competidor de gama alta para núcleos ARM.

Un representante de Huawei también se sentó en la exposición con una expresión de tristeza brillante en su rostro. Observo que si el gobierno de los EE. UU. Obliga a las compañías estadounidenses de EDA a prohibir a los chinos, la situación de China será mucho peor de lo que es ahora, ya que es técnicamente más difícil clonar el Compilador de IC Synopsys que los núcleos de procesador ARM y Android Market.

Todos los DAC desde 1998 tenían al menos una compañía que desarrollaba otro compilador C-to-Verilog. En 1998 fue

mi propia startup . Este año es alguien más:

Desde 1998, ha habido al menos una compañía en DAC que compila C en Verilog. En 1998, esa empresa era mi propia startup. Este año alguien más:

Este caballero se gana la vida vendiendo soluciones que contrarrestan el llamado "Zakladki" (un término ruso, un plural de "Zakladka"). Le expliqué el significado del término y estuvo de acuerdo en que esto es lo que vende.

Aquí hay un compañero que se gana la vida con los marcadores de los analizadores en los procesadores:

Traje a DAC a mi hija estudiante para que pueda ver cómo papá se gana la vida:

Llevé a mi hija a Las Vegas para que pudiera ver cómo la gente gana dinero en el duro mundo industrial de la industria electrónica y se dio cuenta de que los dólares de papá no crecían en los árboles:

Fiesta después de la exposición:

En la fiesta después de la exposición:

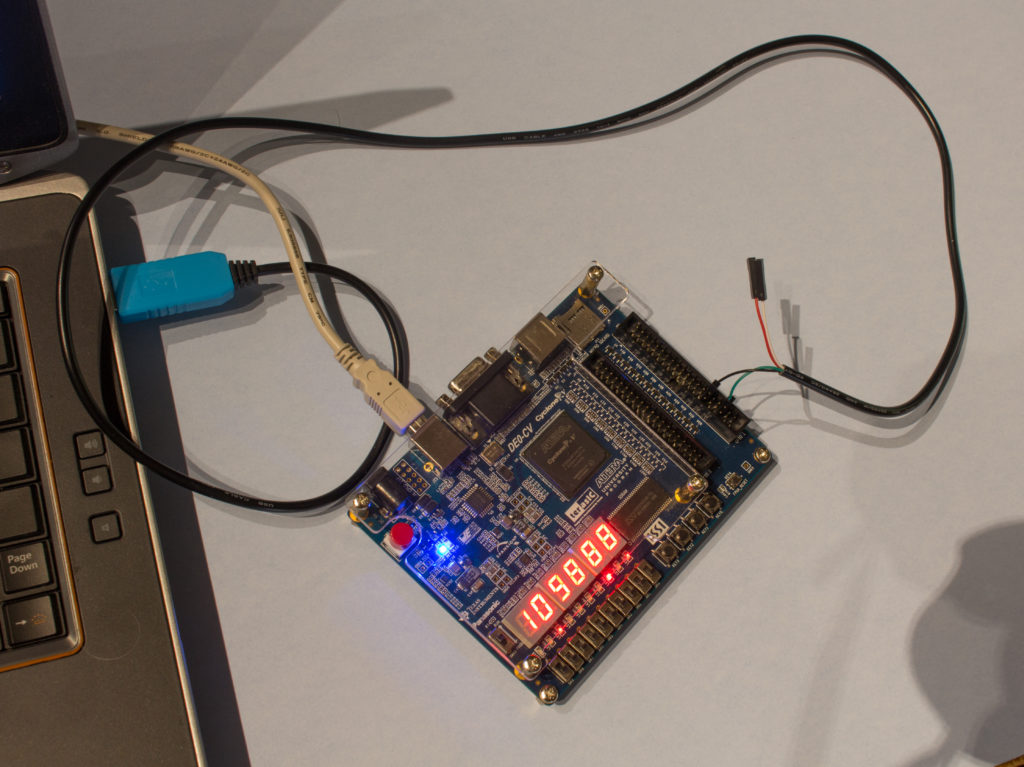

Después de la exposición, hice el MIPS Open Developer Day junto con mis colegas de Wave Comnputing. Contamos con varias personas de algunas de las empresas mencionadas más arriba + mis amigos rusos de

VivEng , un servicio de diseño de señales mixtas de Silicon Valley de California que también tenía algunos clientes en Zelenograd, un Silicon Valley ruso. Primero hicimos una

presentación , luego los participantes hicieron algunos ejercicios en las placas Digilent Nexys4 DDR y Terasic DE10-Lite FPGA.

Luego, junto con mis colegas, conduje el seminario abierto MIPS. Asistieron camaradas de algunas de las compañías descritas, incluidas aquellas que otorgan licencias de herramientas FPGA y EDA integradas, venden servicios para producción, realizan capacitación de verificación y también hacen chips como tales. Y también mis viejos amigos de la compañía rusa

VivEng . Mis colegas y yo mostramos

estas diapositivas , después de lo cual los participantes probaron ejemplos sobre FPGA Digilent Nexys4 DDR y Terasic DE10-Lite.

Para repetir los resultados, puede descargar y combinar dos paquetes:

Si desea reproducir los resultados, puede hacer lo siguiente:

- Vaya a https://www.mipsopen.com/mips-open-components/mips-open-fpga-getting-started-guide .

- Descargue el paquete estándar MIPSfpga 2.0.

- Vaya a https://github.com/MIPSfpga/mipsfpga-plus .

- git clone github.com/MIPSfpga/mipsfpga-plus.git

- Copie los archivos RTL principales del paquete MIPS Open FPGA al subdirectorio principal del paquete MIPSfpga +; consulte las instrucciones en https://github.com/MIPSfpga/mipsfpga-plus/tree/master/core

Intel FPGA Quartus Prime Lite Edition o Xilinx Vivado, así como la cadena de herramientas Codescape GCC Bare Metal Tool, deben estar instaladas en su computadora. Después de eso, puede seguir las instrucciones de las diapositivas:

Debe tener Intel FPGA Quartus Prime Lite Edition o Xilinx Vivado instalado en su sistema, así como Codescape GCC Bare Metal Toolchain. Después de esto, puede seguir las instrucciones de las diapositivas:

- cd your_git_directory / boards / board_directory (por ejemplo de10_lite o nexys4_ddr)

- hacer toda la carga

- Presione restablecer (o TECLA 0 en algunas placas) para restablecer el procesador.

- El programa predeterminado codificado debería comenzar a funcionar.

- cd your_git_directory / programs / 00_counter (u otro programa)

- hacer programa srecord uart

- Si la computadora usa una conexión en serie que no sea ttyUSB0 (el valor predeterminado), entonces:

- hacer programa srecord uart UART = 1 (o 2, 3, etc.)

- El programa cargado a través de USB a UART ahora se está ejecutando.

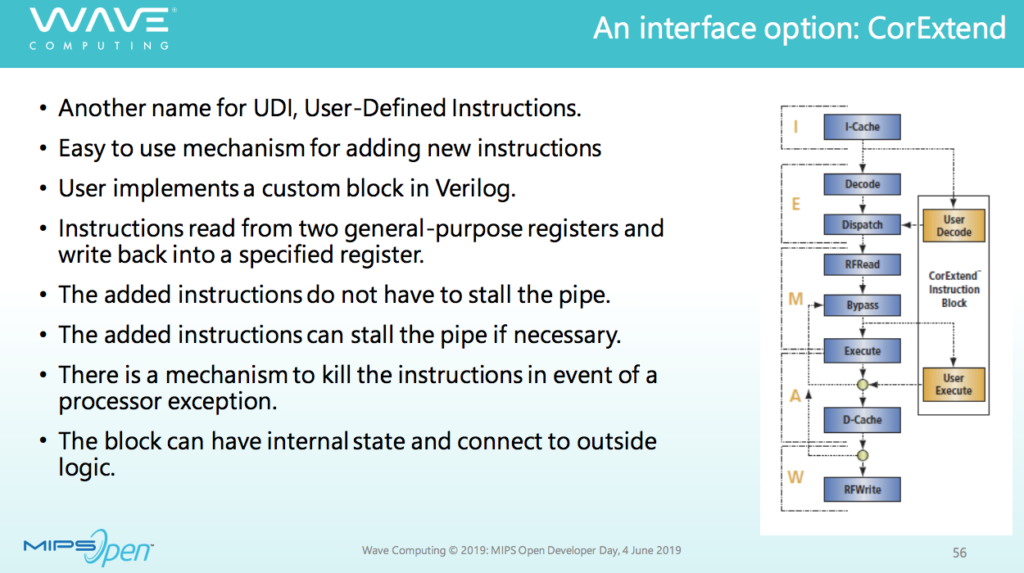

En la presentación, mostré cómo incrustar un bloque en el procesador que decodifica y ejecuta instrucciones adicionales para el sistema principal de comandos que el diseñador del sistema puede determinar en un chip. El bloque se puede sintetizar y formar parte del microcircuito o configurarse en el FPGA / FPGA.

Las instrucciones adicionales se mueven a lo largo de la tubería del procesador junto con las principales. Reciben datos de registros generales visibles para el programador y pueden devolver el resultado al registro. Estas instrucciones también pueden guardar algún estado en el coprocesador. Pueden ser eliminados por excepciones si ocurre una excepción, por ejemplo, en la tubería siguiendo estas instrucciones:

La presentación tiene una explicación detallada sobre cómo agregar instrucciones de procesadores definidos por el usuario al núcleo de la CPU MIPS microAptiv UP y sintetizarlo junto con un simple SoC para la placa FPGA:

Fragmento de código de hardware Verilog del texto de muestra. Este código implementa, en el Nivel de transferencia de registro (RTL), una instrucción especializada para calcular una red neuronal convolucional:

Un fragmento de un módulo CorExtend personalizado que implementa una instrucción definida por el usuario (UDI) para un caso especial de cálculo de redes neuronales:

Mañana viajaré a Rusia para ayudar con otro seminario, no para profesionales de electrónica y EDA, sino para niños interesados en explorar carreras en diseño microelectrónico digital. Para este viaje, creé un simple procesador de video 2D integrado con el núcleo abierto MIPS FPGA, así como un ejemplo de un juego solo de hardware (sin CPU o software) para VGA. A los niños les gustan los juegos y voy a usar el diseño del juego para enseñarles los conceptos básicos de la metodología RTL:

Y el próximo lunes

8 de julio, enseñaré los conceptos básicos del desarrollo de circuitos digitales para escolares en Zelenograd .

Para él, escribí ejemplos de la implementación de gráficos de sprites simples en FPGA. Un circuito sintetizado a partir de verilogue dibuja sprites en una pantalla VGA.

Aquí hay un ejemplo de trabajo en un hardware limpio (

códigos fuente en github ). Una variante del combate naval, donde un satélite de torpedos rojos busca una cruz azul enemiga:

Y aquí hay un ejemplo de una combinación de hardware y software: un saludo de los sprites.

Parte de hardware y

parte de software :

Sí, y prometí dar mis discursos en Las Vegas. Aquí hay una pieza:

Vista del Strip de Las Vegas cuando oscurece, pero todavía no hay multitudes:

Y la vista de la calle en la franja, cuando ya es de noche, pero todavía no hay multitudes:

Durante dos días en Las Vegas no tuve la oportunidad de jugar, así que jugué con $ 1 cuando nuestro avión de regreso a San José estaba abordando en el aeropuerto de Las Vegas:

Durante todo este tiempo, nunca jugué en Las Vegas, porque di una vuelta por la exposición y hablé sobre temas electrónicos, luego realicé un seminario. Pero al abordar el avión, sin embargo, noté que perdió un dólar: