Este artículo describirá la instalación y el uso de software gratuito para modelar circuitos lógicos digitales en Verilog como una alternativa a los productos comerciales Incisve de Cadense y ModelSim de MentorGraphics. Comparación de simulaciones en ModelSim y Verilator. También se considerará una metodología de verificación universal, UVM.

Instalación del software SystemC UVM

1. El verilador

Uno de los lenguajes de descripción de hardware es verilog. Puedes escribir un módulo en este idioma.

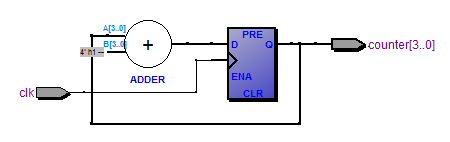

Por ejemplo, hay un esquema de contador:

Su código se verá así:

reg [3:0]counter; always @(posedge clk or posedge reset) if(reset) counter <= 4'd0; else counter <= counter + 1'd1;

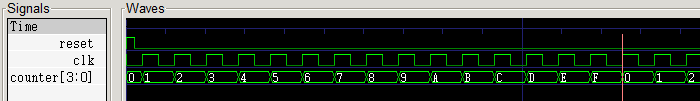

Después de la simulación, obtenemos las formas de onda:

Se puede ver que el siguiente valor, uno más que el anterior, se escribirá en los registros del contador a lo largo del frente de la frecuencia del reloj.

Un módulo escrito puede tener una estructura más compleja, que será difícil de verificar manualmente todos los estados de. Necesitaremos pruebas automatizadas. Para esto, es necesario desarrollar un entorno de prueba en uno de los lenguajes de programación. El entorno de prueba nos dará la oportunidad de realizar una verificación funcional completa del dispositivo.

Para probar el código del proyecto, además de lenguajes como Verilog, SystemVerilog, Python (para escribir modelos), puede usar el lenguaje

SystemC . SystemC es un lenguaje de diseño y verificación a nivel de sistema para modelos a nivel de sistema implementado como una biblioteca C ++ de código abierto.

Una forma de verificar los módulos Verilog usando SystemC es traducir los archivos Verilog a C ++. Ayúdanos con este verilador.

Verilator es el simulador HDL Verilog gratuito más rápido que supera la mayoría de los simuladores comerciales. Verilator compila SystemVerilog sintetizado (por lo general, este no es el código del banco de pruebas), así como algunas declaraciones de SystemVerilog y Synthesis en código C ++ o SystemC de subproceso único o multiproceso. Verilator fue diseñado para grandes proyectos donde el rendimiento de la simulación es primordial y es particularmente adecuado para generar modelos de procesadores ejecutables para equipos de desarrollo de software embebido. Verilator se utiliza para simular muchos diseños de puerta de enlace multimillonarios muy grandes con miles de módulos y es compatible con muchos proveedores de tecnología IP, incluida la IP de Arm y todos los famosos proveedores de IP RISC-V.

Verilator puede no ser la mejor opción si espera un reemplazo completo para NC-Verilog, VCS u otro simulador comercial de Verilog, o el simulador de comportamiento Verilog para un proyecto muy pequeño. Sin embargo, si está buscando una forma de portar Verilog sintetizado a C ++ o SystemC, y su equipo es libre de escribir solo código C ++, este es un compilador de Verilog gratuito para usted.

Para instalar la última versión en Ubuntu: descargue el archivo

desde el enlace desde el sitio oficial .

Instalar:

2. GTK Wave

GTKWave es un visor de forma de onda con todas las funciones y también le permite convertir archivos de formato vcd a fst, más conveniente y más rápido.

Instalar:

sudo apt-get install gtkwave

3. SYSTEMC

Un lenguaje para diseñar y verificar modelos a nivel de sistema implementados en forma de una biblioteca C ++ de código abierto.

Como se mencionó anteriormente, verilator es compatible con systemc, por lo que debe crear un proyecto en el que el punto de referencia de prueba se describirá en systemc y los archivos de origen en verilog sintetizado. Para hacer esto, necesitamos las bibliotecas del compilador g ++ proporcionadas por Accelera. Accellera Systems Initiative es una organización independiente y sin fines de lucro dedicada a crear, respaldar, promover y promover estándares de diseño, simulación y verificación a nivel de sistema para su uso en la industria electrónica mundial.

Descargar el archivo:

http://accellera.org/images/downloads/standards/systemc/systemc-2.3.1a.tar.gzInstalar:

tar -xvf systemc-2.3.1a.tar.gz cd systemc-2.3.1a mkdir objdir sudo ./configure --prefix=/usr/local/systemc-2.3.1a/ sudo make sudo make install cd ../

4. UVM para SYSTEMC

Este artículo revisará un proyecto que implementa herramientas de verificación UVM. La verificación es una confirmación de la conformidad del producto final con los requisitos de referencia predefinidos. Una de sus herramientas de verificación pueden ser las pruebas. Para ejecutar secuencias de prueba en modelos de dispositivos reales al nivel de descripciones RTL, es necesario desarrollar un entorno de prueba.

UVM - (Metodología de verificación universal) es una metodología de verificación universal, un estándar que permite el desarrollo eficiente y la reutilización de entornos de validación de bloque de IP. UVM es una metodología de verificación cuyas tareas incluyen organizar un entorno efectivo alrededor de la unidad bajo prueba. Sus ventajas:

- estructura clara en forma de bloques dedicados que deciden específicos

- tareas

- la capacidad de reutilizar bloques en proyectos posteriores;

- la máxima automatización posible de la verificación;

- la información de informes más completa que permite, cuando ocurre un error, identificar sus causas de la manera más rápida y precisa posible y sugerir soluciones.

Las metodologías UVM constan de dos partes: un conjunto de reglas para construir un entorno de prueba y una biblioteca de bloques en blanco para verificación, por ejemplo, un generador de texto, un colector de estadísticas, etc. La principal ventaja de UVM es su versatilidad y compatibilidad con entornos de terceros.

Como systemc admite la metodología UVM, pasemos a instalar las bibliotecas necesarias.

Descargar el archivo:

https://www.accellera.org/images/downloads/drafts-review/uvm-systemc-1.0-beta2.tar.gzInstalar:

tar -xvf uvm-systemc-1.0-beta2.tar.gz cd uvm-systemc-1.0-beta2/ mkdir objdir sudo ./configure --prefix=/usr/local/systemc_uvm/ --with-systemc=/usr/local/systemc-2.3.1a sudo make sudo make install

Creamos una alianza:

sudo mkdir /usr/local/uvm_systemc_aliance

Copie el contenido de las carpetas / usr / local / uvm_systemc_aliance / y /usr/local/systemc-2.3.1/ a esta carpeta

Descargue el proyecto terminado en el enlace:

https://github.com/paprikun/SYSTEMC/Abra la carpeta de ejemplos de verilator.

La carpeta rtl contiene una descripción del dispositivo. En este ejemplo, es un controlador PWM.

En el archivo makefile de la carpeta sim para construir el proyecto.

En la carpeta tb está el código para el verificador. La carpeta tb / uvm contiene un ejemplo de entorno uvm. El archivo principal es un punto de entrada en las pruebas; conecta el dispositivo bajo prueba con el entorno uvm.

Intentamos construir el proyecto desde la carpeta sim con el comando make all. Vemos un error:

/usr/local/uvm_systemc_aliance//include/systemc.h:120:16: error: 'std::gets' has not been declared using std::gets;

Lo arreglamos reemplazando la línea 120:

#if defined(__cplusplus) && (__cplusplus < 201103L) using std::gets; #endif

Una vez más, intentamos ejecutar el banco de pruebas y tropezar con la advertencia:

/usr/local/uvm_systemc_aliance//include/sysc/packages/boost/get_pointer.hpp:21:40: warning: 'template<class> class std::auto_ptr' is deprecated [-Wdeprecated-declarations] template<class T> T * get_pointer(std::auto_ptr<T> const& p)

Cambia auto_ptr a unique_ptr.

Proyecto de montaje y simulación

Ahora que las bibliotecas están instaladas y funcionando, estamos construyendo el proyecto: hacer todo. El archivo ejecutable simu debe aparecer en la carpeta sim. Este es un objeto creado por el compilador. Comenzamos con el equipo ./simu. Debería aparecer lo siguiente:

SystemC 2.3.1-Accellera --- Jun 28 2019 11:39:29 Copyright (c) 1996-2014 by all Contributors, ALL RIGHTS RESERVED Universal Verification Methodology for SystemC (UVM-SystemC) Version: 1.0-beta2 Date: 2018-10-24 Copyright (c) 2006 - 2018 by all Contributors See NOTICE file for all Contributors ALL RIGHTS RESERVED Licensed under the Apache License, Version 2.0 UVM_INFO @ 0 s: reporter [RNTST] Running test ... simulation real time = 9 sec UVM_INFO uvm_default_report_server.cpp(666) @ 179490249010 ps: reporter [UVM/REPORT/SERVER] --- UVM Report Summary --- ** Report counts by severity UVM_INFO : 1 UVM_WARNING : 0 UVM_ERROR : 0 UVM_FATAL : 0 ** Report counts by id [RNTST] 1 UVM_INFO @ 179490249010 ps: reporter [FINISH] UVM-SystemC phasing completed; simulation finished

Cuando finaliza la simulación, finaliza la grabación en forma de onda. El archivo simu.vcd se puede abrir con gtkwave:

Para mostrar las señales a la izquierda, seleccione SystemC, luego manteniendo presionada la tecla Mayús, seleccione cualquier señal y haga clic en Anexar. La información sobre herramientas aparece en la barra de herramientas cuando pasa el mouse por encima. El desplazamiento del mouse funciona, debe mantener presionada la tecla Mayús o Ctrl.

También hay formas de convertir este archivo a otro más pequeño.

Si hay modelosim hará la conversión. En la terminal, ingrese el comando vsim. En el terminal modelsim:

vcd2wlf simu.vcd simu.wlf

O usando gtkwave en la terminal de Linux:

vcd2lxt simu.vcd simu.lxt vcd2lxt2 simu.vcd simu.lxt2

Para comparar el tiempo de simulación, se creó un proyecto similar, pero ya para

Modelsim . Modelos de carpetasim_example. Del mismo modo creado entorno UVM. La sintaxis es similar a pesar del hecho de que hay diferentes idiomas. Si instaló Modelsim con soporte para uvm, puede ejecutar el comando make all.

Además del entorno en ambos proyectos, se tomó una simulación en tiempo real de las mediciones.

Con el tiempo, la diferencia resultó:

Como puede ver en la tabla, el verilador tiene una ventaja. Los datos se presentan para una PC con 8GB de RAM, un procesador de 8 núcleos, 800 MHz, cargando un núcleo.

Compare el tamaño del archivo:

Aquí el verificador pierde, pero puede experimentar creando formas de onda y trazar profundidad, el período de grabación (el comienzo y el final de la grabación de forma de onda se pueden cambiar). Con qué archivo trabajar depende de usted.

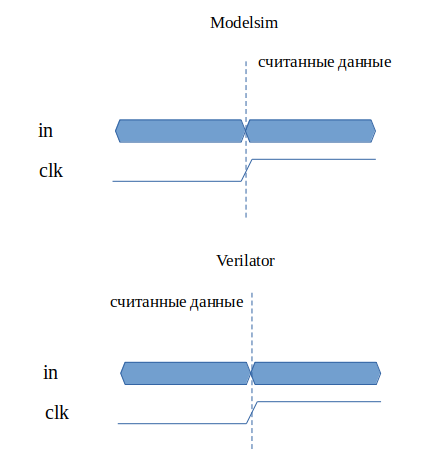

Durante las pruebas, además del tiempo de la simulación en sí, se encontró una discrepancia en la lectura de los datos de entrada del bus. Si los datos del bus en el bus cambian durante el frente clk, Modelsim lee los datos después del frente, verificador antes:

input clk; input [7:0] in; reg [7:0] in_last_ ; ... always @(posedge clk) begin ... in_last_ <= in; ... end

Durante las pruebas, este punto debe tenerse en cuenta, ya que parte del entorno de prueba para diferentes simuladores funcionará de manera diferente.

Además, el verificador no tiene en cuenta el estado "x" de la señal y traduce todo a "0";

BANCO DE PRUEBA UVM

Considere el entorno de prueba, la carpeta tb / uvm.

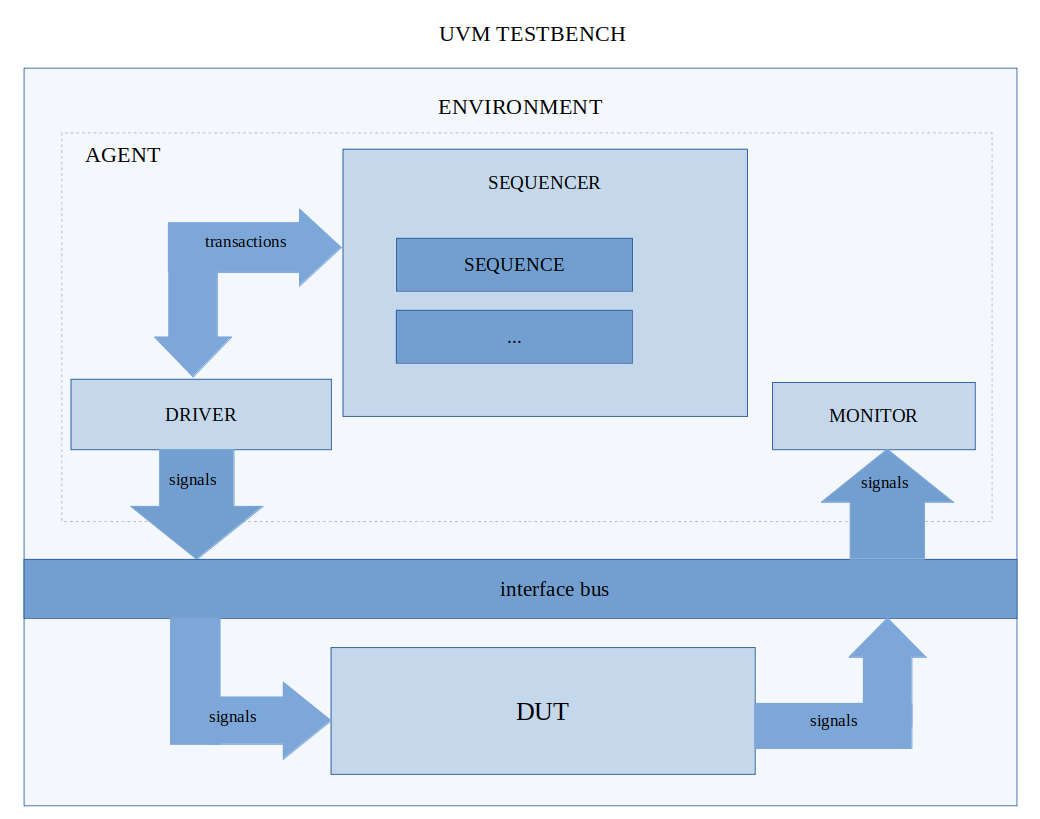

El banco de pruebas UVM es el entorno sobre el dispositivo. En este ejemplo, el dispositivo es un controlador PWM. Diagrama del entorno UVM:

Como puede ver en el diagrama, UVM consiste en bloques (clases). Cada bloque realiza sus funciones. El ejemplo muestra uno de los posibles diseños del entorno de prueba. El nombre y la funcionalidad de cada clase corresponde a la clase de la que se hereda. Consideremos cada clase con más detalle.

Archivo de entorno env.h o env.svh. Esta es una clase que puede contener una o más clases de agente, en las que se conectan tres clases: secuenciador, controlador, monitor. No hay agente en el ejemplo, pero su función se implementa en la clase env. Para la prueba necesitamos escribir alguna secuencia de acciones: secuenciación.

Pasemos al código de inicio de secuenciación:

sequence_[n]->start(sqr, NULL);

Secuenciador (secuenciador) - archivo sequncer.h. En el sistema verilog, resultó utilizar el secuenciador predeterminado. Una clase que contiene una o más secuencias (secuencia) (archivos secuencia_a.h, secuencia_a.svh). Cada secuencia es una cadena de acciones. Una de estas acciones puede ser enviar una transacción. Transacción: transferir datos de una clase a otra. La clase en la que se describen las transacciones es bus_trans. A continuación se muestra una descripción de dos clases, cada una de las cuales ideológicamente tiene sus propias funciones específicas: controlador y monitor.

Controlador: archivo drv.h, drv.svh. Una clase que recibe transacciones de un secuenciador y las traduce en señales. El conductor sirve como asistente de secuenciador en un nivel inferior. Considere enviar un paquete.

La secuencia abre una ventana de transacción, el controlador detecta este evento y comienza a recibir datos. La secuencia está esperando una respuesta del conductor. El controlador simula las señales para el dispositivo, luego le indica al secuenciador que la ventana se puede cerrar. La idea es que el secuenciador funcione a un nivel alto y el controlador a un nivel inferior.

Las señales se conectan a través del bus de interfaz al dispositivo. La interfaz se describe en los archivos vip_if.h, vip_if.svh.

A continuación, debe verificar si las señales de salida coinciden con las esperadas. Hay dos soluciones:

- Escribir un modelo para un dispositivo

- Verificación de señal a través del agente UVM

En el ejemplo, se considera la segunda opción. Para probar el dispositivo a nivel funcional, es necesario comparar la salida con la esperada. El requisito para el dispositivo era la corrección del ciclo de trabajo dado de la señal y el período de la señal. Para monitorear las señales de salida, se escribe una nueva clase: Monitor (archivo monitor.h, monitor.svh). Por lo general, en un entorno de prueba, el monitor transfiere las señales en la transacción (a un nivel superior) y se envía a la clase de comparación: cuadro de indicadores.

En este ejemplo, las señales se verifican de inmediato. En caso de discrepancia entre el valor esperado y el medido, la prueba se detiene.