Los procesos de fabricación intermedios, los diferentes tipos de transistores y muchas otras opciones agregan incertidumbre al proceso de fabricación de productos electrónicos.

Los fabricantes de productos electrónicos se están preparando para la próxima ola de procesos de fabricación de vanguardia, pero sus clientes se confundirán con un montón de opciones confusas, ya sea para desarrollar chips utilizando la tecnología de proceso de 5 nm, esperar 3 nm o elegir algo intermedio.

El camino a 5 nm está bien definido, a diferencia de 3 nm. Después de eso, el paisaje se confunde a medida que las fábricas agregan procesos de fabricación intermedios, como 6 nm y 4 nm. Cambiar a cualquiera de estos procesos técnicos es muy costoso y los beneficios no siempre son obvios.

Otro motivo de preocupación es la reducción de la base de fabricación. En el caso de los procesos técnicos más avanzados, la elección de los fabricantes es pequeña. Hubo varios fabricantes líderes en la industria, pero con el tiempo esta área se ha reducido debido a un fuerte aumento en el costo y una disminución en la base de usuarios. En general, cuantos menos fabricantes, menos opciones de tecnología y precio.

Hoy, Samsung y TSMC son los

dos únicos fabricantes que trabajan con procesos tecnológicos de 7 nm o menos, aunque esto puede cambiar. Intel y la empresa china SMIC están desarrollando procesos de fabricación avanzados. Intel, que no es el jugador más importante en el campo de la producción comercial, está experimentando problemas con el desarrollo de la tecnología de proceso de 10 nm. Y no está claro si SMIC podrá entregar 7 nm, ya que este tema aún está en la etapa de investigación y desarrollo (lo mismo sucede con Intel con la tecnología de proceso de 10 nm).

En cuanto a los procesos de fabricación más avanzados, Samsung y TSMC trabajan con 7 nm utilizando transistores finFET, y ambos fabricantes continuarán esto a 5 nm. A diferencia de los transistores planos tradicionales, los finFET son estructuras tridimensionales con un mejor rendimiento y menos fugas.

Luego, a 3 nm, Samsung pasará de finFET a la nueva arquitectura de transistor FET de nano hoja, que es un desarrollo de la tecnología finFET. TSMC aún no ha revelado sus planes para 3 nm, dejando a muchos clientes en el limbo. TSMC, según las fuentes, pesa una variedad de opciones, que incluyen nanocapas, nanocables y aletas forzadas. Intel, TSMC y otros también están trabajando en nuevas formas de empaque avanzado como posibles opciones para la reducción de escala.

Sin embargo, a 3 nm, el tamaño de la tecnología de transistores puede ir en diferentes direcciones. finFET todavía puede jugar, pero esta tecnología necesita algunos avances. Aparentemente, la industria tendrá que prepararse para la transición a la nueva arquitectura de la tecnología de proceso de 3 nm, y la próxima tecnología de proceso intermedio a 2 nm, a juzgar por los planes de desarrollo de una organización que trabaja en esta área.

"5 nm todavía es finFET", dijo Naoto Horiguchi, director del programa en Imec. - Digamos que a 3 nm ingresaremos en un período de transición de finFET a otras arquitecturas. Creemos que serán nanocapas ”.

Los FET de nanocapa se relacionan con la arquitectura de los transistores gate-all-around (GAA). Y esta no es la única opción. “La industria es muy conservadora. Sus participantes tratarán de exprimir todo, desde finFET hasta el límite ”, dijo Horiguchi. - En el proceso de fabricación de 3 nm, tenemos la oportunidad de usar finFET. Pero necesitaremos hacer varias innovaciones de finFET, mejorarlo en general ”.

¿Se mantendrán los fabricantes de chips con la tecnología de proceso de 7 nm, migrarán a 5 nm, 3 nm o al intermedio? 7 nm proporciona un rendimiento suficiente para casi todas las aplicaciones, por lo que este proceso durará mucho tiempo. Afuera hay varias opciones de alto rendimiento, y todas cuestan más. Y veremos si estas tecnologías tienen tiempo de aparecer a tiempo.

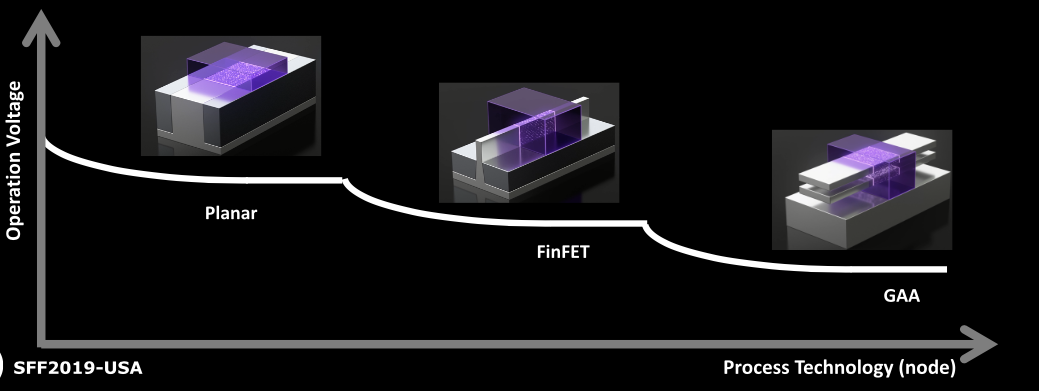

El voltaje de funcionamiento de varios procesos de fabricación es transistores planos, finFET y nanocapa FET.

El voltaje de funcionamiento de varios procesos de fabricación es transistores planos, finFET y nanocapa FET.Ruina de produccion

El chip consta de muchos transistores que actúan como interruptores. Durante muchas décadas, el progreso de los circuitos integrados fue consistente con la ley de Moore, según la cual la densidad de los transistores en un dispositivo se duplica en un período de 18 a 24 meses.

En un ritmo similar, los fabricantes introdujeron nuevos procesos tecnológicos con una mayor densidad de transistores, lo que permitió a la industria reducir el costo de los chips en términos de la cantidad de transistores. En cada proceso de fabricación, los fabricantes escalaron las especificaciones del transistor 0,7 veces, lo que permitió a la industria aumentar la productividad en un 40% con el mismo consumo de energía y una reducción de dos veces en el área.

La industria de circuitos integrados siguió esta fórmula y floreció. Desde la década de 1980, ha allanado el camino para PC rápidas a precios reducidos.

Para 2001, ya había al menos 18 fabricantes con fábricas donde podían fabricar chips a 130 nm, que en ese momento era un proceso técnico avanzado, según el IBS. También entonces, aparecieron varios nuevos fabricantes más, fabricando chips a medida en las fábricas de otras personas. Además, la fabricación de chips se practicaba en laboratorios que los desarrollaron, pero no tenían su propia producción.

A finales de la década, el costo de los procesos de producción y fabricación aumentó. Incapaces de hacer frente al aumento de precios, muchos fabricantes de chips cambiaron al modelo fab lite. Produjeron algunos chips en casa, y el resto fueron subcontratados.

Con el tiempo, menos fabricantes de chips fabricaron dispositivos avanzados en sus propias instalaciones. Algunos se deshicieron completamente de la producción o abandonaron este negocio.

Sin embargo, en la década de 2000, apareció un modelo de negocio de talleres de silicio. Los talleres se quedaron atrás de Intel y otras compañías de tecnología, pero les dieron acceso a diversos procesos a las compañías de diseño.

El siguiente cambio importante ocurrió en la etapa de 20 nm, cuando los transistores planos tradicionales chocaron contra una pared y encontraron

un efecto de canal corto . En respuesta, Intel cambió a la tecnología de transistores de próxima generación, finFET, a 22 nm en 2011. Los talleres cambiaron a finFET a 16/14 nm.

FinFET tiene varias ventajas sobre los transistores planos. “En este esquema, todo el transistor se extiende verticalmente para que el canal se eleve por encima del sustrato y la válvula se enrolle alrededor de tres lados de la aleta. El área de contacto incrementada de la válvula permite un mejor control de la corriente de fuga ”, escriben Matt Kogorno y Toshihiko Miyashita de Applied Materials. Kogorno es el director de gestión global de productos y Miyashita es el tecnólogo jefe.

FinFET también es dispositivos más complejos, es más difícil producirlos y escalarlos para cada proceso técnico posterior. Como resultado, el costo de la I + D subió al cielo. Así que ahora el ritmo de un cambio de proceso completo ha crecido de 18 meses a 2.5 años o más.

Los precios de los circuitos integrados también continúan aumentando. Según Gartner, el costo de desarrollar un dispositivo plano a 28 nm varía de $ 10 millones a $ 35 millones. A modo de comparación, el costo de diseñar un sistema de un solo chip (SoC) a 7 nm varía de $ 120 millones a $ 420 millones.

"El costo de desarrollo depende en gran medida de la complejidad del SoC", dijo Samuel Wen, analista de Gartner. - Dos tercios van al desarrollo del chip. El resto es el desarrollo de submarinos, el costo de las máscaras y la producción mejorada. Con el tiempo, el costo del diseño también cae ”.

Sin embargo, las tendencias de los precios han cambiado el panorama del mundo de los circuitos integrados. Con el tiempo, menos compañías pueden pagar el diseño de chips para los procesos de fabricación más avanzados. Muchos de ellos dependen de talleres para cuestiones de producción.

Una disminución en el número de clientes junto con un aumento en el costo de producción influyó en el panorama de los talleres que producen chips avanzados. Por ejemplo, quedan cinco fabricantes / talleres en el mercado de 16/14 nm: GlobalFoundries, Intel, Samsung, TSMC y UMC. SMIC también funciona con finFET en una tecnología de proceso de 14 nm.

Y a 7 nm sucedió otra transición. Los procesos tecnológicos y el costo de producción continuaron creciendo, y el retorno de la inversión ya estaba en cuestión. Como resultado, GlobalFoundries y UMC el año pasado dejaron de intentar desarrollar una tecnología de proceso de 7 nm. Ambas compañías continúan operando en el mercado de 16/14 nm.

Intentando desarrollar más, Samsung y TSMC se apresuran a toda velocidad a la vuelta de 7 nm y más. Después de varios retrasos, Intel planea lanzar la producción a 10 nm a mediados de 2019 y a 7 gm para 2021. SMIC, mientras tanto, no promete ningún plazo.

Pero no todos los clientes de talleres requieren procesos de fabricación avanzados. Hay un mercado próspero para chips de 28 nm. "Todo depende de las características del producto", dijo Ven de Gartner. - Algunos productos requieren el máximo rendimiento. Los desarrolladores aún pueden usar procesos técnicos obsoletos. Y los chips para aplicaciones que no requieren alto rendimiento pueden vivir en los procesos de fabricación N-1 y N-2 ".

Otros le hacen eco. “¿Cuántas empresas pueden permitirse el último silicio hoy desde un punto de vista económico? Su número está disminuyendo. En los mercados que requieren un rendimiento extremadamente alto, tal necesidad siempre lo será. Pero en la cadena de suministro, en términos de volúmenes, se forma una ruptura en el medio. Los clientes más exigentes requieren procesos tecnológicos a 7, 5 y posiblemente algún día a 3 nm. Pero todos los demás disminuyeron la velocidad un poco ", dijo Walter Eun, vicepresidente de gestión empresarial de UMC.

Pero en ciertos casos, se necesitan los chips más avanzados: estos son servidores y teléfonos inteligentes. También hay un mar de nuevas startups relacionadas con chips de IA. Muchas empresas diseñan chips para el aprendizaje automático y el aprendizaje profundo.

“Nadie argumenta que la necesidad de contar algo 10 veces más rápido que hoy siempre será comercialmente útil y competitiva, incluso en mercados no técnicos. Todos estos logros únicos de la tecnología de aprendizaje profundo son evidencia de esto. Literalmente, no hay fin a las solicitudes de potencia informática cada vez mayor ", dijo Aki Fujimura, director de D2S.

"Las demandas de potencia informática han experimentado varios cambios importantes, al principio fue la GPU y luego, el aprendizaje profundo", dijo Fujimura. - El aprendizaje profundo es una tecnología masiva para encontrar patrones adecuados, y el entrenamiento de redes neuronales es la tarea de una optimización consistente. Ahora que el mundo ha creado un mecanismo para procesar una gran cantidad de datos y convertirlo en información útil en forma de un programa capaz de conclusiones lógicas, la cantidad de cálculos necesarios aumenta con la cantidad de datos disponibles. Y dado que la cantidad de datos en todas las áreas está creciendo exponencialmente, se garantiza que los requisitos de potencia informática aumentarán significativamente, al menos en el campo del aprendizaje profundo ".

Aún no está claro si los chips AI requieren procesos técnicos de 5 nm o más, pero definitivamente hay requisitos para un aumento en la potencia informática. Pero la migración a estos procesos tecnológicos no se convierte en un proceso más fácil o más barato.

5 nm vs 3 nm

Mientras tanto, a principios de 2018, TSMC alcanzó otro hito, convirtiéndose en el primer fabricante del mundo en utilizar la tecnología de proceso de 7 nm. Samsung más tarde se unió a la carrera de 7 nm. El proceso de fabricación de chips a 7 nm se basa principalmente en finFET, y consiste en la fabricación de chips con un paso de puerta de 56 a 57 nm y un paso mínimo de colocación de conductores metálicos [paso de metal] a 40 nm, según la información de IC Knowledge y TEL.

En la primera versión de 7 nm, TSMC utilizó una

litografía de inmersión de 193 nm y patrones múltiples. Este año, TSMC promete lanzar una nueva versión de 7 nm utilizando la litografía ultravioleta extrema (EUV). EUV simplifica los pasos del proceso, pero es una tecnología costosa y tiene su propio conjunto de dificultades.

TSMC está preparando su nueva tecnología de proceso de 5 nm para su lanzamiento en la primera mitad de 2020. La nueva tecnología de TSMC a 5 nm será un 15% más rápida que 7 nm y consumirá un 30% menos de energía. La segunda versión de la tecnología de proceso de 5 nm, que saldrá el próximo año, será un 7% más rápida. Ambas versiones utilizarán EUV.

TSMC ya está obteniendo pedidos a 5 nm. "Se esperan grandes pedidos de Apple, HiSilicon y Qualcomm", dijo Handel Jones, Director de IBS. "El volumen de sustratos será de 40,000 - 60,000 por mes para el cuarto trimestre de 2020".

La velocidad de transición a 5 nm para TSMC es inferior a 7 nm. En primer lugar, 5nm es un proceso completamente nuevo, con herramientas y patentes EDA actualizadas. Además, es más caro. En promedio, el costo de desarrollar un dispositivo a 5 nm varía de $ 210 millones a $ 680 millones, según Gartner.

Algunos fabricantes de chips quieren alejarse de 7 nm sin gastar tanto dinero como 5 nm. Por lo tanto, TSMC introdujo recientemente una nueva tecnología de proceso de 6 nm, que es más barata, pero con algunos compromisos.

"Los números N6 y N5 no parecen ser diferentes, pero en realidad la brecha es grande", dijo S. S. Wei, director de TSMC en la última reunión. - En N5, en comparación con N7, la densidad lógica se incrementa en un 80%. N6 en comparación con N7 solo el 18%. Como puede ver, hay una gran diferencia entre la densidad lógica y la eficiencia de los transistores. Como resultado, el consumo de energía general del chip N5 es menor. Hay muchos beneficios al cambiar a N5. Pero N5 es un proceso técnico completo y lleva tiempo que los clientes desarrollen nuevos productos para él. La belleza de N6 es que si ya tienen un proyecto bajo N7, tendrán que gastar muy poco esfuerzo. Pueden actualizar a N6 y obtener ciertos beneficios. Y dependiendo de las características del producto y el mercado, los clientes decidirán qué hacer ".

Mientras tanto, Samsung lanzó 5 nm, que aparecerá en la primera mitad de 2020. En comparación con 7 nm, la nueva tecnología de proceso de 5 nm de Samsung en finFET proporciona hasta un 25% de compactación lógica y un 20% menos de consumo de energía, o un 10% más de velocidad de trabajo.

Samsung también introdujo una nueva tecnología de proceso de 6 nm, que ofrece a los clientes otra opción. "6nm tiene la ventaja de la escalabilidad con 7nm y la reutilización de la propiedad intelectual", dijo Ryan Lee, vicepresidente de marketing para talleres en Samsung. Y los planes de Samsung ya tienen el desarrollo de la tecnología de proceso de 4 nm finFET. Hasta ahora, prácticamente no hay información abierta sobre esta tecnología.

Después de 5 nm, varios procesos de fabricación completos cuestan 3 nm. Pero 3 nm no es para los débiles. Según el IBS, el costo de desarrollar un dispositivo para la tecnología de proceso de 3 nm oscila entre $ 500 millones y $ 1.5 mil millones. El costo del proceso de desarrollo varía de $ 4 mil millones a $ 5 mil millones, y la producción, de $ 15 a $ 20. "El costo de los transistores de 3 nm debe ser 20-25% más de 5 nm de la misma disponibilidad", dijo Jones de IBS. "Podemos esperar un aumento del 15% en la eficiencia y una reducción del 25% en el consumo de energía en comparación con el finFET de 5 nm".

Samsung es la única compañía que anuncia planes para desarrollar una tecnología de proceso de 3 nm. Para esto, el taller cambiará a la arquitectura de transistores circulares, nanocapas. TSMC aún no ha revelado planes, por lo que algunos creen que la compañía está detrás. "A 3 nm, es muy probable que Samsung entre en producción de volumen en 2021", dijo Jones. "TSMC acelera el desarrollo al tratar de mantenerse al día con Samsung".

A 3 nm, TSMC examina los FET de nanocapa, los FET de nanocables e incluso los finFET. Una de las formas de expandir la tecnología finFET es utilizar materiales de alta movilidad en los canales, a saber, Alemania. Los dispositivos finFET de hoy en día usan silicio o silicio-germanio (SiGe) en los canales. Al aumentar la mezcla de germanio, puede aumentar la movilidad del canal, es decir, la velocidad de paso de electrones a través del dispositivo. Y aquí el problema es la gestión de defectos.

Ampliar la tecnología finFET tiene sentido. finFET a 3 nm proporciona una ruta de transición de 5 nm. Sin embargo, hay problemas. Teóricamente, la tecnología finFET se encuentra con un callejón sin salida cuando el ancho de la aleta alcanza los 5 nm, que está cerca del estado actual. "Hoy usamos dos aletas para NMOS y tres para PMOS en una celda estándar", dijo Horiguchi de Imec. - Uno de los aspectos importantes de 3 nm es que necesitamos cambiar a una arquitectura de una sola aleta para diseños de celdas estándar. Una sola aleta debería funcionar lo suficientemente bien. Para expandir la tecnología finFET a N3, necesitamos una tecnología especial para mejorar el poder de una sola aleta y reducir los fenómenos espurios de fondo ”.

Además de la alta movilidad de finFET, la siguiente opción es GAA. En 2017, Samsung presentó el Multi Bridge Channel FET (MBCFET) para 3 nm. MBCFET - Nanocapa FET. El MBCFET de prueba de Samsung estará disponible en 2020.

Los chips de nanocapa tienen ventajas sobre finFET. En finFET, el obturador se dobla alrededor de la aleta desde tres lados. En las nanocapas, el obturador está ubicado en los cuatro lados de la aleta, lo que brinda más control sobre la corriente.

En comparación con 5 nm, los FET de nanocapa de Samsung proporcionan hasta un 45% de aumento en la eficiencia del área lógica y una reducción del 50% en el consumo de energía o un aumento del 35% en la velocidad. "La estructura finFET tiene sus propias limitaciones en la escalabilidad, ya que el voltaje de suministro no puede reducirse por debajo de 0,75 V. Nuestra innovación con nanocapas nos permite reducir el voltaje a valores inferiores a 0,7 V", dijo Samsung Lee.

Existen varios tipos de tecnologías GAA, que incluyen nanocapa FET y nanocable FET. GAA en sí es el siguiente paso después de finFET. En este sistema, finFET se ubica de lado y luego se divide en piezas horizontales. Las piezas forman canales. El material del obturador envuelve cada capa.En comparación con el FET de nanocables, dicho circuito tiene canales más amplios, es decir, una mayor productividad y corriente de excitación. "Las nanocapas tienen anchos más efectivos", dijo Imec Horiguchi. "A los nanocables les va mucho mejor con la electrostática". Pero su sección transversal es muy pequeña. Esto no dará ventajas en términos de ancho efectivo del canal ".Las arquitecturas GAA tienen varios problemas. Por lo general, dan un aumento extremadamente pequeño en comparación con finFET a 5 nm. Hacer chips con esta tecnología es bastante difícil."La próxima generación de GAA a 3 nm y menos agrega otro nivel de complejidad a la fabricación", dijo Richard Gotshaw, vicepresidente y director técnico de Lam Research . - A primera vista, parece una modificación de finFET. Sin embargo, los requisitos están aumentando y la complejidad de esta arquitectura GAA es significativamente mayor que finFET ".En el proceso de producción de chips de nanocapas, el primer paso es la colocación de capas delgadas alternas de SiGe y silicio sobre el sustrato. “Obtenemos una pila de silicio, silicio-germanio, silicio. Lo llamamos superredes ”, dijo Namsun Kim, director de ingeniería de Applied Materials, en una entrevista reciente. "Al tener contenido de germanio, debe proporcionarle una buena capa de aislamiento".Como mínimo, el paquete debe constar de tres capas de SiGe y tres de silicio. Luego, se aplican pequeñas estructuras de láminas al paquete. Después de eso, se forma un aislamiento con ranuras y luego divisores internos.Luego, las capas de SiGe se eliminan de la superrejilla, dejando capas de silicio con un espacio vacío entre ellas. Cada capa de silicio forma la base de la lámina o canal en el dispositivo. Luego, debe aplicar un material con una alta constante dieléctrica para crear un obturador. “Hay una distancia mínima entre nanocables. Muy pequeño. El problema es colocar metal de espesor de trabajo allí ”, dijo Kim.La industria ha trabajado durante años para crear la tecnología GAA, pero todavía hay algunos problemas. "Uno de los principales es la capacidad parasitaria", dijo Kim. - Si me pregunta cuáles son los principales problemas de la tecnología GAA, entonces hay dos de ellos. Separadores internos y aislamiento de sustrato ".Que sigue

¿Cuánto tiempo es suficiente la tecnología GAA o las nanocapas? “Las nanocapas sobrevivirán a las dos o tres de la próxima tecnología de proceso. Los talleres pueden hacer nanocapas en N3. La próxima generación es segura. Y después de eso, puede que tenga que cambiar la integración de nanocapas o arquitectura. Pero seguirá siendo una arquitectura de nanocapa ”, dijo Horiguchi de Imec.La industria está explorando formas de mejorar las tecnologías GAA y finFET en procesos de fabricación avanzados. Los dispositivos GAA actualmente ofrecen una ligera ventaja sobre finFET. Por ejemplo, el paso del obturador del chip de nanocapa Imec anterior era de 42 nm, y el paso mínimo de los conductores metálicos era de 21 nm. En comparación, los finFET a 5 nm pueden tener un paso de puerta de 48 nm y un paso mínimo de conductores metálicos de 28 nm.En el laboratorio, Imec demostró la escalabilidad de un dispositivo semiconductor tipo p con una doble pila de GAA y germanio en el canal. Usando un circuito sin extensión, Imec ha desarrollado un nanocable con una longitud de puerta de aproximadamente 25 nm. Se puede adaptar para nanocapas. Al igual que con la versión anterior, el tamaño del cable es de 9 nm.El germanio puede desempeñar un papel en el uso continuo de finFET fuera de la tecnología de proceso de 5 nm. Imec mostró Ge nFinFET con niveles récord de Gmsat / SSsat y PBTI. Se lograron mejorando el reemplazo de material dieléctrico alto.También veremos si la tecnología finFET se puede ampliar a 3 nm. Tampoco está claro si los chips de nanocapa aparecerán a tiempo. Hay muchas incógnitas e incertidumbres en este panorama cambiante, y no hay un calendario para aclarar la situación.