Finalmente, se lanzó un

libro de texto sobre SystemVerilog en Rusia

a un nivel superior al de los principiantes . El libro de texto describe las tecnologías y técnicas que se solicitan para entrevistas en NVidia, Intel, AMD, Apple y otras compañías electrónicas: el uso de afirmaciones concurrentes y cobertura funcional, que ahora requieren no solo ingenieros de verificación, sino también diseñadores de chips; el algoritmo del simulador con ciclos delta; explicación sensata del análisis de tiempo estático; diagramas de comunicación de unidades de hardware a través de colas de hardware; la implementación de estas comunicaciones utilizando máquinas de estados finitos con rutas de datos, etc.

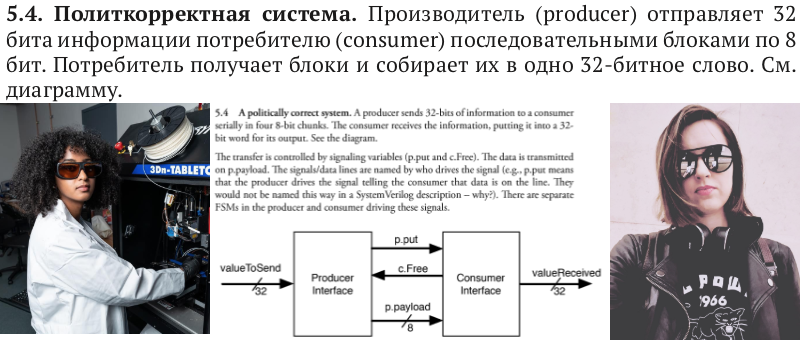

En el capítulo sobre este último, el lector ruso puede estar desconcertado por la mención de un "sistema políticamente correcto". ¿Qué significaría eso? Esto es probablemente una alusión al

incidente que ocurrió en el condado de Los Ángeles en 2003. Los funcionarios de Los Ángeles pidieron a los fabricantes, proveedores y contratistas que dejen de usar los términos "maestro / esclavo" para equipos informáticos, ya que uno de los empleados del condado recordó el pasado esclavo.

Ahora los autores de literatura técnica están evitando los términos maestro / esclavo. Los ingenieros afroamericanos también trabajan en la América moderna (por ejemplo, Sofía Mvokani de Camerún, en la foto de la izquierda), y el uso de términos antiguos parece arcaico, como los términos "pan / esclavo" en la literatura técnica ucraniana se verían en lugar del "plomo / plomo" aceptado ( Ruso "líder / esclavo").

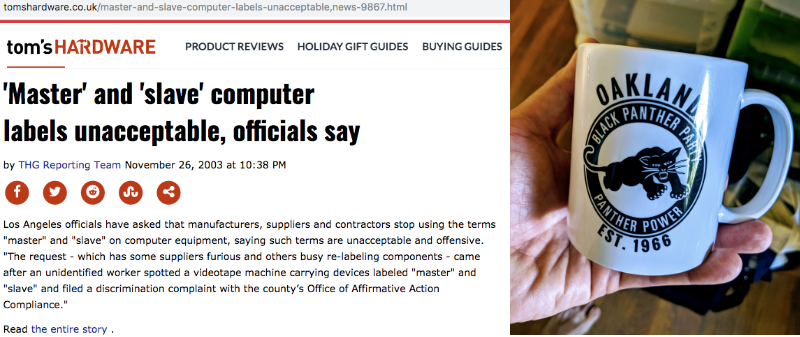

Esta no es la primera vez que el tema de la lucha de los afroamericanos por los derechos civiles aparece en la educación electrónica rusa. Por ejemplo, Tatyana Volkova, una reconocida especialista en educación en electrónica, usa una camiseta con el emblema de "Black Panthers", el movimiento de California, que en un momento consideró insuficiente la protesta pacífica y participó en una protesta armada.

La imagen completa del emblema debajo de la piel de Tatyana Alexandrovna está debajo del corte, pero principalmente hablaré sobre los ciclos delta y las máquinas de estado:

A continuación se muestra una captura de pantalla del artículo sobre maestro / esclavo y el emblema prometido de Black Panther, después de lo cual pasamos al libro como tal.

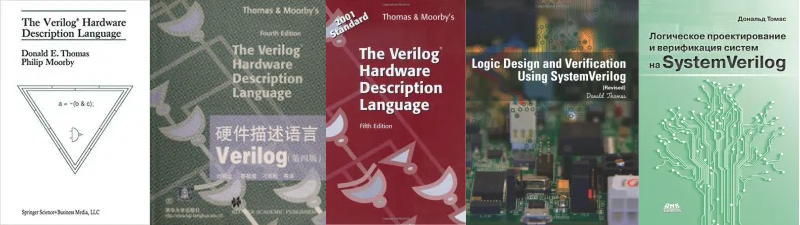

En primer lugar, Donald Thomas, autor del libro

"Diseño lógico y verificación de sistemas en SystemVerilog" (2019 en ruso de DMK-Press, 2016 en inglés) es el mismo Donald Thomas, coautor con Philip Murbi, escribió un libro en 1991 El lenguaje de descripción de hardware Verilog por Donald Thomas y Philip Moorby. Luego, en 1991, muchas compañías electrónicas todavía diseñaron microchips a la antigua usanza, dibujándolos con el mouse en la pantalla; las tecnologías de síntesis lógica acaban de abandonar el laboratorio para la producción; los lenguajes de descripción de hardware se consideraron destinados a escribir modelos y pruebas, y no códigos fuente para crear circuitos finales; Además de VHDL y Verilog cerrados en ese momento, había muchos lenguajes pequeños y propietarios como Abel, CUPL, PALASM; e Intel y MIPS tenían lenguajes de descripción de hardware internos.

En ese entorno, salió el libro de Thomas y Murbi, que se convirtió en el mismo para los diseñadores de circuitos digitales de la década de 1990 que el libro de Kernigan-Richie para los programadores de C, y los libros de Bjarni Straustrup para los programadores de C ++. El libro ha sobrevivido a cinco ediciones, de 1991 a 2002, pero para la era de los iPhones fue claramente insuficiente. Y en 2016, Donald Thomas decidió ponerse al día y lanzó un nuevo libro en el que describía las innovaciones clave en el lenguaje y la metodología a lo largo de 25 años. En los 25 años durante los cuales Verilog se ha convertido en una base común para toda la industria, se han escrito esquemas para todo, desde los notorios iPhones y las computadoras de control en Tesla hasta los helicópteros militares rusos.

A continuación, resaltaré mis comentarios con texto azul para separarlos de las imágenes del libro.

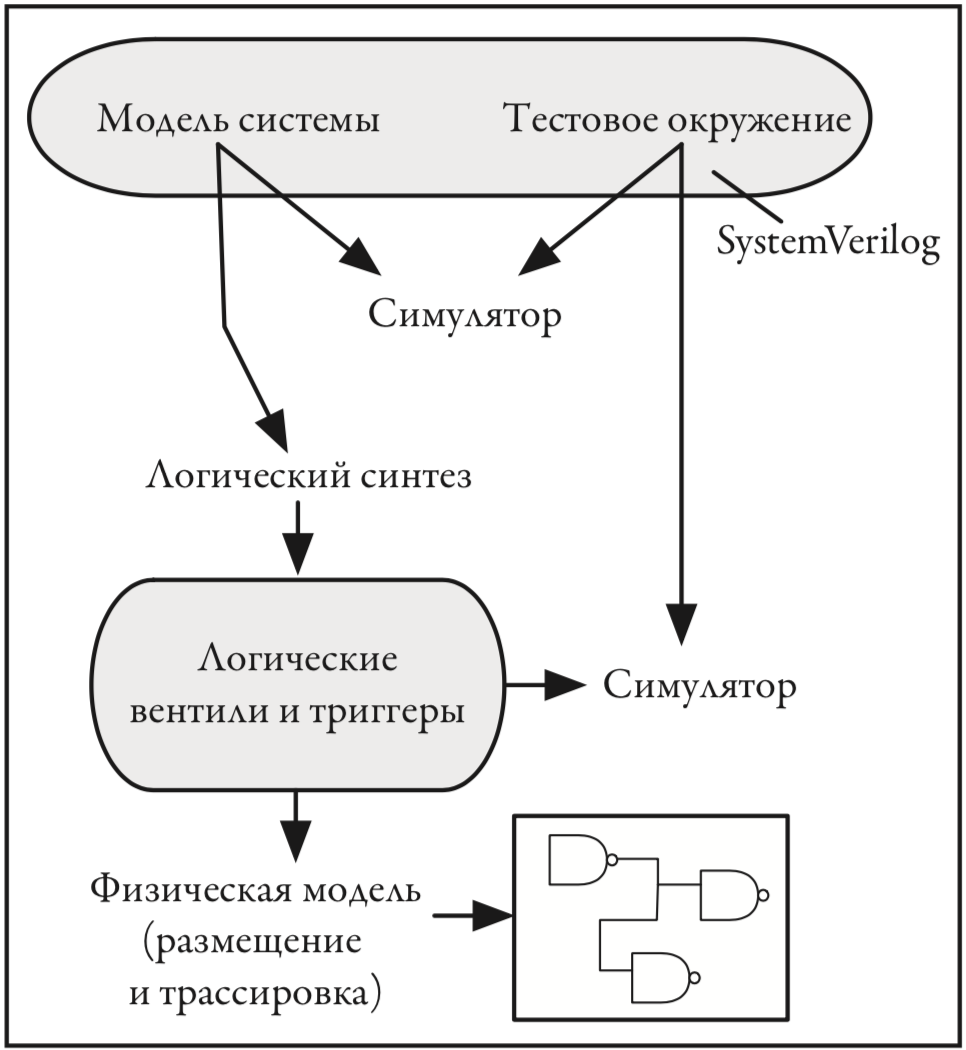

Incluso antes del texto principal del libro, está el capítulo anterior "Contexto: diseño a nivel de transferencias de registros", de modo que un programador, un alumno o, por ejemplo, un amante del ejercicio con tablas de prototipos, que saca este libro del estante, comprende de inmediato lo que se dice y cómo puede usar el libro. Dice:Los sistemas digitales se están produciendo con miles de millones de transistores en un chip. Un aficionado, por supuesto, puede dibujar varias puertas lógicas y conectarlas con cables como una especificación (para implementación en una placa de pruebas), pero para proyectos comerciales esta es una historia antigua ... Los sistemas modernos se especifican en lenguajes de descripción de hardware como SystemVerilog.

Al mismo tiempo, aquí hay una imagen tan simplificada para ilustrar cómo el texto en el veril se convierte en pistas y transistores del microcircuito en la fábrica:

La primera palabra en el libro después del prefacio es "simulador". Para comprender los lenguajes de descripción de hardware, debe tener claro que el subconjunto sintetizado del verilogue no es un lenguaje de programación, sino un lenguaje para describir circuitos eléctricos. Como digamos, HTML no es un lenguaje de programación, sino un lenguaje para describir páginas web. Mientras que un lenguaje de programación está destinado a ser compilado en una cadena de instrucciones de procesador, un lenguaje de descripción de hardware está destinado a convertirse (en particular) en hierro de procesador como tal. En este caso, antes de convertirlo en hierro, se debe verificar el código en el lenguaje de descripción del hardware, para lo cual sirve un intérprete especializado, llamado simulador.

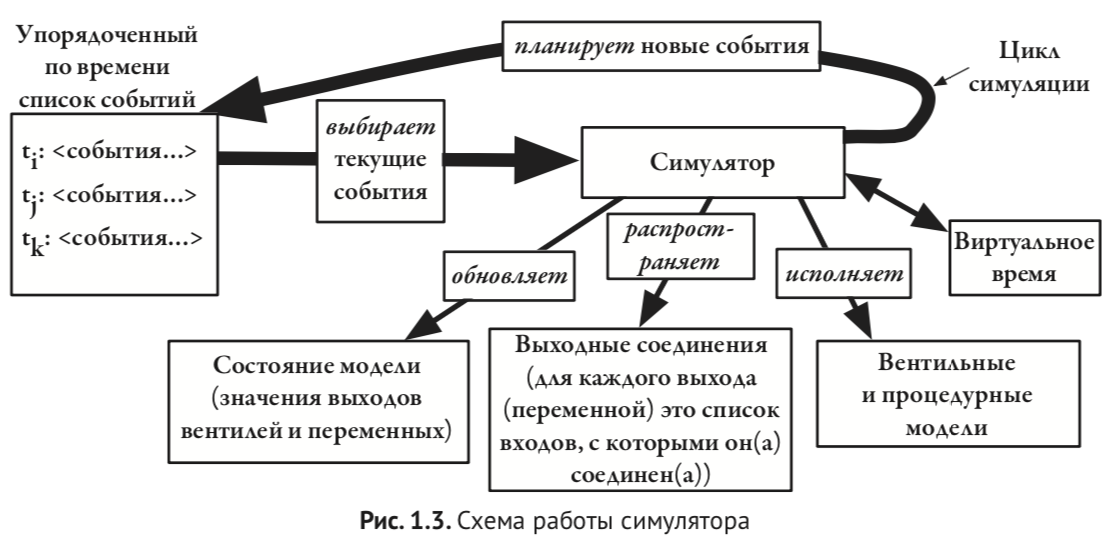

Al principio del libro, Donald Thomas muestra una imagen simplificada del simulador, y al final del libro lo aclara y complementa:

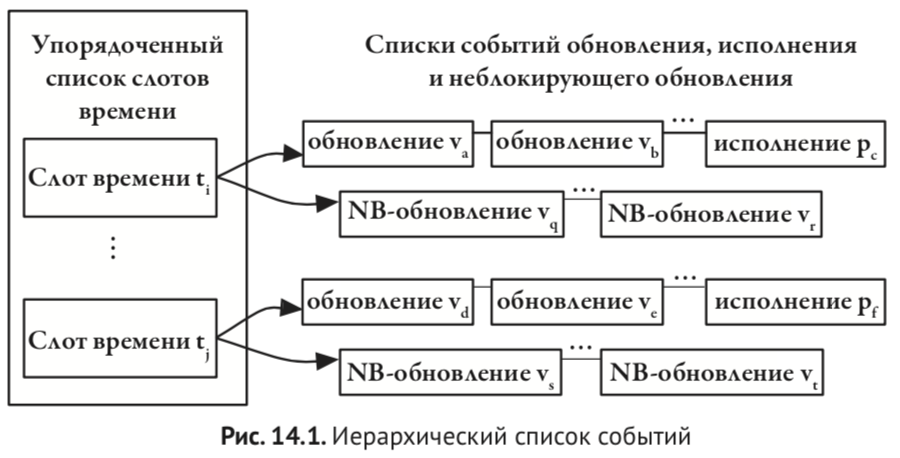

El simulador tiene colas de eventos y tiempo simulado:

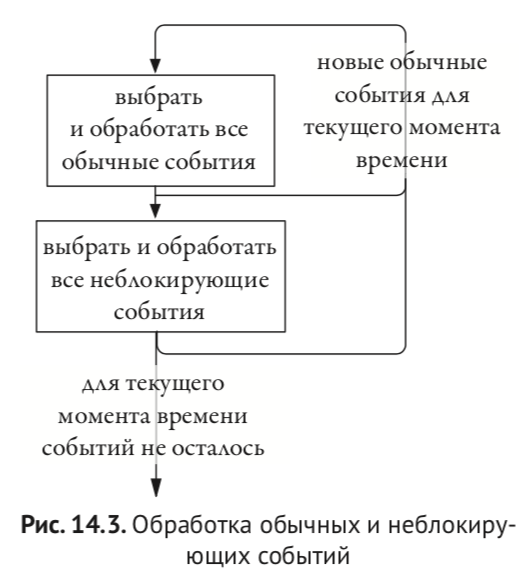

Un evento puede dar lugar a un nuevo evento, tanto en el momento actual de la simulación (en el ciclo delta actual) como en el tiempo futuro. En el ciclo delta actual, todos los eventos generados por las llamadas asignaciones de bloqueo se procesan primero, y luego se procesan los eventos generados por las asignaciones sin bloqueo. Esto es necesario para la correcta simulación de la semántica paralela de la propagación de señales eléctricas en hierro:

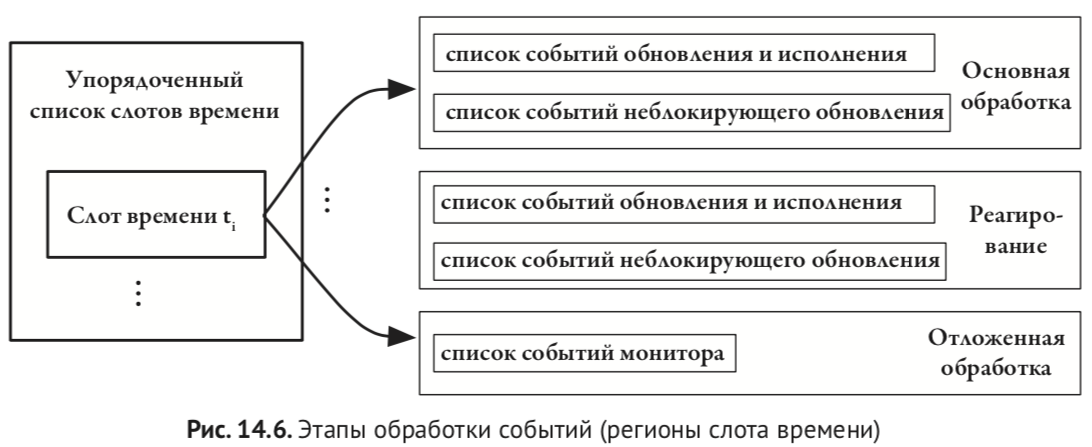

Además del subconjunto sintetizado del verilog, también hay un subconjunto no sintetizado. Su objetivo es describir el entorno de prueba y las pruebas, y ahora puede considerarse como un tipo de lenguaje de programación. Para eventos y monitores de entorno de prueba, se introducen pasos adicionales del simulador:

El conocimiento exacto del algoritmo del simulador es muy útil para evitar una variedad de errores asociados con la llamada raza (condición de carrera). Cuando intervengo ingenieros, siempre les pido que den un ejemplo de condición de carrera en Verilog. Además, si para los jóvenes ingenieros de diseño y verificación de diseño de RTL dicho conocimiento es muy deseable, pero no en todos los aspectos 100% necesario, es decir, profesiones en las que se paga dinero directamente por este conocimiento. Estoy hablando de programadores que trabajan en los equipos Synopsys VCS, Cadence IES y Mentor ModelSim.

Synopsys y Cadence son dos compañías ubicadas en California dentro de una unidad de 15 minutos. Emplean a unos pocos miles de personas, pero controlan el desarrollo de microcircuitos en todo el mundo: en Intel, Apple, Samsung, Huawei, incluso en institutos secretos de Rusia que fabrican chips para equipos militares.

Si los camaradas Putin, Rogozin y Vekselberg realmente quieren introducir la sustitución de importaciones en Rusia, entonces podrían financiar el desarrollo del análogo ruso Synopsys VCS (para simular un verilogue), Synopsys Design Compiler (para la síntesis lógica de un verilogue) y Synopsys IC Compiler (para publicar físicamente los resultados de la síntesis lógica) ) Probablemente hay varios miles de programadores matemáticamente expertos en Rusia.

Aunque las licencias para estos productos de software son bastante fáciles de romper, es difícil usarlas sin soporte. Si Huawei se desconecta de Synopsys y Cadence, tendrán, en cierto sentido, peor que cuando se desconecta de Android e incluso de los núcleos ARM.

Sí, así que aquí está el algoritmo refinado al final del libro de Donald Thomas. Si no lo aprende de memoria, es inútil intervenir en los grupos de simulación en Synopsys, Cadence, Siemens / Mentor, Xilinx, y le pedirán que lo dibuje en la pizarra y le sugiera cómo optimizar un caso particular:

Después de aclarar la simulación al comienzo del libro, Donald Thomas describe el lenguaje SystemVerilog como tal. Este lenguaje surgió como el superconjunto Verilog en 2002, como resultado de la fusión de los idiomas Verilog-2001, Vera y Superlog, y con la adición de ideas del Lenguaje de especificación de propiedades (PSL), que se transformaron en Afirmaciones de SystemVerilog (SVA).

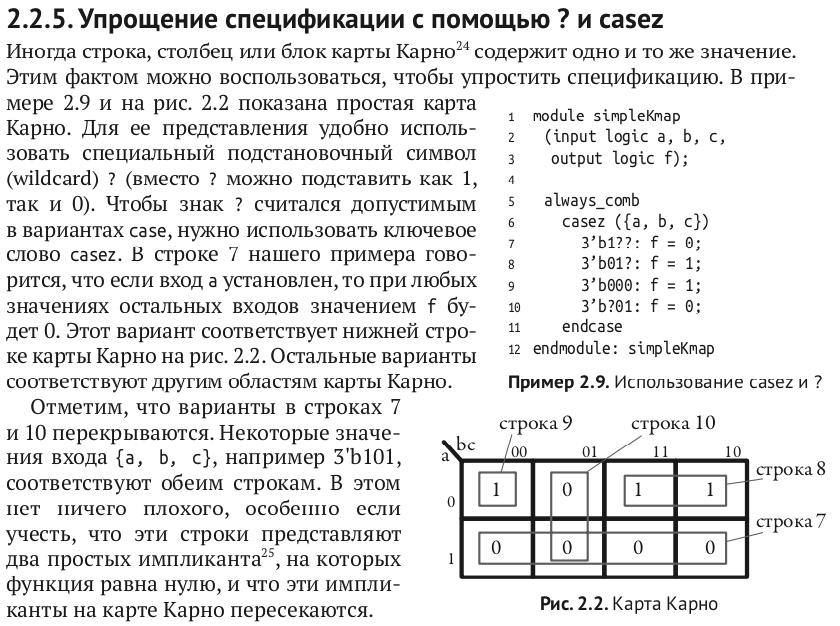

Donald Thomas cree que ya has aprendido los conceptos básicos del diseño digital en algún lugar y, por lo tanto, teje en el tejido narrativo varias piezas conocidas como las tarjetas de Carnot. Los mapas de Carnot se usaron para el diseño manual de circuitos en la década de 1960, después de lo cual este método fue reemplazado por la optimización automática de la lógica utilizando el algoritmo Quine - McCluskey y el optimizador automático de lógica Espresso. Por lo tanto, las tarjetas de Carnot están presentes en todos los libros de texto universitarios sobre el diseño de la lógica digital, pero parecen estar suspendidas en el aire. Y aquí Donald Thomas adjunta mapas de Carnot a la vida de un diseñador en un verilo del siglo XXI:

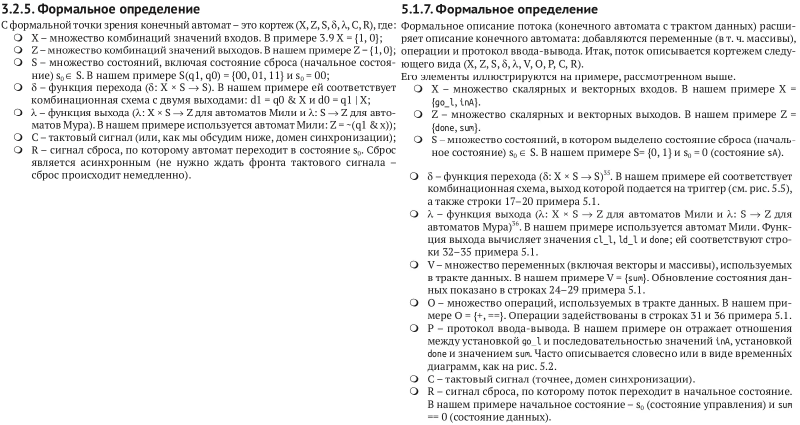

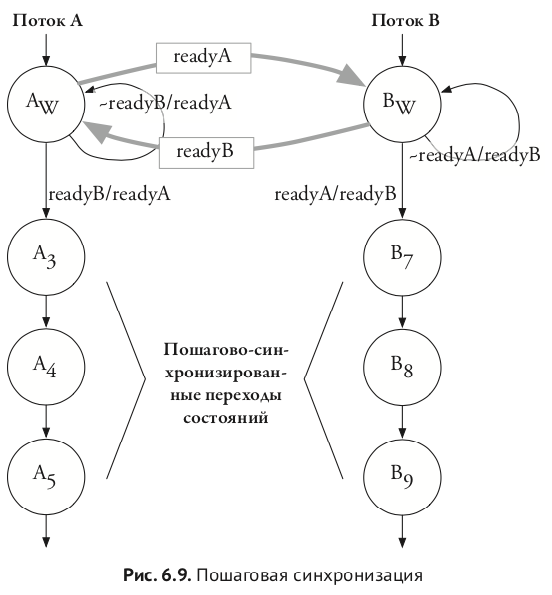

Además, Donald Thomas escribe sobre máquinas de estados finitos, y da 1) una definición matemática estricta; 2) diagramas; 3) código; 4) después de lo cual comienza a expandirse a máquinas de estados finitos con una ruta de datos: flujos de hardware; 5) después de lo cual estos flujos comienzan a interactuar con él, tanto de acuerdo con protocolos simples "políticamente correctos" (ver arriba) como usando colas de hardware.

Aquí está el código para un autómata simple con una ruta de datos que Thomas cita como primer ejemplo:

A continuación, Thomas tiene un capítulo sobre análisis de tiempo estático. Nada especial, pero más limpio que en muchos sitios populares de la India, "Cómo superar la entrevista VLSI". Y también de manera más completa que en algunos libros sobre veril, que mastican tediosamente la sintaxis del lenguaje, pero en realidad no muestran cómo usarlo.

¿Por qué necesitamos análisis de tiempo estático? En el hardware real, en contraste con la ilusión de que el procesador muestra al programador, cada cálculo pasa por un intervalo de tiempo cuando toda la basura está en los cables, no solo ceros y unos calculados claramente, sino también cualquier falla aleatoria, es decir, falla, y en general valores no digitales en la zona prohibida. Por ejemplo, si tiene todos los voltajes por encima de 0.7 voltios considerados como una unidad digital, y todos los voltajes por debajo de 0.3 voltios como cero digital, entonces pueden aparecer 0.4 voltios en el cable.

Al final, todas las señales en el circuito siguen su propio camino y la situación se calma, pero esto "al final" debería ser menor que el ciclo de la señal del reloj (reloj). Este ciclo es inversamente proporcional a la frecuencia a la que opera el circuito (gigahercios, megahercios).

Si el resultado establecido de los cálculos o las operaciones lógicas no cae en el disparador D (elemento de memoria mínimo) en el momento de la apertura (intervalo alrededor del cambio de dicha señal), el estado del circuito se convertirá en basura: el satélite o el reactor explotarán, el iPhone dejará de responder llamadas. Todo el diseñador de equipos necesita saber no menos ironía que la lógica.

¿Por qué el análisis es estático? En la década de 1980, fue dinámico: los retrasos se aclararon mediante la simulación. Esto resultó no ser confiable para circuitos con cientos de miles, millones y miles de millones de transistores, y ahora todos los retrasos se calculan estáticamente, en función del análisis de las rutas de señal después de la síntesis.

La señal del reloj también puede llegar a diferentes partes del chip con cierto retraso, lo que agrega otra incertidumbre a esta cocina que debe eliminarse (afortunadamente, no manualmente, sino con la ayuda de programas de árbol de síntesis de reloj y otros métodos):

En el capítulo sobre flujos, Thomas analiza varias opciones básicas de cómo las máquinas de estado de operación paralelas con rutas de datos pueden intercambiar información, incluido el uso de buffers y colas. Al igual que en el diseño / circuito en sí, a nivel de transferencias de registros, también en el modelo de comportamiento o entorno de prueba del circuito. Al leer a Thomas, es bueno escribir y depurar ejemplos usted mismo para todos los casos de los protocolos descritos por él. El hecho es que les gusta escribir código sobre estos temas (una pequeña máquina de control de estado finito, flujo de datos entre dos módulos, rutas de datos canalizadas o simplemente código para una cola de hardware) en una pizarra o en una computadora durante una entrevista de segundo nivel en compañías electrónicas. Si puede escribir un ejemplo para cualquiera de las combinaciones descritas por Thomas en 20 minutos con un código de 30-50 líneas, causará una buena impresión. Difícil de aprender, fácil en la batalla.

El entorno de prueba para enrutadores (Fig. 8.3) con colas para varios puertos es un ejemplo popular que se utiliza para explicar las metodologías de verificación. Probablemente porque algunas de estas metodologías fueron inventadas por Cisco y otras compañías que diseñaron chips para hardware de red.

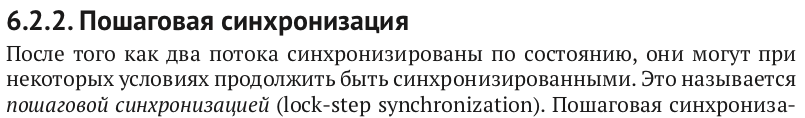

En el capítulo 6.2.2. Thomas describe una de las opciones para la interacción de subprocesos: sincronización paso a paso (Lock-step). Una de las aplicaciones de paso de bloqueo son los sistemas de alta confiabilidad, por ejemplo en electrónica automotriz. Un caso especial: dos procesadores pueden ejecutar el mismo programa con un retraso de varios ciclos, y durante esta ejecución un circuito especial puede verificar que tengan los mismos resultados.

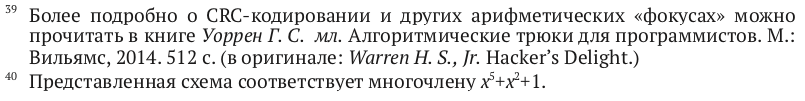

Thomas estaba claramente preocupado por la confiabilidad, ya que además del paso de bloqueo, cita el uso de CRC, un código cíclicamente redundante para detectar errores en la transferencia de datos. Al mismo tiempo, Thomas le dice cómo calcular CRC usando LFSR, un registro de desplazamiento de retroalimentación lineal. Tanto eso como otro necesitan poder ser un joven ingeniero. Esta es la ventaja del libro de Thomas, aunque no siempre profundiza, toca muchos temas y muestra dónde cavar:

Al describir CRC, Thomas se refiere a un libro muy interesante e incomprendido en Rusia por Hacker's Delight :

Donald Thomas en su nuevo libro toca tres tecnologías que no estaban en el libro antiguo:

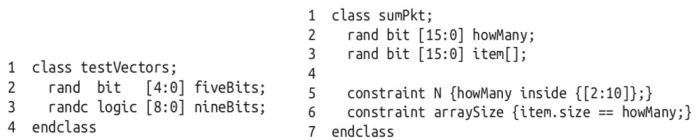

- Generación automática de transacciones pseudoaleatorias con reglas restringidas (transacciones aleatorias restringidas / solucionadores de restricciones).

- Contabilización de la cobertura de escenarios interesantes que surgen durante el bombardeo de un diseño mediante transacciones aleatorias limitadas, cobertura funcional.

- El lenguaje de las declaraciones de lógica temporal (aserciones concurrentes) y su uso tanto en simulación como en pruebas automáticas de propiedades de diseño utilizando programas formales de verificación.

Estas tres tecnologías ingresaron a la industria en el buen sentido solo en el siglo XXI, pero entraron con bastante firmeza. Al principio, todos los ingenieros de verificación los utilizaron para crear entornos de prueba, pero ahora el conocimiento de la cobertura funcional y el Lenguaje de Afirmación Temporal (Afirmaciones de SystemVerilog - SVA) también requieren diseñadores. Thomas tiene un cierto mínimo que lo ayudará a no ser interrumpido en una entrevista telefónica, pero para un trabajo real necesita saber mucho más. Además, no solo el lenguaje de las declaraciones temporales como tales, sino también la práctica de depurar con su ayuda las máquinas de estados finitos paralelos generados por el simulador para cada declaración, así como el uso de programas formales de verificación. La verificación formal basada en afirmaciones en los últimos años se ha implementado en gran medida en Apple, AMD y otras compañías similares.

Tengo un amigo que descargó

este libro sobre el lenguaje de las declaraciones temporales y lo estudió todas las vacaciones de Año Nuevo en lugar de un viaje a Hawai con niñas. Desde aquí puede comprender cómo las verificaciones de SystemVerilog (SVA) son importantes para la carrera y la industria. Es cierto que, en aras de la exhaustividad, debo mencionar que es hijo de emigrantes de Taiwán, y que tienen una actitud más severa que los rusos.

Así es como Thomas se ocupa de generar transacciones pseudoaleatorias (una transacción con campos rand y su restricción utilizando la construcción de restricción):

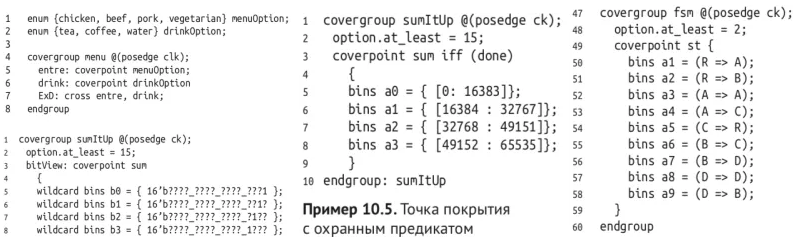

Y así es como Thomas se relaciona con la cobertura funcional: covergroup / coverpoint / bins, teniendo en cuenta las combinaciones de varias cubiertas variables (cruzadas), utilizando contenedores comodín, rangos de valores, así como la cobertura de transición en máquinas de estado:

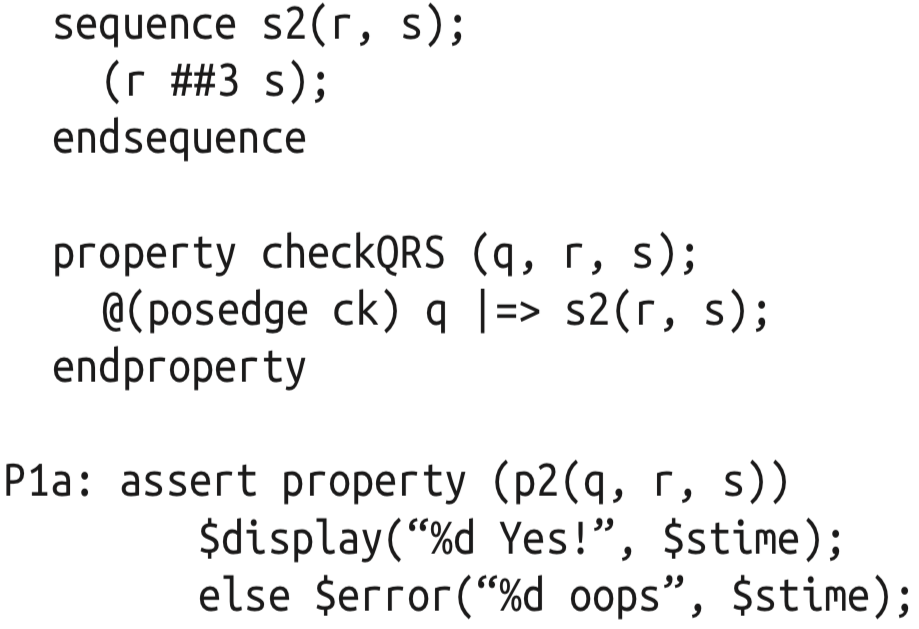

Aquí hay un ejemplo de la declaración temporal más simple “si q es verdadero en el borde positivo de la señal de reloj, entonces la secuencia s2 debe ejecutarse a través del ciclo, en el cual r es primero verdadero, y s está en tres ciclos más:

¿Qué leer antes y después del libro "Diseño lógico y verificación de sistemas en SystemVerilog" de Donald Thomas?

Si no entiendes nada en mi publicación, puedes intentar leer el libro

"Digital Circuitry and Computer Architecture" de David Harris y Sarah Harris . El libro Harris & Harris puede ser entendido por todos los que pueden leer y contar, siempre que el lector tenga motivación.

El libro comienza en el nivel secundario (voltajes, números binarios) y termina con el diseño de su propio procesador en el veril.Spoiler: David Harris y Sarah Harris no son marido y mujer, ni siquiera hermano y hermana. Son solo homónimos que accidentalmente comenzaron a trabajar como maestros en la misma universidad, durante la cual escribieron un libro.Aquí a la izquierda en la foto está la niña Irina del Novosibirsk Academgorodok sosteniendo la edición en inglés de Harris & Harris, y a la derecha está su edición en ruso. Después del libro de Donald Thomas, recomiendo descargar artículos de Cliff Cummings. Es el entrenador de veril más famoso tanto para síntesis como para verificación. Mientras leía el libro de Donald Thomas, tuve la idea de "muchas veces sería bueno insertar tal o cual pieza de Cliff Cummings" para completar. Cliff toma entre $ 1,000 y $ 3,000 por cada estudiante en los seminarios, dependiendo de la duración del seminario (de día a semana), y las compañías electrónicas pagan para mejorar la calidad de sus ingenieros que no están bien capacitados en las universidades. Incluso en Stanford, por desgracia, no todos aprenden esto: tuve un pasante de Stanford, lo sé por él. Si descarga todos los artículos gratuitos de Cliff Cummings después de leer a Donald Thomas, entonces ahorrará todo este dinero.Estos dos artículos son obligatorios: les gusta preguntar en todas partes de la entrevista:Técnicas de diseño y verificación de Clock Domain Crossing (CDC) utilizando técnicas desimulación y síntesis de Verilog del sistema para el diseño FIFO asíncrono con comparaciones de puntero asíncronoEstos tres artículos son recomendables para leer, especialmente sobre la eliminación de reinicios asíncronos, recodificación de estados FSM y caso de estilo FSM (1'b1) // synopsys parallel_case ... state [STATE_N]: ... ", que se ha utilizado durante mucho tiempo en chips de alta velocidad, en Sun Microsystems, y continúa utilizándose ahora:Técnicas de diseño de reinicio asíncrono y síncrono: técnicas decodificación y scripting de parte Deux para diseños FSM con síntesis -Opciones optimizadas y sin fallasTécnicas de diseño de máquinas de estados finitos sintetizables utilizando el nuevo sistema Mejoras Verilog 3.0Y aquí hay un artículo curioso donde verás la falta de pensamiento sobre el verilogue, que se ha mantenido desde la década de 1980. Aunque ahora, en la era del análisis de tiempo estático, esto no es tan relevante, pero los retrasos de inercia y transporte a veces se mencionan en la literatura y el código, y debe saber cómo modelarlos:Métodos correctos para agregar retrasos a los modelos de comportamiento VerilogEste soy yo con Cliff Cummings:

Después del libro de Donald Thomas, recomiendo descargar artículos de Cliff Cummings. Es el entrenador de veril más famoso tanto para síntesis como para verificación. Mientras leía el libro de Donald Thomas, tuve la idea de "muchas veces sería bueno insertar tal o cual pieza de Cliff Cummings" para completar. Cliff toma entre $ 1,000 y $ 3,000 por cada estudiante en los seminarios, dependiendo de la duración del seminario (de día a semana), y las compañías electrónicas pagan para mejorar la calidad de sus ingenieros que no están bien capacitados en las universidades. Incluso en Stanford, por desgracia, no todos aprenden esto: tuve un pasante de Stanford, lo sé por él. Si descarga todos los artículos gratuitos de Cliff Cummings después de leer a Donald Thomas, entonces ahorrará todo este dinero.Estos dos artículos son obligatorios: les gusta preguntar en todas partes de la entrevista:Técnicas de diseño y verificación de Clock Domain Crossing (CDC) utilizando técnicas desimulación y síntesis de Verilog del sistema para el diseño FIFO asíncrono con comparaciones de puntero asíncronoEstos tres artículos son recomendables para leer, especialmente sobre la eliminación de reinicios asíncronos, recodificación de estados FSM y caso de estilo FSM (1'b1) // synopsys parallel_case ... state [STATE_N]: ... ", que se ha utilizado durante mucho tiempo en chips de alta velocidad, en Sun Microsystems, y continúa utilizándose ahora:Técnicas de diseño de reinicio asíncrono y síncrono: técnicas decodificación y scripting de parte Deux para diseños FSM con síntesis -Opciones optimizadas y sin fallasTécnicas de diseño de máquinas de estados finitos sintetizables utilizando el nuevo sistema Mejoras Verilog 3.0Y aquí hay un artículo curioso donde verás la falta de pensamiento sobre el verilogue, que se ha mantenido desde la década de 1980. Aunque ahora, en la era del análisis de tiempo estático, esto no es tan relevante, pero los retrasos de inercia y transporte a veces se mencionan en la literatura y el código, y debe saber cómo modelarlos:Métodos correctos para agregar retrasos a los modelos de comportamiento VerilogEste soy yo con Cliff Cummings: