Hace algún tiempo, el autor de estas líneas se comprometió a desarrollar una grabadora compacta de una señal analógica unipolar dentro de los 3 voltios con la velocidad de lectura más alta posible y los costos y tamaños más bajos posibles. En la lista de los costos más bajos posibles, también ingresé en mi dolor de cabeza y elegí el conocido STM32F303. Esto, recuerdo, Cortex-M4 de 72 megahercios de una conocida empresa, con convertidores analógicos a digitales incorporados de 12 bits, bastante ágiles (ADC o ADC, como desee) y con una interfaz CAN a bordo.

Tales pequeños registradores requerían varias docenas. Y la presencia de una caja de microcontrolador con 48 patas inspiró la esperanza de que sería posible llamar a este lector compacto. La interfaz CAN, con la que ya tenía una buena relación, me dio la oportunidad de combinar todo este jazz de una manera bastante conveniente.

La velocidad con la que, al final, todo funcionó, resultó ser bastante adecuada para declarar la operatividad del enfoque elegido. Fue posible lograr un paso de muestreo de medio microsegundo. El dolor de cabeza y el ensamblador no podían evitarse, pero ¿quién ahora recuerda esto?

Sin embargo, quedó algo de sedimento. El pensamiento seguía siendo que, en términos de velocidad, no todo estaba exprimido.

Y ahora, la serie STM32G4 ha aparecido recientemente con una frecuencia de reloj de hasta 170 megahercios con una opción en un caso pequeño y con casi los mismos ADC rápidos a bordo en la cantidad de cinco piezas. Era necesario hacer algo.

Nadie estaba parado sobre el alma ahora y no había necesidad de preocuparse por los plazos y los planes.

De hecho, si no lo piensa, puede disfrutar incluso del trabajo. Pero, francamente, tuve que pensar en el tiempo. Pensar durante mucho tiempo en poco tiempo (y qué, poéticamente).

El pensamiento sugirió que deberíamos comenzar un poco desde el otro extremo. Es decir, debemos proceder del tiempo más corto posible para el muestreo de ADC, que, según la descripción, toma 2.5 ciclos de reloj y asciende a 62.5 nanosegundos a 40 MHz (160 MHz / 4). Luego, el paso de muestreo de 100 nanosegundos se sugiere. El número es redondo y, lo más importante, bastante pequeño y hermoso, ¿por qué no probarlo?

Además, la placa NUCLEO-G474RE adecuada para experimentos apareció a la venta y se compró, a lo que era razonable agregar una placa de pruebas adicional con dos conectores de doble fila para soldar todo tipo de cables y piezas a la placa de pruebas y no estropear la principal. Así es como se ve listo.

Allí, debajo, hay varios cables y una resistencia con un condensador, confía en mi palabra.

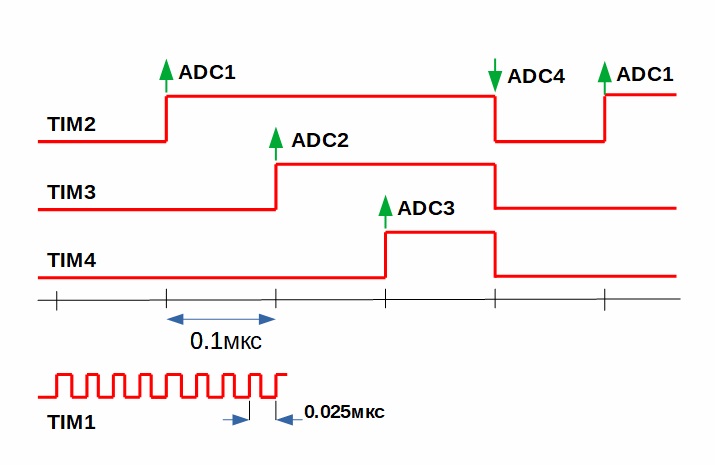

Ahora debe aplicar una señal eléctrica adecuada a los cuatro ADC a la vez, luego ejecutarlos uno tras otro con un paso constante (al principio, al depurar, no muy corto). ¿Por qué cuatro? Según la descripción, cada ADC gasta 15 ciclos de reloj por conversión, o 0.025 * 15 = 375 nanosegundos (casi 400). Por lo tanto, en el paso 100, se requiere un transportador de cuatro ADC.

Se usó un circuito RC como señal de entrada, a la que simplemente se suministró voltaje desde el pie del controlador. Asigné este tramo para controlar el temporizador TIM5 en modo de pulso único.

El diagrama de cableado mínimo se parecía a la imagen de abajo.

ADC1-ADC4 estuvieron involucrados. La profundidad de bits podría reducirse para un cierto aumento en la velocidad, pero pesaron 12 bits, porque no quería perder la precisión de las mediciones. Para iniciar cada ADC en el orden necesario y con el paso requerido, se utilizan tres temporizadores (TIM2, TIM3, TIM4) y otro temporizador (TIM1) para sincronizar los tres anteriores. La Figura 2 a continuación muestra las señales alrededor de las cuales se construye todo.

Las flechas verdes indican el borde de los pulsos a lo largo del cual se activan los respectivos convertidores ADC1-ADC4.

Para obtener los 100 nanosegundos planeados, tuvimos que reducir la frecuencia del reloj a 160 megahercios, para que todo se dividiera por completo como debería. Al principio, el paso se estableció mucho más lento, 4 microsegundos, para verificar con calma el funcionamiento de los temporizadores mediante interrupciones, puertos de salida y un osciloscopio. Luego, por interrupción, se depuró y obtuvo acceso directo a la memoria. En última instancia, solo se procesa una interrupción: esta es la interrupción del final del trabajo desde el cuarto (último) canal de acceso directo a la memoria. La siguiente figura muestra las conexiones de las unidades de hardware involucradas en el proceso, así como cuatro memorias intermedias de salida.

De las cuatro memorias intermedias de memoria (en la figura de la derecha), las muestras se recopilan mediante programación en una memoria intermedia de resultados.

En este controlador, a diferencia del STM32F303, hay una unidad de conmutación de solicitud (DMAMUX), que le permite redirigir una gran cantidad de solicitudes de dispositivos periféricos a solo 16 canales DMA1 y 16 canales DMA2. En el manual de referencia, las solicitudes de salida DMAMUX se cuentan desde 0, y las entradas de los canales DMA se cuentan desde 1. No lo cambié, lo dejé como en la fuente original.

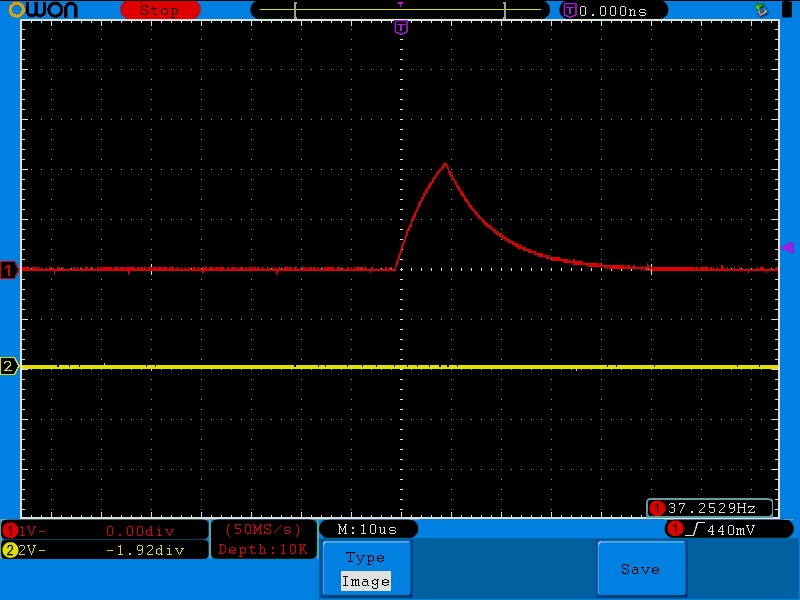

Se utiliza un temporizador TIM5 como generador de pulso único. Proporciona un conveniente modo de pulso único. La conveniencia radica en la posibilidad de establecer el tiempo antes del inicio del pulso y establecer la duración del pulso mismo. Este impulso salió como se muestra a continuación en la imagen, amablemente proporcionado por un osciloscopio alquilado.

El oscilograma muestra que el aumento del pulso dura 10 microsegundos, lo que significa que debe acomodar unas 100 muestras.

El proyecto se realizó en IAR 8.4 manualmente (es decir, sin Cuba y el Balón), pero espero que sea entendido por una variedad de religiones. Puedes verlo aquí .

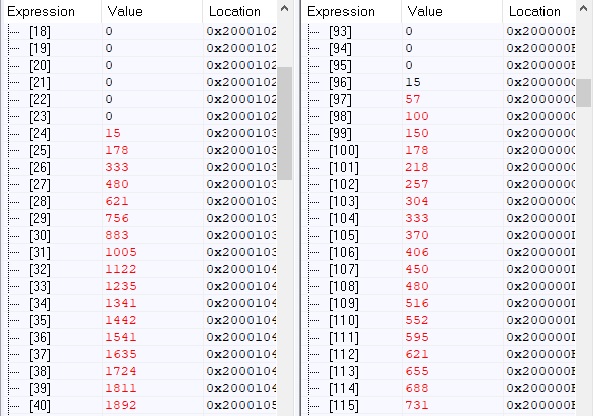

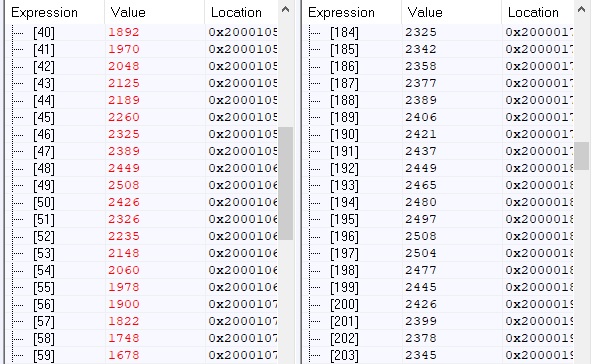

Aquí hay una imagen del contenido de un búfer ADC1 separado y el resultado recopilado de cuatro fuentes del búfer en la región del comienzo del pulso de entrada.

Pero el contenido de estos búferes está en la región del pico del pulso (donde el valor alcanza 2508).

Como puede ver, 196-95 = 101 recuentos se gastaron en la sección desde el comienzo del pulso hasta su pico.

Entonces, la frecuencia de muestreo es de 10 megahercios. No funcionó a esa velocidad de inmediato.

Para lograr esto, tuve que detener el procesador antes de iniciar el acceso directo a la memoria (DMA1). Es bueno que el Cortex-M4 tenga una instrucción de ensamblador especial WFI (Espere interrupciones). Si esto no se hace, entonces el procesador se interpondrá bajo los pies del DMA y ocupará el bus con accesos de memoria que bien pueden esperar.

Si aumenta el paso de conteo a 200 nanosegundos, dejarán de empujar y sanarán pacíficamente y felizmente.

Si involucramos al comparador COMP4 en su trabajo y conectamos su entrada positiva (puerto PB0) con la señal de entrada, entonces usamos el DAC (DAC1) y conectamos su salida (CH1) con la entrada negativa del comparador (dentro del controlador), obtenemos un dispositivo umbral con un umbral ajustable. Las interrupciones del funcionamiento del comparador le permitirán iniciar el temporizador general del reloj TIM1 y obtener un modo de espera, como en un osciloscopio.