Si pensabas que la "pandilla" de Intel son los partidarios más leales

de la ley de Moore , entonces probablemente no hayas escuchado cómo se está propagando Philip Wong sobre este tema. Wong, vicepresidente de investigación corporativa de Taiwan Semiconductor Manufacturing Corp (TSMC), hizo una presentación en una reciente conferencia de Hot Chips que indica que la ley de Moore no solo está viva y bien, sino con un conjunto bastante diverso de trucos tecnológicos, todavía no es cierto menos de tres décadas

"No está muerto", dijo a los presentes en Hot Chips. "No baja la velocidad, ni siquiera tose".

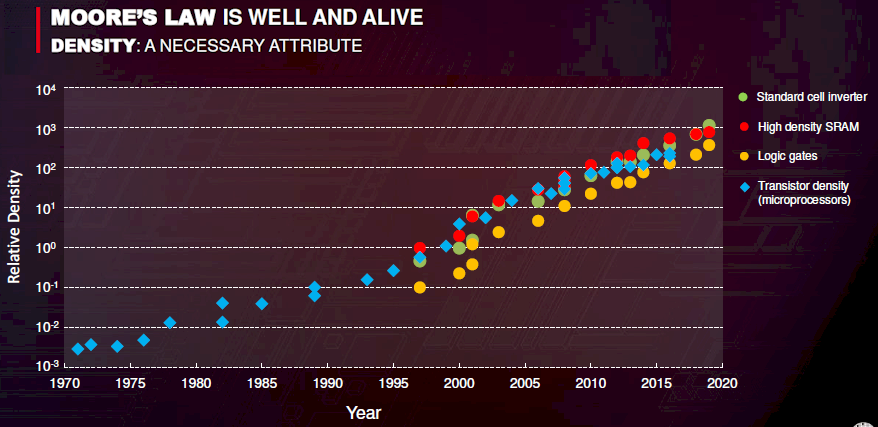

Escuche a Wong, entonces la única acción necesaria para mantener la ley de Moore es mejorar la densidad. Y aunque admite que la frecuencia del reloj ha descansado en su techo, marcando el final

de la ley de escala de Dennard , dice que es la densidad de los transistores lo que mejorará la velocidad y la eficiencia energética.

La ley de Moore está viva

La ley de Moore está vivaEn definitiva, no importa cuánto se logre una densidad más alta. Wong cree que lo principal es que las empresas pueden cargar más transistores en un volumen más pequeño con una mejor eficiencia energética. A corto plazo, esto se puede lograr de la manera antigua y comprobada, es decir, mejorando la tecnología de fabricación de CMOS para que produzca transistores con una longitud de puerta más corta.

TSMC ya ha dominado la tecnología de proceso de 7 nm y se está moviendo hacia 5 nm. Wong dijo que el ecosistema de desarrollo de tecnología de proceso de 5 nm ya está listo, y la compañía ya ha comenzado la producción de muestras riesgosas, es decir, la tecnología de proceso y las herramientas de desarrollo están listas, y se están produciendo sustratos de trabajo. En la última reunión de accionistas, TSMC anunció que planea comenzar la producción en masa de chips a 5 nm en el primer semestre de 2020. Resulta que los planes de la compañía ya incluyen una tecnología de proceso de 3 nm.

Pero toda esta tecnología se basa en chips

planos [planos], y Wong admite que este enfoque finalmente dejará de escalar. "Si seguimos el camino del aumento bidimensional, entonces ya hemos alcanzado varios cientos de átomos, y pronto todos nuestros átomos se agotarán", explicó.

Pero esto no significa el final del aumento de la densidad. Señaló que algunas innovaciones en la industria de semiconductores respaldaron un gráfico de densidad ascendente incluso al final de la escala de Dennard. En particular,

apareció la tecnología de silicio tensado y

dieléctrico de alta k , y luego FInFet (Fin Field Effector Transistor), la tecnología de estructuras tridimensionales, siguió. Ahora, para ir más allá de 7 nm, se está investigando la tecnología DTCO (Design Technology Co-Optimization).

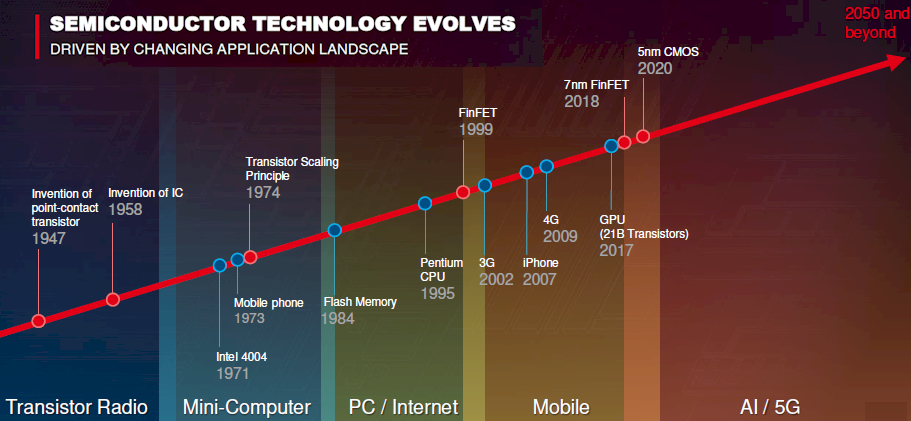

Todas estas innovaciones ocurrieron porque era necesario desarrollar nuevas plataformas informáticas que requerían hardware más rápido y con mayor eficiencia energética. Esta evolución generó minicomputadoras en la década de 1970, PC en la década de 1980, Internet en la década de 1990 y hoy en día, dispositivos móviles. Cada etapa requirió un aumento de densidad a través de la fabricación mejorada de semiconductores. Wong cree que las siguientes solicitudes provendrán de inteligencia artificial y 5G.

Evolución de la tecnología de semiconductores

Evolución de la tecnología de semiconductores¿Qué innovaciones serán necesarias para garantizar que Moore's Law Party no se detenga?

A corto plazo, la densidad computacional general y la densidad de memoria aumentarán el uso de conjuntos de chips utilizados para crear cajas de chips múltiples de estructuras 2.5D, incluso si los chips en sí no se vuelven más densos. Wong dijo que este proceso ya está haciendo que la tecnología de proceso específica de un chiplet individual sea un parámetro menos importante que la capacidad de integrar estos componentes en un solo paquete.

TSMC tiene su propia versión del chasis 2.5D con tecnología Chip-on-Wafer-on-Substrate (CoWoS) (Embedded Multi-die Interconnect Bridge, o EMIB, de Intel compite con esta tecnología). CoWoS le permite crear gabinetes de múltiples chips, fijar conjuntos de chips y una memoria adecuada en el intercalador, y conectarlos utilizando los contactos verticales TSV. La implementación más interesante de CoWoS es el acelerador de GPU Nvidia Tesla V100, en el que la GPU GV100 está repleta de memoria de alto ancho de banda (HBM). Intel, AMD y Xilinx están integrando más conjuntos de chips.

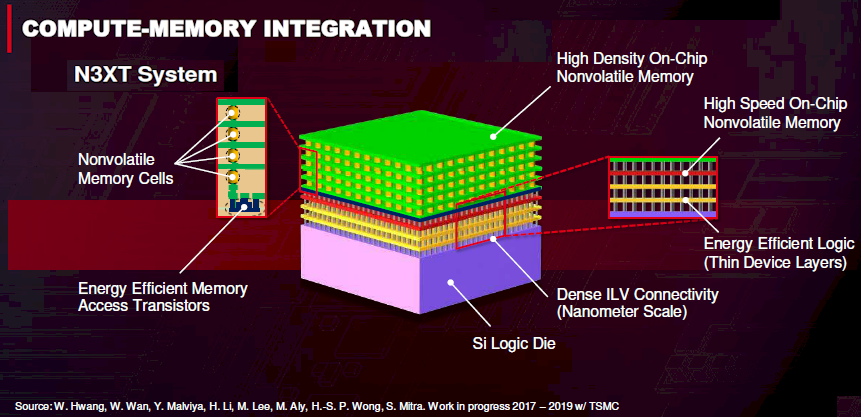

Pero las posibilidades de 2.5D para aumentar la densidad no son ilimitadas. Una solución más escalable requerirá tecnologías de colocación de transistores verdaderamente tridimensionales. Para esto, según Wong, la tecnología monolítica tridimensional N3XT es la más adecuada basada en nuevos materiales y una estrecha integración de la memoria con la lógica. N3XT, la "tecnología de nanoingeniería de los sistemas informáticos", se ha debatido en el mundo académico desde 2015, pero ahora que empresas como TSMC han comenzado a tomarlo en serio, tiene muchas posibilidades de comercialización.

Wong mostró diapositivas con diagramas de cómo podría verse ese dispositivo. Consiste en capas de lógica de eficiencia energética (amarillo), memoria de alta velocidad (rojo) y memoria no volátil de alta capacidad (verde), dispuestas alternativamente una encima de la otra. Y todo esto se encuentra en un cristal lógico de silicio común (púrpura).

Sistema N3XT

Sistema N3XTLo principal aquí es combinar las diversas capas a través de ILV, Inter-Layer-Via (acceso vertical entre capas). A diferencia de un TSV a escala micrométrica, el ILV se puede formar a escala nanométrica. Aunque esta es una parte extremadamente importante de la tecnología N3XT, Wong no podría decir mucho al respecto. Sin embargo, es obvio que TSMC está trabajando de cerca y ya ha registrado varias patentes relacionadas.

En los chips tridimensionales, el entrelazado de la memoria y la lógica es muy importante, ya que le permite reducir la distancia entre ellos, asegurando así un alto rendimiento y una baja latencia de transferencia de información, que será necesaria para aplicaciones como AI y 5G. En CMOS, la memoria y la lógica no se pueden intercalar, ya que el grabado de los transistores lógicos requiere una temperatura del orden de 1000 grados Celsius, lo que destruiría las capas vecinas en la producción. Requiere algo que pueda fabricarse a temperaturas del orden de 400 grados.

Resulta que en los últimos años, los investigadores han estudiado nuevos materiales que parecen ser adecuados para la producción de transistores de alta velocidad a temperaturas relativamente bajas. A diferencia de los materiales de silicio utilizados en la producción actual, las monocapas de dichos metales de transición de cogeneuro (TMD) se utilizan allí sobre la base de elementos como el molibdeno, el tungsteno y el selenio.

Los materiales TMD demuestran una alta movilidad de los portadores de carga (los electrones viajan a través de ellos con gran facilidad) con canales estrechos. Lo que es conveniente, son necesarias tales características para crear transistores con un tamaño de menos de 2-3 nm. Wong dijo que el laboratorio TSMC está probando sustratos TMD experimentales basados en disulfuro de tungsteno.

Otro candidato para los nanomateriales son los nanotubos de carbono. Wong dijo que sus variaciones experimentales se hicieron, mostrando un buen comportamiento del material como semiconductor. Ya se han ensamblado prototipos funcionales de lógica y SRAM basados en nanotubos de carbono, incluida la variante RISC-V de los investigadores del MIT.

En cuanto a la memoria, según Wong, los candidatos más probables para la integración tridimensional serán: SST-MRAM (memoria de acceso aleatorio magnetorresistivo de par de transferencia de giro, memoria de acceso aleatorio magnetorresistivo, que utiliza transferencia de momento de giro de electrones para registrar);

Memoria de cambio de fase PCM;

memoria resistiva de acceso aleatorio ReRAM; memoria basada en metalización programable de célula CBRAM; Memoria

ferroeléctrica de acceso aleatorio FERAM. Todo esto es memoria no volátil con acceso aleatorio, que no requiere la operación de borrar una celda antes de escribirle nueva información. Algunas opciones ya están en el mercado: Everspin MRAM, Samsung MRAM, Crossbar ReRAM e Intel 3D XPoint (que, según la mayoría, es una variante de PCM).

Nuevos tipos de memoria.

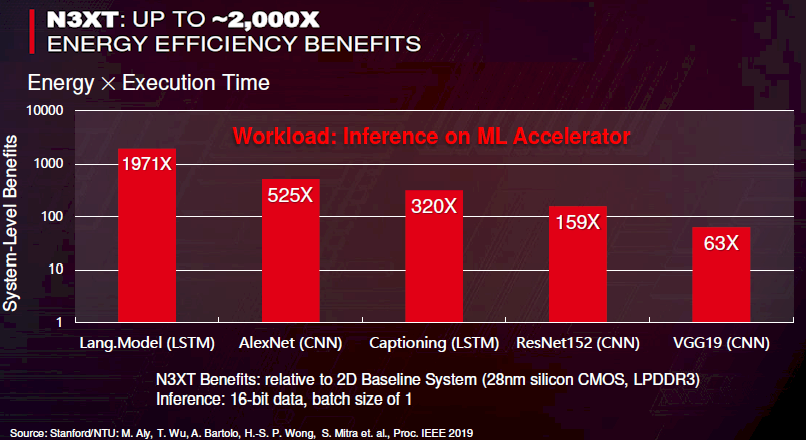

Nuevos tipos de memoria.Los investigadores simularon el rendimiento de los dispositivos N3XT y los compararon con los chips bidimensionales tradicionales con aproximadamente la misma capacidad lógica y de memoria. Según su investigación, donde se usaron varios métodos para medir la velocidad de los algoritmos de aprendizaje automático, los dispositivos de la tecnología N3XT resultaron ser 63-1971 veces más eficientes que los bidimensionales.

La ventaja del N3XT sobre los sistemas bidimensionales.

La ventaja del N3XT sobre los sistemas bidimensionales.Eso suena prometedor. Pero Wong no difundió cómo exactamente estas tecnologías en los próximos 30 años podrán mantener la velocidad de mejora tecnológica necesaria para la ley de Moore. Por ejemplo, la transición a nuevos nanomateriales nos dará un aumento único en la densidad de los transistores con respecto a los componentes bidimensionales. Pero allí, al final, encontraremos restricciones atómicas.

Teóricamente, si puede duplicar la altura de los dispositivos tridimensionales cada 18 meses, puede lograr un aumento de la densidad por área de superficie cuadrada. Por supuesto, para dispositivos móviles e integrados, este enfoque rápidamente se volverá demasiado engorroso, y los chips para computadoras en centros de datos después de siete u ocho generaciones descansarán en un techo de 4 metros.

Para que todo continúe funcionando durante varias décadas, y la densidad continúe encajando en la curva de la ley de Moore, deberán desarrollarse otras innovaciones técnicas no mencionadas por Wong. Pero si produce chips como TSMC, debe aceptar que los investigadores constantemente le darán nuevos candidatos para tecnologías que solo necesitarán solicitudes de tareas nuevas y más exigentes para ingresar al mercado. Y si recuerdas la historia, entonces tales tareas ciertamente aparecerán.