En los últimos dos artículos (

primero ,

segundo ), examinamos el principio de funcionamiento de

Check Point Maestro , así como las ventajas técnicas y económicas de esta solución. Ahora me gustaría ir a un ejemplo específico y describir un posible escenario de implementación para Check Point Maestro. Mostraré una especificación típica, así como una topología de red (circuitos L1, L2 y L3) usando Maestro. De hecho, verá un proyecto estándar listo para usar.

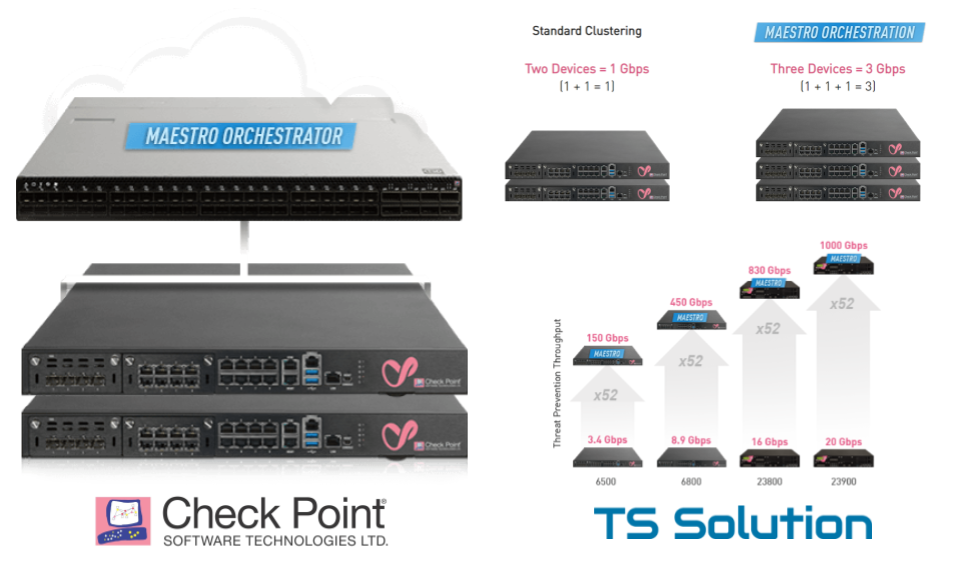

Supongamos que decidimos que usaremos la plataforma escalable Check Point Maestro. Para hacer esto, tome un paquete de tres puertas de enlace 6500 y dos orquestadores (para una tolerancia completa a fallas):

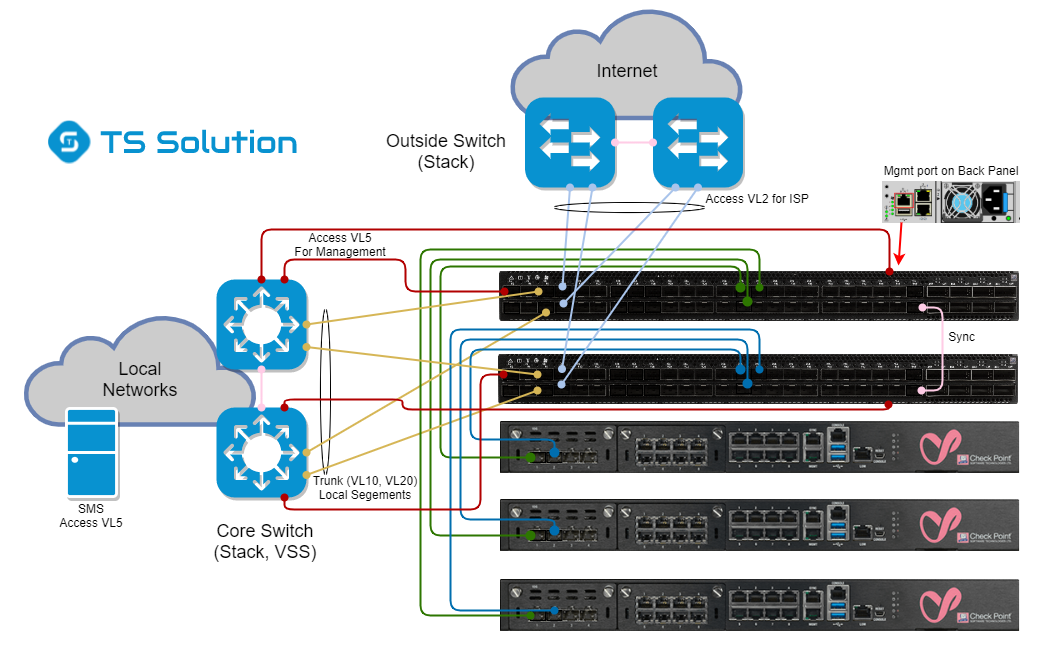

CPAP-MHS-6503-TURBO + CPAP-MHO-140 . El diagrama de conexión física (L1) se verá así:

Tenga en cuenta que es obligatorio conectar los puertos de administración de los orquestadores, que se encuentran en el panel posterior.

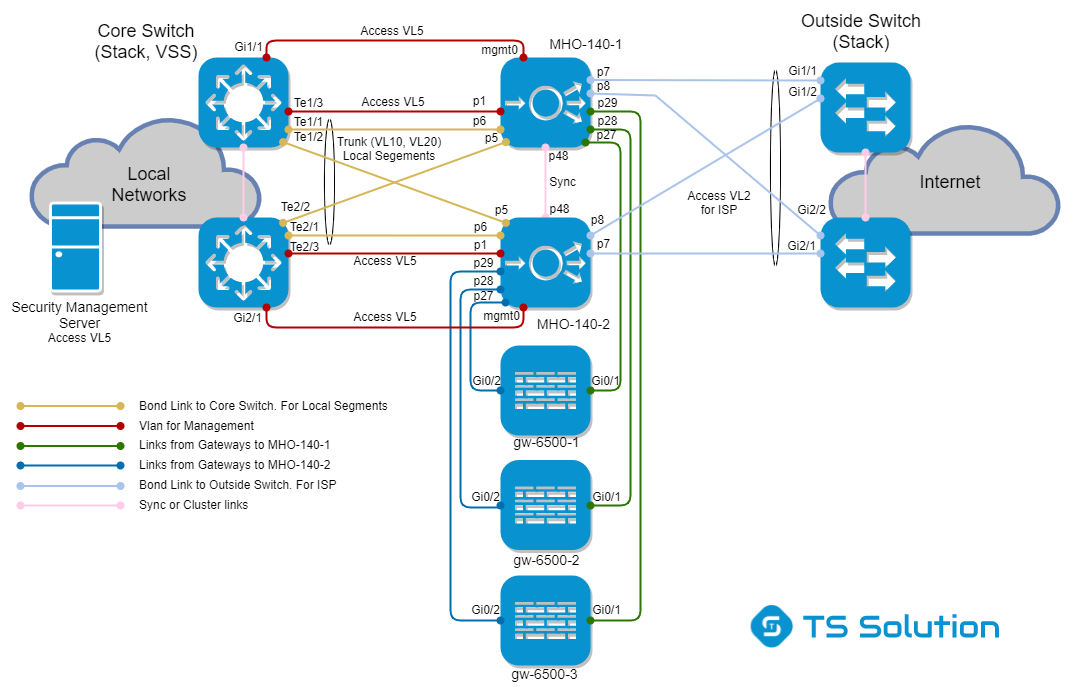

Sospecho que muchas cosas de esta imagen pueden no ser muy claras, por lo que inmediatamente daré un diagrama típico del segundo nivel del modelo OSI:

Algunos puntos clave en el esquema:

- Por lo general, se instalan dos orquestadores entre los conmutadores principales y los conmutadores externos. Es decir aislamiento físico del segmento de internet.

- Se supone que el "núcleo" es la pila (o VSS) de los dos conmutadores en los que está organizado el PortChannel de 4 puertos. Para Full HA, cada orquestador se conecta a cada conmutador. Aunque puede usar un enlace a la vez, como se hace con la VLAN 5 - red de administración (enlaces rojos).

- Los enlaces responsables de la transmisión del tráfico productivo (amarillo) están conectados a puertos de 10 gigabits. Para esto, se utilizan módulos SFP - CPAC-TR-10SR-B

- De manera similar (Full HA), los orquestadores están conectados a conmutadores externos (enlaces azules), pero utilizando puertos gigabit y los módulos SFP correspondientes: CPAC-TR-1T-B .

Las puertas de enlace están conectadas a cada uno de los orquestadores mediante cables DAC especiales que se incluyen (

Cable de conexión

directa (DAC), 1m - CPAC-DAC-10G-1M ):

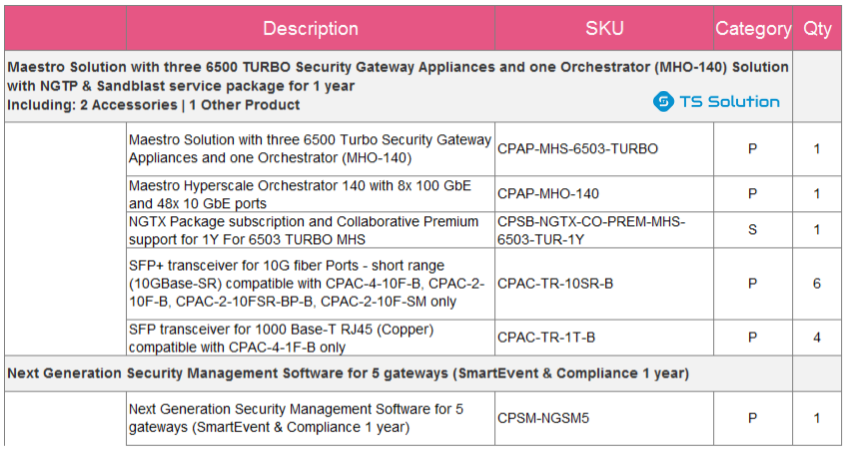

Como puede ver en el diagrama, debe haber una conexión de sincronización (enlace rosa) entre los rectores de Oracle El cable requerido también está incluido. La especificación final es la siguiente:

Lamentablemente no puedo publicar precios en el dominio público. Pero siempre puede

solicitarlos para su proyecto .

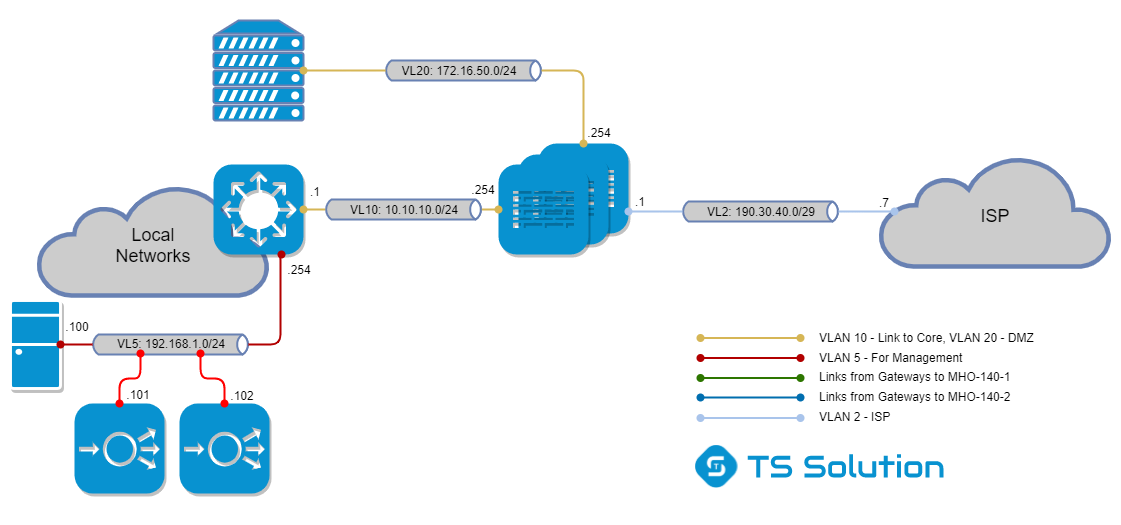

En cuanto al circuito L3, parece mucho más simple:

Como puede ver, todas las puertas de enlace en el tercer nivel se ven como un solo dispositivo. Al mismo tiempo, el acceso a los orquestadores es solo a través de la Red de administración.

Esto concluye nuestro breve artículo. Si tiene preguntas sobre los esquemas o necesita la fuente, deje comentarios o

escriba al correo .

En el próximo artículo, trataremos de mostrar cómo Check Point Maestro trata con el equilibrio y realiza pruebas de carga. ¡Así que estad atentos (

Telegram ,

Facebook ,

VK ,

Blog de soluciones TS )!

PD: ¡Expreso mi gratitud a Anatoly Masover e Ilya Anokhin (compañía Check Point) por su ayuda en la preparación de estos esquemas!