Introduccion

Una vez que necesitaba implementar un pequeño bloque de CAM (memoria asociativa). Después de leer cómo Xilinx hace esto en BRAM (bloques de memoria estática) o en SRL16 (registros de desplazamiento de 16 bits), me entristeció un poco, ya que sus implementaciones ocuparon mucho espacio. Decidí intentar hacerlo yo mismo. La primera opción era la implementación de la frente. Mirando hacia el futuro, se me ocurrió casi de inmediato y, bueno, la frecuencia objetivo para el diseño fue de solo 125 MHz.

Arquitectura

Para comenzar, considere la declaración del problema. Entonces, necesitamos una CAM pequeña con un ancho de palabra de 8-64 bits y una profundidad de 16-1024 palabras. Necesitaba una búsqueda binaria en CAM, pero más tarde resultó que hacer TCAM (memoria asociativa ternaria) es bastante barato en términos de recursos y afecta ligeramente el tiempo. El límite inferior de frecuencia es de 125 MHz en la familia Kintex7 . ¡Empecemos! Nuestro CAM estará compuesto por estas líneas, cada una de las cuales corresponderá a una dirección y almacenará una palabra:

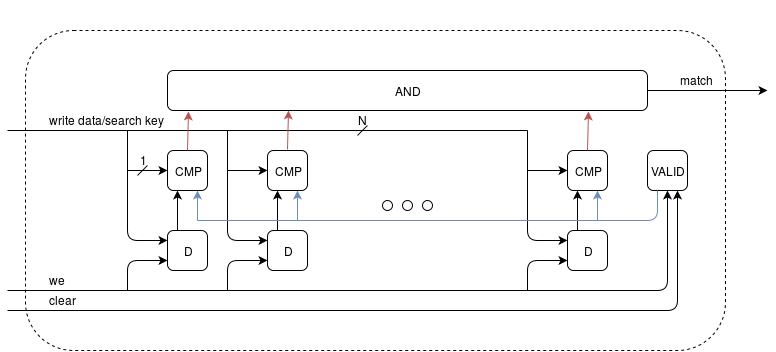

Figura 1. La estructura de una línea de CAM

En la Fig. 1, D es un disparador D normal para almacenar datos; el número de estos disparadores en la línea corresponde al ancho de la palabra de datos de entrada en CAM. VÁLIDO - D-trigger, que almacena '1' si los datos en la línea son relevantes. CMP es un comparador que compara el valor del bit de bus de clave de búsqueda correspondiente si VALID = '1'. escribir datos : escribir bus de datos , conectado en bits a la D correspondiente (ancho de palabra N - CAM), nosotros - escribir bandera, borrar - restablecer VÁLIDO (invalidación de la línea de datos). AND - lógico AND de N salidas de los comparadores, el marcador de coincidencia se convierte en '1' si la búsqueda en esta línea es exitosa.

Entonces, tenemos una línea en la que podemos buscar. Ahora combínalos:

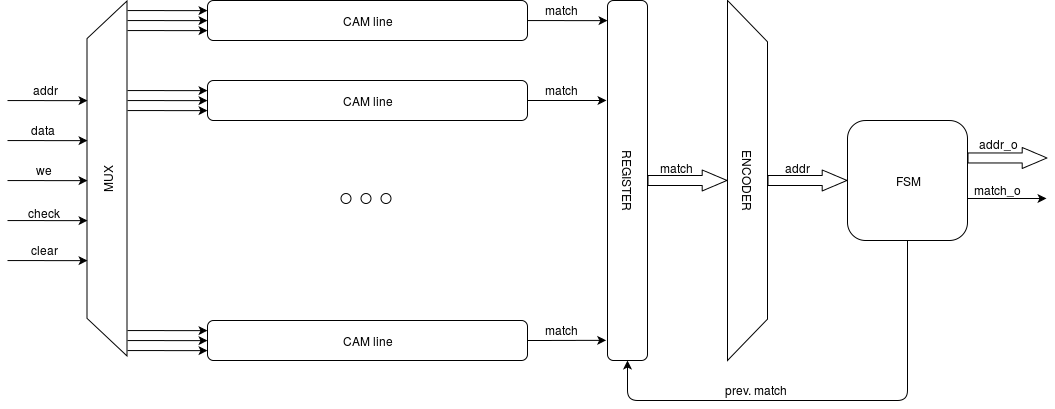

Figura 2. Estructura CAM

En la Fig. 2, CAM_line es la línea CAM real de la Fig. 1, MUX es el multiplexor de dirección de entrada, MATCH REGISTER es un registro que almacena los valores de los marcadores de coincidencia, ENCODER es un decodificador que convierte el bus de coincidencias en la dirección de coincidencia más baja encontrada. FSM es una máquina controladora de estados finitos, que es anterior. match elimina de MATCH REGISTER el bit correspondiente a la dirección enviada para que ENCODER cambie a la siguiente dirección encontrada. La interfaz de nuestra CAM será la siguiente:

Tabla 1. Interfaz CAM

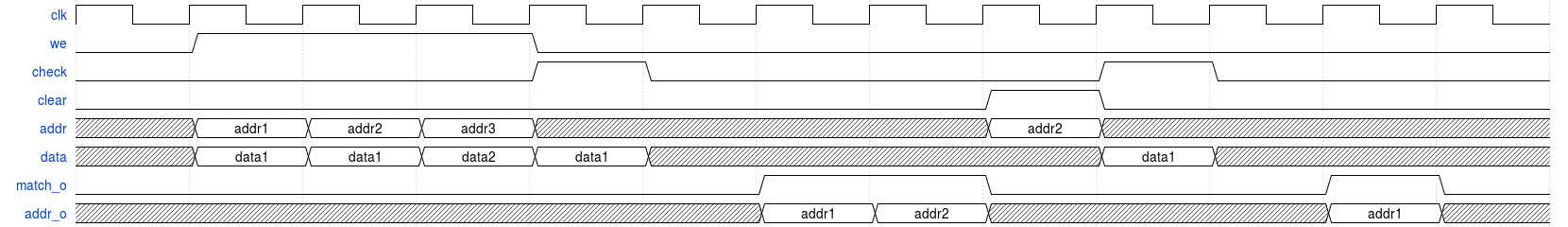

A continuación, en la Fig. 3, hay un diagrama de tiempo del funcionamiento de esta interfaz, que muestra primero la grabación de tres palabras en CAM, luego una búsqueda exitosa, borrado y búsqueda nuevamente:

Figura 3. Diagrama de tiempos de la interfaz a la CAM

Entonces, tenemos una descripción de CAM, pasemos a la síntesis.

Síntesis

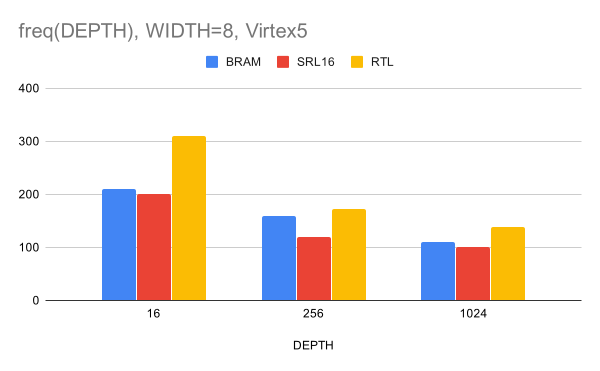

Sintetizaremos en Xilinx ISE para comparar los resultados con los obtenidos en XAPP1151 .

Figura 4. Dependencia de frecuencia después de XST (sintetizador como parte de ISE) en la profundidad CAM para el ancho del bus de datos de 8 bits

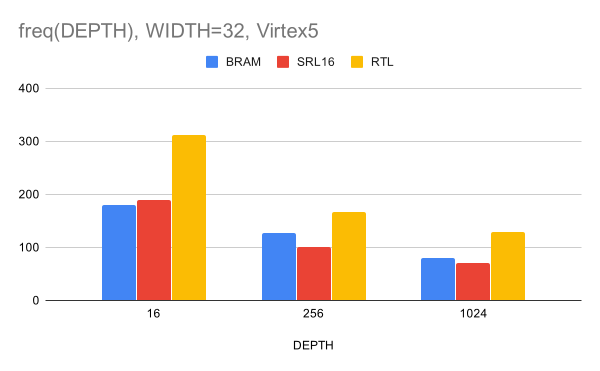

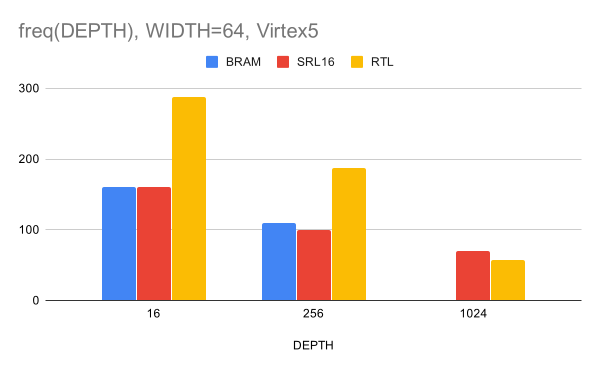

Figura 5. Frecuencia después de XST versus profundidad CAM para el ancho del bus de datos de 32 bits

Figura 6. Frecuencia después de XST versus profundidad CAM para el ancho del bus de datos de 64 bits

En la Fig. 6, no hay datos para Virtex5 , ya que CAM de este tamaño no se ajustaba a la BRAM existente. También observamos que para un ancho de 64 bits y una profundidad de 1024, nuestro resultado fue ligeramente peor que el de la implementación en SRL16. Ahora pasemos a la síntesis de Vivado para el XC7K325T . Los resultados son los siguientes:

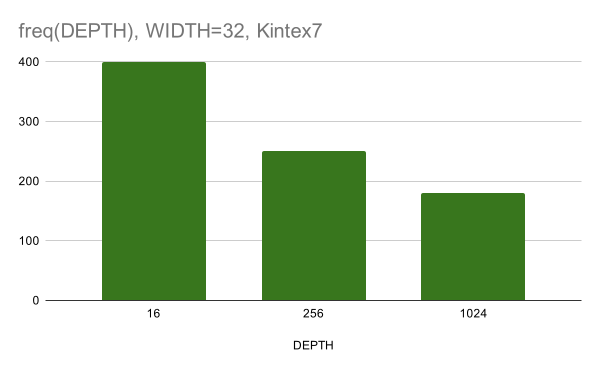

Figura 7. Dependencia de frecuencia después de PnR (colocación de bloques en el chip y seguimiento de señal) en la profundidad CAM para un ancho de bus de datos de 32 bits

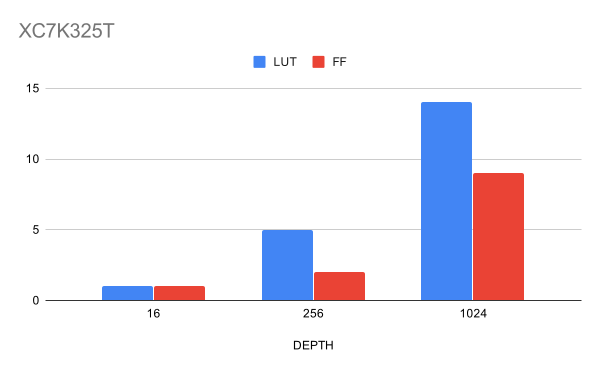

Figura 8. Utilización de recursos para varias profundidades CAM para un ancho de datos de 32 bits en%

Es importante tener en cuenta que los resultados en Vivado se obtuvieron después de PnR, lo que significa que el diseño no tiene dificultades con el trazado.

TCAM

Como se mencionó anteriormente, obtener este enfoque de CAM TCAM no fue un problema particular. Es suficiente agregar un bus de enmascaramiento de datos para bits de datos y distribuirlo poco a poco en los comparadores para que al comparar datos con una clave, tengan en cuenta su valor. Tal cambio no condujo a una caída en la frecuencia o un aumento serio en los recursos consumidos, por lo que obtuvimos TCAM de forma gratuita.

Conclusiones

Entonces, pudimos completar la tarea. El diseño resultante permite que la séptima familia Xilinx FPGA reciba CAM suficientemente grande con una frecuencia por encima del objetivo de 125 MHz. El resultado de la comparación con XAPP1151 resultó inesperado para mí, supuse que la implementación en BRAM, aunque es muy costosa en términos de recursos, superará la implementación frontal en frecuencia. Sin embargo, no celebre la victoria tan temprano, este documento describe el núcleo Xilinx CAM IP, que permite, por ejemplo, obtener CAM con una profundidad de celdas de 32K y una frecuencia de 155 MHz, basada en BRAM. Este resultado probablemente se pueda lograr en la versión propuesta en el artículo, ya sea agregando las etapas de la tubería o recolectando CAM grandes de los pequeños, pero no puedo predecir de inmediato si encajará en el chip. En el futuro intentaré implementar algo similar en BRAM, pero por ahora, gracias por su atención.