Colocar conjuntos de chips desnudos en una red de silicio le permitirá hacer computadoras más pequeñas y más potencia de procesamiento

La necesidad de fabricar ciertos dispositivos cada vez menos, mientras que otros cada vez más, ha sido durante mucho tiempo el principal motivador para la innovación en electrónica. La primera opción se manifiesta en progreso desde computadoras portátiles a teléfonos inteligentes, luego a relojes inteligentes, auriculares inteligentes y otros dispositivos electrónicos "invisibles". La segunda opción determina la configuración de los centros de datos modernos: monstruos de megavatios que llenan instalaciones de almacenamiento especialmente construidas para ellos en todo el mundo. Curiosamente, en ambos casos, el progreso está limitado por la misma tecnología, solo por varias razones.

Argumentamos que el PCB es el culpable. Nuestra solución es deshacernos de él por completo.

Nuestro estudio muestra que las placas de circuitos impresos pueden reemplazarse con el mismo material en el que consisten los chips soldados, es decir, silicio. Tal enfoque permitiría crear sistemas de menor tamaño y peso, adecuados para dispositivos electrónicos portátiles y otros dispositivos de tamaño limitado, e increíblemente potentes computadoras de alta velocidad, capaces de empujar la potencia informática de una docena de servidores en un sustrato de silicio del tamaño de un plato.

Una tecnología similar de silicio, que llamamos la red de interconexión de silicio, le permite conectar chips desnudos directamente a fragmentos de silicio individuales. A diferencia de las pistas en las placas de circuito impreso, el contacto entre los chips en nuestro sustrato es del mismo tamaño que las pistas dentro de los chips. En este sentido, se pueden establecer muchas más conexiones en el sustrato, y todas ellas son capaces de transmitir datos más rápido con menos consumo de energía.

El tejido de interconexión de silicio (Si-IF) proporciona otro beneficio adicional. Esta es una excelente manera de dividir los sistemas de un solo chip de producción relativamente grandes, complejos e incómodos [system-on-a-Chip, SoC], en los que todo descansa hoy, desde teléfonos inteligentes hasta supercomputadoras. En lugar de SoC, los desarrolladores de sistemas podrían usar conglomerados de diseño más pequeño y más simple y en la producción de chiplets, estrechamente interconectados en Si-IF. Tal revolución de los conjuntos de chips ya está en marcha: AMD, Intel, Nvidia y otras compañías están ofreciendo conjuntos de conjuntos de chips ensamblados dentro de cajas avanzadas. Una red de silicio interconectada amplía esta idea al romper la carcasa del sistema y permitirle incluir toda la computadora.

Para comprender el beneficio total de eliminar una placa de circuito, considere lo que sucede con un SoC típico. Debido al desarrollo de la electrónica de acuerdo con la ley de Moore, en un centímetro cuadrado de silicio, puede empacar casi todo lo que necesita para que un teléfono inteligente funcione. Desafortunadamente, por muchas razones relacionadas con las características de la placa de circuito impreso, esta pieza de silicio se coloca dentro de una caja de plástico, a veces 20 veces el tamaño del chip.

La diferencia de tamaño entre el chip y la carcasa crea al menos dos problemas. En primer lugar, el peso y el volumen de un chip empaquetado es mayor que el de una pieza de silicio. Obviamente, este es un problema para todos los dispositivos que necesitan ser pequeños, delgados y livianos. En segundo lugar, si un producto terminado requiere que varios chips intercambien datos entre sí (y la mayoría de los sistemas tienen uno), la distancia que necesita cubrir la señal aumenta más de 10 veces. Este es un cuello de botella para la velocidad y el consumo de energía, especialmente cuando se intercambian grandes cantidades de datos. Este es probablemente el mayor desafío para implementar aplicaciones dependientes de datos: gráficos, aprendizaje automático y búsqueda. Peor aún, las papas fritas en tales casos son más difíciles de enfriar. La disipación de calor ha sido un factor limitante en la electrónica durante varias décadas.

Pero si estos casos son tan problemáticos, ¿por qué no deshacerse de ellos? Por la placa de circuito.

La tarea de la placa de circuito es combinar chips, componentes pasivos y otros dispositivos en un sistema de trabajo. Pero esta tecnología no es perfecta. Las placas de circuito impreso son difíciles de igualar perfectamente: a menudo se doblan. Las cajas de chips generalmente se conectan a la placa mediante gotas de soldadura, que se funden y vuelven a soldar durante la producción. Las limitaciones de la tecnología de soldadura junto con la curvatura de la superficie hacen que las gotas no estén más cerca de 0.5 mm entre sí. En otras palabras, será posible colocar no más de 400 contactos por centímetro cuadrado. Para muchas aplicaciones, esto es demasiado poco para la transmisión de potencia y señal hacia y desde el chip. Por ejemplo, en una pequeña superficie ocupada por el cristal del procesador Intel Atom, hay suficiente espacio para cientos de contactos con un tamaño de 0,5 mm, y necesita 300. Los desarrolladores usan cajas para cristales para que las matemáticas converjan con el número de contactos por unidad de área. El estuche toma pequeños contactos de un chip de silicio, de 1 a 50 micras de ancho, y los extiende a la escala de la placa, 500 micras.

Recientemente, la industria de los semiconductores ha intentado limitar los problemas asociados con las placas de circuito impreso mediante el desarrollo de gabinetes avanzados con tecnología de interposición de silicio. El intercalador es una capa delgada de silicio en la que se une una pequeña cantidad de chips de silicio desnudos, conectados entre sí a través de una gran cantidad de contactos. Pero al mismo tiempo, el intercalador con sus chips aún debe estar oculto en la caja y colocarse en la placa de circuito impreso, por lo que esta opción agrega complejidad sin resolver los problemas restantes. Además, los intercaladores son necesariamente delgados, frágiles y de tamaño limitado, lo que significa que es difícil crear sistemas grandes en ellos.

Creemos que la mejor opción sería deshacerse por completo de las cajas y placas de circuito impreso uniendo los chips a un sustrato de silicio relativamente grueso (de 500 micras a 1 mm). Los procesadores, los cristales de memoria, los conjuntos de chips de RF, los módulos de control de voltaje e incluso los componentes pasivos como inductores y condensadores se pueden conectar directamente al silicio. En comparación con el material habitual de las placas de circuito impreso (fibra de vidrio y composición epoxi FR-4), el sustrato de silicio es sólido y puede pulirse en un plano casi perfecto, por lo que la curvatura no le tiene miedo. Además, dado que los chips y el sustrato se expandirán y contraerán cuando la temperatura cambie en la misma cantidad, ya no necesita una conexión grande y flexible entre el chip y el sustrato, como la soldadura.

Las gotas de soldadura se pueden reemplazar con pernos de cobre micrométricos incrustados en el sustrato. Usando compresión térmica, de hecho, la aplicación precisa de calentamiento y presión, los contactos de entrada / salida de cobre de los chips se pueden conectar directamente a los pines. La optimización completa de la unión de termocompresión puede proporcionarnos contactos mucho más confiables que la soldadura, y al mismo tiempo usar menos materiales diferentes.

Al eliminar las placas de circuito impreso y sus debilidades, será posible organizar los puertos de E / S a una distancia de solo 10 micras entre sí en lugar de 500 micras. Como resultado, será posible colocar 2500 veces más puertos en un chip de silicio sin la necesidad de usar un estuche.

Aún mejor, el proceso estándar de fabricación de semiconductores se puede reconfigurar para fabricar diagramas de cableado Si-IF de niveles múltiples. Sus pistas pueden hacerse mucho más delgadas que en las placas de circuito impreso. Se pueden separar entre sí por solo 2 micras, y no por 500 micras, como en las placas de circuito impreso. La tecnología incluso le permite colocar chips a una distancia de 100 micrones entre sí, a diferencia de las placas de circuito impreso, donde debería ser más de 1 mm. Como resultado, el sistema Si-IF ahorra espacio, energía y tiempo de viaje.

Además, a diferencia de las placas de circuito impreso y los materiales para cajas de circuitos integrados, el silicio conduce el calor bastante bien. Los radiadores se pueden montar en ambos lados del Si-IF para eliminar aún más calor, según nuestras estimaciones, un 70% más. Y cuanto más calor se elimine, más rápido podrán trabajar los procesadores.

Aunque el silicio tiene buena resistencia a la tracción y tenacidad, es ligeramente frágil. Afortunadamente, la industria de los semiconductores ha desarrollado métodos para trabajar con sustratos de silicio grandes para evitar el agrietamiento durante varias décadas. Y después de todos los procedimientos de producción de Si-IF necesarios, esperamos que pasen la mayoría de las pruebas de confiabilidad, incluidas las pruebas de impacto, el calentamiento cíclico y la exposición ambiental.

No hay forma de escapar del hecho de que el silicio cristalino es más caro que el FR-4. Aunque el costo depende de muchos factores, el precio por milímetro cuadrado de una placa de circuito impreso de 8 capas puede ser diez veces menor que el de un Si-IF de 4 capas. Sin embargo, nuestro análisis muestra que si resta el costo de colocar los chips en los estuches y la compleja producción de los tableros, y tiene en cuenta el ahorro de espacio utilizando la tecnología Si-IF, la diferencia en el costo será insignificante y, en algunos casos, el Si-IF puede ser incluso más rentable.

Red de silicio entre componentes en comparación con la placa de circuito impreso y los chips en el chasis. En la parte inferior del diagrama hay una escala aproximada para comprender la diferencia de tamaño.

Red de silicio entre componentes en comparación con la placa de circuito impreso y los chips en el chasis. En la parte inferior del diagrama hay una escala aproximada para comprender la diferencia de tamaño.Veamos algunos ejemplos de los beneficios de usar Si-IF en un sistema informático. En un estudio de diseños de servidores, descubrimos que el uso de procesadores sin chasis que usan Si-IF puede duplicar el rendimiento de los procesadores convencionales debido a una conectividad mejorada y una mayor disipación de energía. Además, el tamaño de la "placa" de silicio (en ausencia de un término mejor) se puede reducir de 1000 cm

2 a 400 cm

2 . Una disminución tan grave afectará significativamente el volumen de los edificios del centro de datos y el tamaño de la infraestructura de enfriamiento. En cuanto al otro extremo de la escala, estudiamos un pequeño sistema para el "Internet de las cosas" basado en el microcontrolador Arm. En este caso, el uso de Si-IF reduce no solo el tamaño de la placa en un 70%, sino también su peso, de 20 a 8 gramos.

Además de reducir los sistemas existentes y aumentar la productividad, Si-IF permitirá a los desarrolladores crear computadoras que de otro modo serían imposibles de construir, o sería muy poco práctico.

En un servidor potente típico, la placa cuesta 2-4 procesadores. Algunos proyectos con alta carga computacional requieren múltiples servidores. Al mover datos entre diferentes procesadores y placas, se producen retrasos y cuellos de botella. Pero, ¿qué pasa si todos los procesadores se colocan en un solo sustrato de silicio? Podrían integrarse tan estrechamente que todo el sistema funcionaría como un gran procesador.

Este concepto fue propuesto por primera vez por Gene Amdahl en su empresa Trilogy Systems. Pero Trilogy no tuvo éxito, porque su proceso de producción no pudo producir suficiente calidad para el sistema de trabajo. Cuando se fabrica un chip, siempre existe la posibilidad de defectos, y con un aumento en su área, la probabilidad de matrimonio aumenta exponencialmente. Cuando el tamaño del chip es comparable a un plato de comida, es casi seguro que mata todo el sistema de matrimonio.

Pero si tiene una red de interconexión de silicio, puede comenzar con los conjuntos de chips que ya podemos fabricar sin defectos y luego combinarlos en un solo sistema. Nuestro equipo de investigadores de la Universidad de California en Los Ángeles y la Universidad de Illinois en Urbana-Campaign desarrollaron dicho sistema con un sustrato que contiene 40 GPU. En las simulaciones, aceleró los cálculos en más de 5 veces, y consumió energía en un 80% menos que el sistema equivalente de 40 GPU creado con cajas avanzadas de múltiples chips y placas de circuito impreso.

Los resultados fueron convincentes, aunque la tarea no fue fácil. Teníamos que tener en cuenta muchas restricciones, en particular: la cantidad máxima de calor eliminada del sustrato; cómo hacer que la GPU intercambie datos lo más rápido posible; cómo suministrar energía a toda el área del sustrato.

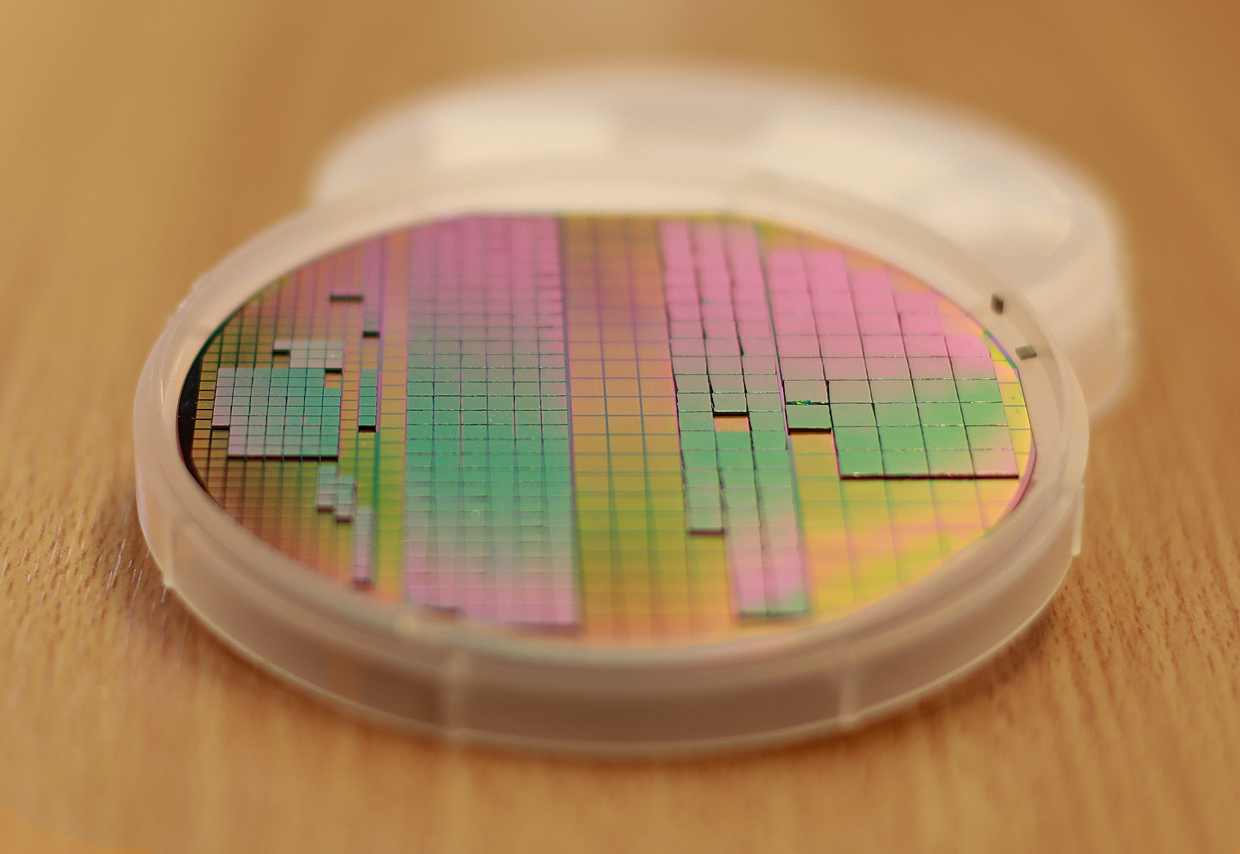

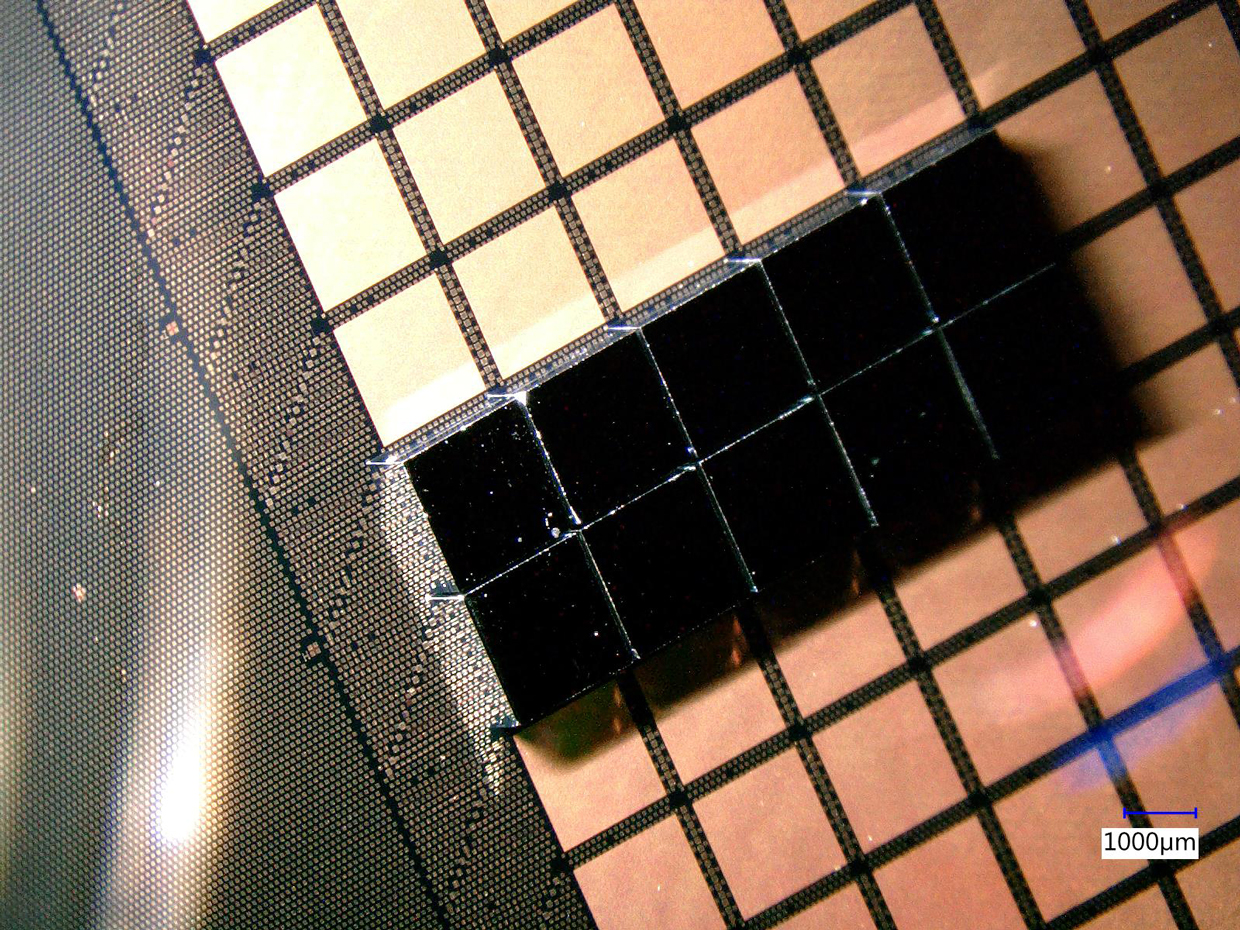

Diletes, o conjuntos de chips, integrados en una red de silicio interconectada, sustrato de 100 mm. Los diletes, a diferencia de los chips en una placa de circuito impreso, se pueden colocar a una distancia de 100 micrones entre sí

Diletes, o conjuntos de chips, integrados en una red de silicio interconectada, sustrato de 100 mm. Los diletes, a diferencia de los chips en una placa de circuito impreso, se pueden colocar a una distancia de 100 micrones entre síLa principal limitación fue la nutrición. Con un voltaje de funcionamiento de chip estándar de 1 V, las pistas delgadas del sustrato tendrían que consumir 2 kW. En cambio, elevamos el voltaje a 12 V, reduciendo así la corriente y la potencia. Para hacer esto, era necesario distribuir los reguladores de voltaje y los condensadores por todo el sustrato, y tomaron el lugar que de otro modo podría asignarse a GPU adicionales. Inspirados en los primeros resultados, ahora estamos armando un prototipo de sistema informático que esperamos completar para fines de 2020.

Una red de silicio interconectada puede desempeñar un papel en una tendencia importante en la industria informática: la división del SoC en conjuntos integrados de daylets [dielet - de “die”, crystal y “–let”, prefijo de reducción / aprox. transl.], o chiplets (preferimos llamarlos daylets, ya que esto enfatiza su esencia como cristales de silicio desnudos, su pequeño tamaño y, posiblemente, su funcionalidad incompleta sin otros daylets Si-IF). En las últimas dos décadas, el deseo de aumentar el rendimiento y reducir los costos ha convencido a los desarrolladores a reemplazar los conjuntos de chips con SoC integrados aún más grandes. Y, a pesar de sus ventajas, SoC tiene una cantidad suficiente de desventajas.

En primer lugar, el SoC es un chip grande y, como ya se mencionó, es bastante difícil lograr indicadores aceptables del porcentaje de rechazos en la producción de chips grandes, especialmente en las industrias avanzadas de semiconductores (recuerde que el porcentaje de rechazos crece exponencialmente al aumentar el área de chips). Otra desventaja de SoC es el alto costo de diseñar y comenzar la producción; Por ejemplo, en los EE. UU., una máscara fotolitográfica puede costar desde $ 2 millones, lo que hace que la opción de SoC no esté disponible para la mayoría de los esquemas. Además, cualquiera, incluso un pequeño cambio en el esquema o la actualización del proceso de producción requerirá un procesamiento significativo de todo el SoC. Finalmente, el enfoque de SoC intenta ajustar todos los subsistemas en un proceso de producción, incluso cuando algunos de estos subsistemas se podrían mejorar en otro proceso. Como resultado, nada en SoC logra la mayor eficiencia o velocidad posible.

La integración en Si-IF sin la participación de recintos evita todos estos problemas, al tiempo que mantiene el tamaño y la velocidad pequeños de SoC, al tiempo que ofrece ventajas y costos de desarrollo. Descompone el SoC en sus componentes constituyentes y recrea un sistema en un sustrato, sistema en Si-IF (SoIF).

Dicho sistema consiste en daylets producidos independientemente que están conectados a través de Si-IF. La distancia mínima que separa los diletes (decenas de micrómetros) es comparable a la distancia entre dos bloques de funciones SoC. El cableado en Si-IF es el mismo que el utilizado en el nivel superior de SoC, por lo que la densidad de los compuestos es comparable.

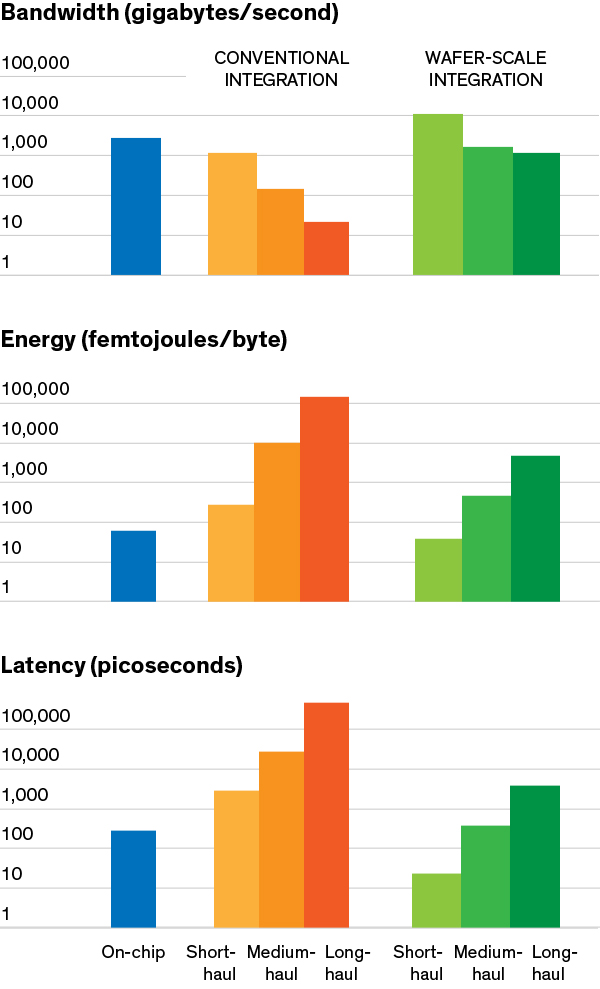

De arriba a abajo: ancho de banda (GB / s), consumo de energía (fJ / B), retraso (ps).

De arriba a abajo: ancho de banda (GB / s), consumo de energía (fJ / B), retraso (ps).

Azul: sistema en un chip, tonos de rojo: integración normal, tonos de verde: sistema sobre sustratoLas ventajas de SoIF sobre SoC se deben al tamaño del retraso. Las eliminaciones pequeñas son más baratas de producir que las grandes SoC porque tienen una tasa de rechazo menor debido a su pequeño tamaño. En SoIF, solo el sustrato tiene un gran tamaño. Pero es poco probable que tenga un problema con el matrimonio, ya que está hecho de varias capas que son fáciles de fabricar. La mayor parte de la pérdida debida a defectos se debe a defectos en las capas del transistor o en capas metálicas inferiores superdensas, y este es el caso de una red de silicio interconectada.

Además, SoIF tendrá todas las ventajas en la búsqueda de que la industria esté cambiando a chipsets. Por ejemplo, la transición de SoIF al siguiente proceso de fabricación debería ser más fácil y más barata. Cada dylet puede tener su propia tecnología de producción, y solo aquellos dylets que realmente lo requieran pueden actualizarse. Y las eliminaciones que no se benefician particularmente de los transistores reducidos no necesitarán ser cambiadas. Dicha integración heterogénea le permite crear una clase completamente nueva de sistemas que mezclan mezcladores de diferentes generaciones y tecnologías que generalmente no son compatibles con CMOS. Por ejemplo, nuestro grupo demostró recientemente la combinación de un cristal de fosfuro de indio con SoIF como un ejemplo de uso potencial en circuitos de alta frecuencia.

Dado que los dilettes se producirán y verificarán antes de conectarse a SoIF, se pueden usar en diferentes sistemas, lo que ahorrará significativamente en ellos. Como resultado, el costo total de desarrollar y fabricar SoIF puede ser un 70% más bajo que el de SoC. Esto será especialmente cierto para los sistemas grandes producidos en lotes pequeños, como es el caso de las industrias aeroespacial y de defensa, donde solo hay demanda de lotes del orden de varios cientos o miles de unidades. Los sistemas personalizados también serán más fáciles de hacer en SoIF, ya que esto reduce los costos y el tiempo de desarrollo.

Creemos que tales beneficios de costo y diversidad pueden conducir al comienzo de una nueva era de innovación en la que el nuevo hardware estará disponible para un número mucho mayor de diseñadores, nuevas empresas y universidades.

En los últimos años, hemos logrado un progreso significativo en la tecnología de integración Si-IF, pero queda mucho por hacer. En primer lugar, es necesario mostrar un proceso de producción de Si-IF poco defectuoso y comercialmente viable.

La creación de sustratos a escala Si-IF puede requerir innovación en la litografía sin máscara. La mayoría de los sistemas litográficos que existen hoy en día pueden hacer sustratos de 33x24 mm. Como resultado, necesitamos un sistema capaz de entregar un sustrato con un diámetro de 300 mm.También necesitamos mecanismos para controlar daylets desnudos y Si-IF. La industria ya se está moviendo hacia la prueba de cristales desnudos, ya que los fabricantes de chips están cambiando a los cheatlets en paquetes avanzados e integración tridimensional.Luego necesitamos nuevos radiadores u otras estrategias de disipación de calor que utilicen una buena conductividad térmica de silicio. Mis colegas de la Universidad de California y yo estamos desarrollando una solución integrada de nutrición y enfriamiento de sustrato llamada PowerTherm.Además, para el ensamblaje de sistemas completos, necesitará marcos, sujetadores, conectores y cables.También tendremos que hacer algunos cambios en la metodología de desarrollo para que una de las promesas de SoIF se haga realidad. Si-IF es un sustrato pasivo en el que solo hay un conductor. Por lo tanto, las conexiones entre vuelos deben ser cortas. Para pistas más largas que conectan dilets lejanos, necesitamos dilets intermedios que pasen datos más abajo en la cadena. Será necesario revisar los algoritmos de diseño responsables de la disposición de los elementos y el propósito de los contactos para que aprovechen al máximo este tipo de integración. Y también necesitaremos desarrollar nuevas formas de explorar diversas arquitecturas de sistemas que aprovechen la heterogeneidad y la capacidad de actualización de SoIF.También tendremos que tener en cuenta la fiabilidad de los sistemas. Si se descubre que un dique es defectuoso después de unirlo o falla durante la operación, será muy difícil reemplazarlo. Por lo tanto, en SoIF, especialmente en los grandes, será necesario generar tolerancia a fallas. Se puede implementar a nivel de red o a nivel de día. A nivel de red, será necesario garantizar el paso de la señal sin pasar por los daylets fallidos. A nivel de día, se pueden considerar varios trucos con redundancia física, por ejemplo, el uso de varios pines de cobre para cada uno de los puertos de E / S.Por supuesto, las ventajas de un conjunto de daylet dependen de la disponibilidad de daylets útiles que se puedan integrar en el sistema. Hasta ahora, la industria está resolviendo qué tipo de dilets debería producir. No puede hacer un daylet para cada subsistema en SoC, porque algunos de los daylet serán demasiado pequeños. Un enfoque prometedor es el uso del procesamiento estadístico de los circuitos SoC existentes y las placas de circuitos impresos para encontrar funciones que "tienden" a estar físicamente más cerca unas de otras. Si estas funciones tienen las mismas tecnologías de producción y ciclos de actualización, entonces deben integrarse en un solo día.Esta lista de problemas puede parecer muy larga, pero los investigadores ya están trabajando en algunos de ellos como parte del programa de Estrategias de Reutilización de IP y de Integración Heterogénea Común de Defensa de la Agencia de Proyectos de Investigación Avanzada de Defensa (CHIPS), así como con consorcios industriales. Y si podemos resolver estos problemas, nos ayudará seriamente a mantener el legado de la ley de Moore de una manera más pequeña, más rápida y más barata.