Boris Tsirlin y Alexander Kushnerov

30/10/2019

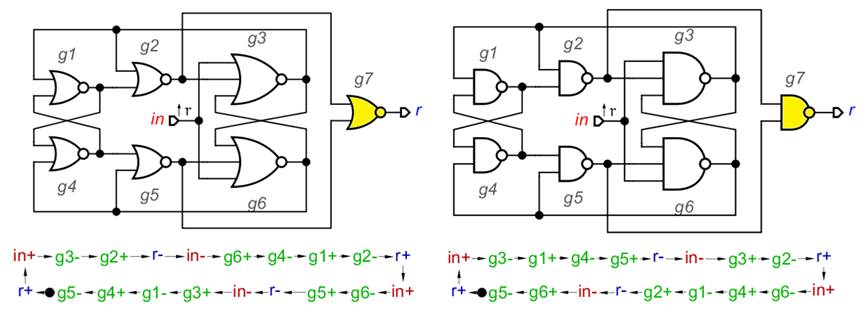

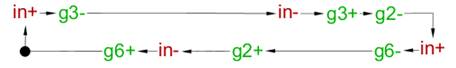

No es difícil para un diseñador de circuitos experimentado encontrar un circuito familiar, sin importar en qué forma se dibuje. En este artículo, mostramos que los dos circuitos de transistores de las patentes son una variante del disparador de conteo asíncrono (AST). En comparación con el circuito estándar, faltan algunos transistores en las patentes. Esto puede considerarse un mal funcionamiento. Mostraremos que si ocurre la misma falla en el circuito estándar, continúa funcionando correctamente. Un AST implementado solo en elementos OR-NOT [1] o solo en elementos AND-NOT se conoce como activador de Harvard. Ambas variantes de los esquemas se muestran en la Fig. 1, donde g7 es un indicador de finalización transitoria. En el futuro, no lo consideraremos. En la fig. La Figura 1 también muestra los gráficos de transición de señal (STG) [2] integrados en Workcraft [3].

Fig. 1. Gatillo de conteo asíncrono (AST) y su STG.

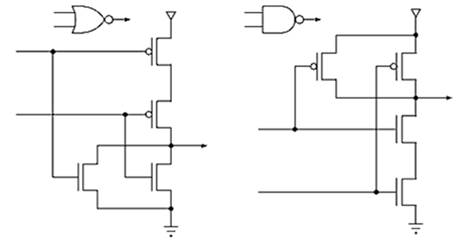

Tenga en cuenta que en ambas versiones del AST hay tres pares de elementos (g1, g2), (g4, g5) y (g3, g6) que tienen una entrada común. Los circuitos de transistores de los elementos 2I-NOT y 2OR-NOT se muestran en la Fig. 2. Los elementos de tres entradas están dispuestos de manera similar y contienen 6 transistores.

Fig. 2. Circuitos de transistores de los elementos 2I-NOT y 2OR-NOT.

Tomamos dos elementos 2OR-NOT y seleccionamos en cada entrada, donde el transistor p-MOS está conectado a Upit. Conecte estas entradas juntas y conéctese a tierra (log. 0). Ambos transistores se abrirán y el voltaje en sus drenajes será igual a Upit. ¿Es esto suficiente para conectar con seguridad los desagües y reemplazar los dos transistores con uno, como se muestra en la Fig. 3? No Debe verificar qué sucede si inicia sesión en la entrada compartida. 1. Las salidas de ambos elementos se conectarán a tierra y tendremos un circuito puente de cuatro transistores p-MOS. Para las dos entradas restantes, tenemos cuatro combinaciones 0 y 1. Es fácil mostrar que en ninguna de ellas hay un cortocircuito entre Upit y tierra.

Fig. 3. Dos elementos 2OR-NOT que comparten una entrada común.

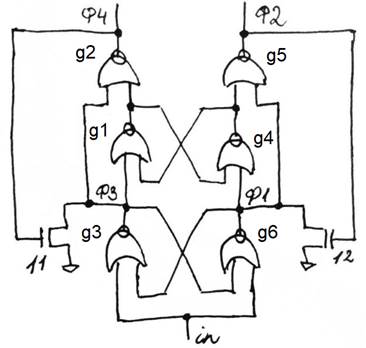

Ahora consideramos el circuito distribuidor de impulsos [4] en la Fig. 4. Usando la Fig. 3, podemos volver a dibujar este diagrama como se muestra en la Fig. 5. Ya es posible reconocer AST en la Fig. 1, sin embargo, allí los elementos g3 y g6 tienen 3 entradas.

Fig. 4. El esquema del distribuidor de pulsos de [4].

Fig. 5. Una variante del circuito en la Fig. 4)

Las puertas de los transistores 11 y 12 pueden considerarse como entradas de elementos 3OR-NOT en los que el tercer transistor p-MOS está en cortocircuito. ¿Esto afecta el correcto funcionamiento del circuito? Considere el orden de aparición de las señales en, g2 y g6 en la entrada del elemento g3. Para hacer esto, elimine todas las otras señales en el STG correspondiente en la Fig. 1 como se muestra en la Fig. 6)

Fig. 6. STG para O NO. Señales, g2, g6 y g3.

Dado que el tercer transistor p-MOS está en cortocircuito, la conmutación g3 + puede ocurrir después de conmutar in y g6- (en cualquier orden) sin permitir la conmutación de g2-. Sin embargo, como se puede ver en la Fig. 6, en la sección de g2 + a g2- solo hay in y g6 +, por lo tanto, el cambio prohibido g3 + no ocurre. Antes de cambiar g2 +, el elemento g3 ya está en 0, y en su entrada g6 sigue siendo 0, es decir El primer transistor p-mos está abierto. El cambio de g2 + abre el transistor 11 y debería apagar el transistor p-MOS en corto. Esto no sucede, además, la conmutación abre el segundo transistor p-MOS. Por lo tanto, a través de dos transistores p-MOS abiertos y un transistor abierto 11, la corriente comienza a fluir desde Upit a tierra. Esto continúa por un corto tiempo hasta que el próximo interruptor g6 + cierre el primer transistor p-MOS. Durante este tiempo, el transistor 11 proporciona 0 en la salida de g3. Como exactamente Suponga que las resistencias de los transistores abiertos p-MOS y n-MOS son iguales e iguales a R, luego de cambiar el voltaje en g3 salta de 0 a (1/3) Upit, pero este es el caso ideal. En la práctica, hay una capacitancia parásita entre g3 y la tierra, cuyo voltaje aumenta suavemente y puede no alcanzar (1/3) Upit. De una forma u otra, este voltaje será inferior a (1/2) Upit y significa un registro. 0. Para el transistor 12, todo es similar, proporciona un corto tiempo 0 a la salida de g6. Por lo tanto, los retrasos de los elementos g6 y g3 determinan dos períodos de tiempo cuando el disparador consume una gran corriente de aproximadamente igual a Upit / (3R).

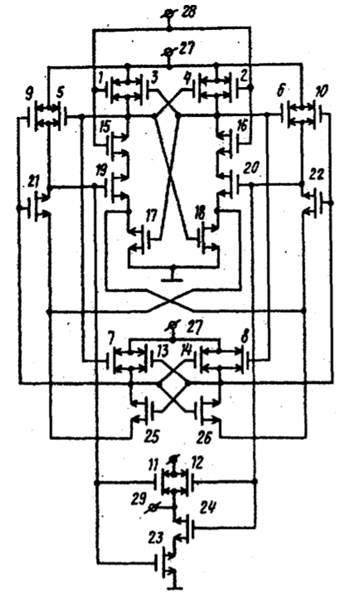

Consideremos ahora el circuito disparador de conteo [5] en la Fig. 7. Aquí los transistores 11, 12, 24, 23 forman el elemento 2I-NOT, que, aparentemente, es un indicador de AST en la Fig. 1. Otro elemento 2I-NOT está formado por los transistores 7, 13, 25 y 18. Prestemos atención al hecho de que el transistor 18 está conectado a tierra y de manera similar al ejemplo de la Fig. 3, es común a los tres elementos Y NO. El segundo elemento 2I-NOT, que incluye el transistor 18, está formado por los transistores 5, 9, 21, y el tercero es 3I-NOT en los transistores 2, 4, 16, 20. En paralelo con los transistores 2 y 4, debe haber un tercer transistor p-MOS Pero él está ausente. El circuito en la Fig. 7 es simétrico, para una mejor comprensión, lo volvemos a dibujar como se muestra en la Fig. 8)

Fig. 7. Esquema del activador contable de [5].

Fig. 8. Una variante del circuito en la Fig. 7)

¿Habrá salidas g3 y g6 en la Fig. 8 ¿cambia correctamente si falta el tercer transistor p-mos en paralelo? Esto se entenderá después de analizar el STG en la Fig. 9, que, como en el caso anterior, se obtiene del STG correspondiente en la Fig. 1 eliminando todas las señales excepto en g2, g6 y g3.

Fig. 9. STG para NAND. Señales, g2, g6 y g3.

El elemento g3 es 3I-NOT, por lo que después de cambiar +, g6 + y g2 + (en cualquier orden), g3- cambiará. Cualquiera de las conmutaciones inversas in, g6- o g2- debería provocar la conmutación g3 +. Sin embargo, g2- no puede abrir el transistor p-MOS faltante, por lo que g3 permanecerá en 0 y esperará a que cambie in o g6-. Como se puede ver en la Fig. 9, en la sección de g3- a g3 + no hay conmutación g2- y aquí no se necesita el transistor p-MOS. Por otro lado, este transistor debería proporcionar un registro. 1 a g3 cuando está dentro y g6 cambian arbitrariamente. Considere en la Fig. Novena sección de g3 + a g2 +. El cambio de g2- cierra el transistor 19. A continuación, el cambio + cierra el transistor 1 y abre el transistor 15. El elemento g6 permanece en 1, es decir. el transistor 17 está abierto y el transistor 3 está cerrado. Por lo tanto, en + desconecta g3 tanto de la tierra como de Upit. Sin embargo, el registro se mantiene en g3. 1, ya que en la práctica hay una capacitancia parásita entre g3 y tierra, que se carga hasta Upit. Conmutar g6- abre el transistor 3 y conecta esta capacitancia a Upit. Para la segunda mitad del esquema, todo es similar. Por lo tanto, los retrasos de los elementos g6 y g3 determinan el tiempo durante el cual el estado se almacena en el tanque. En la práctica, es importante que la corriente de fuga de los transistores 19 y 20 sea pequeña, de lo contrario, la capacitancia puede descargarse por debajo de (1/2) Upit en el tiempo asignado.

En comparación con el AST estándar en la Fig. 1, en los diagramas de la Fig. 5 y en la Fig. 8, la función de configuración en 1 elemento 3 O NO y la función de reinicio en 0 del elemento 3 O NO está dañada. Esto significa que el AST estándar continuará funcionando correctamente, incluso si se produce un mal funcionamiento correspondiente en los elementos g6 y g3. Para un circuito estándar (sin g7), se necesitan 28 transistores. Para los circuitos de la Fig. 4 y en la Fig. 7 (sin los transistores 11, 12, 24, 23) necesita 23 y 22 transistores, respectivamente. Si devuelve los transistores p-MOS que faltan, estos circuitos funcionarán de manera más confiable. El número mínimo de transistores en el circuito en la Fig. 7 no significa necesariamente que sea mejor que el circuito de la Fig. 4 y mejor circuito en la Fig. 1. Además del número de transistores y el consumo de corriente, existen otros parámetros importantes, por ejemplo,

- complejidad de un circuito adicional para establecer estados iniciales

- capacidad de carga (tasa de recarga de la capacidad de carga)

- tasa de salida del estado metaestable

- número y valores de capacitancias parásitas

- número y valores de corrientes de fuga

Un análisis comparativo de estos parámetros, así como una discusión de los esquemas AST implementados en otros elementos, está más allá del alcance de este artículo.

Literatura

[1] GT Osborne, "Etapa de registro de contador binario asincrónico con flip-flop y puerta que utiliza una pluralidad de circuitos NOR interconectados". Patente US3139540, 30 de junio. 1964.

[2] L. Ya. Rosenblum y A. V. Yakovlev, "Sobre una nueva forma gráfica para ilustrar la esencia de la invención", Issues of Invention, No. 11, pp. 36-40, 1988.

[3] https://workcraft.org

[4] V. I. Goryachev, B. M. Mansurov, Ya. D. Martynenko y R. G. Talibov, "Distribuidor de pulsos de cuatro fases". Certificado de copyright SU342299, 14/06/1972.

[5] V. I. Varshavsky, N. M. Kravchenko, V. B. Marakhovsky y B. S. Tsirlin, "Gatillo contador en transistores CMOS". Certificado de copyright SU1398069, 23/05/1988.