En condiciones modernas, el ingeniero de diseño necesita adquirir constantemente nuevos conocimientos para tener demanda en el mercado laboral. A menudo, se debe recibir nueva información, por así decirlo, "sin interrupción de la producción": durante el trabajo en un proyecto, en viajes al trabajo, etc. El mundo digital moderno lo permite, sería un deseo. Sin embargo, a veces la calidad del conocimiento adquirido puede sufrir. La información es asimilada por una persona superficialmente o incluso de forma distorsionada.

Al comunicarme con los rastreadores de software que trabajan en el software CAD para las placas de circuitos impresos Cadence OrCAD / Allegro, a veces noté que las personas no otorgan mucha importancia a la indicación de color de los campos en el editor de reglas del Administrador de restricciones. A saber: los usuarios no prestan atención al hecho de que algunas columnas están pintadas en amarillo.

De hecho, el color amarillo en el editor de reglas de Cadencia significa que esta verificación no se puede realizar por ningún motivo. Las razones pueden ser diferentes:

- Validación deshabilitada por el usuario.

- El camino conductivo no está establecido o no está completo.

- Otras razones

En la mayoría de los casos, no hay situaciones fatales en las que aparezcan errores que conduzcan a la inoperancia del software. Dado que OrCAD PCB Editor tiene un mecanismo de etapas múltiples para verificar el proyecto en DRC, así como así, no puede desactivarlos de una vez. Sin embargo, a veces debido a una brecha de conocimiento molesta, o por falta de atención, se crean situaciones que conducen a situaciones incorrectas en el proyecto.

Por ejemplo, un desarrollador me contó cómo accidentalmente apagó la comprobación de cortocircuito entre líneas opuestas entre sí. Además, el software CAD no informará un error en esta situación, ya que el usuario deshabilita la verificación.

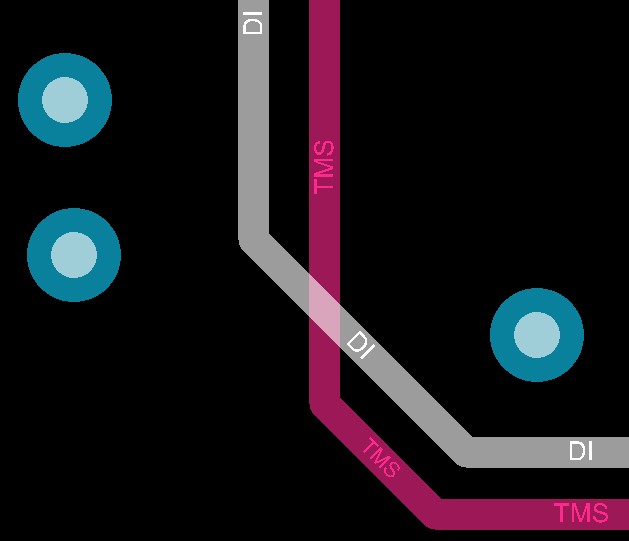

Intersección de un conductor por otro sin mensaje de error

Intersección de un conductor por otro sin mensaje de errorLa figura muestra que los conductores de líneas opuestas se cruzan entre sí. Sin embargo, no se produce un mensaje de error. El desarrollador no tiene claro el motivo de este comportamiento del programa, ya que durante el seguimiento en línea se guardan y mantienen todos los huecos establecidos en el administrador constante.

Las lagunas y reglas en las regiones son compatibles al rastrear

Las lagunas y reglas en las regiones son compatibles al rastrearLa falta de un token DRC radica precisamente en la configuración del Administrador de restricciones.

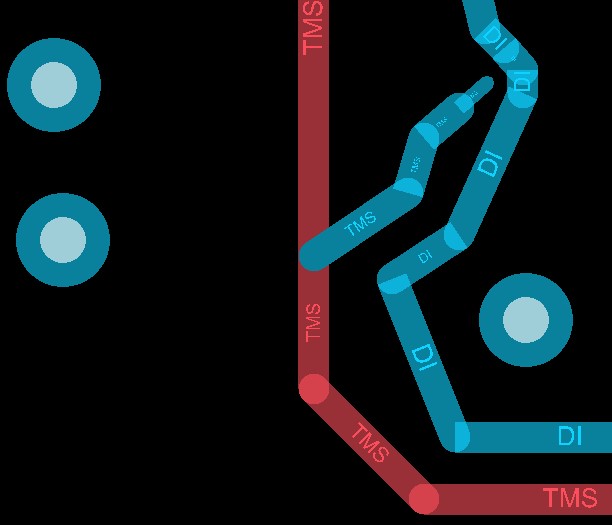

Así es como se ve la verificación deshabilitada en el Administrador de restricciones

Así es como se ve la verificación deshabilitada en el Administrador de restriccionesUn color amarillo en la sección de verificación de espacio de línea a línea significa que la verificación no se realiza (o no se puede realizar). Debido a esto, el marcador DRC no se produce. Por supuesto, la inhabilitación parcial de los controles a veces es muy conveniente y puede reducir el tiempo total para verificar un proyecto, pero ... Esto puede tener consecuencias fatales si, al enviar un proyecto y generar archivos para producción, el desarrollador no incluye todas las verificaciones necesarias y no realiza una verificación final de DRC con ellos.

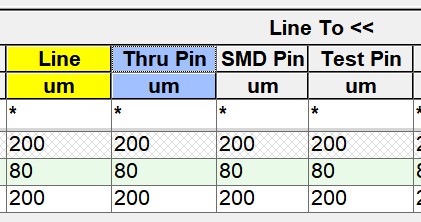

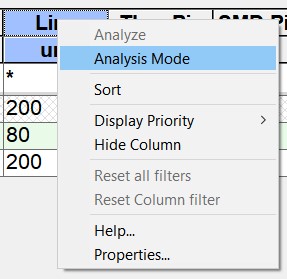

Deshabilitar o habilitar una verificación particular en Cadence es muy simple: simplemente haga clic en el encabezado de la celda de interés y seleccione Modo de análisis en el menú desplegable.

Activar o desactivar rápidamente ciertos tipos de comprobaciones

Activar o desactivar rápidamente ciertos tipos de comprobacionesCuando el cheque está activado, el color del gorro es gris; cuando el cheque está deshabilitado, el color del gorro es amarillo.

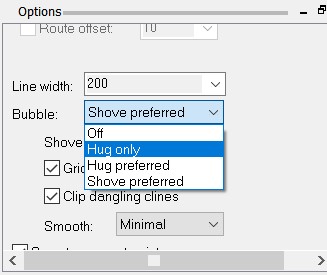

¿Por qué, cuando la comprobación está deshabilitada en el Administrador de restricciones, las lagunas necesarias aún son compatibles durante el seguimiento, y OrCAD PCB Designer evita que el usuario cometa un error accidentalmente? Esto se debe al hecho de que el sistema de verificación de DRC consta de dos partes: las comprobaciones en línea de DRC en tiempo real y las comprobaciones bajo demanda de DRC en modo Batch. El modo Batch DRC simplemente se apaga a la fuerza en el Administrador de restricciones. El DRC en línea continúa funcionando si en el modo de rastreo el valor del parámetro Bubble en la ventana Opciones es diferente del estado OFF.

Posibles valores que puede tomar el parámetro Bubble

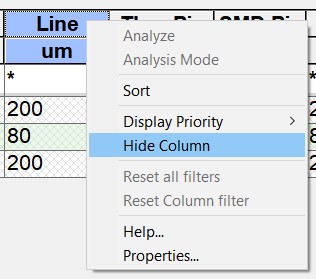

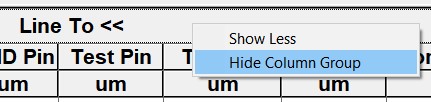

Posibles valores que puede tomar el parámetro BubbleSi un ingeniero no quiere ver las comprobaciones deshabilitadas o algunas secciones en el editor de reglas del Administrador de restricciones, se pueden ocultar fácilmente.

Ocultar una columna o sección de consideración

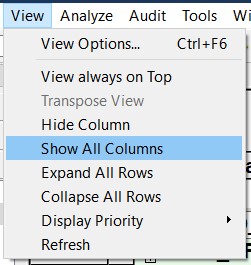

Ocultar una columna o sección de consideraciónCuando la verificación se vuelve necesaria nuevamente, puede devolverse en el campo de las columnas mostradas.

Devolver columnas ocultas

Devolver columnas ocultasVale la pena señalar que el editor de tablas de las reglas de CAD Cadence Allegro / OrCAD, con toda su potencia, es muy conveniente y fácil de configurar, y las comprobaciones en sí mismas se realizan con bastante rapidez, por lo que a menudo no es necesario forzar que algo se apague.

Por otro lado, si fue necesario deshabilitar algunas comprobaciones especialmente lentas, el desarrollador primero puede guardar el archivo "tecnológico" que contiene la configuración para todas las comprobaciones necesarias, luego deshabilitarlas temporalmente, y al emitir la documentación de diseño después de completar el seguimiento, vuelva a cargar ese archivo tecnológico con todos los controles y ejecutar el DRC final.

Sí, por cierto, si recuerda al desarrollador que apagó la prueba de cortocircuito entre los circuitos, afortunadamente, el fabricante de PCB cuando comenzó el pedido llamó su atención sobre el problema del circuito entre los circuitos, de modo que lograron evitar pérdidas financieras y de tiempo. Pero, por experiencia en una empresa que se dedicaba a la fabricación de placas de circuito impreso, puedo decir que el problema de deshabilitar las verificaciones "innecesarias" se encontró con mucha frecuencia, por la mayoría de los clientes, y no dependía de qué desarrolladores de CAD trabajaran. ¡Así que no olvide incluirlos en el momento adecuado!