Esta semana, Intel compartió sus planes a largo plazo para la introducción de nuevos procesos de fabricación. Alrededor de 2029, Intel

tiene la intención de introducir una tecnología de proceso con estándares de 1.4 nm. Después de 10 años, es poco probable que el equipo directivo de la compañía sea el mismo que hoy. Por lo tanto, estos planes recuerdan sutilmente la parábola de Khoja Nasreddin sobre el bien leído burro, khan y maestro del animal en la persona del propio Khoja. Al mediodía, el acusado puede no estar allí. Pero esto no se trata de eso. Planificado, luego aceptamos como guía de acción.

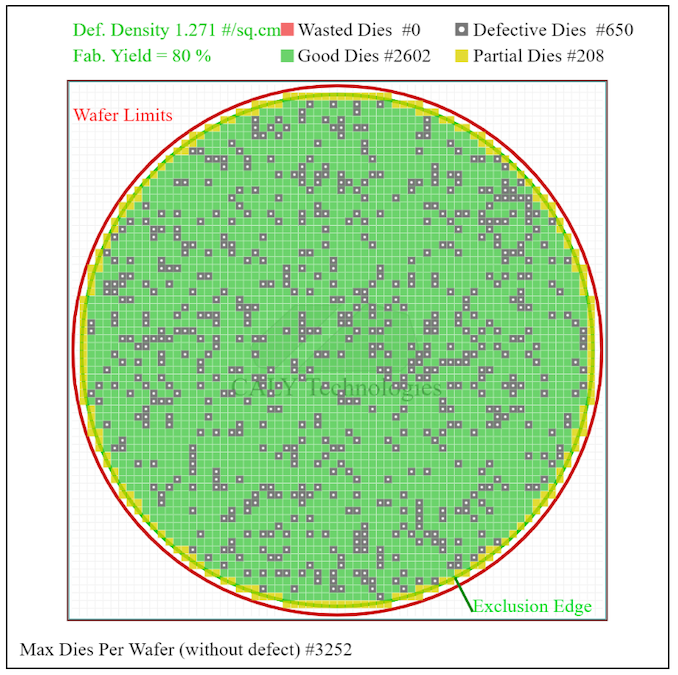

En los campos de los principales rivales de semiconductores, hay un poco más de claridad, lo que se confirma por la producción arriesgada de chips TSMC con estándares de 5 nm (

hoy la tasa de defectos es solo del 20% a la norma del 3-8% para cristales con un área de 17.92 mm

2 , para los chiplets AMD Zen 2 tendrá un mayor nivel de rechazo, hasta un 60%). Sin embargo, antes del lanzamiento de los procesadores AMD con estándares de 5 nm, pasará al menos otro año y medio.

/ imagen del sitio web de AnandTech

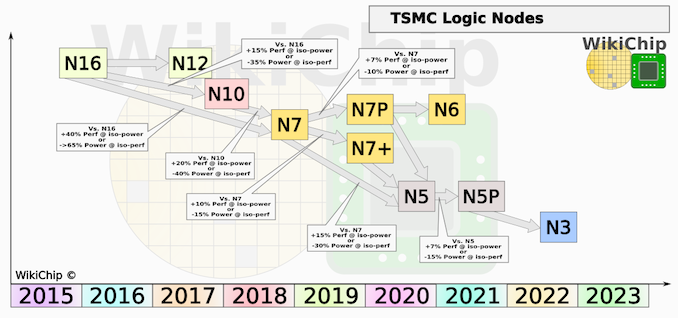

/ imagen del sitio web de AnandTechEl próximo año, a partir del segundo trimestre, la tecnología de proceso TSMC con estándares de 5 nm se utilizará para la producción en serie de SoC en núcleos ARM. Obviamente, en 2022, TSMC comenzará la producción arriesgada de chips de 3 nm (lo que sea que signifiquen estos nanómetros), y en un par de años, la compañía promete comenzar la producción de soluciones de 2 nm. Será en 2024-2025, o dos o tres años antes de que Intel presente la misma tecnología de proceso.

Para Samsung, los procesos con estándares de 5 nm y 4 nm serán la

evolución de la tecnología de proceso de 7 nm, que se expresará en una pequeña reducción gradual en los pasos de metalización bajo elementos FinFET como canales y compuertas. En general, la estructura de los transistores (el número de bordes) seguirá siendo la misma, ya que la estructura de la celda SRAM no cambiará. Samsung comenzará la producción de chips utilizando la tecnología de proceso de 4 nm en el área de 2021. En el mismo año, la compañía promete comenzar una producción arriesgada utilizando una tecnología de proceso de 3 nm. Y algunas fuentes de Corea del Sur

afirman que esto podría suceder tan pronto como 2020, lo que parece poco probable.

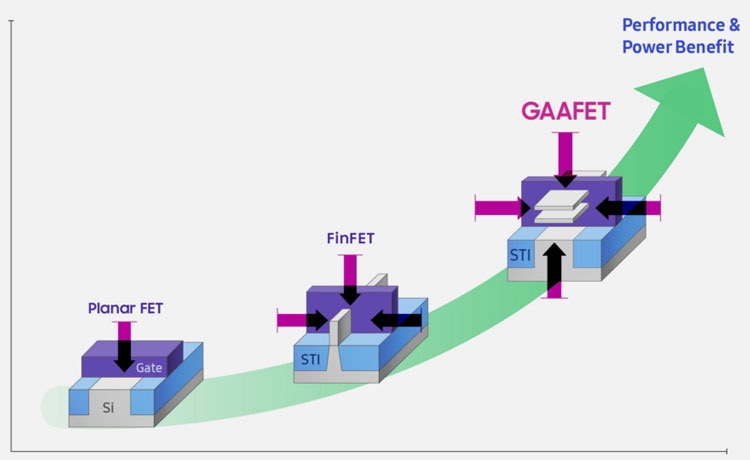

En este artículo, estamos interesados en el hecho de que, hasta la tecnología de proceso de 4 nm, Samsung y, obviamente, Intel y TSMC utilizarán transistores FinFET, aletas de puertas altas, en las que las crestas de los canales verticales cortan y atraviesan. En tales transistores, el campo electromagnético de la puerta penetra en los canales desde tres lados, y dos o tres canales en cada transistor en total proporcionan la corriente necesaria para que la válvula funcione.

/ Imagen de Samsung

/ Imagen de SamsungComenzando con la tecnología de proceso de 3nm, Samsung romperá esta práctica. El concepto FinFET dejará de funcionar como antes. Las puertas del transistor FinFET serán demasiado pequeñas y no podrán cambiar los transistores. La necesidad de reducir aún más la tensión de alimentación de los transistores solo agravará esta situación. Por lo tanto, para la tecnología de proceso de 3 nm, se

introducirá un transistor con una puerta de anillo GAA (Gate-All-Around) (envolvente).

/ Imagen de Samsung

/ Imagen de SamsungSamsung le dio al nuevo transistor el nombre comercial MBCFET (Multi Bridge Channel FET). En la práctica, este es el desarrollo de la idea de un transistor,

creado conjuntamente por investigadores de IBM, Samsung y GlobalFoundries. Se supuso que un transistor de estructura similar estaría involucrado en la transición a una tecnología de proceso con estándares de 5 nm. Pero en realidad, esta estructura de válvula aparecerá en los chips solo con el comienzo de la producción de 3 nm de Samsung. El transistor MBCFET consistirá en canales dispuestos horizontalmente uno encima del otro en forma de nano páginas, en lugar de crestas verticales, como en FinFET. Las características de los transistores MBCFET se controlarán convenientemente variando el número de páginas ubicadas una encima de la otra y cambiando el ancho de la página. Cada página es un canal. La suma de estas variables determinará qué transistor tenemos: potente y rápido, o débil, pero de baja potencia. Habrá más de dos gradaciones, de cinco a siete.

/ Imagen de Samsung

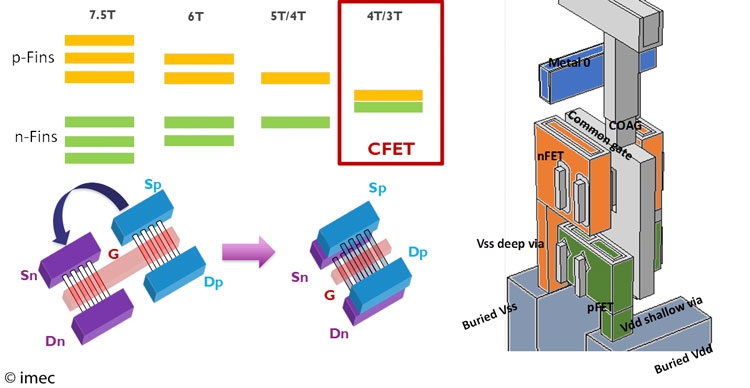

/ Imagen de SamsungLo más interesante, en aras de la cual se concibió esta nota, es que el transistor MBCFET solo puede aparecer dentro del marco de la tecnología de proceso de 3 nm, y la tecnología de proceso con estándares de 2 nm requerirá nuevamente cambios en la estructura del transistor. Este nuevo transistor bajo el nombre de Forksheet fue propuesto por el centro de investigación belga Imec. Por primera vez, los representantes de Imec

hablaron en detalle sobre la estructura de un transistor con páginas separadas (nano) esta primavera en un evento anual. Pero no puedes alimentar al ruiseñor con fábulas. Lo sentiríamos Todavía no lo puede sentir, pero los belgas realizaron una simulación del transistor Forksheet en TCAD, que se

informó hace tres días.

Antes de considerar los datos, explicamos que el transistor Forksheet es una modificación del transistor con nano páginas, ese mismo MBCFET o Gate-All-Around, si ignoramos los términos Samsung. La aleta del obturador vertical en el transistor de la hoja de horquilla es ligeramente más ancha que la del MBCFET, pero las nanopáginas de los canales del transistor están divididas en dos y separadas por una capa dieléctrica. De hecho, un transistor MBCFET con un movimiento de la muñeca se convierte en un par de transistores complementarios de transistores de tipo p y n.

La estructura propuesta destruye una barrera seria en el sellado de los transistores en forma de complejidad para acercar los transistores p y n lo más posible y al mismo tiempo evitar la influencia negativa mutua de las compuertas.

Obviamente, el enfoque propuesto aumentará la densidad de los transistores en el chip, pero el modelado ha demostrado que el rendimiento y el consumo de energía también mejorarán. Cambiar a un transistor con páginas separadas reducirá el área de cristal hasta en un 20%, y al reducir las capacidades espurias y las fugas, el rendimiento de los dispositivos electrónicos aumentará hasta en un 10%. Si no aumenta la frecuencia, puede reducir el consumo de energía hasta en un 24%.

En stock, Imec tiene otra

tecnología que puede aumentar aún más la densidad de los transistores. Se puede aplicar tanto en la etapa de producción de chips de 3 nm como con estándares de producción más bajos. La idea es hacer un par de transistores complementarios uno encima del otro. Esta operación aparentemente simple promete reducir el tamaño de la celda lógica estándar y la celda SRAM en un 50%. Las ideas bien desarrolladas y parcialmente probadas en modelos terminan aquí.

Cambiar a una tecnología de proceso de 1 nm también puede requerir una nueva estructura de transistor. Al mismo tiempo, debe recordarse que los ingenieros a menudo encuentran posible estirar su placer: idear algo así para dar un paso más con las muletas viejas.