El 10 de julio de 1962, el cohete Tor con el primer satélite comercial de telecomunicaciones a bordo lanzado desde el sitio de lanzamiento en Cabo Cañaveral. Telstar-1 fue el comienzo de una nueva era de la astronáutica, que mostró que el espacio puede aportar beneficios reales a las personas. Este dispositivo estaba esperando un gran futuro, pero un día antes en el cielo sobre el atolón Johnson, ubicado en la parte desértica del Océano Pacífico, explotó la bomba atómica Starfish Prime. La explosión destruyó trescientas farolas en Hawai, ubicadas a mil quinientos kilómetros, y también creó una gran cantidad de electrones libres, recogidos por el campo magnético de la Tierra en el cinturón de radiación artificial. Cada vez que Telsat-1 pasaba por este cinturón, un transistor avanzado llenaba una dosis de radiación y, en noviembre de 1962, había dejado de funcionar. La historia de la protección de la electrónica espacial contra la radiación comenzó con un estudio de las consecuencias de este incidente.

Afortunadamente, comenzaron a participar en explosiones nucleares a gran altitud con bastante rapidez, pero incluso sin ellas hay suficiente trabajo, y los requisitos de confiabilidad y durabilidad presentados a los satélites modernos son cada vez más ambiciosos. Es imposible hablar de todo, pero intentaré cubrir brevemente el pasado y el presente de los microprocesadores espaciales de diferentes países. ¿Por qué exactamente microprocesadores? La mayoría de ellos son información sobre ellos y los no especialistas los entienden mejor. El artículo resultó ser largo, así que lo dividí en dos partes: una historia temprana sobre el ejemplo de Estados Unidos y Europa (bajo el corte) y moderna, sobre el ejemplo de Rusia (

aquí ). Vamos!

Reglas del juego

Comencemos con los términos y definiciones. Por "microprocesador" me refiero a un microcircuito o un conjunto de microcircuitos de alto grado de integración, diseñados para ejecutar programas. El primer microprocesador popular de un solo chip fue el Intel 4004 de cuatro bits, lanzado en 1971, esto es después de que los estadounidenses aterrizaran en la luna, por lo que con esta definición, las computadoras de a bordo de la era de la exploración espacial heroica quedan fuera de escena, dejándonos solo aburridos "caballos de batalla". Sin embargo, se ha escrito mucho sobre las computadoras a bordo de la era heroica, incluso en Habré.

Aquí ,

aquí y

allá . Ellos, por regla general, fueron diseñados para una misión específica, tenían algún tipo de sistema de comando y una profundidad de bits de 13 bits, luego 17, luego 21, en general, no intenten repetirlo en casa. La unificación comenzó con recortes presupuestarios después del final de la carrera lunar y con el despliegue simultáneo de varias constelaciones de satélites. Como resultado, casi todas las partes interesadas llegaron a un número limitado de chips universales utilizados en cualquier lugar.

El segundo punto importante es la disponibilidad de información. La industria espacial nunca ha sido particularmente abierta. El primer satélite, el acceso del astronauta a la luna o la cantidad de satélites en la constelación GLONASS es un anuncio simple y comprensible, pero es difícil alardear de las características del diseño del transmisor de radio en Sputnik-3. Agregue el secreto tradicional cercano a la guerra desde arriba, y sabemos sobre el procesador RAD750 que "hay más de 150 de ellos", y solo una docena de satélites en los que se encuentra. Una cita típica de publicaciones científicas especializadas escritas en los años setenta se ve así:

“También se ha construido y probado un registro de desplazamiento PMOS / SOS resistente a la radiación de 32 bits; sin embargo, los datos de prueba en este circuito están clasificados ”. Acerca de los datos abiertos en satélites y microcircuitos rusos (y yo, por supuesto, solo uso datos abiertos), ni siquiera quiero comenzar; Las migajas existentes generalmente van a Internet por supervisión. Las publicaciones científicas nos ahorran un poco, especialmente si sabe lo que está buscando. La base de datos en línea de IEEE es simplemente un almacén para el historiador de la electrónica; Con los archivos de las revistas y conferencias científicas soviéticas y rusas, la situación es radicalmente peor que con los extranjeros, pero tampoco desesperada. La desventaja de las publicaciones es que a través de ellas es difícil rastrear la conexión entre los microcircuitos y su aplicación, pero se puede encontrar información interesante sobre el diseño de los microcircuitos. Total: el artículo no pretende ser completo, es más bien una colección de ejemplos mediante los cuales se puede seguir el desarrollo y presentar el estado actual de los microprocesadores y microcontroladores para aplicaciones espaciales.

La tercera cosa para acordar es que no compararé el rendimiento del procesador del móvil con un iPhone. Hay algo de diversión en esto, pero la diferencia en el rendimiento no proviene de una buena vida, tiene razones objetivas: un largo ciclo de desarrollo, otros requisitos de confiabilidad, una larga certificación y pruebas de todo, desde la tecnología de fabricación de chips hasta el ensamblaje satelital. Por supuesto, los desarrolladores espaciales siempre quieren obtener la máxima potencia informática (procesar información a bordo, ahorrando el ancho de banda del canal de radio), pero a menudo otras prioridades son más importantes. Es por eso que pueden pasar diez años desde la finalización del desarrollo hasta el primer vuelo, y por lo tanto, a todos les encantan las soluciones que ya han volado: hay mucho menos problemas con ellas. Como resultado, la vida útil de los microcircuitos espaciales puede ser de treinta a cuarenta años, el desarrollo de una nueva generación puede comenzar incluso antes del primer vuelo del anterior, y en este momento los procesadores desarrollados en la década de los noventa todavía están en marcha. Notaré de inmediato que el diseño de naves espaciales se está volviendo cada vez más complicado, y ahora puede haber docenas de computadoras a bordo que tienen requisitos muy diferentes: debe procesar matrices de imágenes durante todo el día y sondear un par de sensores una vez por hora.

Cuarto, un recordatorio muy breve de los efectos de la radiación del espacio exterior. Un recordatorio de longitud media

está aquí , pero muy largo,

aquí .

Los efectos de una dosis completa de radiación están asociados con la acumulación de carga eléctrica en dieléctricos y en la interfaz entre un dieléctrico y un semiconductor; Estamos principalmente interesados en el óxido de puerta y el aislamiento lateral de los transistores MOS. Estos efectos se manifiestan como un cambio en el voltaje de umbral de los transistores (para canales p, un aumento en el valor absoluto, para los canales n generalmente disminuye, pero luego verá matices), una disminución en la movilidad de los portadores de carga (disminución en la velocidad del circuito) y fugas en los transistores de canal n ( tanto entre el drenaje y la fuente de un transistor, como entre diferentes transistores), lo que lleva a un aumento en el consumo de energía estática.

Los efectos individuales se deben al hecho de que cuando una sola partícula cargada ingresa al transistor, parte de la energía de esta partícula se transfiere al material del microcircuito, y se forman pares de electrones libres. Algunos de estos pares están separados en el microcircuito por un campo eléctrico, y "ve" un pulso de corriente corto, "traído" por una partícula externa. Además, este pulso actual puede cambiar el valor registrado en la celda de memoria, ir a la entrada del elemento lógico o hacer algo catastrófico, por ejemplo, romper la puerta del transistor o abrir la estructura del tiristor parásito y crear una falla a tierra local con energía.

Los efectos del desplazamiento se deben al hecho de que una partícula entrante no solo puede crear pares de electrones, sino que también interactúa directamente con los átomos de una sustancia, sacándolos de las posiciones correctas en la red cristalina. Para los transistores ordinarios, tales defectos locales no son terribles, pero conducen a daños significativos en dispositivos optoelectrónicos, semiconductores bidimensionales y transistores a nanoescala.

Todavía hay

efectos de la tasa de dosis , pero en su mayoría tienen aplicaciones no comerciales, por lo que no hablaré de ellos.

La etapa inicial: el ejemplo de los Estados Unidos

El hecho de que no pude descubrir de manera confiable qué microprocesador fue el primero a bordo de la nave espacial fue bastante predecible. Los datos públicos solo están disponibles en misiones científicas bien conocidas y, por lo general, se utilizan en los más confiables y verificados, es decir, silenciosamente elaborados por adelantado en satélites menos costosos. Se sabe que las computadoras de a bordo Viking y Voyager se ensamblaron en lógica discreta, pero fue en ellas que comenzaron la estandarización y la reutilización de componentes. Voyager es interesante porque fue el primer dispositivo en usar memoria de semiconductores en lugar de núcleos magnéticos. Además, era una SRAM CMOS volátil, es decir, la información que contiene se borra si se pierde la energía. ¿Cómo lograron los ingenieros convencer a la gerencia para que corriera tal riesgo? Primero, sin una nueva memoria, no tendría sentido aplicar una lógica CMOS rápida. En el espacio, la tecnología CMOS era más que oportuna: a pesar del hecho de que los circuitos CMOS eran más lentos que sus homólogos bipolares y mucho más sensibles a la descarga electrostática, toleraban temperaturas extremas, tenían baja sensibilidad al ruido y consumían radicalmente menos energía, que generalmente está a bordo. Había una escasez. En segundo lugar, como respaldo de la fuente de alimentación, el voltaje de la salida RTG se llevó directamente a la memoria, razonando razonablemente que si algo le sucede al generador, los problemas de memoria ya no serán relevantes.

Figura 1. Placa con una memoria de semiconductores con Voyager.

El primero - RCA 1802

La primera nave espacial que encontré en la que no había microcircuitos de grado medio de integración, sino un microprocesador monolítico (RCA 1802 de 8 bits) es el satélite Magsat lanzado el 30 de octubre de 1979. Dado que los primeros RCA 1802 comerciales se lanzaron en 1975, esto debería significar que llegaron a la NASA antes que los estantes de las tiendas, lo que, en general, era una práctica normal en los primeros días de Silicon Valley.

Como un pequeño ejemplo de esa época, citaré un artículo de EE King, "Efectos de la dosis total en el microprocesador 1802", IEEE Transactions on Nuclear Science, 1977. El artículo compara el efecto de la dosis de radiación en cuatro variantes de 1802: dos comerciales, una muestra experimental producida en un sustrato de silicio sobre zafiro (SPS) y una muestra producida por un proceso especial diseñado para aumentar la resistencia a la radiación.

Figura 2. Desplazamiento del voltaje umbral de ambos tipos de transistores bajo la influencia de la dosis de radiación. C1 y C2 son chips comerciales, S es un chip en el SPS, X es una muestra especial.

De la figura se puede ver que tanto las muestras comerciales como el chip KNS a dosis de radiación bastante pequeñas (8-15 crad (Si)), el umbral de los transistores de canal n se vuelve inferior a cero y los circuitos lógicos simplemente dejan de cambiar. Al mismo tiempo, un proceso técnico especial permitió alcanzar una resistencia de más de 1 Mrad (Si), es decir, dos órdenes de magnitud más. Una vez más, observo que el año es solo 1977, y ya se han desarrollado y producido chips especiales. Sin embargo, el RCA 1802 descrito fue probablemente el primer signo, porque en los recuerdos de los participantes en el desarrollo del próximo gran dispositivo de la NASA, Galileo, encontré una historia de que en el momento de elegir la arquitectura electrónica de control en 1977, 1802 era el único microprocesador monolítico resistente a radiantes asequible.

Es importante tener en cuenta que ya trataron de usar los chips más comunes en el espacio, y continúan haciéndolo con éxito ahora. Para muchas aplicaciones, no se necesita confiabilidad extrema, ni alta resistencia a la radiación, ni la ausencia total de fallas; solo la ausencia de fallas en un período de tiempo razonable es importante, y muchos chips comerciales cumplen con este requisito, a la vez que son varios órdenes de magnitud más baratos que su diseño especial. hermanos Para una constelación satelital de varios cientos de dispositivos en órbita baja, incluso la presencia de fallas poco frecuentes no es crítica, en contraste con el costo. Y solo donde la seguridad del país depende del funcionamiento de los microcircuitos, la vida de los astronautas, o al menos el destino de una misión científica de varios millones de años, es imposible sin chips resistentes a la radiación. Existen, por supuesto, enfoques mixtos, cuando los sistemas más críticos se ejecutan en chips resistentes a la radiación, y el resto son convencionales, y también conocidos como troqueles, cuando el fabricante toma los mismos cristales que se usan en productos caros resistentes a la radiación, los empaca en cajas de plástico baratas y no realiza pruebas de extremo a extremo, ahorrando en el precio varias veces. Hay compañías que se dedican específicamente a probar chips comerciales para encontrar entre ellos aquellos que accidentalmente resultaron ser resistentes a la radiación. Pero volvamos a Galileo y 1802.

Figura 3. Lanzamiento de Galileo con el transbordador espacial. Las computadoras de a bordo del transbordador, creadas en los años setenta, funcionaron en microcircuitos de un pequeño grado de integración, y solo durante una gran actualización, realizada ya en la dos milésima, se subieron a bordo el resistente al radiante 386-e, 1802-e y civil PowerPC 750.

Galileo, debido a varios problemas, voló solo en 1989, pero fue diseñado casi inmediatamente después de los Voyagers y utilizando sus mejores prácticas. "A 1802 a nadie en el equipo de desarrollo realmente le gustó", porque las soluciones discretas, aunque más engorrosas, eran mucho más rápidas. Como resultado, sus ventajas todavía eran mayores que las desventajas, y el subsistema de comando y datos del dispositivo (Subsistema de Comando y Datos) se construyó en 1802, y el subsistema de control de maniobras menos cargado, pero más exigente relacionado con la velocidad (Subsistema de Control de Actitud y Articulación) fue controlado por una computadora de 16 bits ensamblado a partir de chips bipolares de corte de bits de cuatro bits Am2900 (contraparte soviética - serie 1802).

Galileo también es importante para nuestra historia, ya que fue el primer dispositivo en el que se tuvo en cuenta el problema de las fallas individuales en el diseño. En los microcircuitos fabricados de acuerdo con los estándares de diseño, casi no aparecieron, y nadie sabía de su existencia hasta que las sondas de investigación llegaron a los cinturones de radiación de Júpiter. ¡La magnetosfera de Júpiter es tan grande que parte de sus satélites (Europa, Io y Ganímedes) están dentro! Los campos magnéticos de Júpiter aceleran los iones pesados a una energía colosal, cuya fuente es Io volcánicamente activa. Tales condiciones monstruosas resultaron ser suficientes para causar un mal funcionamiento incluso en los antiguos microcircuitos Pioneer, pero cuanto más pequeños son los estándares de diseño, ¡se necesita menos energía para cambiar el bit en la memoria!

Figura 4. Una imagen de radiación alrededor de Júpiter. Fuente: Hans Huybrighs, "La viabilidad de las observaciones in situ de las columnas de vapor de agua de Europa", 2015

En 1977, cuando comenzó el diseño de Galileo, los Voyagers aún no habían llegado a Júpiter, y todos los datos de radiación disponibles se relacionaban solo con los Pioneros. Algunos de sus misteriosos errores se clasificaron posteriormente como fallas individuales, pero esto fue más tarde, y hasta ahora no se han incorporado códigos de autocorrección ni ninguna otra forma de encontrar y corregir errores en el equipo a bordo de Galileo. Después de que se descubriera la causa probable de las fallas en Pioneers and Voyagers (1982), todos los componentes electrónicos de Galileo, seleccionados para ser resistentes a la dosis de radiación, se enviaron urgentemente al acelerador: averigüe cómo van a hacer frente. con un nuevo problema Los resultados fueron decepcionantes: si 1806, realizado con una tecnología relativamente antigua, se comportó normalmente, entonces en el conjunto de microprocesador bipolar progresivo 2901, del 20 al 50% de los impactos de partículas cargadas causaron fallos de funcionamiento, y fue imposible iniciarlo. Que hacer Se encontraron dos opciones:

- Pruebe la última computadora a bordo resistente a la alegría basada en la arquitectura 1750A y vuelva a compilar todo el software después de escribir el compilador. El costo de esta opción se estimó en 20 millones de dólares (los dólares entonces, eran significativamente más caros que los actuales).

- Para ordenar urgentemente el desarrollo de análogos tolerantes a fallas de chips problemáticos 2901. En este caso, no se pudo volver a hacer todo el software probado repetidamente. Sandia Labs estimó el desarrollo de nuevos chips en 5 millones, y se tomó una decisión.

NASA Tech Briefs, Volumen 10, Número 3 da algunos detalles sobre los chips desarrollados por Sandia Labs: no eran bipolares como el original, sino CMOS, había nueve tipos de ellos (de aproximadamente cuarenta chips de la serie original), y se usaron para lograr tolerancia a fallas transistores más anchos de lo necesario, así como resistencias en los circuitos de retroalimentación de los elementos de almacenamiento.

Retiro sobre fallas individualesFigura 5. Esquema de una celda de memoria estática de seis transistores (6T SRAM)

Cuando un SLC ingresa al drenaje de un transistor cerrado, surge un pulso de corriente de ionización, y comienzan dos procesos en la célula: la activación de la retroalimentación positiva y la disipación de carga inducida.

Deje que el golpe ocurra en un transistor cerrado M2, en cuyo drenaje apareció un pulso de corriente como resultado. El transistor M1 en este momento está completamente abierto y tiene una pequeña resistencia, es decir, la corriente TZCh inducida a través de él va al suelo. Sin embargo, la capacitancia del nodo nQ puede ser lo suficientemente pequeña como para cargar a un alto voltaje, lo que conducirá a la conmutación del segundo inversor (M3-M4), que, a su vez, cambiará el primer inversor a través de la retroalimentación. Esta es una falla inducida por la radiación (trastorno de evento único, SEU). La instalación de resistencias en el circuito de retroalimentación le permite ralentizar el proceso de retroalimentación y darle a la carga el tiempo suficiente para resolver.

Diseño SA3000 - Resistente a la radiación 8085

El proceso de desarrollo de microcircuitos resistentes a la radiación en ese momento parecía que podía seguir las publicaciones científicas. Como ejemplo, tomé un artículo de W. Kim et. al., «Radiation-Hard Design Principles Utilized in CMOS 8085 Microprocessor Family», 1983 IEEE Transactions on Nuclear Science. Sandia Labs , SA3000 – Intel 8085 ( SA3001 SA3002 RAM Intel 8155 ROM Intel 8355). , Intel , . , . RHBP , – - , n+- . , – RHBD .

NMOS- , , . 700 (Si) 30 (Si). , . Sandia Labs ( ), -. , -, . , .

.

- n- 2 ( 1 ) p- -0.5 -4 ( -1 ). - , , , , .

- , -4 5 p- , , Sandia Labs , 10 . , , NMOS CMOS , .

- , p- , NAND ( p- ) NOR ( ).

- , . , , . , , , .

( ) , , 10 , , . , 10 5 .

«» : – , – , , – , - . Sandia Labs pin-to-pin 18000 6500, . : , . , , , - .

- , . , - . .

, , JFET , . 1984 , DARPA GaAs MIPS — RCA, McDonnell Douglas CDC-TI. 30 , “ ”. , GaAs- Am2900, 1802 , .

, 1984-1994 GaAs , «» 6500 . , GaAs , 6500 , - (). GaAs – - , . .

RISC-

GaAs RISC-, CISC . , RISC- , . « » – ARM, MIPS, SPARC, POWER – , -, - , -, , – , .

1980 US Air Force Mil-Std-1750A, 16- . , , USAF . , , JOVIAL (Mil-Std-1589) (Mil-Std-1815A). JOVIAL, , ( , , ).

USAF, NASA, ESA . 1750- ( , , , bit-slice 2901 , Galileo) , Cassini . Mil-Std-1750A MA31750 Dynex Plessey - . IT , 1750A USAF 1996 , , 16 32- , . , , 1750 . , Rosetta, 2004 , “”, 2013.

, : «1802+8085» «1750+386», 386 Sandia Labs Intel; 386 , Hubble , Space Shuttle. - MIPS-, Mongoose-V, New Horizons, - RAD, POWER. Phoenix, Opportunity, Spirit Curiosity, Spitzer Kepler – , NASA . – RAD5500 – 2016 . – HPSC (High Performance Spaceflight Computing), Boeing ARM-, NASA USAF. , (RTEMS ), , – Yocto Linux.

, , – HPSC , , , . Mongoose-V – MIPS , RAD6000 , PowerPC601. , , ; . , , , .

Figura 6. Comparación de los cristales PowerPC750 y RAD750. Los chips están hechos con los mismos estándares de diseño, su área al mismo tiempo casi se duplica. Preste atención al diseño de bloque casi idéntico: esto es lo que sucede cuando se garantiza la compatibilidad de bajo nivel. Las enormes diferencias en los tamaños de los bloques de memoria sugieren el uso de celdas de memoria resistentes a radiantes multitransistor (10T en lugar de 6T) con redundancia incorporada.

Un cambio de paradigma: el caso de la Agencia Espacial Europea

La historia de la ingeniería europea de procesadores espaciales está indisolublemente unida al nombre del ingeniero sueco Jiri Gaisler. Se unió a la ESA a mediados de los años ochenta y comenzó a desarrollar los primeros microprocesadores espaciales europeos patentados. Al principio era un 1750A estadounidense con licencia, luego su propio desarrollo basado en el mismo sistema de comando (producido en Inglaterra), para mantener la compatibilidad con el software ya escrito. Y, dado que este es un sitio de TI, veamos qué tipo de software es:

Herramientas de propiedadAda compilador de TLD (EE. UU.)

Código abiertoEl sistema de compilación GNU para el 1750 se compuso inicialmente de dos partes principales.

Un conjunto de herramientas desarrolladas por CNS bajo el contrato de la Agencia:

- Compilador GNU C (gcc-2.7.2)

- Enlazador, ensamblador, archivador, etc. (binutils-2.7)

- Biblioteca c independiente

- Biblioteca POSIX-Threads (IEEE 1003.1c-1995) (un ejecutivo preventivo en tiempo real)

- Depurador GNU (gdb-4.16) para el 1750

un conjunto de herramientas desarrolladas internamente en la Agencia o disponibles de fuentes externas, a saber:

- CRTX (el SmartCom pequeño ejecutivo cíclico / síncrono en tiempo real - externo)

- Simulador independiente 1750 (O. Kellogg sim1750-2.3b - externo)

- wxIDE (un entorno de desarrollo integrado portátil basado en J. Smart wxWindows 2.65 - interno)

Un punto importante que distingue el trabajo de la Agencia Espacial Europea en términos de software es el apoyo específico y sistemático y el pago para la creación de productos de código abierto, así como la creación de ecosistemas para la reutilización del desarrollo y la reducción de costos. No solo para software: para microcircuitos resistentes a la radiación, el Instituto IMEC belga crea y apoya las plataformas de desarrollo DARE (Design Against Radiation Effects) de los intereses de la ESA, que incluyen rutas de diseño, PDK adaptados y grandes conjuntos de bloques de IP digitales y analógicos en seis procesos de fabricación diferentes (350, 180 , 90 y 65 nm). Estas plataformas no son de código abierto, pero tienen licencia para todos los artistas de contacto de la ESA si es necesario.

ERC32 - el primer completamente europeo

Ahora de vuelta a Jiri Geysler. La primera generación de sus propios procesadores europeos de arquitectura 1750A (un kit de tres chips se completó en 1989, el MA31750 totalmente integrado en 1991) se desarrolló con la mirada puesta en la misión Rosetta, que se convertiría en uno de los buques insignia de un amplio programa científico europeo-estadounidense, que también incluía el telescopio " Hubble ”y misiones para estudiar el sol y los planetas.

"Rosetta" es un aparato con un destino largo y complejo. El proyecto comenzó en 1986, junto con los Estados Unidos y se suponía que reutilizaría muchas partes de los dispositivos Mariner MkII (las patas del 1750A están creciendo a partir de aquí), pero después de un tiempo el Congreso de los Estados Unidos canceló la financiación de la parte estadounidense del programa (luego se convirtió en un presupuesto más bajo para la sonda Cassini), y Europa se quedó sola. En 1994, cuando quedó claro que la misión original, que incluía la entrega de materia cometaria a la Tierra, por sí sola no podía ser retirada, las tareas de la misión se reformularon; diez años más tarde, en 2004, Rosetta comenzó su viaje al cometa Churyumov-Gerasimenko, y en 2014, cuando lo alcanzó, se podían leer las noticias, incluidos los circuitos antiguos con el rendimiento de una calculadora de bolsillo. Y esto todavía no es suficiente noticia en las noticias sobre los procesadores de pila en el módulo de aterrizaje de Filae que implementan el hardware del lenguaje Forth.

El destino de Rosetta mostró claramente a la ESA que depender de socios estadounidenses no es la mejor idea, y la agencia comenzó a invertir una gran cantidad de dinero en programas para lograr la independencia tecnológica o, en nuestra opinión, en la sustitución de importaciones. Treinta años después, estos programas continúan existiendo, recibiendo un impulso relativamente nuevo relacionado con el deseo de Europa de tener acceso al mercado espacial ruso y, lo que es más importante, al chino, independientemente de las restricciones a las exportaciones, las sanciones y las guerras comerciales de Estados Unidos con China.

Habiendo ganado suficiente experiencia, el equipo de la ESA asumió una tarea más ambiciosa: un procesador de 32 bits. En ese momento, todavía estaba de moda crear sus propias arquitecturas RISC, pero la ESA no asignó dinero para dicho entretenimiento, sugiriendo a los desarrolladores que elijan una de las ISA existentes, además de no propietaria y preferiblemente con un buen ecosistema de software. Después de un estudio y una discusión posterior con un par de docenas de posibles contratistas de la ESA, la elección recayó en SPARC, que posee todas las cualidades necesarias y ya se distribuyó libremente a principios de los noventa por un consorcio acreditado liderado por Sun y Fujitsu. Un hecho curioso: se consideró ARM, pero se rechazó debido a la pequeña cantidad de software. Entre otros requisitos interesantes para el procesador estaba el soporte de hardware para el lenguaje Ada para acelerar el trabajo del software ya escrito para el 1750A, así como la presencia de modelos VHDL para acelerar el desarrollo de sistemas basados en procesadores.

Un punto fundamentalmente nuevo en los requisitos de desarrollo fue que el microprocesador en sí no se desarrolló como un chip, sino como un modelo de procesador de alto nivel en VHDL. Esto se hizo para no depender del fabricante de chips en particular y para garantizar la disponibilidad del procesador durante muchos años, incluso si algo le sucede a la fábrica seleccionada. Según la tradición estadounidense, el diseño central se basó en el procesador comercial Cypress CY601, y la fábrica francesa Temic Semiconductor (proceso de fabricación volumétrica resistente a la radiación con estándares de diseño de 800 nm) fue responsable de la resistencia a la radiación. En lugar de los tres años planeados, el proyecto duró cinco (1992-1997), el diseño se finalizó en la décima (!) Iteración de los chips de prueba, Ada tuvo que ser abandonada, pero como resultado el proyecto se consideró exitoso. El diseño resultante se llamó ERC32, un kit de microprocesador de tres chips ingresó al mercado con los nombres TSC691-693, e incluso más tarde, el proyecto se realizó en un solo chip como TSC695 (20 MHz, 14 MIPS, 4 MFLOPS, 0.5 W).

Además de la implementación habitual de SPARC, ERC32 implementa detección de fallas y corrección de software. El 99% de los disparadores en los registros de la Unidad Entera, el 100% de los disparadores en la FPU y los buses externos están equipados con paridad. Los errores detectados provocan seis tipos de interrupciones, cuya respuesta se determina mediante programación. En el caso más simple, el manejo de la interrupción consiste en repetir la instrucción fallida; en el peor de los casos, puede ser un reinicio de la computadora a bordo. Además, la instrucción NOP se modifica de tal manera que, en lugar de no hacer nada, verifica la suma de verificación recibida como los códigos de operación XOR de todas las instrucciones anteriores. Si la suma no coincide con el valor esperado (obtenido en la compilación), también se llama a una interrupción. Al concluir la descripción de ERC32, noto que no hay caché en absoluto, es decir, los desarrolladores de procesadores empujaron este gran problema a otras personas.

Las medidas propuestas para detectar fallas llevaron a un aumento del área en un 15%. O 130%, si consideramos la inclusión de dos ERC32 en una configuración duplicada, para lo cual también hubo soporte de hardware.

ERC-32 y el segmento ruso ISS

El primer dispositivo que usó ERC32, sin duda, merece una historia separada, ya que fue el primer caso de usar una unidad extranjera en equipos rusos de misión crítica, y también porque muestra claramente lo importante que no deben hacerse los proyectos.

En 1992, debido a mayores dificultades en la construcción de la estación espacial estadounidense a largo plazo Freedom, la ESA inició negociaciones sobre la posibilidad de su participación en el proyecto de la estación orbital rusa Mir-2. La parte rusa estuvo de acuerdo, pero no tenía un presupuesto en 1992. Después de dos años de intensas negociaciones (la votación en el Congreso de los Estados Unidos terminó con el puntaje 216-215), los proyectos Mir-2 y Freedom se convirtieron en la Estación Espacial Internacional (ISS), tal como lo conocemos hoy. Mientras tanto, los acuerdos europeo-rusos continuaron vigentes, y la ESA lanzó un proyecto de un sistema de procesamiento de datos para el módulo ruso "Dawn" (DMS-R, Sistema de gestión de datos - ruso).

Los procesadores disponibles en 1995, los resistentes a la radiación 1750 y 386, no cumplían con los requisitos de rendimiento, y en la carga del RAD6000 era necesario comprar placas de procesador completas, lo que no daba flexibilidad de desarrollo. Otra opción era ERC32, pero para ese momento solo existía en forma de modelos, y aún no se había hecho un solo chip de prueba en silicio. No sé qué impulsó a estas personas, pero claramente no era la idea de que algo pudiera salir mal con un procesador avanzado

inexistente . Y con él, por supuesto, hubo un retraso en el cronograma (que se omitió durante algún tiempo usando análogos comerciales) y un mar de errores (que era predecible para el primer gran proyecto de un pequeño equipo de desarrollo), y los errores estaban mal documentados, incluso bajo constante constante contacte a los desarrolladores DMS-R y los desarrolladores ERC32. Uno de los errores en FPU, que los desarrolladores de RSC Energia no pudieron localizar de ninguna manera, eventualmente tuvo que ser eludido con parches en el sistema operativo.

Hubo más demoras (en 1998, la financiación espacial en Rusia no fue muy buena nuevamente), pero en 2000 las computadoras a bordo desarrolladas por la ESA se pusieron en órbita con éxito y desde entonces han estado trabajando dentro del bloque ruso Zarya.

Figura 7. La computadora a bordo del módulo ISS Zarya basada en el procesador ERC32.

En 1996, incluso antes del final del proyecto ERC32, comenzó el desarrollo de requisitos para sus herederos. El apetito de los programadores creció a 100-500 MIPS en lugar de 10, y el rotundo éxito del proyecto original significó que Europa continuaría trabajando con la arquitectura SPARC en el futuro previsible. La tarea principal fue la creación de una versión de un solo chip de ERC32, la prometedora fue el nuevo núcleo del procesador.

LEON-FT

La característica principal del proyecto LEON-FT fue la tarea inicial de crear no un producto final en forma de chip, sino un núcleo con licencia en forma de código vhdl, y garantizar la tolerancia a fallas en lugar de la dureza de la radiación. La experiencia de ERC32 ha demostrado que requiere duplicación para una operación confiable, y el siguiente paso lógico fue desarrollar un sistema que no lo necesite. La solución a este problema requirió no solo la detección, sino también la corrección de fallas a nivel de hardware, sin usar software. Las ideas de tolerancia a fallas y endurecimiento de la radiación por diseño, por supuesto, no fueron inventadas por los autores LEON-FT, pero antes de ellos, este enfoque se consideró principalmente a nivel de transistor, y fueron los primeros en desatar completamente la lucha contra fallas individuales de la implementación física del chip y establecer el objetivo del proyecto para crear un chip estable en tecnología comercial y en cualquier disponible en un momento particular, resolviendo así el problema de la obsolescencia de los procesos tecnológicos y el cierre de fábricas. Por lo tanto, se registró un cambio de paradigma: veinte años antes de que viéramos el ejemplo de los chips SA3000, el problema principal era la dosis completa de radiación, que se combatía con métodos tecnológicos, y las fallas individuales se consideraban de acuerdo con el principio residual. Para el año 2000, el enfoque cambió, las fallas individuales se convirtieron en el problema principal, y el apego a una tecnología específica comenzó a verse como una desventaja y no como un mérito, incluso si la fábrica fue probada y confiable. Por cierto, ahora el inglés (y ni una palabra sobre Brexit) Dynex Semiconductor pertenece a los chinos, y el francés Temic se ha convertido en parte del microchip estadounidense.

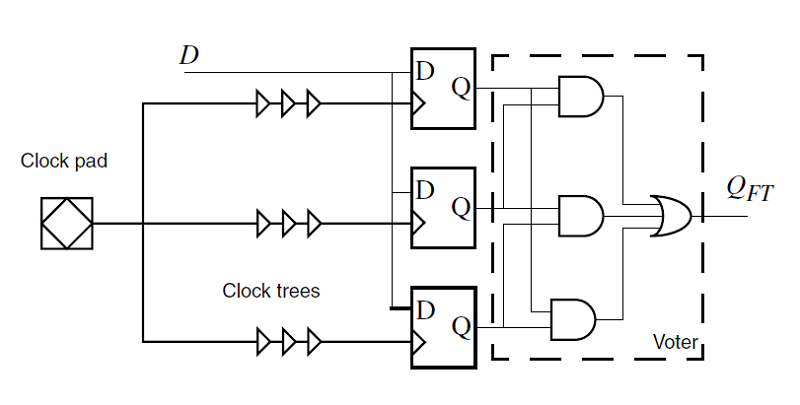

El núcleo LEON-FT fue escrito en VHDL y equipado con un configurador que le permite elegir diferentes opciones de protección contra fallas individuales para diferentes partes del chip: para un archivo de registro y memoria caché (¡apareció la caché!) Uno / dos bits de paridad o un código Hamming, así como forzar error de caché, para desencadenantes en la ruta de datos, la presencia o ausencia de redundancia triple, para una tubería (apareció una tubería): la capacidad de restablecer y volver a intentar comenzar desde una instrucción fallida. Por lo tanto, la única dependencia de la implementación física está solo en las características de la interfaz con bloques de memoria personalizados que conforman el archivo de registro. El crecimiento del área central con la máxima protección, excluyendo los cachés, es de aproximadamente el 100%, teniendo en cuenta, aproximadamente el 40%; con todas las opciones deshabilitadas, resultó ser el núcleo SPARC V8 lanzado en Open Source como LEON (sin el prefijo -FT). Esta práctica continuó aún más, y las versiones posteriores de LEONx en una versión inestable se presentaron en el dominio público, y las versiones configurables a prueba de fallas de LEONx-FT obtuvieron una licencia por dinero para crear microchips o como Soft IP para firmware en FPGA. De hecho, dado que LEONx-FT no está conectado a la tecnología de ninguna manera, nada impide que se usen en FPGA, por supuesto, si se cumple la condición (bastante estricta) de la ausencia de fallas en la memoria que controla las conexiones de elementos en el chip. Sin embargo, si esta memoria no es SRAM, sino flash o EEPROM, esta es una idea bastante realista, incluso sin tener en cuenta la existencia de FPGA tolerantes a fallos en los que la memoria de configuración está cubierta por hardware con códigos de autocorrección.

Figura 8. Gatillo troyado.

Nota de diseño de la biblioteca: para compatibilidad con cualquier biblioteca, el elemento de votación aquí se ensambla a partir de puertas lógicas ordinarias. Por supuesto, él mismo no está protegido de fallas individuales de ninguna manera, pero es mucho menos que un disparador ordinario, lo que significa que la probabilidad de ingresar es menor, y la falla es corta, pero no está bloqueada. Si esto no es suficiente, existen implementaciones especiales del elemento de votación a nivel de transistor, más resistentes a fallas que la opción mostrada en la figura, y se pueden agregar a la biblioteca como primitivas. Con estándares de diseño de 1000-100 nm, son posibles muchas implementaciones interesantes de elementos lógicos con mayor tolerancia a fallas, lo que permite cambiar mínimamente el diseño lógico del microcircuito y no introducir diseños triples complejos. Las opciones más populares son la duplicación interna en elementos y el filtrado incorporado (por ejemplo, en forma de resistencias en circuitos de retroalimentación en la memoria).

Figura 9. Celda de memoria DICE con duplicación incorporada; Debido a las retroalimentaciones cruzadas, es posible que falle solo si golpea simultáneamente dos inversores, lo cual es relativamente fácil de evitar. A la derecha están las topologías de una celda de memoria normal y DICE.

LEON-FT fue un proyecto de prueba y no estaba destinado a la comercialización; Este desarrollo, al igual que los productos comerciales posteriores, núcleos LEON2-FT, fue realizado por Geisler en su propia compañía Gaisler Research, ubicada en Gotemburgo. Atmel, que adquirió Temic, una empresa ERC32, obtuvo los derechos exclusivos de LEON2-FT; el producto resultante es el chip AT697, ampliamente conocido incluso en Rusia, realizado con la tecnología radiante especial Atmel y debido al hecho de que Atmel es una empresa estadounidense sujeta a restricciones de exportación y sanciones. En 2008, Gaisler Research se vendió a los estadounidenses de Aeroflex, luego el inglés Cobham los compró, luego comenzó Brexit, y ahora Cobham está comprando algún inversor estadounidense bajo el aullido sobre la inadmisibilidad de malgastar el tesoro nacional y la defensa nacional. Tal es la historia de la sustitución de importaciones y la independencia tecnológica en Europa.

La versión actual, LEON5, tiene una tubería de ocho etapas, un predictor de ramificación y otras características de los microprocesadores modernos, y a partir de la tercera versión, Gaisler ofrece no solo núcleos de procesador, sino también una gran biblioteca de varios bloques de IP, lo que permite a los usuarios crear sistemas en un chip que son adecuados para su específico requisitos, así como una gama bastante amplia de software propietario, de terceros y de código abierto (puede encontrar una descripción detallada

aquí , los sistemas operativos incluyen VxWorks 6.9 y 7.0, RTEMS 4.10 y 5, así como Linux basado en el núcleo 3.10 y 4.9).

Una pequeña digresión sobre economía y planificación.LEON se consideran los chips espaciales más exitosos y a gran escala. Al mismo tiempo, la circulación total de ambas variantes ERC32 fue de aproximadamente cinco mil unidades, y la circulación de chips Atmel basados en el núcleo LEON2-FT fue de aproximadamente mil quinientas unidades. American BAE Systems se jacta en folletos con 200 computadoras a bordo con el RAD6000 y ciento cincuenta con el RAD750. Es absolutamente claro que con tales circulaciones, el desarrollo y la certificación de dichos microcircuitos no pueden justificarse comercialmente a ningún precio para el microcircuito, y el desarrollo debe ser subsidiado por el estado (o, en el caso de la ESA, la unión de estados). Además, la necesidad de subsidiar el desarrollo en la mayoría de los casos se aplica no solo a los microprocesadores, sino también a la mayoría de los otros microcircuitos para aplicaciones espaciales, las excepciones se encuentran más fácilmente entre chips relativamente simples que pueden desarrollarse a bajo costo y luego venderse en grandes cantidades según los estándares espaciales. A su vez, esto crea las condiciones para la planificación estratégica a largo plazo para el desarrollo de la base de elementos espaciales, destacando áreas clave y reutilizando la propiedad intelectual desarrollada con dinero subsidiado. En este sentido, los modelos que operan en los EE. UU., Europa y Rusia difieren solo en los detalles de implementación y el nivel de organización del proceso.

División del trabajo

Como dije anteriormente, los núcleos IP LEONx-FT solo resuelven el problema de fallas individuales; la protección contra la dosis completa y el efecto tiristor recae en el usuario, que debe elegir un FPGA estable o una combinación de tecnología y bibliotecas.

Echemos un vistazo más de cerca al ejemplo del chip Gaisler GR712 utilizado en la reciente misión lunar israelí Bereshit.. GR712 – LEON3-FT. – 180 TowerJazz. – RadSafe, Ramon Chips ( , «»). RadSafe . GR716 – LEON3-FT – IMEC, IP 180 UMC. GR740 – , LEON4-FT – 65 ST Microelectronics, . , , , .

10. , MA31750 , GR740 ( 65 STM, , 250 , 459 MIPS/, 22.7 MFLOPS).

, . -, , , . -, , , . -, ( ), , .

–

. , , , .