Esta es la segunda parte del artículo sobre la historia de los microprocesadores para aplicaciones espaciales. La primera parte está

aquí . En él, en los ejemplos de microcircuitos estadounidenses y europeos, analizamos la historia del desarrollo de chips resistentes a la radiación desde los primeros procesadores de cristal único hasta el final de las dos milésimas, cuando los estándares de diseño para desarrollos espaciales estaban cerca de 100 nm.

El siguiente gran paso para garantizar la resistencia a la radiación comenzó con la transición a menos de 100 nm, donde casi cada próxima generación de tecnología trae nuevas preguntas: cambio de materiales, cambios en los requisitos de topología, crece la potencia estática (fugas sin radiación, que empeoran aún más bajo una dosis) , la importancia de los efectos individuales, que se convierten en múltiples, continúa creciendo. Estas tareas requirieron el desarrollo de nuevos enfoques y, sorprendentemente, un retorno parcial a los antiguos, porque algunas de las cosas que demostraron ser excelentes en los estándares de 1-0.18 μm no funcionan con estándares más finos. Por ejemplo, en tales tecnologías, para aumentar el rendimiento, está prohibido hacer transistores de anillo amados por los diseñadores de chips resistentes a la radiación. Contaré sobre cómo los diseñadores enfrentan nuevos desafíos con el ejemplo de Rusia, y al mismo tiempo compararé los logros de nuestros compatriotas con el éxito de colegas extranjeros y mostraré qué esperar en el futuro previsible.

Modernidad: el ejemplo de Rusia

Elegí Rusia para ilustrar la etapa actual, no porque los desarrollos rusos se destaquen a escala global, sino porque no tiene sentido escribir sobre algo más antiguo. Hubo muchos microcircuitos geniales en la URSS, pero toda la información sobre productos de doble uso fue clasificada, y ahora solo puede encontrar bicicletas de la forma sin un formulario de admisión: “Después del accidente de Chernobyl, Gorbachov personalmente acudió a los desarrolladores de robots para tratar los escombros y trajo un microprocesador radiante BM6” (de hecho, las palabras clave "mantienen la operabilidad en una amplia gama de factores mecánicos, climáticos y de

otro tipo " están contenidas en la descripción no "xxxxxBM6", sino 1806BM2). Hay pequeñas cosas al azar: en la serie 1839, según las entrevistas disponibles de desarrolladores creados para necesidades industriales, hay un chip N1839VZh2, un elemento de votación. En las computadoras convencionales, el elemento mayoritario no es necesario para nada, pero si buscas un poco en Google, puedes descubrir que la serie 1839 son computadoras integradas de los satélites GLONASS-M. Es una pena que tal cantidad de datos no permita escribir nada. Además, en el momento del advenimiento de los microprocesadores radiantes, la URSS ya se había embarcado firmemente en el camino de copiar los desarrollos occidentales, por lo que todavía no deberían esperarse innovaciones especiales.

Los años noventa en microelectrónica estuvieron marcados por la supervivencia y el exprimido de los últimos jugos de la herencia soviética. Se produjo un cambio condicional en 2003, que resultó ser un acontecimiento: en NIISI RAS, se lanzó su propia fábrica con estándares de diseño de 500 nm, los primeros procesadores de la familia Multicor entraron en la serie Angstrem, la empresa Digital Solutions se fundó, en el primero Antes de eso, un distribuidor de Milandre abrió un centro de diseño. Luego vino el programa objetivo federal "Desarrollo de la base de componentes electrónicos y electrónica de radio" para 2008-2015, que no logró los objetivos establecidos (45 nm para 2015, ventas de 300 mil millones de rublos, etc., etc.), pero aún así logró ayudar seriamente a la microelectrónica rusa. En este momento en Rusia hay aproximadamente 150-200 centros de diseño involucrados en el desarrollo de circuitos integrados, desde gigantes como el Micron hasta equipos de cinco a seis personas involucradas en cosas de nicho. La gran mayoría de estos equipos de alguna manera trabajan con órdenes gubernamentales y crean productos de doble uso. Además, la década entre 2003 y 2014 transcurrió no solo en el desarrollo de nuevos microcircuitos rusos y en los intentos de cerrar la brecha ya catastrófica con los fabricantes extranjeros; Una tarea más difícil que la creación de nuevos microcircuitos, fue la tarea de convencer a los fabricantes de sistemas para que comenzaran su aplicación. Después de agotar la cartera de pedidos soviética, la mayoría de los técnicos de sistemas se trasladaron densamente a componentes importados que estaban mejor fabricados, mejor documentados, más confiables y más accesibles; en general, realmente no había razón para hacerlo de otra manera. A continuación, un círculo vicioso de compatibilidad con versiones anteriores y la reutilización de la cartera de pedidos existente, gracias a la cual los desarrollos internos apretados continuaron por la borda. Para ser justos, había y hay compañías entre los fabricantes de equipos de radio a bordo en principio y cooperando constantemente con los desarrolladores nacionales de componentes electrónicos, pero en general, la situación en la industria se parecía a esto:

Una cita de una entrevista con Nikolay Testoedov, director del mayor fabricante ruso de naves espaciales ISS, que lleva el nombre de Reshetnev:

- ¿El satélite de comunicaciones militares Blagovest tiene una gran parte de componentes extranjeros?

- Allí, la relación tampoco fue muy buena, porque hasta 2014, cuando no había riesgos ni restricciones , compramos una gran cantidad de componentes extranjeros. El momento de crear satélites para el Ministerio de Defensa fue más importante.

Parece que no entiendo algo en la definición de la palabra "riesgo". Pero una vez en los vehículos militares puede usar componentes importados, podemos suponer que los "marcadores" en los microcircuitos no existen o se caen durante el arranque debido a sobrecargas.

Un cambio brusco se produjo en 2014, cuando, debido a las sanciones, los buenos microchips importados de doble uso inesperadamente dejaron de estar disponibles. Parece que aquí fue un gran momento para reunirnos y pasar a desarrollos domésticos, pero en cambio, la microelectrónica rusa volvió a caer en los resbaladizos rieles de la copia o, como dicen ahora, la sustitución de importaciones. Sin embargo, las letras me dejaron llevar, así que agreguémoslo incluso antes de mirar los estándares de diseño por debajo de 100 nm, veamos brevemente el estado de las cosas en los microprocesadores y microcontroladores espaciales rusos basados en los resultados de diez años de desarrollo y cinco años de sustitución de importaciones.

El zoologico

Mientras que en Estados Unidos existe un monopolio de poder de facto, y en Europa - SPARC, en Rusia todas las flores florecieron en todas las arquitecturas.

- BRAZO : Milander fabrica tres modelos de microcontroladores resistentes a la radiación basados en núcleos Cortex-M0 y Cortex-M4F, uno más Cortex-M0 es la alianza Angstrem y Digital Solutions, y otros tres Cortex-M4F son NIIIS.

- MIPS : los núcleos RISCore32 "compatibles con MIPS" controlan cuatro procesadores MultiBort heterogéneos resistentes a radiantes desarrollados por Elvis SPC; Los núcleos KOMDIV "similares a MIPS" están en el desarrollo de "Progreso" NIIISI, NIIIS y NIIMA.

- SPARC : el contratista principal para el desarrollo del LEON4 ruso (1906MB016) - Voronezh NIIET. Curiosamente, el Centro de Moscú para Tecnologías SPARC (ICST) no tiene nada que ver con eso. Aparentemente, la experiencia de Voronezh en el diseño de chips resistentes a la radiación resultó ser más importante.

- AMCS-96 : en general, el MCS-96 es una arquitectura de 16 bits, pero los sombríos genios de Voronezh de NIIET le hicieron una extensión de 32 bits y le montaron un microcontrolador radiante.

- PowerPC (casi allí): hay un chip del "Módulo" STC, que no tiene una resistencia declarada, pero que está diseñado para "equipo a bordo". Aparentemente para aviónica.

Además, hay varios microcontroladores de 8 y 16 bits, algunas opciones de DSP / VLIW ("análogos" propios y de otra persona), y luego casi cualquier cosa: memoria, BMC, FPGA, FPAA, ADC, DAC, microondas, dispositivos discretos Hay algunos microcircuitos de aplicación espacial para casi todos los gustos, pero el hecho es que no necesitamos algunos, sino competitivos, bien documentados y bien respaldados, y con el segundo y el tercer punto, los fabricantes rusos tradicionalmente tenían todo (y hay, que ya está allí) mal.

Figura 11. Otra observación sobre la cuestión de la diversidad de los microprocesadores nacionales: así es como suele ser un módulo de procesador "sustituido por importación". Agitamos la bandera "tenemos un procesador doméstico", y luego continuamos en modo normal. La misma foto, en principio, puede usarse como una ilustración de la escala de cuánto debe importarse todo.

Digresión de dígitosLos estándares de diseño son una excelente figura de marketing, que no tiene mucho que ver con los tamaños reales de los transistores y es realmente importante para un número limitado de aplicaciones, que incluyen procesamiento de datos, almacenamiento de gran capacidad y FPGA, donde una gran cantidad de metales y transistores van a la conexión de unidades informáticas. En todas las demás aplicaciones, los estándares de diseño no son tan críticos: los microcontroladores comerciales modernos se fabrican de acuerdo con los estándares de 180-90 nm y los microcircuitos de potencia: 180-600 nm, o incluso más. La elección de la tecnología depende de muchos factores, principalmente de las tareas que deben abordarse. Esto también se aplica a los microcircuitos espaciales, y a pesar de todos los crecientes volúmenes de procesamiento de información a bordo, una parte importante de los microcircuitos a bordo está ocupada con cosas completamente diferentes: control de actuadores, telemetría, conversión de energía, comunicaciones por radio, y por lo tanto no requiere los últimos estándares de diseño.

Si produce chips en el extranjero, en este momento para productos sobre los que no declara que es de doble uso, no hay riesgos, no hay restricciones y puede ejecutar cualquier cosa. Para la producción en Rusia, las tecnologías con estándares de diseño de hasta 90 nm están ahora disponibles, pero los "caballos de batalla" para los chips resistentes a la radiación de la mayoría de los desarrolladores rusos son la tecnología Mikron volumétrica de 180 nm y su propio proceso SOI de 240 nm. Sin embargo, las fábricas también están llenas de problemas con las sanciones debido a los suministros y equipos importados, pero esta es una historia larga y triste por separado.

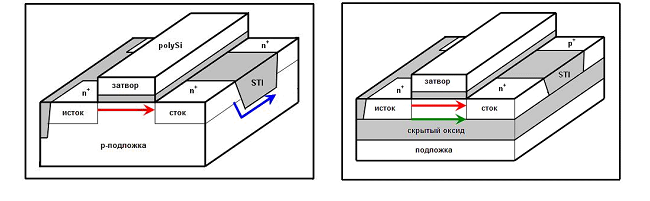

Figura 12. Comparación de la aparición de corrientes de fuga en transistores volumétricos y SOI MOS. Las fugas son la causa principal de fallas paramétricas causadas por una dosis completa de radiación. La figura muestra claramente que el SOI no resuelve todos los problemas con la resistencia a la radiación, pero la ausencia fundamental de un efecto tiristor debido al aislamiento completo de cada transistor facilita la vida de los desarrolladores, por lo que muchos de ellos son muy aficionados al SOI.

Dado que es absolutamente imposible mencionar a todos en Rusia sin resistencia a la radiación (y no brindan información sobre desarrollos en cada esquina), hablaré brevemente sobre tres compañías que se ocupan de microcircuitos espaciales no de vez en cuando, sino de manera sistemática y Por supuesto, se dedican a microprocesadores y microcontroladores. Estas empresas son Elvis, Milander y NIISI. Me gustaría informarle en detalle sobre el desarrollo de NIIET, pero sobre los métodos de protección contra la radiación, resultó ser difícil encontrar algo más específico que palabras generales como "soluciones estructurales y de circuitos especiales implementadas en el microcontrolador que aseguran su funcionamiento estable al nivel de la dosis acumulada no menos de 250 Crad y pérdida de energía lineal (TZZ) hasta 60 MeV ∙ cm2 / mg ”. La excepción es su LEON, pero todo es igual que en cualquier otro LEON-FT: disparadores triples y codificación resistente al ruido en la memoria.

JSC SPC "Elvis"

La compañía Elvis ha estado desarrollando la plataforma Multicor desde principios de la década de 2000, que es una combinación del núcleo de control RISC y DSP en un chip. Comenzaron un trabajo sistémico para garantizar la resistencia a la radiación aproximadamente al mismo tiempo, junto con el Departamento de Electrónica de MEPhI, utilizando primero tecnologías extranjeras; Después de la aparición de la propia tecnología de 180 nm de Micron, Elvis se convirtió en uno de los primeros clientes externos al desarrollar una biblioteca radiante de puertas lógicas y un conjunto de bloques de IP para crear sistemas en un chip. En las descripciones de la mayoría de los microcircuitos de

la plataforma Multibort (la versión resistente a la radiación de Multicore), la inscripción "el microcircuito está diseñado y fabricado en el territorio de la Federación de Rusia". Un conjunto de chips está diseñado para construir redes de datos a bordo de acuerdo con los estándares SpaceWire y SpaceFibre e incluye procesadores, DSP, memoria, PLL e interruptores.

Desde el principio, Elvis ha participado activamente en la creación y el desarrollo del estándar europeo para la transferencia de datos a bordo de la nave espacial SpaceWire (los estadounidenses usan su propio estándar - RapidIO), participando en reuniones del grupo de trabajo internacional y siendo el principal impulsor de la implementación del estándar SpaceFiber aún más rápido.

Figura 13. Diagrama de bloques del procesador 1892VM206. La frecuencia de operación del núcleo RISC es 120 MHz, los núcleos DSP son 140 MHz, cuatro puertos SpaceWire son 300 Mbit / s cada uno, dos puertos SpaceFibre son 1.25 Gbit / sy luego hay varios detalles triviales.

La ejecución en nuestra propia biblioteca resistente a la alegría en todos los circuitos se declara como la principal forma de lograr resistencia a la radiación. Hay pocos detalles sobre algunas técnicas arquitectónicas en las descripciones en el sitio web oficial, y la búsqueda de publicaciones no ha aclarado la imagen, porque Elvis se publica poco y principalmente sobre otros temas. Para todos los procesadores, se declara la codificación Hamming de toda la memoria, y en uno de los chips hay una triple reserva del archivo de registro y el árbol de reloj. Refiriéndose a la integridad de esta información con escepticismo saludable, supongamos que la defensa arquitectónica en los Multiborts está algo menos desarrollada que en LEON-FT.

JSC PKK "Milander"

Otro fabricante que se ocupa mucho de los microcircuitos resistentes a la lluvia es Milander. La mayoría de sus

chips resistentes a la alegría están diseñados de alguna manera para sistemas de telemetría a bordo: estos son chips de procesamiento de señal de sensores, conmutadores analógicos y digitales, ADC, memoria y, por supuesto, el tema de nuestro interés son tres microcontroladores. Más precisamente, no tres, sino dos y medio, porque el 1986BE8T y el 1986BE81T tienen núcleos ARM Cortex-M4F a bordo, conjuntos periféricos idénticos y difieren solo en el tipo de memoria de programa: ROM en el primer caso y SRAM en el segundo. Supongamos que la variante SRAM es realmente necesaria para depurar la variante ROM. 19230014 está equipado con un núcleo ARM Cortex-M0 más modesto y es parte del conjunto de chips para organizar un sistema de sensores multicanal, y este chip no es un microcontrolador en el sentido habitual, sino un controlador especializado, afilado para una aplicación específica.

En las especificaciones para 1986BE8T y 1986BE81T (tienen una común) puede encontrar una descripción del "controlador para procesar eventos de falla, fallas y errores", incluida la funcionalidad para detener fallas individuales, similar a la descrita anteriormente usando el procesador ERC32 también Una descripción detallada del funcionamiento de la codificación de corrección de errores (código Hamming SECDED) en diferentes tipos de memoria. No pude encontrar ninguna información abierta sobre, por ejemplo, la triple reserva de disparadores o un árbol de reloj, así que supongamos que desde el punto de vista de la tolerancia de falla arquitectónica 1986 19868 está entre ERC32 y LEON-FT.

Figura 14. BCD SOI de sección transversal con transistor LDMOS de alto voltaje en un bolsillo aisladoLa base tecnológica para la mayoría de los chips Milander resistentes a la radiación son las bibliotecas y un conjunto IP patentado de tecnología de proceso BCD SOI de 180 nm de la fábrica alemana XFAB. Esta tecnología, a diferencia del SOI convencional, tiene una capa gruesa de instrumentos de silicio (del orden de un micrón) y en la mayoría de los casos se comporta como una tecnología convencional a granel. La presencia de óxido latente le permite a uno organizar el aislamiento dieléctrico de los elementos entre sí y, por lo tanto, garantiza la ausencia de un efecto tiristor, y el hecho de que esté a una gran profundidad le permite no preocuparse por las fugas en la interfaz de silicio y un dieléctrico oculto, lo que reduce la resistencia a la dosis de la tecnología SOI convencional.

Figura 15. Comparación de dos elementos OR.

La figura muestra dos elementos lógicos idénticos (OR de dos entradas) de las bibliotecas de Milander realizadas utilizando diferentes métodos para aumentar la resistencia a la radiación. A la izquierda, puede ver los transistores de canal n en anillo que neutralizan completamente la fuga del transistor. Sin embargo, una medida tan radical a menudo es excesiva, ya que los transistores lineales convencionales (a veces con ligeros cambios) son suficientes para dosis moderadas de radiación, y debido a su aplicación, se puede lograr suficiente resistencia con un área más pequeña y un consumo de energía, que se muestra claramente en la figura.

Una característica importante de la tecnología elegida por Milander es la presencia en ella de transistores y otros elementos diseñados para operar con altos voltajes, hasta 200 V. La integración de la lógica digital y los dispositivos de potencia en un solo chip le permite crear convertidores de CC / CC, controladores clave, microcontroladores con eficiencia integrados. conductores y muchas otras cosas en demanda. En este momento, estas oportunidades no se utilizan, pero cuando comiencen, Milander obtendrá serias ventajas competitivas sobre otros desarrolladores, porque no hay análogos directos de esta tecnología en Rusia; o 180 nm a un voltaje de 3.3 V, o altos voltajes con estándares de diseño de 1-3 micras. Los trabajos sobre el tema de LDMOS de alto voltaje (e incluso su alegría) han sido publicados por el NIIIS durante los últimos años, pero hasta ahora son solo publicaciones científicas, y no se habla de producción en masa.

En la primavera, hubo noticias de que los estándares de diseño de 500 nm "para microcircuitos de fuentes de energía secundarias" se dominaron en Bryansk "Silicon-L", pero no se dieron detalles.Figura 16. Hoja de ruta para el desarrollo de desarrollos resistentes a radiantes de Milander utilizando la tecnología BCD SOI 180 nm. Y sí, ve correctamente la palabra "FPGA" en la esquina inferior derecha, ya la tienen y funciona.Institución del Estado Federal Centro de Investigación Científica para la Investigación del Sistema de la Academia de Ciencias de Rusia

NIISI explora sistemáticamente la informática, incluidos los microprocesadores radiantes para aplicaciones espaciales. La investigación sistemática, como corresponde a un instituto académico, implica un KPI en el número de publicaciones, por lo que monitorear el progreso del instituto es mucho más fácil que para las empresas comerciales. Estamos interesados en la parte de "espacio" de la línea "COMDIV" (también hay una parte de "alto rendimiento").La arquitectura de KOMDIV es una revisión creativa de MIPS32, licenciada por NIIIS a principios de los noventa. Inicialmente, el instituto trabajó con fábricas extranjeras, y después de la aparición de su propia producción, comenzó a trabajar en dos frentes, trasladando la mayor parte de la línea resistente a la alegría a casa. La fábrica de NIIIS está ubicada en Moscú, en el Instituto Kurchatov; Fue lanzado en 2003 y es una producción piloto a pequeña escala ubicada en grupos sellados en un área muy modesta. De hecho, los esfuerzos de los académicos Betelin, Valiev y Velikhov se dieron cuenta del concepto Minimal Fab que está de moda hoy, que solo funcionó normalmente quince años antes que los japoneses (y el primero fue inventado en Minsk por V.A. Labunov en 1983). Inicialmente, la fábrica trabajó con estándares de diseño de 500 nm, luego se dominaron los estándares de 350 y 250 nm,así como la tecnología de silicio sobre aislante, que se convirtió en la base de la línea resistente a radiantes NIIIS.Dos ventajas principales del procesador 1890VM1T (tecnología volumétrica de 500 nm, 50 MHz): funciona y es doméstico. Pero los microcircuitos rusos son tan severos que para una órbita baja (es decir, para las computadoras a bordo de las nuevas naves espaciales "digital" Soyuz-TMA y Progress-M) esto es suficiente, a pesar de la ausencia total de protección especial contra la radiación. Para el funcionamiento normal, el 1890BM1T necesita un chip complementario responsable de trabajar con interfaces externas (similar a cómo se hizo ERC32 en tres chips). Para condiciones más graves, se desarrollaron análogos (series 5890, 1900 y 1907) utilizando la tecnología SOI para eliminar el efecto tiristor. Al mismo tiempo, en los chips de la serie 1907, el controlador de interfaz ya está en el mismo chip que el procesador mismo.Como dije un poco más arriba, una de las ventajas de estudiar los productos NIISI es la abundancia de publicaciones. Como ejemplo, tomemos dos artículos publicados en IEEE Transactions on Nuclear Science en 2011 y 2013. El primero es MS Gorbunov et.al., "Análisis de la sensibilidad SEE del microprocesador CMOS SOI: correlación de los resultados obtenidos por diferentes métodos de prueba". Describe un procesador SOI de 500 nm con una frecuencia de reloj de 33 MHz. De las medidas arquitectónicas declaradas para aumentar la tolerancia a fallas, solo la paridad de caché, donde un error causa la misma interrupción que una falta de caché. Además, se aplicó una topología especial de transistores, que suprime el efecto bipolar parásito y, por lo tanto, aumenta el umbral de mal funcionamiento (y al mismo tiempo, por razones no relacionadas, aumenta la resistencia a la dosis de radiación completa). Relativamente fácilpero si el objetivo principal es la tolerancia a fallas, entonces esto es exactamente lo que necesita. Y luego, cuando se resuelve el problema de las fallas, puede comenzar a pensar en la tolerancia a las fallas.El segundo artículo es PN Osipenko et.al., "Microprocesador SOI tolerante a fallas para aplicaciones espaciales". Aquí vemos ya 350 nm en lugar de 500 y 50-66 MHz en lugar de 33 (rendimiento 8.9 MFLOPS a 50 MHz). Esto todavía no es de 150 MHz, como el RAD750 estadounidense que vuela casi al mismo tiempo en el espacio, pero el progreso es evidente. Aún más interesante es la estructura interna detallada del chip. Se triplica todo el núcleo, no disparadores, como en LEON-FT, sino toda la lógica combinacional. Esto, por supuesto, aumenta el área y el consumo en tres veces (1.8 W a 66 MHz), pero ayuda de fallas no solo en los elementos de almacenamiento, sino también en los combinados. Son mucho más pequeños que en la memoria, porque deben coincidir en el tiempo con la parte frontal de la señal del reloj para afectar algo (y también hay un efecto de enmascaramiento cuando la falla no pasa por la lógica, pero esto es particular),pero si ya ha comenzado a hacer todo correctamente, debe deshacerse de ellos.

Y ahora finalmente sub-100

Figura 19. Múltiples fallas de memoria usando el cristal de prueba de 65 nm como ejemplo.La figura muestra los resultados de obtener una partícula cargada de un tipo diferente (se notaron casi todos los gases nobles) en una matriz de memoria realizada con tecnología de 65 nm. A la izquierda hay memoria ordinaria, a la derecha hay una memoria radiante especialmente diseñada. ¡Diez fallas de un solo golpe! No dos, no tres - diez. Este efecto es causado por el hecho de que las dimensiones de los elementos del microcircuito disminuyen constantemente, pero el tamaño de la región de donde se recoge el exceso de carga cuando entra una partícula cargada sigue siendo el mismo (aproximadamente 2-2.5 micras), porque este tamaño depende de la difusión de la carga sobre el cristal. Y ahora la tecnología ha llegado al punto donde la celda de memoria se ha vuelto lo suficientemente pequeña como para que cualquier golpe cubra muchas celdas a la vez. El hecho de que se trata de difusión es evidente por la forma específica de las áreas afectadas, exactamente dos columnas, y no hay propagación más hacia la derecha y la izquierda.Por separado, preste atención a la columna de la derecha: estas son fallas de los protones, que constituyen la mayor parte de la radiación solar. Son la razón por la que no solo debes ejecutar chips comerciales modernos detrás de los cinturones de radiación de la Tierra (Ilon Mask, te estoy mirando a ti y a tu vuelo a Marte ahora). En el lado derecho de la figura: datos en una memoria similar, pero radostoykoy. Como puede ver, una parte importante de los problemas con múltiples fallas (y al mismo tiempo con todo lo demás) se ha resuelto: solo el área de dicha celda de memoria es varias veces mayor de lo habitual. Y ni siquiera comenzaré sobre cómo ensamblar una celda DICE de 65 nm con todos los transistores espaciados en el espacio, mezclando simultáneamente dos o cuatro de estas celdas para ahorrar espacio y no enredarse en los fideos de metalización de niveles múltiples resultantes. Sin embargo, entre las publicaciones de NIIIS también hay tales trabajos.formando la mayor parte de la radiación solar. Son la razón por la que no solo debes ejecutar chips comerciales modernos detrás de los cinturones de radiación de la Tierra (Ilon Mask, te estoy mirando a ti y a tu vuelo a Marte ahora). En el lado derecho de la figura: datos en una memoria similar, pero radostoykoy. Como puede ver, una parte importante de los problemas con múltiples fallas (y al mismo tiempo con todo lo demás) se ha resuelto: solo el área de dicha celda de memoria es varias veces mayor de lo habitual. Y ni siquiera comenzaré sobre cómo ensamblar una celda DICE de 65 nm con todos los transistores espaciados en el espacio, mezclando simultáneamente dos o cuatro de estas celdas para ahorrar espacio y no enredarse en los fideos de metalización de niveles múltiples resultantes. Sin embargo, entre las publicaciones de NIIIS también hay tales trabajos.formando la mayor parte de la radiación solar. Son la razón por la que no solo debes ejecutar chips comerciales modernos detrás de los cinturones de radiación de la Tierra (Ilon Mask, te estoy mirando a ti y a tu vuelo a Marte ahora). En el lado derecho de la figura: datos en una memoria similar, pero radostoykoy. Como puede ver, una parte importante de los problemas con múltiples fallas (y al mismo tiempo con todo lo demás) se ha resuelto: solo el área de dicha celda de memoria es varias veces mayor de lo habitual. Y ni siquiera comenzaré sobre cómo ensamblar una celda DICE de 65 nm con todos los transistores espaciados en el espacio, mezclando simultáneamente dos o cuatro de estas celdas para ahorrar espacio y no enredarse en los fideos de metalización de niveles múltiples resultantes. Sin embargo, entre las publicaciones de NIIIS también hay tales trabajos.en el que no deberías simplemente ejecutar chips comerciales modernos para los cinturones de radiación de la Tierra (Ilon Mask, te estoy mirando a ti y a tu vuelo a Marte ahora). En el lado derecho de la figura: datos en una memoria similar, pero radostoykoy. Como puede ver, una parte importante de los problemas con múltiples fallas (y al mismo tiempo con todo lo demás) se ha resuelto: solo el área de dicha celda de memoria es varias veces mayor de lo habitual. Y ni siquiera comenzaré sobre cómo ensamblar una celda DICE de 65 nm con todos los transistores espaciados en el espacio, mezclando simultáneamente dos o cuatro de estas celdas para ahorrar espacio y no enredarse en los fideos de metalización de niveles múltiples resultantes. Sin embargo, entre las publicaciones de NIIIS también hay tales trabajos.en el que no deberías simplemente ejecutar chips comerciales modernos para los cinturones de radiación de la Tierra (Ilon Mask, te estoy mirando a ti y a tu vuelo a Marte ahora). En el lado derecho de la figura: datos en una memoria similar, pero radostoykoy. Como puede ver, una parte importante de los problemas con múltiples fallas (y al mismo tiempo con todo lo demás) se ha resuelto: solo el área de dicha celda de memoria es varias veces mayor de lo habitual. Y ni siquiera comenzaré sobre cómo ensamblar una celda DICE de 65 nm con todos los transistores espaciados en el espacio, mezclando simultáneamente dos o cuatro de estas celdas para ahorrar espacio y no enredarse en los fideos de metalización de niveles múltiples resultantes. Sin embargo, entre las publicaciones de NIIIS también hay tales trabajos.En el lado derecho de la figura: datos en una memoria similar, pero radostoykoy. Como puede ver, una parte importante de los problemas con múltiples fallas (y al mismo tiempo con todo lo demás) se ha resuelto: solo el área de dicha celda de memoria es varias veces mayor de lo habitual. Y ni siquiera comenzaré sobre cómo ensamblar una celda DICE de 65 nm con todos los transistores espaciados en el espacio, mezclando simultáneamente dos o cuatro de estas celdas para ahorrar espacio y no enredarse en los fideos de metalización de niveles múltiples resultantes. Sin embargo, entre las publicaciones de NIIIS también hay tales trabajos.En el lado derecho de la figura: datos en una memoria similar, pero radostoykoy. Como puede ver, una parte importante de los problemas con múltiples fallas (y al mismo tiempo con todo lo demás) se ha resuelto: solo el área de dicha celda de memoria es varias veces mayor de lo habitual. Y ni siquiera comenzaré sobre cómo ensamblar una celda DICE de 65 nm con todos los transistores espaciados en el espacio, mezclando simultáneamente dos o cuatro de estas celdas para ahorrar espacio y no enredarse en los fideos de metalización de niveles múltiples resultantes. Sin embargo, entre las publicaciones de NIIIS también hay tales trabajos.cómo ensamblar una celda DICE a 65 nm con todos los transistores espaciados en el espacio, mezclando simultáneamente dos o cuatro de estas celdas para ahorrar espacio y no enredarse en los fideos de metalización de niveles múltiples resultantes. Sin embargo, entre las publicaciones de NIIIS también hay tales trabajos.cómo ensamblar una celda DICE de 65 nm con todos los transistores espaciados en el espacio, mezclando simultáneamente dos o cuatro de estas celdas para ahorrar espacio y no enredarse en los fideos de metalización de niveles múltiples resultantes. Sin embargo, entre las publicaciones de NIIIS también hay tales trabajos.

Figura 21. Redundancia modular triple y redundancia modular dual con voto automático. Del artículo de J.Teufel, "Circuitos de redundancia dual-modular de auto-votación para

Mitigación transitoria de evento único ”, IEEE Transactions on Nuclear Science, 2008 (Sandia Labs todavía está con nosotros, o más bien, todavía con ellos)

El diagrama en la figura data de 2008 y muestra que nuestros amigos jurados también usan muchas cosas interesantes diferentes en productos menos públicos que el RAD750 (y el principal campo de actividad de Sandia Labs es el programa nuclear militar estadounidense). En particular, en el artículo mencionado anteriormente y en una serie de publicaciones recientes, se analiza en detalle la cuestión de cómo utilizar la redundancia modular triple y dual en diferentes partes del chip. Y, por cierto, si el elemento de votación tiene un retraso suficientemente grande, entonces, en el esquema de doble redundancia, filtrará fallas individuales en la lógica, y el resultado será tan estable como la triple redundancia.

Ahora veamos cómo se ven los elementos de la biblioteca en la tecnología de 65 nm. Cito nuevamente el trabajo de NIISI - Yu.B. Rogatkin et al., "Desarrollo de una biblioteca de elementos resistentes a la radiación utilizando tecnología CMOS de 65 nm", Actas del NIISI RAS, 2018. Dado que la preocupación por la tolerancia a fallas se transfiere casi por completo a otros niveles de desarrollo (arquitectura y síntesis automática de topología, teniendo en cuenta las restricciones en la ubicación de los elementos), las tareas principales de los desarrolladores de bibliotecas de elementos nuevamente se convirtieron en protección contra la dosis absorbida total y el efecto tiristor.

Figura 22. Células lógicas hechas con tecnología de 65 nm.

El elemento más a la izquierda en la figura es un inversor de biblioteca regular.

El segundo elemento es su versión radiante, equipada con anillos de protección que evitan el efecto tiristor. Es importante que el anillo tenga contactos con el metal en un solo lado, y debemos tener en cuenta la resistencia de la capa de silicio, que puede ser lo suficientemente grande como para afectar la efectividad de esta solución.

El tercero es el mismo inversor, en el que los lados del anillo protector se cortan para ahorrar espacio.

El cuarto es el mismo, pero con contactos en la parte externa de los anillos de protección, para controlar bien su resistencia y no preocuparse por cómo se ensamblan en bloques.

Quinto: se muestra un bloque de dos inversores y un elemento 2INE con las partes de cierre de los anillos de protección.

En cuanto a la dosis completa de radiación, aquí, con estándares inferiores a 100 nm, todo es aún más simple y más comprensible que con las tecnologías más antiguas. Las corrientes de fuga en ellos ya no tienen radiación, todo se aplica sobre ellos y, por lo tanto, solo queda introducir una corrección adicional por el hecho de que crecerán aún más. Las tecnologías típicas de este nivel generalmente ofrecen tres opciones para los transistores: con voltaje de umbral bajo (rápido, pero con fugas grandes), con voltaje de umbral medio y con voltaje de umbral alto (lento, pero con fugas pequeñas), y el usuario puede combinarlas si es necesario. Por lo general, las bibliotecas estándar también se fabrican en tres versiones, y al diseñar una resistente a la radiación, se debe hacer un compromiso entre la velocidad y las fugas, dado el hecho de que los transistores están conectados en serie o en paralelo.

Figura 23. Esquemas de los elementos lógicos 2I-NOT y 2OR-NOT.

En el elemento 2, O NO, los transistores de canal n están conectados en paralelo, lo que duplica la fuga, lo que significa que tiene sentido usar transistores con un voltaje de umbral más alto en este lugar. Y en 2I-NOT están conectados en serie, y allí puede dejar el umbral habitual de transistores. Y dicho razonamiento (preferiblemente respaldado por datos de medición) debe aplicarse a todos los cientos de elementos en la biblioteca, y luego pensar qué hacer con los elementos de almacenamiento para que estén menos confundidos y se filtren a través de las teclas analógicas comúnmente utilizadas en los disparadores modernos, no lo rompieron todo, y así sucesivamente.

A partir de hoy, NIIIS tiene una plataforma completa para el desarrollo con estándares de diseño de 65 nm, que incluye bibliotecas, bloques de IP, compiladores de memoria, interfaces de alta velocidad, etc. También es importante que esta plataforma tenga licencia para otras compañías rusas, lo que ayuda a acelerar la superación de la brecha con los estadounidenses y prácticamente ponerse al día con los europeos. Si la fábrica no fuera TSMC, sino la suya, como en Estados Unidos y Europa ... Pero esta es otra historia que se desarrolla ante nuestros ojos. Después de 2014, la tecnología de proceso Micron de Mikron se congeló en el estado de "pasar la calificación y dominar la producción" después de 2014, y no ha habido noticias al respecto durante bastante tiempo; pero en los últimos meses ha habido suficientes noticias sobre planes a largo plazo para crear producción en Rusia con estándares de 28 nm. Cuándo se implementarán estos planes y si lo serán es una gran pregunta.

Resumiendo esta parte, observamos cómo, con una disminución en los estándares de diseño, las tareas que enfrentan los desarrolladores han cambiado nuevamente. Las tecnologías profundamente submicrónicas son resistentes a una dosis completa de radiación, suficiente para la mayoría de las aplicaciones, y le permiten organizar la protección contra el efecto tiristor y las fallas simples / múltiples en la etapa de desarrollo del chip, sin modificar la tecnología de proceso original. Esto ayuda a reducir el costo de producción y acelerar el desarrollo de nuevas tecnologías. Los principales obstáculos para el progreso son económicos: el desarrollo y el estudio integral de los chips de prueba y de "combate" se está volviendo más costoso con cada nueva generación de tecnología, y las escasas circulaciones de chips espaciales no nos permiten compensar adecuadamente estos costos. Por lo tanto, los desarrolladores buscan maximizar las capacidades de cada tecnología utilizada y usarla el mayor tiempo posible, avanzando solo cuando sea absolutamente necesario y creando plataformas de desarrollo y permitiéndole crear una amplia gama de microcircuitos. Los desarrolladores rusos de hoy están bastante detrás de los colegas occidentales, y las razones de este retraso no son científicas o de ingeniería, sino organizativas y económicas.

Forzosamente un breve análisis de todos los demás

Japón

La agencia espacial japonesa JAXA está moderadamente involucrada en la actividad internacional, y la mayor parte de su investigación espacial es realizada por los japoneses por su cuenta. Las misiones impresionan con ambición e historias sorprendentes sobre la superación exitosa de las dificultades que surgen en la órbita. Si Matt Damon pudiera tocar una sonda espacial, entonces ya veríamos películas sobre Hayabusa en la taquilla (los japoneses, por cierto, ya les han disparado tres piezas), y sobre Akatsuki. Los microprocesadores para el espacio, como todo lo demás, los japoneses tienen sus propias arquitecturas, e incluso sus estándares de diseño de producción no son los mismos que en el resto del mundo (300 y 200 nm, por ejemplo). Me complacería mucho escribir sobre esto en detalle, pero hay poca información y casi no hay información en no japonés, por lo que tendré que limitarme a una breve descripción general.

Figura 24. Una fuente típica de información sobre procesadores japoneses resistentes a la radiación.

Los principales proveedores de instrumentos JAXA son Hitachi, NEC y MHI (Mitsubishi Heavy Industries). En los años ochenta, a la industria japonesa le apasionaba el proyecto TRON, que ofrecía un diseño de infraestructura de red de extremo a extremo. Los japoneses todavía usan el sistema operativo TRON en tiempo real en la industria y en el espacio hasta ahora, pero la arquitectura de los microprocesadores TRON se abandonó con bastante rapidez (aunque se hicieron chips resistentes a la radiación y, muy probablemente, volaron) a favor de MIPS64 (en el caso de NEC) y otros Arquitectura japonesa SuperH de 32 bits (H es Hitachi; su versión SH2 se puede encontrar en automóviles japoneses, y SH4 en Sega Dreamcast y productos automotrices Hitachi y Renesas).

Figura 25. Microprocesadores espaciales japoneses. HR5000 - MIPS64, SOI-SOC - SH4.

Figura 26. Ilustración de aplicaciones SOI-SOC2.

"SOI" en SOI-SOC, por supuesto, significa "silicio en el aislante". El nivel tecnológico de SOI-SOC3 es de 200 nm, la próxima generación en desarrollo tendrá menos. También una pequeña pero importante cita de JAXA: “Existe un gran problema de errores suaves en los procesadores de consumo / industriales debido a los neutrones atmosféricos en el nivel del suelo. La MPU SOI-SOC se entregará como piezas de alta confiabilidad a los usuarios de esos procesadores ". El problema de los neutrones atmosféricos está relacionado principalmente con la aviación, pero esa es otra historia. Eso es todo con los japoneses, ve con sus vecinos.

China

El programa espacial chino es el de más rápido crecimiento y uno de los más cerrados, información sobre procesadores japoneses en comparación con los chinos solo el mar. Es difícil decir algo concreto, excepto que los chinos comenzaron copiando capa por capa de todo en una fila, y que en 2014 tenían muchas posiciones para Rusia que cayeron bajo sanciones. Recientemente, sin embargo, se ha invertido mucho dinero tanto en astronáutica china como en microelectrónica china, y los últimos dispositivos vuelan en procesadores compatibles con MIPS desarrollados por la Academia de Ciencias de China (¿no se parece a nada?) Loongson. Loongson Civilians construye PC, tabletas e incluso una supercomputadora; Este proceso se aceleró significativamente después del estallido de la guerra comercial entre Estados Unidos y China.

Israel

La Agencia Espacial de Israel se fundó en 1981, el primer satélite propio se lanzó desde Israel en 1988. Ahora Israel está desarrollando y lanzando (independientemente y desde puertos espaciales extranjeros) varias familias de vehículos civiles científicos y militares. No pude encontrar información sobre su relleno, pero me atrevo a sugerir que al menos los primeros vehículos de reconocimiento desarrollados por uno de los principales contratistas de aviación israelíes volaron en chips de arquitectura 1750A. En la ingeniería civil moderna, las empresas israelíes colaboran mucho con sus homólogos europeos, por lo que es lógico asumir el uso de LEON. La confirmación de esto es que el satélite privado Bereshit voló el año pasado en el GR712, una versión de LEON desarrollada y fabricada en Israel.

India

En India no hay producción de microcircuitos, solo una fábrica experimental de la academia local de ciencias (¿no recuerda nada?) Con estándares de 180 nm. Los indios realizan algunas investigaciones sobre la alegría, pero no se sabe nada importante de ellos. Según información fragmentaria de varias fuentes, utilizaron / están utilizando las opciones de procesador ERC32 y LEON para sus satélites, y la magnífica misión marciana "Mangalyan" estaba completamente controlada por los procesadores de arquitectura Mil-Std-1750A (nuevamente europeos).

Brasil

La microelectrónica brasileña es casi como un programa espacial brasileño: no se sabe nada al respecto, pero existe. En particular, los brasileños son fuertes especialistas en la corrección de fallas individuales en hardware ordinario utilizando métodos de software (por ejemplo, ejecutando parte de los comandos varias veces y verificando los resultados) y en la tolerancia a fallas de FPGA. Grupos universitarios especializados participan activamente en conferencias científicas internacionales y realizan proyectos conjuntos con colegas europeos y estadounidenses.

Eso parece ser todo. El resto de los países no desarrollan independientemente microprocesadores o sistemas espaciales basados en ellos, comprando componentes clave, bloques o satélites ensamblados en el lateral, como Pakistán, que está desarrollando su propia industria satelital en estrecha cooperación con los chinos. Bueno, está claro que el llenado de dispositivos iraníes y norcoreanos es conocido solo por sus creadores y, si tienen suerte, algunos servicios de inteligencia. No somos inteligencia, así que pasemos a la siguiente parte.

El futuro cercano: un ejemplo de todos juntos

El nivel tecnológico de los últimos microprocesadores espaciales es de 45 nm para EE. UU. (RAD5500), 65 nm para Europa (GR740) y 65 nm para Rusia (prometen lanzar algo este año). Al mismo tiempo, en los primeros dos casos, podemos observar un cambio generacional: en los EE. UU., La próxima generación de procesadores espaciales (HPSC) no será realizada por el actual monopolista de BAE Systems en arquitectura PowerPC, sino por Boeing en ARM (según los estándares de diseño de 32 nm en tecnología SOI), sino en Europa Paralelamente al lanzamiento del próximo SPARC LEON, se está desarrollando un procesador DAHLIA multinúcleo con una arquitectura ARM con estándares de diseño de 28 nm (también SOI). Paralelamente, la Agencia Espacial Europea, en su deseo habitual de no depender de las licencias de otras personas, comenzó a desarrollar la nueva arquitectura RISC-V, que está ganando impulso rápidamente en el sector comercial y se está convirtiendo en un ecosistema de software. Los primeros prototipos de chips RISC-V modificados con TMR ya fueron demostrados en 2018 por la colaboración de Antmicro y Thales. A pesar de la popularidad de LEON (como dicen, en círculos estrechos), hacia SPARC ha habido preguntas sobre el soporte de software desde hace mucho tiempo, y los competidores tienen prisa por aprovechar esto. Los competidores están especialmente apurados con ARM, porque el acceso prácticamente libre a una gran cantidad de software de aplicaciones industriales y comerciales es una carta de triunfo muy importante en las conversaciones con los desarrolladores de naves espaciales, cuya importancia está creciendo rápidamente en comparación con el deseo de tener una compatibilidad con proyectos antiguos.

Además de los microprocesadores y DSP, donde la velocidad es una prioridad obvia, existe una demanda de microcontroladores. Hay tales chips en la mayoría de las arquitecturas sonoras: European GR716 (SPARC / LEON), American RAD EMC (PowerPC), ARM de diferentes fabricantes (Vorago, Microchip, Milander, Angstrom), versiones a prueba de lluvia de MSP430 de Texas Instruments, MCS- 96 y MCS-51 de NIIET y así sucesivamente. Los microcontroladores generalmente protegen de manera más simple que sus contrapartes "grandes", con énfasis en la ausencia de fallas (efecto de tiristores) y con una corrección mínima de los núcleos comprados (o sin corrección y síntesis usando disparadores triples y bibliotecas de elementos especiales). Volviendo a los procesadores, veamos qué plataformas de desarrollo de menos de 100 nm existen o se anuncian en este momento.

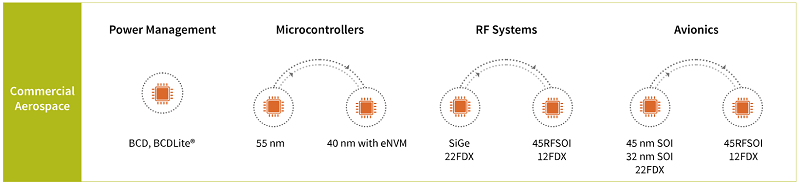

Figura 27. Plataforma de desarrollo de menos de 100 nm para circuitos integrados resistentes a la radiación.

65 nm para los desarrolladores de Europa y Rusia ya es "hoy", y los estadounidenses generalmente saltaron de 150 inmediatamente a 45 nm. Lo más probable es que, en los próximos diez años, estas tecnologías sean las principales, y los estándares más sutiles que ya se muestran en este diagrama pasarán de las etapas iniciales a las finales del desarrollo. Sin embargo, lo que se muestra en la figura son solo grandes colaboraciones públicas; de hecho, nada (excepto tiempo y dinero) no interfiere con el desarrollo de chips resistentes a la radiación en otros procesos técnicos sin demasiado ruido. Por ejemplo, GlobalFoundries ofrece crear chips aeroespaciales una línea completa de tecnologías para diferentes gustos y presupuestos. Es en sus instalaciones donde se producen los últimos RAD5545, y HPSC también se producirá en ellos; Esto no es sorprendente, porque las fábricas GloFo han sido certificadas por Trusted Foundry desde que pertenecieron a IBM. Y es poco probable que todos los procesos declarados sean sin clientes estadounidenses.

Figura 28. Ofertas de GlobalFoundries para la industria aeroespacial.

En GlobalFoundries, aunque no son estadounidenses, sino alemanes (en Dresde) planean producir sus futuros chips IMEC resistentes a la radiación (lo que significa toda Europa menos STM) y Milander.

Figura 29. La hoja de ruta de Milandra para el desarrollo de chips resistentes a la radiación basados en tecnología de 22 nm. Como puede ver, hay muchos planes, incluidos grandes FPGA y ADC rápidos para Radio definida por software (SDR). Ya se ha producido el primer chip de prueba, por lo que esperamos buenas noticias.

¿Qué es el FDSOI? FD está completamente agotado, completamente agotado; la delgada capa de silicio activo entre el óxido de la puerta y el óxido latente se agota por completo, y todo el canal del transistor lo ocupa. Esto le permite eliminar por completo la capacitancia parásita del drenaje y la fuente, así como eliminar la distancia de fuga a lo largo de la profundidad del silicio, lo cual es típico de tecnologías similares a granel, y reducir el consumo de energía estática. Además, en lugar de usar varios tipos de transistores, como en la tecnología volumétrica, en FDSOI puede suministrar localmente voltaje negativo o positivo a un óxido oculto, cambiando así el umbral del transistor (y con él la velocidad y el consumo de energía), dependiendo de si el chip está en activo o en modo de reposo. Juntos, esto hace que FDSOI sea extremadamente atractivo, por ejemplo, para Internet de las cosas. O para circuitos espaciales de baja potencia, el beneficio de la tecnología SOI alivia automáticamente al desarrollador de un dolor de cabeza con fallas catastróficas debido al efecto tiristor.

Figura 30. Vistas en sección transversal de los transistores surround y FDSOI.

La principal desventaja de FDSOI en términos de resistencia a la radiación es la ruta de fuga adicional a lo largo del límite del canal y el óxido latente. La carga que se acumula en el óxido oculto desempeña el papel de un voltaje positivo aplicado al óxido oculto, y en lugar de controlar el comportamiento de los transistores a través de la puerta inferior, el efecto de la radiación tiene que ser compensado. Y para hacer esto, se debe aplicar un gran voltaje negativo, lo que mejorará el proceso de acumulación de carga en el óxido latente y empeorará la resistencia a la dosis. En general, se obtiene un círculo vicioso, cuya salida puede resultar no trivial. Es cierto que hay muchas personas que quieren buscarlo, por lo que puede abastecerse de palomitas de maíz. Las primeras palomitas de maíz serán útiles muy pronto: el proyecto europeo DAHLIA está casi completo.

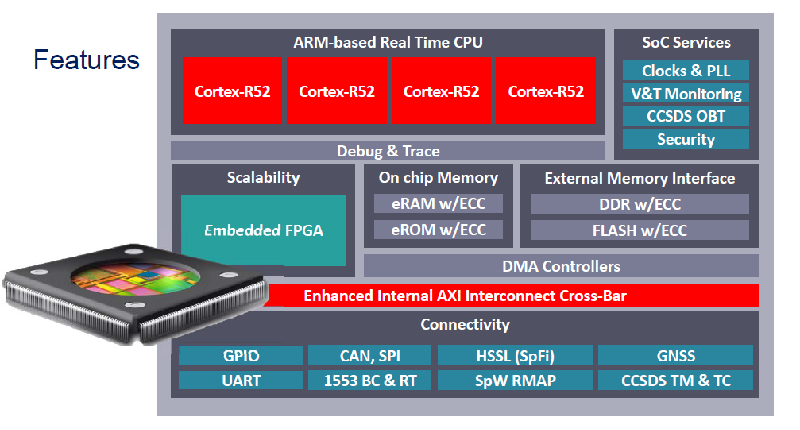

Figura 31. Diagrama de bloques de DAHLIA. FDSOI de 28 nm, cuatro núcleos ARM-Cortex R52 (prometen 4000 DMIPS a 600 MHz), mejorados para aplicaciones en tiempo real con separación avanzada de potencias, memoria a bordo, interfaces más populares e incluso un FPGA integrado para 500 mil LUT, para que un chip sea preciso cubrir las necesidades de todos los usuarios durante muchos años por venir.

La tecnología volumétrica, mientras tanto, no se va a rendir.

Puede ofrecer a los desarrolladores la ausencia de una ruta de fuga "extra" y, a la larga, estándares de diseño más bajos. Además, en los transistores FinFET, la puerta comienza a cubrir el canal cada vez más densamente, y el óxido aislante se aleja del campo eléctrico fuerte, lo que también debería afectar positivamente la resistencia a la dosis completa de radiación. IMEC ya está comenzando a desarrollar bibliotecas de 16 nm resistentes a la radiación, y la industria comercial continúa adoptando nuevas tecnologías.Figura 32. Diferentes generaciones de transistores MOS.A largo plazo, el GAA de Samsung (Gate All Around) promete ser resistente a una dosis completa de radiación, liberando completamente a los desarrolladores de problemas con él: simplemente no tienen ningún lado desde la fuente hasta el drenaje, más allá del canal principal y el obturador principal, y un aislante de puerta tan sutil que el cambio en el voltaje umbral será insignificante incluso a dosis muy grandes. Pero, por supuesto, sin duda habrá algunas dificultades nuevas, no solo con fallas individuales, sino también, por ejemplo, con efectos de sesgo, que ya preocupan por completo a los diseñadores de transistores de nitruro de galio HEMT. En los dispositivos hechos de semiconductores complejos, los efectos cuánticos y a nanoescala no son nuevos, y los desarrolladores de silicio muy pronto necesitarán conocerlos,Por lo tanto, durante los próximos años, el trabajo para garantizar la resistencia a la radiación de los microchips para el espacio será suficiente. Pero también hay colisionadores de hadrones, energía atómica y termonuclear; el progreso es implacable y él no va a detenerse, pero voy a detenerme con esta nota positiva. Gracias por leer hasta el final, espero que haya sido interesante.