Journal: Shock and Vibration 16 (2009) 45–59Autores: Robin Alastair Amy, Guglielmo S. Aglietti (correo electrónico: gsa@soton.ac.uk) y Guy RichardsonLugares de los autores: Grupo de Investigación Astronáutica, Universidad de Southampton, Facultad de Ciencias de la Ingeniería, Southampton, Reino Unido.

Surrey Satellite Technology Limited, Guildford, Surrey, Reino UnidoCopyright 2009 Hindawi Publishing Corporation. Este es un artículo de acceso abierto distribuido bajo la Licencia de Atribución Creative Commons, que permite el uso, distribución y reproducción sin restricciones en cualquier medio, siempre que el trabajo original se cite correctamente.

Anotación En el futuro, se supone que todos los equipos electrónicos modernos tendrán una funcionalidad cada vez mayor, al tiempo que mantendrán la capacidad de soportar cargas de golpes y vibraciones. El proceso de predicción de confiabilidad se ve obstaculizado debido a las características complejas de las respuestas y fallas de los equipos electrónicos, por lo que los métodos actuales son un compromiso entre la precisión de los cálculos y su costo.

La predicción confiable y rápida de la confiabilidad de los equipos electrónicos durante su operación con cargas dinámicas es muy importante para la industria. Este artículo muestra los problemas para predecir la confiabilidad de los equipos electrónicos, ralentizando la recepción de resultados. También se debe tener en cuenta que el modelo para calcular la confiabilidad generalmente se construye teniendo en cuenta una amplia gama de configuraciones de equipos para una serie de componentes del mismo tipo. En este artículo, se comparan cuatro clases de métodos para predecir la confiabilidad (métodos de referencia, datos de prueba, datos experimentales y modelos de las causas físicas de falla - física de falla) para seleccionar la posibilidad de usar uno u otro método. Se observa que la mayoría de las fallas en los equipos electrónicos son causadas por cargas térmicas, pero esta revisión se enfoca en fallas causadas por golpes y vibraciones durante la operación.

Nota del traductor.

Nota del traductor. El artículo es una revisión de la literatura sobre estos temas. A pesar de su edad relativamente grande, sirve como una excelente introducción al problema de evaluar la confiabilidad por varios métodos.

1. Terminología

BGA Ball Grid Array.

DIP Dual In-line Processor, a veces conocido como Dual In-line Package.

FE Elemento finito.

PGA Pin Grid Array.

Placa de circuito impreso de PCB, a veces conocida como PWB (placa de cableado impresa).

PLCC Portador de chips con plomo de plástico.

PTH plateado a través del orificio, a veces conocido como Pin a través del orificio.

QFP Quad Flat Pack - también conocido como ala de gaviota.

Aleaciones de memoria de forma SMA.

Tecnología de montaje en superficie SMT.

Nota de los autores del original: en este artículo, el término "componente" se refiere a un dispositivo electrónico específico que se puede soldar a una placa de circuito impreso, el término "paquete" se refiere a cualquier componente de un circuito integrado (generalmente cualquier componente SMT o DIP). El término "componente adjunto" se refiere a cualquier placa de circuito combinado o sistema de componentes, al tiempo que enfatiza que los componentes conectados tienen su propia masa y rigidez. (El embalaje de cristal y su efecto sobre la fiabilidad no se consideran en el artículo, por lo tanto, el término "paquete" puede entenderse más como el "caso" de un tipo u otro - aprox. Transl.)

2. Declaración del problema.

Las cargas de choque y vibración aplicadas a la placa de circuito causan tensiones en el sustrato de la placa de circuito, paquetes de componentes, conductores de componentes y uniones soldadas. Estas tensiones se deben a una combinación de momentos de flexión en la placa de circuito impreso y la inercia de la masa del componente. En el peor de los casos, estas tensiones pueden causar uno de los siguientes modos de falla: delaminación de la placa de circuito impreso, destrucción de la unión de soldadura, destrucción de plomo o destrucción del paquete de componentes. Si se ha producido alguno de estos modos de destrucción, lo más probable es que se produzca un fallo completo del dispositivo. El modo de falla experimentado durante la operación depende del tipo de empaque, las propiedades de la placa de circuito impreso y también de la frecuencia y amplitud de los momentos de flexión y las fuerzas de inercia. El lento progreso en el análisis de la confiabilidad de los equipos electrónicos se debe a las numerosas combinaciones de factores de entrada y tipos de fallas que deben considerarse.

En el resto de esta sección, trataremos de explicar la complejidad de considerar simultáneamente varios factores de entrada.

El primer factor de complicación a considerar es la amplia gama de tipos de paquetes disponibles en la electrónica moderna, ya que cada paquete puede fallar por varias razones. Los componentes pesados son más susceptibles a las cargas de inercia, mientras que la respuesta de los componentes SMT depende más de la curvatura de la placa de circuito. Como resultado, debido a estas diferencias básicas, estos tipos de componentes tienen criterios de falla significativamente diferentes, dependiendo de la masa o el tamaño. Este problema se ve exacerbado por la aparición constante de nuevos componentes disponibles en el mercado. Por lo tanto, cualquier método propuesto para predecir la confiabilidad debe adaptarse a los nuevos componentes para tener una aplicación práctica en el futuro. La respuesta de la placa de circuito a la vibración está determinada por la rigidez y la masa de los componentes que afectan la respuesta local de la placa de circuito. Se sabe que los componentes más pesados o más grandes cambian significativamente la reacción de la placa a la vibración en los lugares de su instalación. Las propiedades mecánicas de la placa de circuito impreso (módulo y grosor de Young) pueden afectar la confiabilidad de una manera difícilmente predecible.

Una placa de circuito más rígida puede reducir el tiempo de respuesta general de la placa de circuito bajo carga, pero al mismo tiempo, los momentos de flexión aplicados a los componentes pueden aumentar localmente (además, en términos de fallas inducidas térmicamente, en realidad es preferible especificar una placa de circuito más compatible, ya que reduce las tensiones térmicas impuestas al embalaje - aprox. La frecuencia y la amplitud de los momentos de flexión locales y las cargas de inercia superpuestas en el paquete también afectan el modo de falla más probable. Las cargas de alta frecuencia y baja amplitud pueden conducir a la falla por fatiga de la estructura, que puede ser la causa principal de la falla (fatiga cíclica baja / alta, LCF se refiere a fallas en las que prevalece la deformación plástica (N_f <10 ^ 6), mientras que HCF se refiere a la falla de la deformación elástica , generalmente (N_f> 10 ^ 6) a la falla [56] - nota del autor) La disposición final de los elementos en la placa de circuito impreso determinará la causa de la falla que puede ocurrir debido al voltaje en un componente individual causado por una carga inercial o momentos de flexión locales. Finalmente, es necesario tener en cuenta la influencia del factor humano y las características de producción, lo que aumenta la probabilidad de falla del equipo.

Cuando se considera un número significativo de factores de entrada y su compleja interacción, queda claro por qué todavía no se ha creado un método efectivo para predecir la confiabilidad de los equipos electrónicos. Una de las revisiones bibliográficas recomendadas por los autores sobre este tema se presenta en IEEE [26]. Sin embargo, esta revisión se enfoca principalmente en clasificaciones bastante amplias de modelos de confiabilidad, como el método para predecir confiabilidad en bibliografía de referencia y regulatoria, datos experimentales y modelado asistido por computadora de condiciones de falla (Física de falla de confiabilidad (PoF)), y no toca las fallas con suficiente detalle. causado por golpes y vibraciones. Foucher et al. [17] siguen un esquema similar de la revisión IEEE, ya que se pone un énfasis significativo en las fallas térmicas. La brevedad previa del análisis de los métodos de PoF, especialmente en relación con fallas de choque y vibración, merece su consideración adicional. Una revisión similar al IEEE está en proceso de compilar la AIAA, pero hasta ahora se desconoce el alcance de esta revisión.

3. La evolución de los métodos de predicción de fiabilidad.

El primer método de predicción de confiabilidad desarrollado en la década de 1960 se describe actualmente en MIL-HDBK-217F [44] (Mil-Hdbk-217F es la última y última versión del método, lanzado en 1995 - nota del autor) Este método, utilizando una base de datos de fallas de equipos electrónicos, obtiene la vida promedio de la placa de circuito impreso, que consta de ciertos componentes. Este método se conoce como un método para predecir la fiabilidad de acuerdo con la literatura de referencia. A pesar de que Mil-Hdbk-217F se está volviendo más obsoleto, el método de referencia todavía se usa hoy en día. Las limitaciones e imprecisiones de este método estaban bien documentadas [42,50], lo que condujo al desarrollo de tres clases de métodos alternativos: simulación por computadora de condiciones de falla física (PoF), datos experimentales y datos de pruebas de campo.

Los métodos de PoF predicen la fiabilidad analíticamente, sin recurrir al uso de datos recopilados previamente. Todos los métodos de PoF tienen dos características comunes del método clásico descrito en Steinberg [62]: primero, se busca la respuesta de vibración de la PCB a un efecto de vibración específico, luego se verifican los criterios de falla de los componentes individuales después de la exposición a la vibración. Un logro importante en los métodos de PoF fue el uso de las propiedades distribuidas (promedio) de la placa para crear rápidamente un modelo matemático de la placa de circuito impreso [54], que redujo significativamente la complejidad y el tiempo dedicado al cálculo exacto de la salida de vibración de la placa de circuito impreso (ver sección 8.1.3). Los desarrollos recientes en el campo de los métodos PoF han mejorado la predicción de fallas para componentes soldados SMT; sin embargo, con la excepción del método Barkers [59], estos nuevos métodos solo son aplicables en combinaciones muy específicas de componentes y placas de circuito impreso. Hay muy pocos métodos disponibles para componentes grandes, como transformadores o condensadores grandes.

Los métodos de datos experimentales mejoran la calidad y las capacidades del modelo utilizado en los métodos para predecir la confiabilidad en la literatura de referencia. El primer método basado en datos experimentales para predecir la fiabilidad de los equipos electrónicos fue descrito en 1999 por el método HIRAP (Honeywell In-service Reliability Assessment Program), creado por Honeywell, Inc [20]. El método de datos experimentales tiene varias ventajas sobre los métodos de pronóstico de confiabilidad en la bibliografía de referencia y regulatoria. Recientemente, han aparecido muchos métodos similares (REMM y TRACS [17], también FIDES [16]). El método de datos experimentales, así como el método de predicción de confiabilidad de acuerdo con la bibliografía de referencia y regulatoria, no permite tener en cuenta satisfactoriamente el diseño del tablero y el entorno de trabajo de su operación en la evaluación de confiabilidad. Este inconveniente puede corregirse debido a fallas de datos en la placa, de diseño similar o debido a placas que se encontraban en condiciones de funcionamiento similares.

Los métodos de datos experimentales dependen de la disponibilidad de una extensa base de datos que contiene datos sobre fallas a lo largo del tiempo. Cada tipo de falla en esta base de datos debe identificarse correctamente y debe determinarse su verdadera causa. Este método de evaluación de confiabilidad es adecuado para compañías que producen el mismo equipo en lotes suficientemente grandes, de modo que se pueda procesar un número significativo de fallas para evaluar la confiabilidad.

Los métodos de prueba de confiabilidad de componentes electrónicos se han utilizado desde mediados de la década de 1970, generalmente se dividen en pruebas aceleradas y no aceleradas. El enfoque principal es probar el equipo, que crea el entorno operativo esperado lo más realista posible. Las pruebas se llevan a cabo hasta que ocurre una falla, lo que permite predecir MTBF (tiempo medio entre fallas - MTBF). Si el MTBF se califica como muy largo, la duración de la prueba se puede reducir mediante pruebas aceleradas, lo que se logra al fortalecer los factores ambientales y al usar la fórmula bien conocida para relacionar la tasa de falla en una prueba acelerada con la tasa de falla esperada. Dichas pruebas son vitales para los componentes con un alto riesgo de falla, ya que proporciona al investigador los datos que tienen el mayor nivel de confianza, sin embargo, no sería práctico usarlos para optimizar el diseño de los paneles debido al largo tiempo de una iteración del estudio.

Una revisión rápida de los trabajos publicados en la década de 1990 sugiere que este fue un período en que los métodos que utilizan datos experimentales, datos de prueba y métodos de PoF compitieron entre sí para reemplazar métodos obsoletos para predecir la confiabilidad de la bibliografía de referencia y regulatoria. Además, cada método tiene sus ventajas y desventajas, y cuando se usa correctamente, proporciona resultados valiosos. Como resultado, IEEE lanzó recientemente un estándar [26], que enumera todos los métodos utilizados para predecir la confiabilidad actual. El objetivo de IEEE era preparar un manual que proporcionara al ingeniero información sobre todos los métodos disponibles, así como las ventajas y desventajas inherentes a cada método. Aunque el enfoque IEEE todavía está al comienzo de un largo camino evolutivo, parece tener sus propios méritos, ya que el AIAA (Instituto Americano de Aeronáutica y Astronáutica) sigue con una guía llamada S-102, que es similar a IEEE, pero también tiene en cuenta la calidad relativa de los datos de cada método [27]. Estas pautas tienen el único propósito de reunir los métodos que circulan por la literatura mundial publicada sobre estos temas.

4. Fallos por vibración

La mayoría de los estudios anteriores se han centrado principalmente en la vibración aleatoria como la carga de la PCB, sin embargo, el próximo estudio aborda específicamente las fallas de choque. Dichos métodos no se analizarán en su totalidad aquí, ya que se incluyen en la clasificación de los métodos de PoF y se analizan en las secciones 8.1 y 8.2 de este artículo. Hin et al. [24] crearon una placa de prueba para verificar la integridad de las uniones BGA soldadas bajo impacto. Lau et al. [36] describieron la confiabilidad de los componentes PLCC, PQFP y QFP que se ven afectados a lo largo del plano y fuera del plano. Pitarresi et al. [53,55] examinaron las fallas de las placas base de las computadoras debido a cargas de choque y dieron una buena revisión de la literatura que describe el equipo electrónico bajo exposición a "choque". Steinberg [62] ofrece un capítulo completo dedicado al diseño y análisis de equipos electrónicos impactados, considerando tanto los métodos para predecir el medio de choque como los métodos para garantizar la operabilidad de los componentes electrónicos. Sukhir [64.65] describió errores en los cálculos lineales de la respuesta de la placa de circuito impreso a la carga de choque aplicada a los soportes de la placa. Por lo tanto, los métodos de referencia y los métodos de datos experimentales pueden considerar fallas de equipos relacionadas con el impacto, pero las fallas de "choque" se describen implícitamente en estos métodos.

5. Métodos de referencia

De todos los métodos disponibles descritos en los manuales, nos limitamos a solo dos que consideran fallas de vibración: Mil-Hdbk-217 y CNET [9]. Mil-Hdbk-217 es aceptado como referencia por la mayoría de los fabricantes. Al igual que todos los métodos de manuales y manuales, se basan en enfoques empíricos que tienen como objetivo predecir la confiabilidad de un componente a partir de datos experimentales o de laboratorio. Los métodos descritos en la bibliografía de referencia son relativamente simples de implementar, ya que no requieren un modelado matemático complejo, solo utilizan tipos de partes, número de partes, condiciones de funcionamiento de la placa y otros parámetros de fácil acceso. La entrada se ingresa en el modelo para calcular MTBF - MTBF. A pesar de sus ventajas, Mil-Hdbk-217 se está volviendo cada vez menos popular [12, 17,42,50,51]. Considere una lista incompleta de restricciones sobre su aplicabilidad.

- Los datos se están volviendo más obsoletos desde que se actualizaron por última vez en 1995 y no están relacionados con nuevos componentes, no hay posibilidad de revisar el modelo, ya que el consejo para mejorar los estándares de defensa decidió permitir que el método "muriera por muerte natural" [26].

- El método no proporciona información sobre el modo de falla, por lo tanto, el diseño de la placa de circuito impreso no se puede mejorar ni optimizar.

- Los modelos suponen que la falla es independiente del diseño, ignorando la ubicación de los componentes en la placa de circuito, sin embargo, se sabe que el diseño de los componentes tiene un gran impacto en la probabilidad de falla. [50]

- Los datos empíricos recopilados contienen muchas imprecisiones; se utilizan datos de componentes de primera generación con una tasa de falla anormalmente alta debido a registros erróneos de horas de operación, reparaciones, etc., lo que reduce la confiabilidad de los resultados de predicción de confiabilidad [51].

Todas estas deficiencias indican que se debe evitar el uso de métodos de referencia, sin embargo, dentro de los límites de admisibilidad de estos métodos, se deben implementar una serie de requisitos de las especificaciones técnicas. Por lo tanto, los métodos de referencia solo deben usarse cuando sea apropiado, es decir, en las primeras etapas del diseño [46].

Desafortunadamente, incluso este uso debe abordarse con cierta precaución, ya que dichos métodos no se han revisado desde 1995. Por lo tanto, los métodos de la literatura de referencia predicen de manera inherentemente pobre la confiabilidad mecánica y deben usarse con precaución.6. Métodos de prueba de datos

Los métodos de datos de prueba son los métodos más simples disponibles para predecir la confiabilidad. El prototipo del diseño propuesto de la placa de circuito impreso está sujeto a vibraciones ambientales reproducidas en el banco de laboratorio. A continuación, se realiza un análisis de los parámetros de fractura (MTTF, espectro de impacto), luego se utiliza para calcular los indicadores de fiabilidad [26]. El método de datos de prueba debe usarse teniendo en cuenta sus ventajas y desventajas., . , , . . , [70,71]. , , . , , . .

Como resultado de esto, los métodos de prueba, por regla general, no se usan para fallas por vibración, a menos que haya circunstancias atenuantes, por ejemplo, bajos voltajes, lo que lleva a un tiempo muy largo antes de la falla. Se pueden ver ejemplos de métodos de verificación de datos en Hart [23], Hin et al. [24], Lee [37], Lau y col. [36], Shetty y col. [57], Liguore y Followell [40], Estes y col. [15], Wang y col. [67], Jih y Jung [30]. Una buena visión general del método se da en IEEE [26].7. Métodos de datos experimentales.

El método de datos experimentales se basa en los datos de fallas de placas de circuito impreso similares que se han probado bajo ciertas condiciones de operación. El método es correcto solo para placas de circuito impreso que experimentarán cargas similares. El método de datos experimentales tiene dos aspectos principales: construir una base de datos de fallas de componentes electrónicos e implementar el método basado en el diseño propuesto. Para construir una base de datos apropiada, debe haber datos relevantes sobre fallas que se recopilaron de estructuras similares; Esto significa que deben existir datos de fallas para equipos similares. El equipo defectuoso también debe analizarse y las estadísticas deben recopilarse adecuadamente, no es suficiente indicar que este diseño de la placa de circuito impreso ha fallado después de un cierto número de horas,Es necesario determinar la ubicación, el modo de falla y la causa de la falla. Si no se han analizado a fondo todos los datos de fallas anteriores, se requerirá un largo período de recopilación de datos antes de utilizar el método de datos experimentales.(HALT) , , [27]. [27], , MTBF , , . [11,17,20,26].

8. (PoF)

, , PoF, . , , . , . , .

, . [15,36,37,67], , [40], , [62] [59], , .

Se observó que la falla es una función de la ubicación de los componentes en una placa de circuito impreso [21.38], por lo que es probable que los modelos que tienen en cuenta las reacciones vibratorias locales sean precisos. La elección de qué parámetro (aceleración local, desviación local o momento flector) es decisivo para la falla depende del caso particular.Si se usan componentes SMT, entonces la curvatura o los momentos de flexión pueden ser más significativos para la falla; para componentes pesados, las aceleraciones locales generalmente se usan como criterios de falla. Desafortunadamente, no se han realizado estudios para mostrar qué tipo de criterio es el más adecuado en un conjunto dado de datos de entrada.PoF, PoF, FE ( ), . , , , , PoF . PoF [17,19,26,49].

8.1.

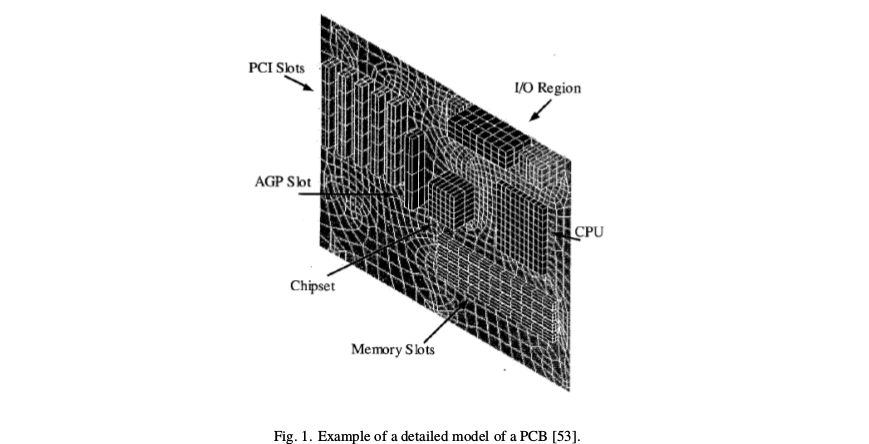

. , , . : , FE FE, . , , ( 8.1.4). . 1. [53].

8.1.1.

[62] . , ; . , , . , .

, . [53] 2% , 3,5% ( 54 ), .

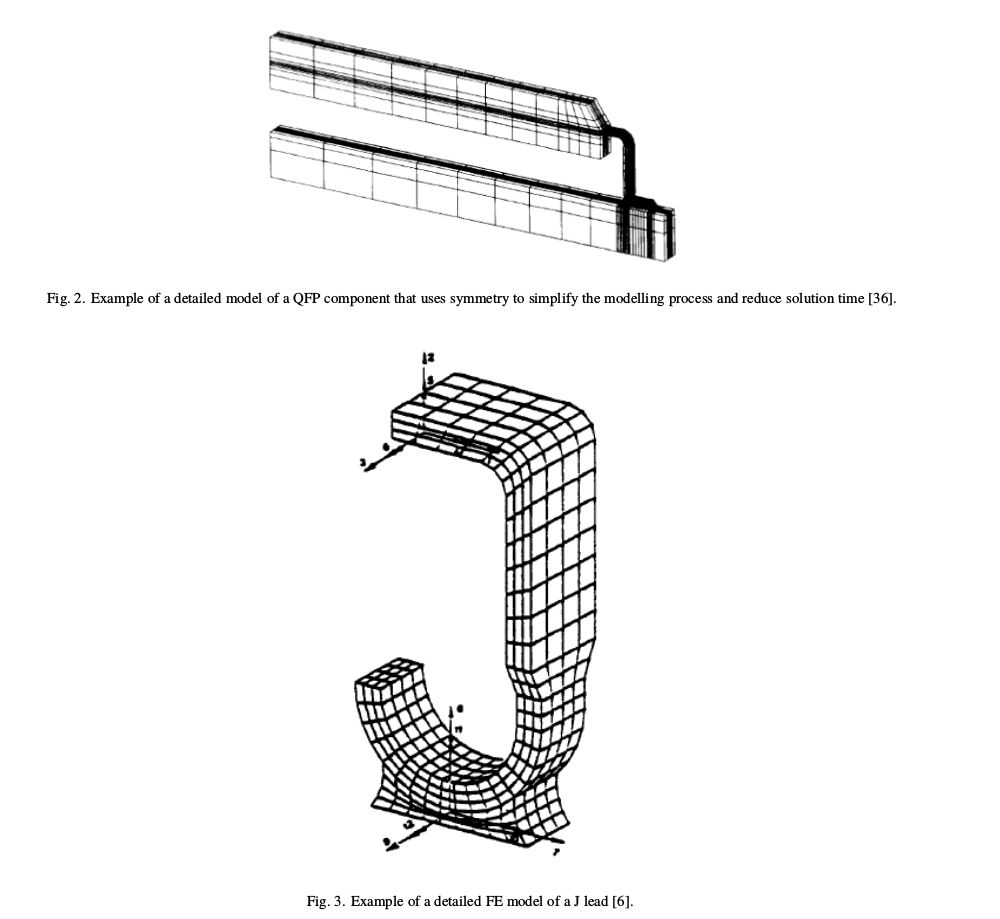

8.1.2. FE

FE [30,37,53, 57,58] ( . 1-3 ), ( ), , , . . , FE , JEDEC 4, [33-35], FE . , ( ), , . , FE , , , , .

8.1.3. FE

FE . , .

. 2. QFP, [36]. . 3. FE- J- [6].

[52]. Pitarresi . [52,54] , , .

En el primer artículo, consideramos un solo caso de un modelo FE simplificado de una placa de circuito impreso, verificado sobre la base de datos experimentales. El área principal de interés en este artículo es la determinación de propiedades distribuidas, con la observación de que se requiere una alta rigidez torsional para un modelo preciso., . . . M ( ) . , , M , . , Cifuentes [10] .

- 90% .

- , , , .

- .

- , .

8.1.4.

[59], , . ( ) , , . [5] , , . , . , . , . Lim et al. [41] , FE PCB; , Barker Chen [5]. , - , . , , [21]; Aglietti [2]; Aglietti Schwingshackl [3], Lim . [41].

8.1.5.

Pitarresi . [53-55] FE- PCB , , 3D — . . (SRS) , .

8.2.

, (MTBF), , (. IEEE [26]; Jensen [28]; O'Connor [47] ). . . , - ( , ), , , . .

8.2.1.

Como se indicó anteriormente, la limitación de la mayoría de los modelos empíricos es que son aplicables solo para configuraciones que incluyen el mismo grosor de la placa de circuito, tipos similares de componentes y carga de entrada, lo cual es poco probable. Sin embargo, la literatura disponible es útil por las siguientes razones: proporciona buenos ejemplos de pruebas de falla, destaca varias opciones para métricas de falla y proporciona información valiosa sobre la mecánica de la falla. Lee [37] creó un modelo empírico para predecir la fiabilidad de un paquete BGA de 272 pines y QFP de 160 pines. Se estudia la falla por fatiga en los conductores y en el cuerpo del paquete, los resultados experimentales están en buen acuerdo con el análisis de daños basado en tensiones calculadas usando el modelo FE detallado (ver también Li y Poglitsch [38, 39]). El proceso da un daño acumulado a un nivel dado de aceleración vibratoria de la señal de vibración de entrada.

Lau et al. [36] estimaron la confiabilidad de componentes específicos bajo carga de choque y vibración utilizando estadísticas de Weibull. Liguore y Followell [40] examinaron las fallas de los componentes LLCC y J-lead cambiando la aceleración local en los ciclos operativos. La aceleración local se usa en contraste con la aceleración de entrada del chasis, además, se investigó el efecto de la temperatura en los resultados de la prueba. El artículo también hace referencia al estudio del efecto del grosor de la placa de circuito impreso en la confiabilidad de los componentes.

Guo y Zhao [21] comparan la confiabilidad de los componentes cuando usan la curvatura torsional local como carga, en contraste con estudios previos que usaron aceleración. Se simula el daño por fatiga, luego se compara el modelo FE con los resultados experimentales. El artículo también analiza la optimización de la disposición de los componentes para aumentar la fiabilidad.

Ham y Lee [22] presentaron un método de datos de prueba para la determinación de tensiones de soldadura de plomo bajo carga de torsión cíclica. Estes et al. [15] examinaron el problema de la falla de los componentes del "ala de gaviota" (GOST IEC 61188-5-5-2013) con la aceleración de entrada aplicada y la carga térmica. Los componentes estudiados son los tipos de alojamiento de microcircuitos CQFP 352, 208, 196, 84 y 28, así como FP 42 y 10. El artículo está dedicado a la falla de componentes electrónicos debido a oscilaciones en la órbita del satélite geoestacionario de la Tierra, MTBF se da en términos de años de vuelo en geoestacionario o órbitas bajas de la tierra. Se observa que la falla de los cables del "ala de gaviota" es más probable en lugares en contacto con el cuerpo del paquete que en una conexión soldada.

Jih y Jung [30] examinan las fallas del equipo causadas por defectos congénitos de fabricación en una unión soldada. Esto se realiza creando un modelo FE muy detallado de la placa de circuito y encontrando la densidad espectral de potencia (PSD) para diferentes longitudes de grietas de producción. Ligyore, Followell [40] y Shetty, Reinikainen [58] han sugerido que los métodos empíricos proporcionan los datos de falla más precisos y útiles para configuraciones específicas de componentes conectados. Dichos métodos se utilizan si ciertos datos de entrada (grosor de placa, tipo de componente, rango de curvatura) pueden suponerse constantes durante todo el tiempo de diseño, o si el usuario puede permitirse realizar pruebas reales de este tipo.

8.2.2. Criterio de falla analítica

Modelos de juntas de esquina SMTVarios investigadores que examinan las fallas del terminal de esquina SMT sugieren que esta es la causa más común de falla. Los artículos de Sidhart y Barker [59] completan una serie anterior de trabajos, presentando un modelo para determinar la deformación de los cables angulares de SMT y componentes de cable de contorno. El modelo propuesto tiene un error de menos del 7% en comparación con el modelo FE detallado para los seis peores escenarios. El modelo se basa en una fórmula publicada previamente por Barker y Sidhart [4], donde se simuló la desviación de la parte adjunta sujeta al momento flector. El artículo de Suhira [63] analiza analíticamente los esfuerzos esperados en las salidas de paquetes debido a los momentos de flexión aplicados localmente. Barker y Sidhart [4] se basan en el trabajo de Suhir [63], Barker et al. [4], que considera la influencia de la rigidez rotacional principal. Finalmente, Barker et al. [7] utilizaron modelos de FE detallados para estudiar el efecto de las variaciones dimensionales en el plomo sobre la vida de fatiga del plomo.

Es apropiado mencionar aquí el trabajo sobre las constantes de resorte de plomo de JEDEC, debido a que la creación de modelos de componentes de plomo se simplificó enormemente [33-35]. Las constantes de resorte se pueden usar en lugar de un modelo detallado de compuestos de plomo, mientras que el modelo reducirá el tiempo para construir y resolver el modelo FE. El uso de tales constantes en el modelo de componente FE evitará el cálculo directo de las tensiones de plomo locales. En cambio, se dará una deformación general del cable, que luego debe asociarse con tensiones locales del cable o con criterios de falla del cable basados en el ciclo de vida del producto.

Datos de fatiga materialLa mayoría de los datos sobre la destrucción de materiales utilizados para soldaduras y componentes están relacionados principalmente con fracturas térmicas, y hay relativamente pocos datos relacionados con fracturas por fatiga. La referencia principal a esta área la proporciona Sandor [56], quien proporciona datos sobre la mecánica de la fatiga y la fractura de las soldaduras. Steinberg [62] considera la destrucción de muestras de soldadura. Los datos de fatiga para soldaduras y alambres estándar están disponibles en un artículo de Yamada [69].

La figura 4. El estado de falla habitual del manual para los componentes QFP está cerca del cuerpo del paquete.

Las fallas de modelado asociadas con la desconexión de la soldadura son un desafío debido a las propiedades inusuales de este material. La solución a esta pregunta depende del componente que necesita ser probado. Se sabe que para los paquetes QFP esto generalmente no se tiene en cuenta, y la fiabilidad se estima a partir de la bibliografía de referencia y reglamentaria. Pero si se calcula la soldadura de BGA, se calcula PGA de componentes grandes, entonces los compuestos de plomo debido a sus propiedades inusuales pueden afectar la falla del producto. Por lo tanto, para los paquetes QFP, las propiedades de fatiga del plomo son la información más útil. Para BGA, la información sobre la durabilidad de las uniones soldadas sometidas a deformación plástica instantánea es más útil [14]. Para componentes más grandes, Steinberg [62] proporciona datos sobre el esfuerzo de tracción de las juntas soldadas.

Modelos de falla de componentes pesadosLos únicos modelos de fractura que existen para componentes pesados se presentan en un artículo de Steinberg [62], que examina la resistencia a la tracción de los componentes y da un ejemplo de cómo calcular la tensión máxima permitida que se puede aplicar a un compuesto de plomo

8.3. Conclusiones sobre la aplicabilidad de los modelos PoF

Las siguientes conclusiones con respecto a los métodos de PoF se han hecho en la literatura.

La respuesta local es crítica para predecir la falla del componente. Como se señaló en Li, Poglitsch [38], los componentes en los bordes de una placa de circuito impreso son menos propensos a fallar que los ubicados en el centro de una PCB debido a las diferencias locales en la flexión. Por lo tanto, los componentes en diferentes lugares de la placa de circuito tendrán diferentes probabilidades de falla.

La curvatura local de la placa se considera un criterio de falla más importante que la aceleración de los componentes SMT. Documentos recientes [38,57,62,67] indican que la curvatura de la placa es el criterio principal para la falla.

Los diferentes tipos de paquetes, tanto en el número de salidas como en el tipo utilizado, son inherentemente más confiables que otros, independientemente del entorno local específico [15.36.38].

La temperatura puede afectar la confiabilidad de los componentes. Liguore y Followell [40] declararon que la vida de fatiga es más alta en el rango de temperatura de 0 ° C a 65 ° C, con una disminución notable a temperaturas inferiores a -30 ° C y superiores a 95 ° C. Para los componentes QFP, el lugar donde el cable se conecta a la bolsa (ver Fig. 4) se considera como el lugar principal de daño, y no como una junta de soldadura [15,22,38].

El grosor de la placa tiene un cierto efecto sobre la vida de fatiga de los componentes SMT, ya que se ha demostrado que la vida de fatiga de BGA disminuye aproximadamente 30-50 veces si el grosor de la placa aumenta de 0,85 mm a 1,6 mm (mientras se mantiene una curvatura total constante) [13] La flexibilidad (flexibilidad) de los cables del componente afecta significativamente la confiabilidad de los componentes del cable periférico [63], sin embargo, esta es una dependencia no lineal, y las conclusiones de la conexión intermedia de los elementos son las menos confiables.

8.4. Métodos de software

El Centro de Excelencia de Tecnología del Ciclo de Vida (CALCE) de la Universidad de Maryland proporciona software para calcular la respuesta de vibración y choque de las placas de circuito impreso. El software (llamado CALCE PWA) tiene una interfaz de usuario que simplifica el proceso de iniciar el modelo FE e ingresa automáticamente el cálculo de la respuesta en el modelo de vibración. No se utilizan supuestos para crear el modelo de respuesta FE, y los criterios de rechazo utilizados se toman de Steinberg [61] (aunque también se supone que se aplica el método de Barkers [48]). Para proporcionar recomendaciones generales sobre la mejora de la confiabilidad de los equipos, el software descrito ofrece buenos resultados, especialmente porque tiene en cuenta simultáneamente los voltajes inducidos térmicamente y requiere un conocimiento especial mínimo, sin embargo, la precisión de los criterios de falla en los modelos no se ha confirmado experimentalmente.

9. Métodos para mejorar la fiabilidad de los equipos.

Esta sección discutirá las modificaciones posteriores al proyecto que aumentan la confiabilidad de los equipos electrónicos. Se dividen en dos categorías: las que cambian las condiciones de contorno de la placa de circuito impreso y las que aumentan la amortiguación.

El objetivo principal de las modificaciones de las condiciones de contorno es reducir la desviación dinámica de la placa de circuito impreso, esto se puede lograr endureciendo las costillas, soportes adicionales o reduciendo la vibración del medio de entrada. Los refuerzos pueden ser útiles porque aumentan las frecuencias naturales, reduciendo así la desviación dinámica [62], lo mismo se aplica a la adición de soportes adicionales [3], aunque la ubicación de los soportes también se puede optimizar, como se muestra en JH Ong y Lim [40] Desafortunadamente, las costillas y los soportes generalmente requieren un rediseño del esquema de diseño, por lo que estos métodos se consideran mejor al comienzo del ciclo de diseño. Además, se debe tener cuidado de que las modificaciones no cambien las frecuencias naturales de modo que coincidan con las frecuencias naturales de la estructura de soporte, ya que esto sería contraproducente.

Agregar aislamiento puede mejorar la confiabilidad del producto, reduciendo la influencia del medio dinámico transmitido al equipo, y puede lograrse de manera pasiva o activa.

Los métodos pasivos suelen ser simples y más baratos de implementar, por ejemplo, usando aisladores de cable [66] o usando las propiedades pseudoelásticas de las aleaciones con memoria de forma (SMA) [32]. Sin embargo, se sabe que los aisladores mal diseñados en realidad pueden aumentar la respuesta.

Los métodos activos proporcionan una mejor amortiguación en un rango de frecuencia más amplio, generalmente debido a la simplicidad y la masa, por lo que generalmente están diseñados para aumentar la precisión de los instrumentos de precisión muy sensibles y no para evitar daños. El aislamiento activo de vibraciones incluye métodos electromagnéticos [60] y piezoeléctricos [18,43]. A diferencia de los métodos para modificar las condiciones de contorno, la modificación de la amortiguación tiene como objetivo disminuir la respuesta de resonancia máxima de los equipos electrónicos, mientras que las frecuencias naturales reales deberían variar ligeramente.

Como en el caso del aislamiento de vibraciones, la amortiguación se puede llevar a cabo tanto pasiva como activamente, con una simplificación similar de la estructura en el primer caso y una mayor complejidad y amortiguación en el segundo.

Los métodos pasivos incluyen, por ejemplo, métodos muy simples, como el material de encolado, que aumenta la amortiguación de la placa de circuito impreso [62]. Los métodos más sofisticados incluyen la amortiguación de partículas [68] y el uso de absorbedores dinámicos de banda ancha [25].

El control activo de la vibración generalmente se logra mediante el uso de elementos piezocerámicos unidos a la superficie de la placa de circuito impreso [1.45]. El uso de métodos de endurecimiento es específico para cada caso y debe considerarse cuidadosamente en relación con otros métodos. La aplicación de estos métodos a equipos que se sabe que no tienen problemas de confiabilidad no necesariamente aumentará el costo y el peso de la estructura. Sin embargo, si un producto con un diseño aprobado presenta una falla durante la prueba, puede ser mucho más rápido y fácil aplicar la técnica de endurecimiento que rediseñar el equipo.

10. Oportunidades para el desarrollo de métodos.

En esta sección se detallan las posibilidades para mejorar la predicción de la confiabilidad de los equipos electrónicos, aunque los recientes avances en optoelectrónica, nanotecnología y tecnología de empaque pueden pronto limitar la aplicabilidad de estas propuestas. No se pueden usar cuatro métodos básicos para predecir la confiabilidad al momento de diseñar el dispositivo. El único factor que podría hacer que tales métodos sean más atractivos sería la creación de tecnologías de fabricación y prueba de bajo costo totalmente automatizadas, ya que esto permitiría construir y probar el diseño propuesto mucho más rápido que en la actualidad, con un esfuerzo humano mínimo.

El método PoF tiene muchas oportunidades de mejora. El área principal en la que se puede mejorar es la integración con el proceso general de diseño. El diseño de equipos electrónicos es un proceso iterativo que acerca al desarrollador al resultado final solo en conjunto con ingenieros especializados en electrónica, fabricación e ingeniería térmica, y diseño estructural. Un método que resuelva automáticamente algunos de estos problemas al mismo tiempo reducirá la cantidad de iteraciones de diseño y ahorrará una cantidad significativa de tiempo, especialmente cuando se considera el volumen de cooperación entre agencias. Otras áreas de mejora en las técnicas de PoF se dividirán en tipos de predicción de respuesta y criterios de falla.

La predicción de respuesta tiene dos posibles vías de desarrollo: modelos más rápidos y detallados, o modelos simplificados mejorados. Con la llegada de procesadores informáticos cada vez más potentes, el tiempo para resolver modelos FE detallados puede ser bastante pequeño, mientras que, al mismo tiempo, el software moderno reduce el tiempo de ensamblaje, lo que en última instancia minimiza el costo de los recursos humanos. Los métodos FE simplificados también se pueden mejorar mediante el proceso de creación automática de modelos FE, similares a los ofrecidos para los métodos FE detallados. Para esto, el software automático (CALCE PWA) está disponible actualmente, pero la tecnología no está suficientemente probada en la práctica, y las suposiciones hechas durante el modelado son desconocidas.

El cálculo del error inherente a varios métodos de simplificación sería muy útil, lo que nos permitiría implementar criterios útiles para la tolerancia a fallas.

Finalmente, una base de datos o método sería útil para impartir mayor rigidez a los componentes adjuntos, donde estas mejoras de rigidez podrían usarse para mejorar la precisión de los modelos de respuesta. La creación de criterios de falla de componentes depende de una ligera variación de componentes similares de diferentes fabricantes, así como del posible desarrollo de nuevos tipos de empaque, ya que cualquier método o base de datos para determinar los criterios de falla debe tener en cuenta dicha variabilidad y cambios.

Una solución sería crear un método / software para construir automáticamente modelos FE detallados basados en parámetros de entrada como plomo y tamaños de empaque. Tal método puede ser factible para componentes de una forma generalmente uniforme, como componentes SMT o DIP, pero no para componentes irregulares complejos, como transformadores, cebadores o componentes no estándar.

Los siguientes modelos de FE pueden resolverse para tensiones y combinarse con datos de falla del material (datos de curva de ductilidad S-N, mecánica de fractura o similar) para calcular la vida útil del componente, aunque los datos de falla del material deben ser de alta calidad. El proceso FE debe estar correlacionado con datos de prueba reales, preferiblemente en el rango más amplio posible de configuraciones.

El esfuerzo dedicado a dicho proceso es relativamente pequeño en comparación con la alternativa a las pruebas de laboratorio directas, que deberían realizar un número estadísticamente significativo de pruebas para diferentes espesores de placas de circuito impreso, diferentes intensidades de carga y direcciones, cientos de diferentes tipos de componentes están disponibles incluso para varios tipos de placas. , , .

- , , , . FE , .

, , : FE, , , , . PoF , . , , , , ( ).

, , , , , (), .

11.

, ( - , , PoF), . - , , , , , , .

PF , , . « » , FE. , FE, . « » , SMT .

, , , . . , , , .

Literatura[1] GS Aglietti, RS Langley, E. Rogers and SB Gabriel, An efficient model of an equipment loaded panel for active control design studies, The Journal of the Acoustical Society of America 108 (2000), 1663–1673.

[2]GS Aglietti, A lighter enclosure for electronics for space applications, Proceeding of Institute of Mechanical Engineers 216 (2002), 131–142.

[3] GS Aglietti and C. Schwingshackl, Analysis of enclosures and anti vibration devices for electronic equipment for space applications, Proceedings of the 6th International Conference on Dynamics and Control of Spacecraft Structures in Space, Riomaggiore, Italy, (2004).

[4] DB Barker and Y. Chen, Modeling the vibration restraints of wedge lock card guides, ASME Journal of Electronic Packaging 115(2) (1993), 189–194.

[5] DB Barker, Y. Chen and A. Dasgupta, Estimating the vibration fatigue life of quad leaded surface mount components, ASME Journal of Electronic Packaging 115(2) (1993), 195–200.

[6] DB Barker, A. Dasgupta and M. Pecht, PWB solder joint life calculations under thermal and vibrational loading, Annual Reliability and Maintainability Symposium, 1991 Proceedings (Cat. No.91CH2966-0), 451–459.

[7] DB Barker, I. Sharif, A. Dasgupta and M. Pecht, Effect of SMC lead dimensional variabilities on lead compliance and solder joint fatigue life, ASME Journal of Electronic Packaging 114(2) (1992), 177–184.

[8] DB Barker and K. Sidharth, Local PWB and component bowing of an assembly subjected to a bending moment, American Society of Mechanical Engineers (Paper) (1993), 1–7.

[9] J. Bowles, A survey of reliability-prediction procedures for microelectronic devices, IEEE Transactions on Reliability 41(1) (1992), 2–12.

[10] AO Cifuentes, Estimating the dynamic behavior of printed circuit boards, IEEE Transactions on Components, Packaging, and Manufacturing Technology Part B: Advanced Packaging 17(1) (1994), 69–75.

[11] L. Condra, C. Bosco, R. Deppe, L. Gullo, J. Treacy and C. Wilkinson, Reliability assessment of aerospace electronic equipment, Quality and Reliability Engineering International 15(4) (1999), 253–260.

[12] MJ Cushing, DE Mortin, TJ Stadterman and A. Malhotra, Comparison of electronics-reliability assessment approaches, IEEE Transactions on Reliability 42(4) (1993), 542–546.

[13] R. Darveaux and A. Syed, Reliability of area array solder joints in bending, SMTA International Proceedings of the Technical Program (2000), 313–324.

[14] NF Enke, TJ Kilinski, SA Schroeder and JR Lesniak, Mechanical behaviors of 60/40 tin-lead solder lap joints, Proceedings – Electronic Components Conference 12 (1989), 264–272.

[15] T. Estes, W. Wong, W. McMullen, T. Berger and Y. Saito, Reliability of class 2 heel fillets on gull wing leaded components. Aerospace Conference, Proceedings 6 (2003), 6-2517–6 C2525

[16] FIDES, FIDES Guide 2004 issue A Reliability Methodology for Electronic Systems. FIDES Group, 2004.

[17] B. Foucher, D. Das, J. Boullie and B. Meslet, A review of reliability prediction methods for electronic devices, Microelectronics Reliability 42(8) (2002), 1155–1162.

[18] J. Garcia-Bonito, M. Brennan, S. Elliott, A. David and R. Pinnington, A novel high-displacement piezoelectric actuator for active vibration control, Smart Materials and Structures 7(1) (1998), 31–42.

[19] W. Gericke, G. Gregoris, I. Jenkins, J. Jones, D. Lavielle, P. Lecuyer, J. Lenic, C. Neugnot, M. Sarno, E. Torres and E. Vergnault, A methodology to assess and select a suitable reliability prediction method for eee components in space applications, European Space Agency, (Special Publication) ESA SP (507) (2002), 73–80.

[20] L. Gullo, In-service reliability assessment and top-down approach provides alternative reliability prediction method. Annual Reliability and Maintainability, Symposium Proceedings (Cat. No.99CH36283), 1999, 365–377.

[21] Q. Guo and M. Zhao, Fatigue of SMT solder joint including torsional curvature and chip location optimization, International Journal of Advanced Manufacturing Technology 26(7–8) (2005), 887–895.

[22] S.-J. Ham and S.-B. Lee, Experimental study for reliability of electronic packaging under vibration, Experimental Mechanics 36(4) (1996), 339–344.

[23] D. Hart, Fatigue testing of a component lead in a plated through hole, IEEE Proceedings of the National Aerospace and Electronics Conference (1988), 1154–1158.

[24] TY Hin, KS Beh and K. Seetharamu, Development of a dynamic test board for FCBGA solder joint reliability assessment in shock & vibration. Proceedings of the 5th Electronics Packaging Technology Conference (EPTC 2003), 2003, 256–262.58

[25] V. Ho, A. Veprik and V. Babitsky, Ruggedizing printed circuit boards using a wideband dynamic absorber, Shock and Vibration 10(3) (2003), 195–210.

[26] IEEE, IEEE guide for selecting and using reliability predictions based on ieee 1413, 2003, v+90 C.

[27] T. Jackson, S. Harbater, J. Sketoe and T. Kinney, Development of standard formats for space systems reliability models, Annual Reliability and Maintainability Symposium, 2003 Proceedings (Cat. No.03CH37415), 269–276.

[28] F. Jensen, Electronic Component Reliability, Wiley, 1995.

[29] JH Ong and G. Lim, A simple technique for maximising the fundamental frequency of structures, ASME Journal of Electronic Packaging 122 (2000), 341–349.

[30] E. Jih and W. Jung, Vibrational fatigue of surface mount solder joints. IThermfl98. Sixth Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (Cat. No.98CH36208), 1998, 246–250.

[31] B. Johnson and L. Gullo, Improvements in reliability assessment and prediction methodology. Annual Reliability and Maintainability Symposium. 2000 Proceedings. International Symposium on Product Quality and Integrity (Cat. No. 00CH37055), 2000, -:181–187.

[32] M. Khan, D. Lagoudas, J. Mayes and B. Henderson, Pseudoelastic SMA spring elements for passive vibration isolation: part i modeling, Journal of Intelligent Material Systems and Structures 15(6) (2004), 415–441.

[33] R. Kotlowitz, Comparative compliance of representative lead designs for surface-mounted components, IEEE Transactions on Components, Hybrids, and Manufacturing Technology 12(4) (1989), 431–448.

[34] R. Kotlowitz, Compliance metrics for surface mount component lead design. 1990 Proceedings. 40th Electronic Components and Technology Conference (Cat. No. 90CH2893-6), 1990, 1054–1063.

[35] R. Kotlowitz and L. Taylor, Compliance metrics for the inclined gull-wing, spider j-bend, and spider gull-wing lead designs for surface mount components. 1991 Proceedings. 41st Electronic Components and Technology Conference (Cat. No. 91CH2989-2), 1991, 299–312.

[36] J. Lau, L. Powers-Maloney, J. Baker, D. Rice and B. Shaw, Solder joint reliability of fine pitch surface mount technology assemblies, IEEE Transactions on Components, Hybrids, and Manufacturing Technology 13(3) (1990), 534–544.

[37] R. Li, A methodology for fatigue prediction of electronic components under random vibration load, ASME Journal of Electronic Packaging 123(4) (2001), 394–400.

[38] R. Li and L. Poglitsch, Fatigue of plastic ball grid array and plastic quad flat packages under automotive vibration. SMTA International, Proceedings of the Technical Program (2001), 324–329.

[39] R. Li and L. Poglitsch, Vibration fatigue, failure mechanism and reliability of plastic ball grid array and plastic quad flat packages.

[40] Proceedings 2001 HD International Conference on High-Density Interconnect and Systems Packaging (SPIE Vol. 4428), 2001, 223–228.

[41] S. Liguore and D. Followell, Vibration fatigue of surface mount technology (smt) solder joints. Annual Reliability and Maintainability Symposium 1995 Proceedings (Cat. No. 95CH35743), 1995, -:18–26.

[42] G. Lim, J. Ong and J. Penny, Effect of edge and internal point support of a printed circuit board under vibration, ASME Journal of Electronic Packaging 121(2) (1999), 122–126.

[43] P. Luthra, Mil-hdbk-217: What is wrong with it? IEEE Transactions on Reliability 39(5) (1990), 518.

[44] J. Marouze and L. Cheng, A feasibility study of active vibration isolation using thunder actuators, Smart Materials and Structures 11(6) (2002), 854–862.

[45] MIL-HDBK-217F. Reliability Prediction of Electronic Equipment. US Department of Defense, F edition, 1995.

[46] SR Moheimani, A survey of recent innovations in vibration damping and control using shunted piezoelectric transducers, IEEE Transactions on Control Systems Technology 11(4) (2003), 482–494.

[47] S. Morris and J. Reilly, Mil-hdbk-217-a favorite target. Annual Reliability and Maintainability Symposium. 1993 Proceedings (Cat. No.93CH3257-3), (1993), 503–509.

P. O'Connor, Practical reliability engineering. Wiley, 1997.

[48] M. Osterman and T. Stadterman, Failure assessment software for circuit card assemblies. Annual Reliability and Maintainability. Symposium. 1999 Proceedings (Cat. No.99CH36283), 1999, 269–276.

[49] M. Pecht and A. Dasgupta, Physics-of-failure: an approach to reliable product development, IEEE 1995 International Integrated Reliability Workshop Final Report (Cat. No. 95TH8086), (1999), 1–4.

[50] M. Pecht and W.-C. Kang, A critique of mil-hdbk-217e reliability prediction methods, IEEE Transactions on Reliability 37(5) (1988), 453–457.

[51] MG Pecht and FR Nash, Predicting the reliability of electronic equipment, Proceedings of the IEEE 82(7) (1994), 992–1004.

[52] J. Pitarresi, D. Caletka, R. Caldwell and D. Smith, The smeared property technique for the FE vibration analysis of printed circuit cards, ASME Journal of Electronic Packaging 113 (1991), 250–257.

[53] J. Pitarresi, P. Geng, W. Beltman and Y. Ling, Dynamic modeling and measurement of personal computer motherboards. 52nd Electronic Components and Technology Conference 2002., (Cat. No. 02CH37345)(-), 2002, 597–603.

[54] J. Pitarresi and A. Primavera, Comparison of vibration modeling techniques for printed circuit cards, ASME Journal of Electronic Packaging 114 (1991), 378–383.

[55] J. Pitarresi, B. Roggeman, S. Chaparala and P. Geng, Mechanical shock testing and modeling of PC motherboards. 2004 Proceedings, 54th Electronic Components and Technology Conference (IEEE Cat. No. 04CH37546) 1 (2004), 1047–1054.

[56] BI Sandor, Solder Mechanics – A State of the Art Asssessment. The Minerals, Metals and Materials Society, 1991.

[57] S. Shetty, V. Lehtinen, A. Dasgupta, V., Halkola and T. Reinikainen, Fatigue of chip scale package interconnects due to cyclic bending, ASME Journal of Electronic Packaging 123(3) (2001), 302–308.

[58] S. Shetty and T. Reinikainen, Three- and four-point bend testing for electronic packages, ASME Journal of Electronic Packaging 125(4) (2003), 556–561.

[59] K. Sidharth and DB Barker, Vibration induced fatigue life estimation of corner leads of peripheral leaded components, ASME Journal of Electronic Packaging 118(4) (1996), 244–249.

[60] J. Spanos, Z. Rahman and G. Blackwood, Soft 6- axis active vibration isolator, Proceedings of the American Control Conference 1 (1995), 412–416.

[61] D. Steinberg, Vibration Analysis for Electronic Equipment, John Wiley & Sons, 1991.

[62] D. Steinberg, Vibration Analysis for Electronic Equipment, John Wiley & Sons, 2000.

[63] E. Suhir, Could compliant external leads reduce the strength of a surface-mounted device? 1988 Proceedings of the 38th Electronics Components Conference (88CH2600-5), 1988, 1–6.

[64] E. Suhir, Nonlinear dynamic response of a printed circuit board to shock loads applied to its support contour, ASME Journal of Electronic Packaging 114(4) (1992), 368–377.

[65] E. Suhir, Response of a flexible printed circuit board to periodic shock loads applied to its support contour, American Society of Mechanical Engineers (Paper) 59(2) (1992), 1–7.

[66] A. Veprik, Vibration protection of critical components of electronic equipment in harsh environmental conditions, Journal of Sound and Vibration 259(1) (2003), 161–175.

[67] H. Wang, M. Zhao and Q. Guo, Vibration fatigue experiments of SMT solder joint, Microelectronics Reliability 44(7) (2004), 1143–1156.

[68] ZW Xu, K. Chan and W. Liao, An empirical method for particle damping design, Shock and Vibration 11(5–6) (2004), 647–664.

[69] S. Yamada, A fracture mechanics approach to soldered joint cracking, IEEE Transactions on Components, Hybrids, and Manufacturing Technology 12(1) (1989), 99–104.

[70] W. Zhao and E. Elsayed, Modelling accelerated life testing based on mean residual life, International Journal of Systems Science 36(11) (1995), 689–696.

[71] W. Zhao, A. Mettas, X. Zhao, P. Vassiliou and EA Elsayed, Generalized step stress accelerated life model. Proceedings of 2004 International Conference on the Business of Electronic Product Reliability and Liability, 2004, 19–25.