मैं हेबर का स्वागत करता हूं। बहुत समय पहले नहीं, इस विषय पर लेख

Verilog पहले ही यहाँ दिखाई दे चुके हैं

। रैम पर डिजिटल फ़िल्टर और परिमित आवेग प्रतिक्रिया के साथ एक डिजिटल फ़िल्टर का निर्माण । मैं अपना मामूली योगदान देना चाहता हूं और आपको वेरिलोग पर डिजिटल IIR फिल्टर के कार्यान्वयन से परिचित कराना चाहता हूं।

इस तथ्य के बावजूद कि इस विषय में शामिल लोग नीचे के सभी को जानते हैं, मैं शुरुआत के लिए, अभी भी पाठकों की एक विस्तृत श्रृंखला के लिए बहुत कम सिद्धांत देता हूं।

IIR फ़िल्टर (IIR फ़िल्टर) - एक असीम आवेग प्रतिक्रिया (अनंत आवेग प्रतिक्रिया) के साथ एक फ़िल्टर।

एफआईआर फ़िल्टर (एक परिमित आवेग प्रतिक्रिया के साथ एक फिल्टर) से फिल्टर के इस प्रकार की एक विशिष्ट विशेषता प्रतिक्रिया की उपस्थिति है, जब फ़िल्टर आउटपुट पर मूल्य न केवल इनपुट डेटा पर निर्भर करता है, बल्कि पिछले पुनरावृत्तियों पर फ़िल्टर द्वारा प्राप्त आउटपुट डेटा पर भी निर्भर करता है। IIR फ़िल्टर की संरचना निम्नानुसार दर्शाई जा सकती है:

मैं एनालॉग फ़िल्टर के गुणांक की गणना करने के तरीकों पर ध्यान नहीं दूंगा, यह विषय बड़ी संख्या में प्रकाशनों में पाया जा सकता है, जैसे

एनालॉग और डिजिटल फ़िल्टर। जी। लेम या

फिल्टर के संश्लेषण की गणना और कार्यान्वयन । Herrero J. Willoner G. इसको करने के लिए कई कार्यक्रम भी हैं। मैं संक्षेप में केवल एनालॉग फ़िल्टर को डिजिटल में बदलने की प्रक्रिया का वर्णन करूंगा।

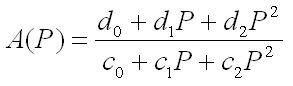

किसी भी फ़िल्टर को एक एनालॉग ट्रांसफर फ़ंक्शन का उपयोग करके दर्शाया जा सकता है। उदाहरण के लिए, दूसरे क्रम के IIR फ़िल्टर के लिए, यह इस तरह दिखेगा:

इस अभिव्यक्ति में सामान्यीकृत जटिल चर को प्रतिस्थापित करना

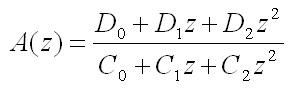

हमें ट्रांसफ़र फ़ंक्शन

A (z) मिलता है , जिसे डिजिटल फ़िल्टर में लागू किया जा सकता है:

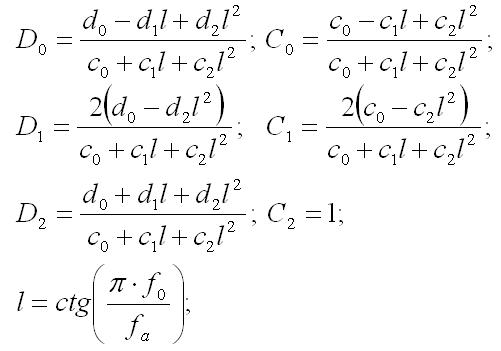

2 डी फिल्टर के लिए गुणांक निम्न सूत्रों द्वारा निर्धारित किया जाएगा:

जहाँ

- घड़ी की आवृत्ति

- फिल्टर कटऑफ आवृत्ति

d

0 ... 2 और

0 ... 2 के साथ एनालॉग फ़िल्टर के गुणांक हैं, यह माना जाता है कि आपने उन्हें पहले से गणना की है।

इन सरल गणनाओं का उपयोग करना और एनालॉग फ़िल्टर के लिए संबंधित गुणांक जानने के बाद, आप किसी भी क्रम के फिल्टर के डिजिटल हस्तांतरण फ़ंक्शन के लिए गुणांक की गणना कर सकते हैं। (मैं, हालाँकि, एक समय में केवल ४ वें क्रम तक पर्याप्त था, और इसमें कोई कठिनाई नहीं है, मुझे अभी बहुत से लंबे सूत्र लिखने हैं, उन्हें संक्षिप्त गुणन के सूत्रों द्वारा सरल करना है। लेकिन मुझे दूर के स्कूल के वर्षों की याद आ गई)। उदाहरण के लिए, मुझे ट्यून करने योग्य विशेषताओं के साथ एक फ़िल्टर को लागू करने के कार्य के साथ सामना किया गया था, इसलिए सभी गुणांक एक पीसी पर गणना किए गए थे और 32-बिट संख्या के रूप में FPGA में स्थानांतरित कर दिया गया था, जो इससे पहले एक फ़्लोटिंग पॉइंट प्रारूप में परिवर्तित हो गया था।

इसलिए, डिजिटल ट्रांसफ़र फ़ंक्शन के गुणांक होने पर, हम उन्हें IIR फ़िल्टर के अंतर समीकरण में प्रतिस्थापित करते हैं:

जिसके आधार पर वेरिलोग में कार्यान्वयन लिखना मुश्किल नहीं है।

मॉड्यूल पाठ module LP_FILTER ( mhz_clk,RESET, D0,D1,D2,C0,C1, X,Y, COUNT ); // low pass filter INPUT32 OUTPUT32 input mhz_clk; input RESET; input [17:0] X; input [31:0] D0; input [31:0] D1; input [31:0] D2; input [31:0] C0; input [31:0] C1; output [17:0] Y; output [5:0] COUNT; // adc-filter counter reg [5:0] COUNT; always @( posedge mhz_clk,negedge RESET ) if (~RESET) COUNT[5:0] = 0; //49 count else if (COUNT[5:0] == 6'h31) COUNT[5:0] = 0; else COUNT[5:0] = COUNT[5:0] + 6'b1; // input - COUNT[4:0] = 24:49 // output - COUNT[4:0] = 6 reg [31:0] c0_y2; reg [31:0] c1_y1; reg [31:0] d0_x2; reg [31:0] d1_x1; reg [31:0] d2_x0; reg [31:0] y0; reg [31:0] y1; reg [31:0] y2; reg [31:0] x0; reg [31:0] x1; reg [31:0] x2; // y(i) = D2 * x(i) + D1 * x(i-1) + D0 * x(i-2) + C1 * y(i-1) + C0 * y(i-2) reg [31:0] mul_a; reg [31:0] mul_b; always @(*) if ( ( COUNT[5:0] >= 0 ) & ( COUNT[5:0] <= 4 ) | ( COUNT[5:0] == 49 ) ) mul_a[31:0] = x0[31:0]; else if ( ( COUNT[5:0] >= 5 ) & ( COUNT[5:0] <= 10 ) ) mul_a[31:0] = x1[31:0]; else if ( ( COUNT[5:0] >= 11 ) & ( COUNT[5:0] <= 16 ) ) mul_a[31:0] = x2[31:0]; else if ( ( COUNT[5:0] >= 17 ) & ( COUNT[5:0] <= 22 ) ) mul_a[31:0] = y1[31:0]; else mul_a[31:0] = y2[31:0]; always @(*) if ( ( COUNT[5:0] >= 0 ) & ( COUNT[5:0] <= 4 ) | ( COUNT[5:0] == 49 ) ) mul_b[31:0] = D2[31:0]; else if ( ( COUNT[5:0] >= 5 ) & ( COUNT[5:0] <= 10 ) ) mul_b[31:0] = D1[31:0]; else if ( ( COUNT[5:0] >= 11 ) & ( COUNT[5:0] <= 16 ) ) mul_b[31:0] = D0[31:0]; else if ( ( COUNT[5:0] >= 17 ) & ( COUNT[5:0] <= 22 ) ) mul_b[31:0] = C1[31:0]; else mul_b[31:0] = C0[31:0]; wire [31:0] mul_out; mul_float32 ( 1, mhz_clk, mul_a[31:0], mul_b[31:0], mul_out[31:0] ); reg [31:0] outmul; always @(*) outmul[31:0]=mul_out[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) d2_x0[31:0] = 32'h0; else if ( COUNT[5:0] == 4 ) d2_x0[31:0] = mul_out[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) d1_x1[31:0] = 32'h0; else if ( COUNT[5:0] == 10 ) d1_x1[31:0] = mul_out[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) d0_x2[31:0] = 32'h0; else if ( COUNT[5:0] == 16 ) d0_x2[31:0] = mul_out[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) c1_y1[31:0] = 32'h0; else if ( COUNT[5:0] == 22 ) c1_y1[31:0] = mul_out[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) c0_y2[31:0] = 32'h0; else if ( COUNT[5:0] == 28 ) c0_y2[31:0] = mul_out[31:0]; // y(i) = D2 * x(i) + D1 * x(i-1) + D0 * x(i-2) + C1 * y(i-1) + C0 * y(i-2) reg [31:0] sum_a; reg [31:0] sum_b; always @(*) if ( ( COUNT[5:0] >= 0 ) & ( COUNT[5:0] <= 18 ) | ( COUNT[5:0] == 49 ) ) sum_a[31:0] = d2_x0[31:0]; else if ( ( COUNT[5:0] >= 19 ) & ( COUNT[5:0] <= 26 ) ) sum_a[31:0] = d0_x2[31:0]; else if ( ( COUNT[5:0] >= 27 ) & ( COUNT[5:0] <= 34 ) ) sum_a[31:0] = c1_y1[31:0]; else sum_a[31:0] = c0_y2[31:0]; always @(*) if ( ( COUNT[5:0] >= 0 ) & ( COUNT[5:0] <= 18 ) | ( COUNT[5:0] == 49 ) ) sum_b[31:0] = d1_x1[31:0]; else sum_b[31:0] = y0[31:0]; wire [31:0] sum_out; sum_float32 ( 1, mhz_clk, sum_a[31:0], sum_b[31:0], sum_out[31:0] ); reg [31:0] outsum; always @(*) outsum[31:0]=sum_out[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) y0[31:0] = 32'h0; else if ( ( COUNT[5:0] == 18 ) | ( COUNT[5:0] == 26 ) | ( COUNT[5:0] == 34 ) | ( COUNT[5:0] == 42 ) ) y0[31:0] = sum_out[31:0]; reg [17:0] int_to_float_in; always @(*) begin int_to_float_in[17:0] = X[17:0];end wire [31:0] int_to_float_out; int18_to_float32 ( 1, mhz_clk, int_to_float_in[17:0], int_to_float_out[31:0] ); always @( posedge mhz_clk,negedge RESET ) if (~RESET) x0[31:0] = 32'h0; else if ( COUNT[5:0] == 49 ) x0[31:0] = int_to_float_out[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) x1[31:0] = 32'h0; else if ( COUNT[5:0] == 49 ) x1[31:0] = x0[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) x2[31:0] = 32'h0; else if ( COUNT[5:0] == 49 ) x2[31:0] = x1[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) y1[31:0] = 32'h0; else if ( COUNT[5:0] == 49 ) y1[31:0] = sum_out[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) y2[31:0] = 32'h0; else if ( COUNT[5:0] == 49 ) y2[31:0] = y1[31:0]; wire [17:0] float_to_int_out; wire nan; wire overflow; wire underflow; float32_to_int18 ( 1, mhz_clk, y0[31:0], nan, overflow, float_to_int_out[17:0], underflow ); reg [17:0] Y; always @( posedge mhz_clk ) if ( COUNT[4:0] == 6 ) Y[17:0] = float_to_int_out[17:0]; endmodule

module LP_FILTER ( mhz_clk,RESET, D0,D1,D2,C0,C1, X,Y, COUNT ); // low pass filter INPUT32 OUTPUT32 /* y(i) = D2 * x(i) + D1 * x(i-1) + D0 * x(i-2) + C1 * y(i-1) + C0 * y(i-2) A(z) = (D0+D1*z+D2*z*z)/(C0+C1*z+z*z) <==> A(P) = (d0+d1*P+d2*P*P)/(c0+c1*P+c2*P*P) A(P) = 1/(1+1.4*P+P*P) LPF D0 = ( d0 - d1*l + d2*l*l)/(c0 + c1*l + c2*l*l) D1 = (2*d0 - 2*d2*l*l)/(c0 + c1*l + c2*l*l) D2 = ( d0 + d1*l + d2*l*l)/(c0 + c1*l + c2*l*l) C0 = -( c0 - c1*l + c2*l*l)/(c0 + c1*l + c2*l*l) C1 = -(2*c0 - 2*c2*l*l)/(c0 + c1*l + c2*l*l) l = ctg ( 3.14 * f_filt / f_samp ) */ input mhz_clk; input RESET; input [17:0] X; input [31:0] D0; input [31:0] D1; input [31:0] D2; input [31:0] C0; input [31:0] C1; output [17:0] Y; output [5:0] COUNT; // adc-filter counter reg [5:0] COUNT; always @( posedge mhz_clk,negedge RESET ) if (~RESET) COUNT[5:0] = 0; //49 count else if (COUNT[5:0] == 6'h31) COUNT[5:0] = 0; else COUNT[5:0] = COUNT[5:0] + 6'b1; // input - COUNT[4:0] = 24:49 // output - COUNT[4:0] = 6 reg [31:0] c0_y2; reg [31:0] c1_y1; reg [31:0] d0_x2; reg [31:0] d1_x1; reg [31:0] d2_x0; reg [31:0] y0; reg [31:0] y1; reg [31:0] y2; reg [31:0] x0; reg [31:0] x1; reg [31:0] x2; // y(i) = D2 * x(i) + D1 * x(i-1) + D0 * x(i-2) + C1 * y(i-1) + C0 * y(i-2) reg [31:0] mul_a; reg [31:0] mul_b; always @(*) if ( ( COUNT[5:0] >= 0 ) & ( COUNT[5:0] <= 4 ) | ( COUNT[5:0] == 49 ) ) mul_a[31:0] = x0[31:0]; else if ( ( COUNT[5:0] >= 5 ) & ( COUNT[5:0] <= 10 ) ) mul_a[31:0] = x1[31:0]; else if ( ( COUNT[5:0] >= 11 ) & ( COUNT[5:0] <= 16 ) ) mul_a[31:0] = x2[31:0]; else if ( ( COUNT[5:0] >= 17 ) & ( COUNT[5:0] <= 22 ) ) mul_a[31:0] = y1[31:0]; else mul_a[31:0] = y2[31:0]; always @(*) if ( ( COUNT[5:0] >= 0 ) & ( COUNT[5:0] <= 4 ) | ( COUNT[5:0] == 49 ) ) mul_b[31:0] = D2[31:0]; else if ( ( COUNT[5:0] >= 5 ) & ( COUNT[5:0] <= 10 ) ) mul_b[31:0] = D1[31:0]; else if ( ( COUNT[5:0] >= 11 ) & ( COUNT[5:0] <= 16 ) ) mul_b[31:0] = D0[31:0]; else if ( ( COUNT[5:0] >= 17 ) & ( COUNT[5:0] <= 22 ) ) mul_b[31:0] = C1[31:0]; else mul_b[31:0] = C0[31:0]; wire [31:0] mul_out; mul_float32 ( 1, mhz_clk, mul_a[31:0], mul_b[31:0], mul_out[31:0] ); reg [31:0] outmul; always @(*) outmul[31:0]=mul_out[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) d2_x0[31:0] = 32'h0; else if ( COUNT[5:0] == 4 ) d2_x0[31:0] = mul_out[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) d1_x1[31:0] = 32'h0; else if ( COUNT[5:0] == 10 ) d1_x1[31:0] = mul_out[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) d0_x2[31:0] = 32'h0; else if ( COUNT[5:0] == 16 ) d0_x2[31:0] = mul_out[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) c1_y1[31:0] = 32'h0; else if ( COUNT[5:0] == 22 ) c1_y1[31:0] = mul_out[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) c0_y2[31:0] = 32'h0; else if ( COUNT[5:0] == 28 ) c0_y2[31:0] = mul_out[31:0]; // y(i) = D2 * x(i) + D1 * x(i-1) + D0 * x(i-2) + C1 * y(i-1) + C0 * y(i-2) reg [31:0] sum_a; reg [31:0] sum_b; always @(*) if ( ( COUNT[5:0] >= 0 ) & ( COUNT[5:0] <= 18 ) | ( COUNT[5:0] == 49 ) ) sum_a[31:0] = d2_x0[31:0]; else if ( ( COUNT[5:0] >= 19 ) & ( COUNT[5:0] <= 26 ) ) sum_a[31:0] = d0_x2[31:0]; else if ( ( COUNT[5:0] >= 27 ) & ( COUNT[5:0] <= 34 ) ) sum_a[31:0] = c1_y1[31:0]; else sum_a[31:0] = c0_y2[31:0]; always @(*) if ( ( COUNT[5:0] >= 0 ) & ( COUNT[5:0] <= 18 ) | ( COUNT[5:0] == 49 ) ) sum_b[31:0] = d1_x1[31:0]; else sum_b[31:0] = y0[31:0]; wire [31:0] sum_out; sum_float32 ( 1, mhz_clk, sum_a[31:0], sum_b[31:0], sum_out[31:0] ); reg [31:0] outsum; always @(*) outsum[31:0]=sum_out[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) y0[31:0] = 32'h0; else if ( ( COUNT[5:0] == 18 ) | ( COUNT[5:0] == 26 ) | ( COUNT[5:0] == 34 ) | ( COUNT[5:0] == 42 ) ) y0[31:0] = sum_out[31:0]; reg [17:0] int_to_float_in; always @(*) begin int_to_float_in[17:0] = X[17:0];end wire [31:0] int_to_float_out; int18_to_float32 ( 1, mhz_clk, int_to_float_in[17:0], int_to_float_out[31:0] ); always @( posedge mhz_clk,negedge RESET ) if (~RESET) x0[31:0] = 32'h0; else if ( COUNT[5:0] == 49 ) x0[31:0] = int_to_float_out[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) x1[31:0] = 32'h0; else if ( COUNT[5:0] == 49 ) x1[31:0] = x0[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) x2[31:0] = 32'h0; else if ( COUNT[5:0] == 49 ) x2[31:0] = x1[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) y1[31:0] = 32'h0; else if ( COUNT[5:0] == 49 ) y1[31:0] = sum_out[31:0]; always @( posedge mhz_clk,negedge RESET ) if (~RESET) y2[31:0] = 32'h0; else if ( COUNT[5:0] == 49 ) y2[31:0] = y1[31:0]; wire [17:0] float_to_int_out; wire nan; wire overflow; wire underflow; float32_to_int18 ( 1, mhz_clk, y0[31:0], nan, overflow, float_to_int_out[17:0], underflow ); reg [17:0] Y; always @( posedge mhz_clk ) if ( COUNT[4:0] == 6 ) Y[17:0] = float_to_int_out[17:0]; endmodule

कार्यक्रम एक पूर्ण मॉड्यूल है, जो एक मौजूदा परियोजना में शामिल होने के लिए तैयार है। इनपुट डेटा इसे 18-बिट पूर्णांक के रूप में स्थानांतरित किया जाता है। (शायद ऐसा कोई व्यक्ति किसी को अजीब लग सकता है, मैं तुरंत समझाऊंगा कि विकसित बोर्ड एक AD7643 18-बिट एडीसी का उपयोग करता है)। फिर उन्हें 32-बिट फ्लोटिंग-पॉइंट फॉर्मेट में बदल दिया जाता है। यह मानक Alter मेगाफ़ंक्शन

int18_to_float32 का उपयोग करके किया जाता है। जोड़ और गुणा भी क्रमशः मानक कार्यों

sum_float32 और

mul_float32 द्वारा कार्यान्वित किया जाता है। आवश्यक गणना करने के बाद, परिणाम एक पूर्णांक 18-बिट संख्या में

float32_to_int18 फ़ंक्शन द्वारा परिवर्तित किया जाता है। पूर्व-गणना गुणांक का उपयोग करके, आप इस मॉड्यूल को कम-पास, उच्च-पास या बैंडपास फ़िल्टर में बदल सकते हैं।

क्वार्टस II 9.1 में प्रोजेक्ट आर्काइवपाठ में विकिपीडिया से पहले ही उल्लिखित पुस्तकों और आंकड़ों के अलावा, विषय लिखते समय,

संदर्भ गाइड सेमीकंडक्टर सर्किटरी का उपयोग किया गया था। टिट्ज़ डब्ल्यू।, शेंक के। और

स्ट्रक्चर्स ऑफ़ डिजिटल फिल्टर्स और उनकी विशेषताओंमैं बयान के कुछ भ्रम के लिए माफी मांगता हूं, क्योंकि साहित्यिक प्रतिभा कभी भी मेरी पहचान नहीं रही है, और आपके ध्यान के लिए धन्यवाद।