الصور والمواد والتقلبات والانعطافات لندوة MIPSfpga في MEPhI

في نهاية أكتوبر ، تم عقد ندوة حول MIPSfpga في MEPhI - وهي واحدة من سلسلة من الحلقات الدراسية التي نظمتها الجامعات الروسية مع Imagination Technologies ، و Microchip Technology بالشراكة مع Gamma St. Petersburg ، وممثلين عن Xilinx في روسيا ، بمشاركة متحدثين من MathWorks و NIISI. فيما يلي مزيج من الصور الفوتوغرافية وروابط للمواد وملاحظات حول إعداد الندوة والثقافة الأسطورية. أدناه صورة MEPhI خارج. تذكر كلمة "نووي" أن هناك مفاعلًا نوويًا في معهد الفيزياء الهندسية بموسكو ، لذا من الصعب الوصول إليه ، خاصة بجواز السفر الأمريكي - لقد حصلت على تصريح لمدة أسبوعين ، ووقع رئيس الجامعة طلب الندوة. عند المدخل يوجد مدفعي رشاش مع كلاشنيكوف (!) (لم يُسمح لي بتصوير المدفعي الآلي) ها أنا (يوري بانشول) مع منظمي الحلقة الدراسية الآخرين - إيجور إيفانوفيتش شاجورين وماكسيم جوربونوف: إيجور إيفانوفيتش شاجورين ، نائب. رئيس قسم الإلكترونيات الدقيقة والنانوية - مؤلف الكتب والمقالات حول المعالجات الدقيقة Intel و Motorola و PowerPC ، والعمل المخبري على MIPS . UPD: توضيح من رفيق من NIIIS:

(لم يُسمح لي بتصوير المدفعي الآلي) ها أنا (يوري بانشول) مع منظمي الحلقة الدراسية الآخرين - إيجور إيفانوفيتش شاجورين وماكسيم جوربونوف: إيجور إيفانوفيتش شاجورين ، نائب. رئيس قسم الإلكترونيات الدقيقة والنانوية - مؤلف الكتب والمقالات حول المعالجات الدقيقة Intel و Motorola و PowerPC ، والعمل المخبري على MIPS . UPD: توضيح من رفيق من NIIIS:

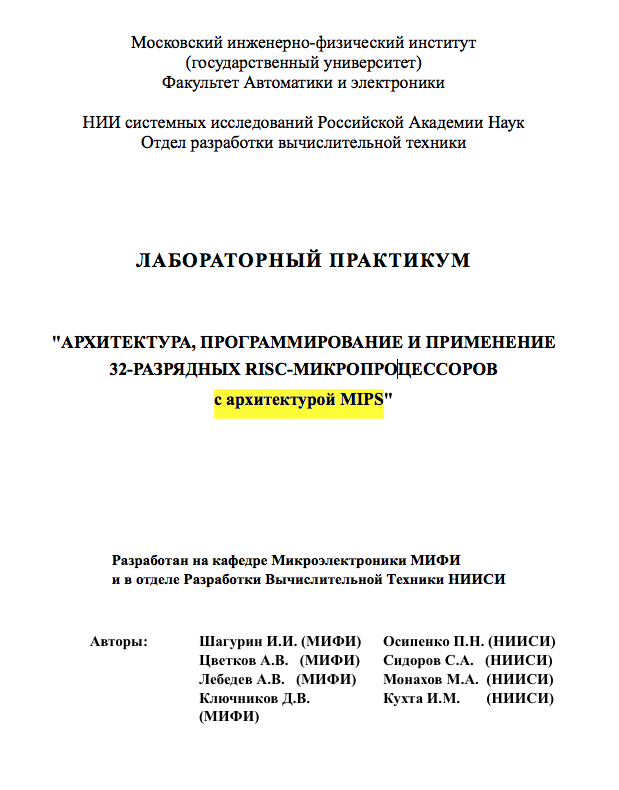

«, -32 -64 MIPS- — ( :) ). , — MIPS- . RISC , . MIPS-I. , , MIPS- , . , „ MIPS“ MIPS- . „

من المثير للاهتمام ، أن إيغور إيفانوفيتش شاجورين ذهب لتمثيل الإلكترونيات السوفيتية في مؤتمر في سان فرانسيسكو في السبعينيات ، عندما كان اتحاد الجمهوريات الاشتراكية السوفياتية دولة معزولة إلى حد ما. تم نقل المشاركين في مؤتمر VLSI في السبعينيات إلى Muir Woods ، المنطقة التي بها أعلى سيكويا على الأرض Sequoia sempervirens Maxim Gorbunov ، باحث من NIISI / SRISA ، وهو معهد يشارك في تطوير المعالجات الروسية مع بنية MIPS - COMDIV-32 و العمولة 64. تتخصص مكسيم في تصميم طوبولوجيا VLSI المقاومة للإشعاع وكانت الرئيس المشارك لأحد أقسام مؤتمر RADECS الدولي في موسكو:

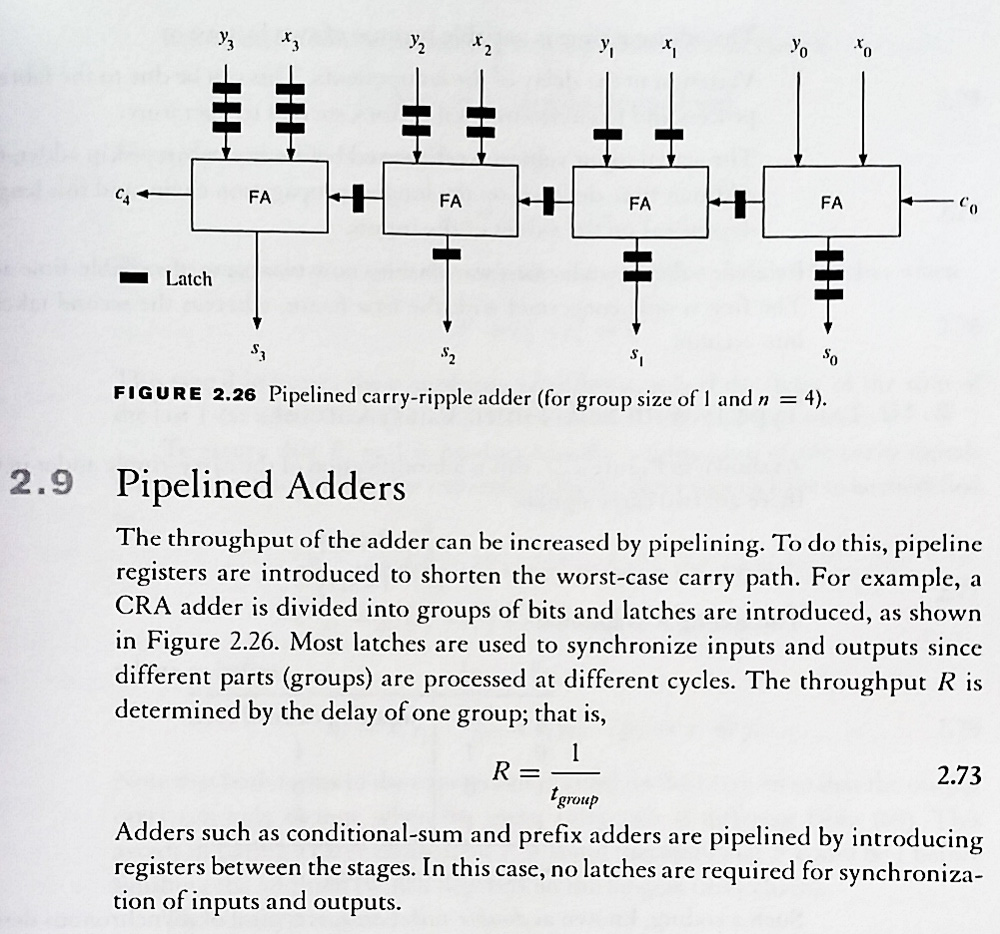

قبل ندوة MIPSfpga في MEPhI ، بدأ أحد المدربين ، إيجور كوزمين ، يسألني عن ظروف السباق في مخطط معين للحوسبة المتخصصة التي نشأت كمشروع طلابي. لست متأكدًا من أنني فهمت ذلك بشكل صحيح ، ولكني أعربت عن أنه في تصميم متزامن منظم بشكل صحيح ، لا تنشأ مثل هذه المشاكل ووعدت بإرسال صورة لصفحة من كتاب "الحساب الرقمي" كمثال، الذي يفهم تنظيم جامع خط الأنابيب ، والذي يحتوي على كمية صغيرة من المنطق التوافقي (مثلما هو الحال في المُصمم مع التحويل المتسلسل) ، ولكن في نفس الوقت يضع السجلات (D-triggers) بطريقة تمكن المُعلِن من بدء عملية إضافة جديدة في كل دورة ساعة ، بتردد إشارة على مدار الساعة ، يتم تحديدها من خلال تأخير مُجمِّع توافقي كامل بت واحد:Digital Arithmetic 1st Edition بواسطة Milos D. Ercegovac و Tomás Lang في نفس الوقت ، قمت بتصوير بضع صفحات حول الدوائر الذاتية غير المتزامنة ذاتيًا ، تتعلق أيضًا بهذه المشكلة .

قبل ندوة MIPSfpga في MEPhI ، بدأ أحد المدربين ، إيجور كوزمين ، يسألني عن ظروف السباق في مخطط معين للحوسبة المتخصصة التي نشأت كمشروع طلابي. لست متأكدًا من أنني فهمت ذلك بشكل صحيح ، ولكني أعربت عن أنه في تصميم متزامن منظم بشكل صحيح ، لا تنشأ مثل هذه المشاكل ووعدت بإرسال صورة لصفحة من كتاب "الحساب الرقمي" كمثال، الذي يفهم تنظيم جامع خط الأنابيب ، والذي يحتوي على كمية صغيرة من المنطق التوافقي (مثلما هو الحال في المُصمم مع التحويل المتسلسل) ، ولكن في نفس الوقت يضع السجلات (D-triggers) بطريقة تمكن المُعلِن من بدء عملية إضافة جديدة في كل دورة ساعة ، بتردد إشارة على مدار الساعة ، يتم تحديدها من خلال تأخير مُجمِّع توافقي كامل بت واحد:Digital Arithmetic 1st Edition بواسطة Milos D. Ercegovac و Tomás Lang في نفس الوقت ، قمت بتصوير بضع صفحات حول الدوائر الذاتية غير المتزامنة ذاتيًا ، تتعلق أيضًا بهذه المشكلة . ثم تعرفت على فلاديمير ديمنتييف ، الذي ، بالتعاون مع أندريه أندريانوف ، دميتري كوزلوفسكي ، ينظم دروسًا مختبرية في MEPhI لبرمجة وحدات التحكم الدقيقة Micropip PIC32MX. أخبرت فلاديمير أن البروفيسور أليكس دين من جامعة نورث كارولينا تعاون مع Imagination و Microchip و Digilent ويقوم الآن بتطوير دورة جديدة حول برمجة Micocontrollers Microchip PIC32MZتتضمن هذه الدورة RTOSs والاتصال الجديد للمتحكم الدقيق بالسحابة. يعتمد الميكروكونترولر PIC32MZ على نواة المعالج الدقيق MIPS microAptiv UP ، مثل تلك المستخدمة في MIPSfpga. لذلك ، بدأت في تحريض رفاق MEPhI على المشاركة في المراجعة والاختبار التجريبي (إذا شاءوا) لهذه الدورة: ولكن عد إلى ندوتنا. وكان موضوع الندوة MIPSfpga. ما هو:

ثم تعرفت على فلاديمير ديمنتييف ، الذي ، بالتعاون مع أندريه أندريانوف ، دميتري كوزلوفسكي ، ينظم دروسًا مختبرية في MEPhI لبرمجة وحدات التحكم الدقيقة Micropip PIC32MX. أخبرت فلاديمير أن البروفيسور أليكس دين من جامعة نورث كارولينا تعاون مع Imagination و Microchip و Digilent ويقوم الآن بتطوير دورة جديدة حول برمجة Micocontrollers Microchip PIC32MZتتضمن هذه الدورة RTOSs والاتصال الجديد للمتحكم الدقيق بالسحابة. يعتمد الميكروكونترولر PIC32MZ على نواة المعالج الدقيق MIPS microAptiv UP ، مثل تلك المستخدمة في MIPSfpga. لذلك ، بدأت في تحريض رفاق MEPhI على المشاركة في المراجعة والاختبار التجريبي (إذا شاءوا) لهذه الدورة: ولكن عد إلى ندوتنا. وكان موضوع الندوة MIPSfpga. ما هو:

MIPSfpga — MIPS microAptiv UP. Microchip PIC32MZ, « » — Samsung Artik 1.

MIPS microAptiv UP 25 , Verilog, , .

MIPS microAptiv UP — MIPSfpga — : (), () Field Programmable Gate Array (FPGA).

لذا ، تحدثت وتحدثت أولاً عن:1. تقنيات Imagination ووحدة الأعمال MIPS الخاصة بها2. البرامج التعليمية لتقنيات Imagination3. لتحديث مفهوم تدفق RTL إلى GDSII لأولئك الذين ليس لديهم Verilog / VHDL إلى التخصص: كيف يتم تصميم كتل وأنظمة IP على شريحة (SoC).4. لقد تحدثت قليلاً عن الأسطر الثلاثة لنوى المعالج الدقيق MIPS وبتفصيل أكبر عن خط النوى من فئة وحدة التحكم الدقيقة ، استنادًا إلى واحد منها (MIPS microAptiv UP) تم إنشاء حزمة MIPSfpga5. منذ أن تضمن أحد التمارين أيضًا إظهار ذاكرة التخزين المؤقت ، قلت زوجين الكلمات وحول ذاكرة التخزين المؤقت في MIPS microAptiv UP

بعد خطابي الأول ، ألقى ميخائيل بيسيلنيك ، متحدث من MathWorks خطابًا: نفذ ميخائيل بيسيلنيك مجموعة فرعية من MIPS على Simulink ، والتي تلقت نوعًا من الجائزة التحريرية MATLAB Central Pick of the Week: أظهر مثال Mikhail أنه بالنسبة للطالب يمكن دراسة الهندسة المعمارية والمعمارية الدقيقة لنوى المعالج بطرق مختلفة - على الأقل في Verilog و VHDL ، على الأقل بمساعدة نماذج C ، على الأقل بمساعدة Simulink. ولكن بعد دراسة أساسيات الهندسة المعمارية والهندسة المعمارية الدقيقة ، يجب على الطالب تجربة المعالج الصناعي ، وهنا يدخل MIPSfpga المشهد ، حيث:

بعد خطابي الأول ، ألقى ميخائيل بيسيلنيك ، متحدث من MathWorks خطابًا: نفذ ميخائيل بيسيلنيك مجموعة فرعية من MIPS على Simulink ، والتي تلقت نوعًا من الجائزة التحريرية MATLAB Central Pick of the Week: أظهر مثال Mikhail أنه بالنسبة للطالب يمكن دراسة الهندسة المعمارية والمعمارية الدقيقة لنوى المعالج بطرق مختلفة - على الأقل في Verilog و VHDL ، على الأقل بمساعدة نماذج C ، على الأقل بمساعدة Simulink. ولكن بعد دراسة أساسيات الهندسة المعمارية والهندسة المعمارية الدقيقة ، يجب على الطالب تجربة المعالج الصناعي ، وهنا يدخل MIPSfpga المشهد ، حيث:

- يمكن للطلاب بناء نماذجهم الأولية للأنظمة على شريحة ، والجمع بين قلب المعالج الدقيق والذاكرة وأجهزة الإدخال / الإخراج المصممة من قبلهم

- , . « ».

- , , .

ولكن من أجل تجربة تطورات SoC ومع النواة ، يجب أن يكون لديهم قيادة جيدة للأداة / أداة التنفيذ. لذلك ، بعد ميخائيل ميخائيل فيليبوف ، مهندس التطبيقات من Macro Group ، الممثل الرسمي لشركة Xilinx في روسيا ، تحدث. Xilinx هي الشركة التي اخترعت مرة واحدة FPGAs وحتى يومنا هذا لا تزال رقم 1 في أكثر FPGAs عالية السرعة.قدم ألكسندر فيليبوف تقريرين:- FPGAs 7-Series الجديدة و MPSoC UltraScale - منتجات XILINX لأنظمة الشرائح القوية القابلة للبرمجة

- XILINX VIVADO بيئة تصميم لإنشاء أنظمة على رقاقة

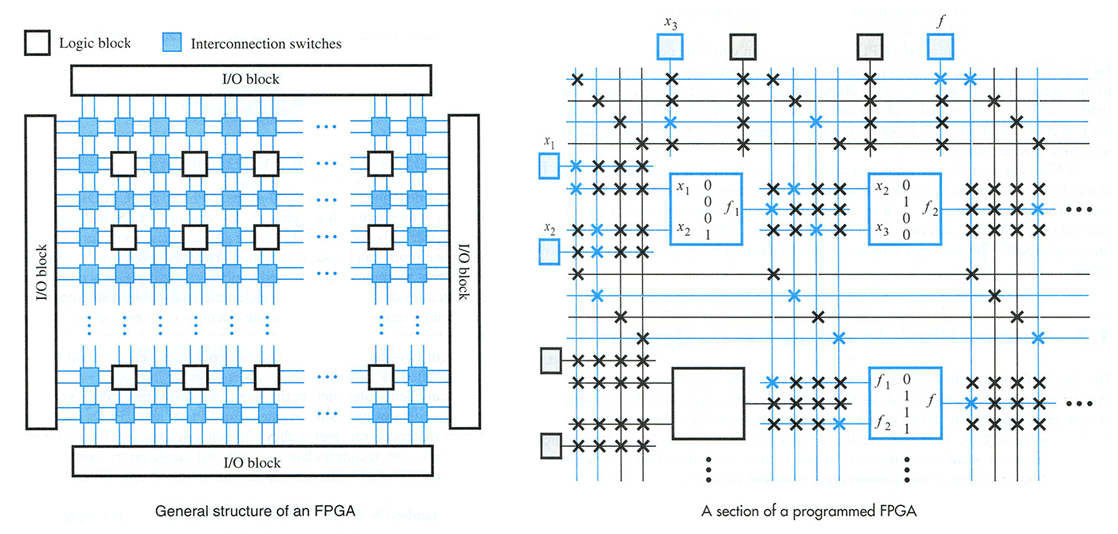

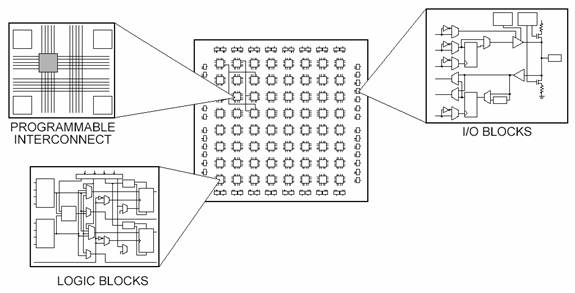

ما أوضحته FPGA / FPGA على الأصابع في منشور آخر على Habr - كيفية بدء تطوير الحديد باستخدام FPGAs - تعليمات خطوة بخطوة . لكن دعنا نكرر هذه المعلومات مرة أخرى:في أبسط إصدار ، يتكون FPGA من مصفوفة من الخلايا المتجانسة ، يمكن تغيير كل منها للعمل باستخدام معددات متصلة بتفاصيل ذاكرة التكوين. يمكن أن تصبح خلية واحدة بوابة AND بأربعة مدخلات وإخراج واحد ، وآخر - تسجيل بت واحد ، إلخ. نقوم بتحميل سلسلة من البتات من الذاكرة إلى ذاكرة التكوين - ويتم تشكيل الدائرة الإلكترونية المعينة في FPGA ، والتي يمكن أن تكون معالجًا ، وحدة تحكم في العرض ، إلخ.FPGAs / FPGAs ليست معالجات ؛ من خلال "برمجة" FPGAs (ملء ذاكرة التكوين الخاصة بـ FPGAs) تقوم بإنشاء دائرة إلكترونية (الأجهزة) ، بينما عند برمجة معالج (جهاز ثابت) ، تنزلق سلسلة من تعليمات البرنامج المتسلسلة المكتوبة فيه (البرمجيات).فيما يلي رسم تخطيطي لأبسط وحدة FPGA ، والتي تتضمن جدول بحث (LUT) وقلب. صحيح ، في هذا المخطط ، لا يتم عرض معددات الإرسال التي تغير وظيفة الخلية ، والاتصالات بذاكرة التكوين.

ما أوضحته FPGA / FPGA على الأصابع في منشور آخر على Habr - كيفية بدء تطوير الحديد باستخدام FPGAs - تعليمات خطوة بخطوة . لكن دعنا نكرر هذه المعلومات مرة أخرى:في أبسط إصدار ، يتكون FPGA من مصفوفة من الخلايا المتجانسة ، يمكن تغيير كل منها للعمل باستخدام معددات متصلة بتفاصيل ذاكرة التكوين. يمكن أن تصبح خلية واحدة بوابة AND بأربعة مدخلات وإخراج واحد ، وآخر - تسجيل بت واحد ، إلخ. نقوم بتحميل سلسلة من البتات من الذاكرة إلى ذاكرة التكوين - ويتم تشكيل الدائرة الإلكترونية المعينة في FPGA ، والتي يمكن أن تكون معالجًا ، وحدة تحكم في العرض ، إلخ.FPGAs / FPGAs ليست معالجات ؛ من خلال "برمجة" FPGAs (ملء ذاكرة التكوين الخاصة بـ FPGAs) تقوم بإنشاء دائرة إلكترونية (الأجهزة) ، بينما عند برمجة معالج (جهاز ثابت) ، تنزلق سلسلة من تعليمات البرنامج المتسلسلة المكتوبة فيه (البرمجيات).فيما يلي رسم تخطيطي لأبسط وحدة FPGA ، والتي تتضمن جدول بحث (LUT) وقلب. صحيح ، في هذا المخطط ، لا يتم عرض معددات الإرسال التي تغير وظيفة الخلية ، والاتصالات بذاكرة التكوين. الرسوم البيانية التي توضح هيكل FPGA:

الرسوم البيانية التي توضح هيكل FPGA: وآخر:

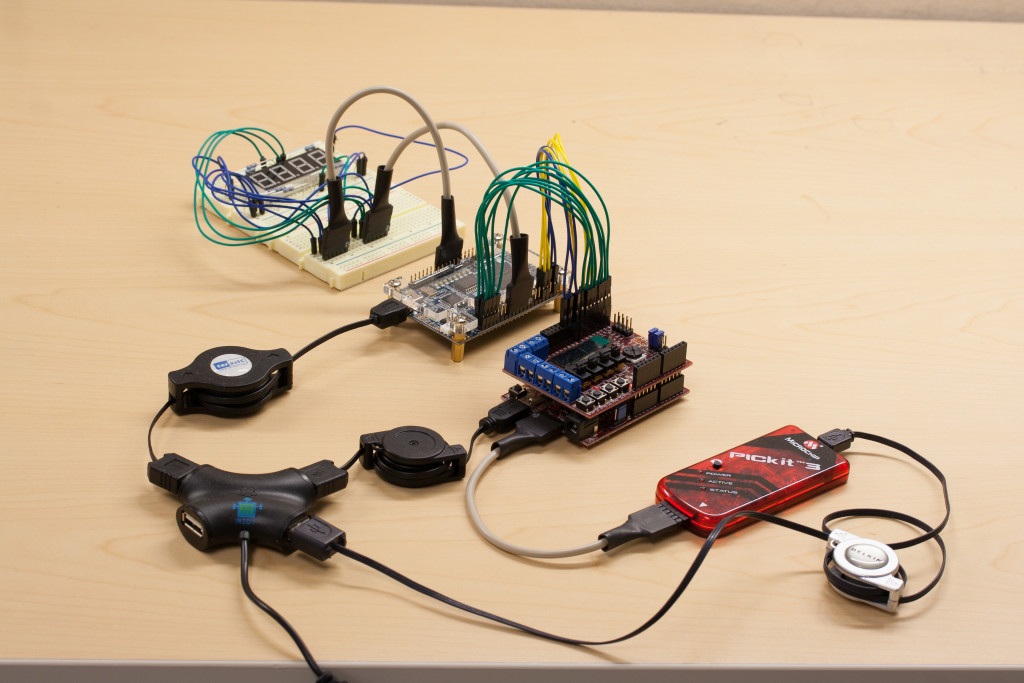

وآخر: بعد الغداء في غرفة الطعام في معهد موسكو للفيزياء الهندسية ، بدأنا الجزء العملي. في البداية ، عندما عقدت Imagination Technologies و Xilinx مثل هذه الحلقة الدراسية في لوس أنجلوس ، استخدمواشرائح أعدها الأساتذة ديفيد وسارة هاريس من جنوب كاليفورنيا . كما بدا في الأصل ، يمكنك أن ترى في الفيديو:جميع مقاطع الفيديو الثمانية منورشة لوس أنجلوس للندوات في روسيا ، يجب تعديل روابط هاريس الأساسية والمخبرية بشكل كبير. يمكن العثور على التعديلات على https://github.com/MIPSfpga/mipsfpga-plus . تشمل الاختلافات:1. يتم فرز كل شيء للوحات الأم الرخيصة من Altera ، والمتوفر في روسيا بدون جرار تصدير واستيراد2. تم تحميل البرنامج في نظام مركب دون استخدام BusBlaster ، ببساطة من خلال UART3. مستشعر الضوء كجهاز طرفي بدلاً من شاشة LCD4. قابل للتحويل إشارة ساعة تردد منخفضة للغاية ، مما يسمح للمختبرات بتصور تشغيل أي معالج داخلي5. تمت إضافة مختبر بسيط لتصور أخطاء التخزين المؤقت+ كل شيء صغير ومستحضرات التجميل - أداة تحميل / أداة تحميل أكثر إحكاما ، وإمكانية المعاملات الضيقة غير القابلة للتخزين المؤقت إلى الذاكرة ، إلخ.مزيد من التفاصيل:1. النقل تحت Alteraبادئ ذي بدء ، أظهرت شرائح هاريس كل شيء لـ Xilinx ، ومؤخرًا ، أصبحت لوحات الشحن من Xilinx FPGAs إلى روسيا إجراء بيروقراطيًا معقدًا إلى حد ما يستغرق 3-4 أشهر. حدث الشيء نفسه مع ترخيص البرنامج للتوليف و Xilinx Vivado للمكان والطريق ، حتى مع التراخيص المجانية. لم يكن لدى بعض الجامعات الروسية لوحات Xilinx أو تراخيص Vivado. كان لدى الآخرين الترخيص القديم فقط لسلف Vivado - برنامج ISE 2013 ، الذي لم يدعم FPGAs على اللوحات التي قمت بنقلها في روسيا.باختصار ، بالنسبة للحلقات الدراسية في روسيا ، قمنا أنا والرفاق في كاليفورنيا بنقل MIPSfpga إلى اثنين من اللوحات الرخيصة المتاحة في روسيا من منافس Xilinx المنافس Altera (هذه الشركة تندمج الآن مع Intel). تم التبرع بألواح Alter لتلبية احتياجات ورشة العمل من قبل شركة Zelenograd SPC Elvis . كانت اللوحة الرئيسية في MEPhI و MIPT و SSAU هي Terasic DE0-CV استنادًا إلى Altera Cyclone V: لوحة أخرى كانت Terasic DE0-Nano - شال صغير للغاية مناسب لمشاريع مثل الروبوتات الطائرة ، ولكن مع كمية صغيرة من الأجهزة الطرفية على متنها: Terasic DE0- عيب نانو هو عدد صغير من الأجهزة الطرفية على اللوحة نفسها ، ولكنه أيضًا ميزة ، حيث يمكن توصيل DE0-Nano كمصمم مع لوحات أخرى ومدمجة في أجهزة مختلفة:

بعد الغداء في غرفة الطعام في معهد موسكو للفيزياء الهندسية ، بدأنا الجزء العملي. في البداية ، عندما عقدت Imagination Technologies و Xilinx مثل هذه الحلقة الدراسية في لوس أنجلوس ، استخدمواشرائح أعدها الأساتذة ديفيد وسارة هاريس من جنوب كاليفورنيا . كما بدا في الأصل ، يمكنك أن ترى في الفيديو:جميع مقاطع الفيديو الثمانية منورشة لوس أنجلوس للندوات في روسيا ، يجب تعديل روابط هاريس الأساسية والمخبرية بشكل كبير. يمكن العثور على التعديلات على https://github.com/MIPSfpga/mipsfpga-plus . تشمل الاختلافات:1. يتم فرز كل شيء للوحات الأم الرخيصة من Altera ، والمتوفر في روسيا بدون جرار تصدير واستيراد2. تم تحميل البرنامج في نظام مركب دون استخدام BusBlaster ، ببساطة من خلال UART3. مستشعر الضوء كجهاز طرفي بدلاً من شاشة LCD4. قابل للتحويل إشارة ساعة تردد منخفضة للغاية ، مما يسمح للمختبرات بتصور تشغيل أي معالج داخلي5. تمت إضافة مختبر بسيط لتصور أخطاء التخزين المؤقت+ كل شيء صغير ومستحضرات التجميل - أداة تحميل / أداة تحميل أكثر إحكاما ، وإمكانية المعاملات الضيقة غير القابلة للتخزين المؤقت إلى الذاكرة ، إلخ.مزيد من التفاصيل:1. النقل تحت Alteraبادئ ذي بدء ، أظهرت شرائح هاريس كل شيء لـ Xilinx ، ومؤخرًا ، أصبحت لوحات الشحن من Xilinx FPGAs إلى روسيا إجراء بيروقراطيًا معقدًا إلى حد ما يستغرق 3-4 أشهر. حدث الشيء نفسه مع ترخيص البرنامج للتوليف و Xilinx Vivado للمكان والطريق ، حتى مع التراخيص المجانية. لم يكن لدى بعض الجامعات الروسية لوحات Xilinx أو تراخيص Vivado. كان لدى الآخرين الترخيص القديم فقط لسلف Vivado - برنامج ISE 2013 ، الذي لم يدعم FPGAs على اللوحات التي قمت بنقلها في روسيا.باختصار ، بالنسبة للحلقات الدراسية في روسيا ، قمنا أنا والرفاق في كاليفورنيا بنقل MIPSfpga إلى اثنين من اللوحات الرخيصة المتاحة في روسيا من منافس Xilinx المنافس Altera (هذه الشركة تندمج الآن مع Intel). تم التبرع بألواح Alter لتلبية احتياجات ورشة العمل من قبل شركة Zelenograd SPC Elvis . كانت اللوحة الرئيسية في MEPhI و MIPT و SSAU هي Terasic DE0-CV استنادًا إلى Altera Cyclone V: لوحة أخرى كانت Terasic DE0-Nano - شال صغير للغاية مناسب لمشاريع مثل الروبوتات الطائرة ، ولكن مع كمية صغيرة من الأجهزة الطرفية على متنها: Terasic DE0- عيب نانو هو عدد صغير من الأجهزة الطرفية على اللوحة نفسها ، ولكنه أيضًا ميزة ، حيث يمكن توصيل DE0-Nano كمصمم مع لوحات أخرى ومدمجة في أجهزة مختلفة:

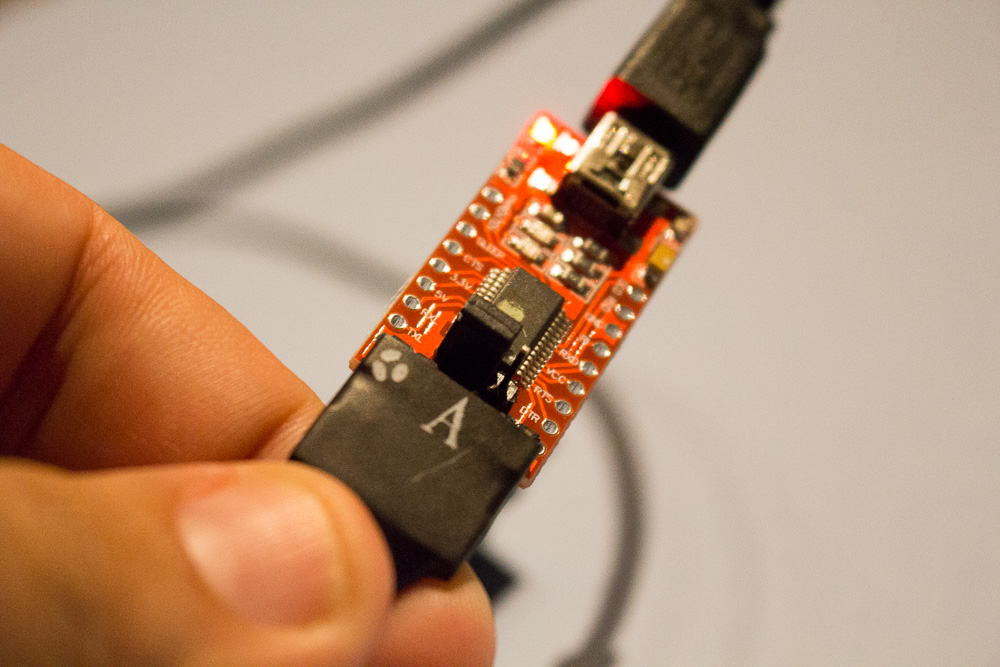

2. التنزيل عبر UART كانتمشكلة الشريحة الثانية من Harris هي استخدام مهايئ التصحيح Bus Busaster وبرنامجه المسمى OpenOCD . في الأساس ، BusBlaster / OpenOCD هو حل جيد من نوعه. لا يسمح فقط بتحميل البرامج في النظام الذي تم توليفه داخل FPGA ، ولكن أيضًا تصحيحها عن بُعد عبر واجهة EJTAG ، وهي وظيفة إضافية بمستوى أعلى عبر واجهة JTAG. في الوقت نفسه ، يكلف BusBlaster 43 دولارًا فقط ، وهو أرخص بكثير من محولات التصحيح الصناعي EJTAG.لسوء الحظ ، فإن تركيبة BusBlaster / OpenOCD غير دقيقة تمامًا ، وكنت أخشى ألا تعمل على بعض تكوينات الكمبيوتر غير المتوقعة في روسيا (كنت على حق - لم تعمل في MIPT و SSAU). الى جانب ذلك ،على موقع يبيع مجموعة BusBlaster / OpenOCD لـ MIPS ، تنفد اللوحات أحيانًا.لهذا السبب ولأسباب أخرى ، بدأت في البحث عن طرق أخرى لتحميل البرامج في النظام (في FPGA ، تحتاج إلى تحميل التكوين / الأجهزة والبرامج للمعالج بشكل منفصل (في نظام مركب مع معالج)). حاول ترول الإنترنت المجهول أليكسي أن يضعني في وضع ضعيف لفترة طويلة ، حتى أتمكن من تنفيذ محمل إقلاع EJTAG من خلال Altera USB Blaster ، ولكن نظرًا لأنني لست خبيرًا في EJTAG ، اخترت حلًا بسيطًا يعمل منذ الحقبة السوفيتية - لتحميل البرنامج من خلال المنفذ التسلسلي / UART. صحيح ، خلال الحقبة السوفيتية كان هناك منفذ RS-232C ، وفي التسعينات ظهرت رقائق FTDI ، مما جعل من الممكن القيام بكل شيء من خلال كابل USB متصل بجهاز الكمبيوتر. يمكن شراء أشكال مختلفة من هذا المحول مقابل 5 دولارات في موسكو وأقل من 2 دولار عبر الإنترنت من الصين:

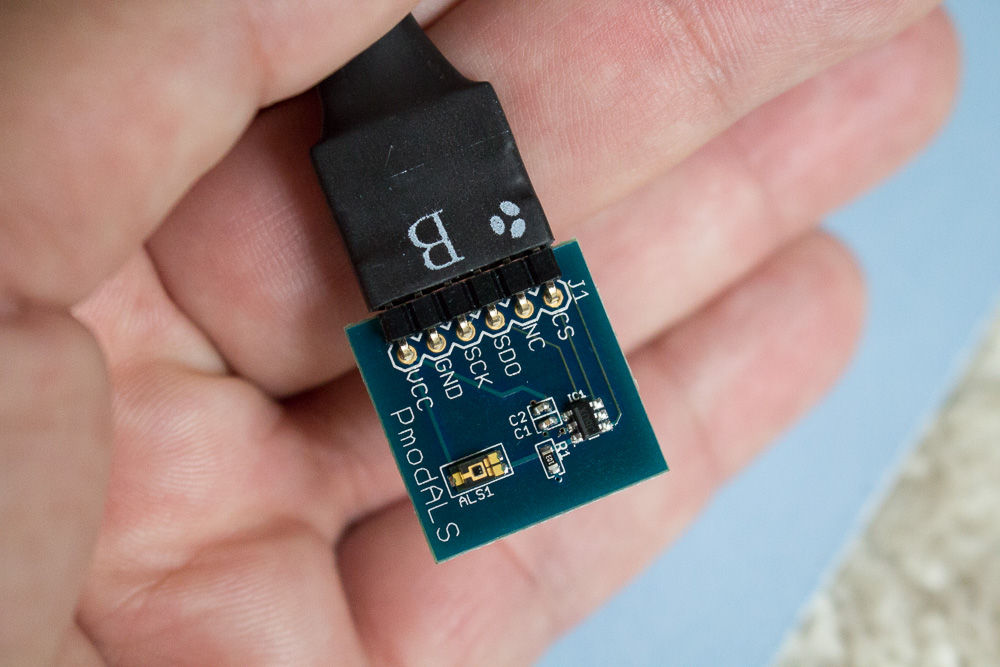

2. التنزيل عبر UART كانتمشكلة الشريحة الثانية من Harris هي استخدام مهايئ التصحيح Bus Busaster وبرنامجه المسمى OpenOCD . في الأساس ، BusBlaster / OpenOCD هو حل جيد من نوعه. لا يسمح فقط بتحميل البرامج في النظام الذي تم توليفه داخل FPGA ، ولكن أيضًا تصحيحها عن بُعد عبر واجهة EJTAG ، وهي وظيفة إضافية بمستوى أعلى عبر واجهة JTAG. في الوقت نفسه ، يكلف BusBlaster 43 دولارًا فقط ، وهو أرخص بكثير من محولات التصحيح الصناعي EJTAG.لسوء الحظ ، فإن تركيبة BusBlaster / OpenOCD غير دقيقة تمامًا ، وكنت أخشى ألا تعمل على بعض تكوينات الكمبيوتر غير المتوقعة في روسيا (كنت على حق - لم تعمل في MIPT و SSAU). الى جانب ذلك ،على موقع يبيع مجموعة BusBlaster / OpenOCD لـ MIPS ، تنفد اللوحات أحيانًا.لهذا السبب ولأسباب أخرى ، بدأت في البحث عن طرق أخرى لتحميل البرامج في النظام (في FPGA ، تحتاج إلى تحميل التكوين / الأجهزة والبرامج للمعالج بشكل منفصل (في نظام مركب مع معالج)). حاول ترول الإنترنت المجهول أليكسي أن يضعني في وضع ضعيف لفترة طويلة ، حتى أتمكن من تنفيذ محمل إقلاع EJTAG من خلال Altera USB Blaster ، ولكن نظرًا لأنني لست خبيرًا في EJTAG ، اخترت حلًا بسيطًا يعمل منذ الحقبة السوفيتية - لتحميل البرنامج من خلال المنفذ التسلسلي / UART. صحيح ، خلال الحقبة السوفيتية كان هناك منفذ RS-232C ، وفي التسعينات ظهرت رقائق FTDI ، مما جعل من الممكن القيام بكل شيء من خلال كابل USB متصل بجهاز الكمبيوتر. يمكن شراء أشكال مختلفة من هذا المحول مقابل 5 دولارات في موسكو وأقل من 2 دولار عبر الإنترنت من الصين: سألاحظ على الفور أنه يمكنك تحميل البرامج في شركة نفط الجنوب المركبة بطرق مختلفة. في أحدها ، الأكثر تقليدية ، يحتوي النظام على برنامج صغير ثابت في الذاكرة (أداة تحميل التشغيل) ، والذي يبدأ بعد إعادة تعيين النظام وتحميل برنامج أكبر من خلال منفذ UART / التسلسلي. تم استخدام هذه الطريقة من قبل أنطون بافلوف من NIIIS ، الذي أظهرها في ندوات في جامعة موسكو الحكومية ومعهد موسكو للفيزياء الهندسية ، وكتب عنه أيضًا في أوقات المهوسات "MIPSfpga: خارج الشريعة" .لقد قمت بالتحميل بطريقة بديلة ، حيث تمتلئ الذاكرة بجهاز حالة ، يتم تنفيذها بالكامل في الأجهزة. يقبل الجهاز ملفًا نصيًا بتنسيق Motorola S-Record من جهاز كمبيوتر عبر UART، يوزعها (كل شيء في الجهاز) ويملأ الذاكرة بالبيانات ، بينما يكون المعالج في حالة إعادة الضبط. ثم يستيقظ المعالج ويبدأ في قراءة البرنامج من ذاكرة النظام. كل ما يجب القيام به على جانب الكمبيوتر الشخصي هو تحويل ملف ELF القابل للتنفيذ إلى تنسيق Motorola S-Record وإرساله إلى منفذ COM الظاهري باستخدام الأمر "type" windows-shell.3. مستشعر الضوء كمحيط بدلاً من شاشة LCDفي مختبرات هاريس الأصلية ، استخدموا مؤشرًا من سبعة أجزاء وشاشة LCD SPI كأمثلة على الأجهزة الطرفية. مثال على مؤشر مكون من سبعة أجزاء هو ممل - أي طالب يفهم أنه إذا كنت تعرف كيف تومض بضوء واحد ، فأنت تعرف كيف يومض بسبعة أضواء. مثال SPI أفضل قليلاً ، خاصة عندما يتعلق الأمر بالطلاب المبتدئين ، ولكن لماذا نحتاج إلى عرض ثانٍ إذا كان هناك بالفعل مؤشر من سبعة أجزاء؟ باختصار ، قبل السفر إلى روسيا ، اشتريت 20 مستشعرًا للضوء ، أيضًا بواجهة SPI ، واستخدمتها بدلاً من شاشات العرض: في نفس الوقت ، الواجهة بسيطة جدًا - إليك وحدة الواجهة التي كتبتها (ملاحظة: لا يحتوي هذا الرمز على جميع تعديلات النظام لإقرانه مع ناقل AHB-Lite ، بحيث يرى البرنامج القيمة):

سألاحظ على الفور أنه يمكنك تحميل البرامج في شركة نفط الجنوب المركبة بطرق مختلفة. في أحدها ، الأكثر تقليدية ، يحتوي النظام على برنامج صغير ثابت في الذاكرة (أداة تحميل التشغيل) ، والذي يبدأ بعد إعادة تعيين النظام وتحميل برنامج أكبر من خلال منفذ UART / التسلسلي. تم استخدام هذه الطريقة من قبل أنطون بافلوف من NIIIS ، الذي أظهرها في ندوات في جامعة موسكو الحكومية ومعهد موسكو للفيزياء الهندسية ، وكتب عنه أيضًا في أوقات المهوسات "MIPSfpga: خارج الشريعة" .لقد قمت بالتحميل بطريقة بديلة ، حيث تمتلئ الذاكرة بجهاز حالة ، يتم تنفيذها بالكامل في الأجهزة. يقبل الجهاز ملفًا نصيًا بتنسيق Motorola S-Record من جهاز كمبيوتر عبر UART، يوزعها (كل شيء في الجهاز) ويملأ الذاكرة بالبيانات ، بينما يكون المعالج في حالة إعادة الضبط. ثم يستيقظ المعالج ويبدأ في قراءة البرنامج من ذاكرة النظام. كل ما يجب القيام به على جانب الكمبيوتر الشخصي هو تحويل ملف ELF القابل للتنفيذ إلى تنسيق Motorola S-Record وإرساله إلى منفذ COM الظاهري باستخدام الأمر "type" windows-shell.3. مستشعر الضوء كمحيط بدلاً من شاشة LCDفي مختبرات هاريس الأصلية ، استخدموا مؤشرًا من سبعة أجزاء وشاشة LCD SPI كأمثلة على الأجهزة الطرفية. مثال على مؤشر مكون من سبعة أجزاء هو ممل - أي طالب يفهم أنه إذا كنت تعرف كيف تومض بضوء واحد ، فأنت تعرف كيف يومض بسبعة أضواء. مثال SPI أفضل قليلاً ، خاصة عندما يتعلق الأمر بالطلاب المبتدئين ، ولكن لماذا نحتاج إلى عرض ثانٍ إذا كان هناك بالفعل مؤشر من سبعة أجزاء؟ باختصار ، قبل السفر إلى روسيا ، اشتريت 20 مستشعرًا للضوء ، أيضًا بواجهة SPI ، واستخدمتها بدلاً من شاشات العرض: في نفس الوقت ، الواجهة بسيطة جدًا - إليك وحدة الواجهة التي كتبتها (ملاحظة: لا يحتوي هذا الرمز على جميع تعديلات النظام لإقرانه مع ناقل AHB-Lite ، بحيث يرى البرنامج القيمة):

4. تحولتالساعة إلى تردد منخفض للغاية عندما ظهر MIPSfpga وبدأ أساتذة الجامعات الروسية بدراستها ، بدأ بعضهم يشكون من أن الحزمة في شكلها الأصلي ليست مثيرة للاهتمام للغاية للطلاب المتقدمين ، حيث أن المختبرات التي أعدها ديفيد وسارة هاريس تستخدم معالجًا مثل "الصندوق الأسود" ، ما عليك سوى توصيل الأجهزة به. وبعبارة أخرى ، تجاهل هاريس تمامًا أن المعالج مذكور في شفرة المصدر ، وبالتالي فمن الممكن تنفيذ المعامل معه التي تسمح بإخراج الاتصالات من سجلات المعالج التعسفي (ليس فقط السجلات المرئية للمبرمج ، ولكن بشكل عام من أي مشغلات D) ، للاتصال على سبيل المثال ، لمصابيح LED ، ولاحظ ما يحدث للمعالج عند تنفيذ برامج معينة.كما تفهم ، من أجل جعل هذه الملاحظات "مباشرة" ، من الضروري جعل المعالج يعمل على تردد ساعة منخفض جدًا ، على سبيل المثال ، ساعة في الثانية. كيف افعلها؟ يمكن أن يعمل نواة MIPS microAptiv UP المنفذة في ASIC على تقنية 28 نانومتر على ترددات أعلى من 500 ميجاهرتز ، وعلى تقنية 65 نانومتر أكثر من 300 ميجاهرتز. عند تنفيذها على FPGA ، تكون الترددات أقل بكثير ، ولكنها لا تزال عالية - 50-60 ميجاهرتز. ترددات مولدات إشارة الساعة على الألواح هي 50-100 ميجا هرتز ، مع إمكانية زيادة أو تقليل التردد باستخدام حلقة قفل الطور (PLL) / حلقة قفل الطور (PLL) .لسوء الحظ ، باستخدام PLL ، يمكنك تقليل التردد إلى 100 كيلوهرتز تقريبًا ، لكنك تحتاج إلى تقليل التردد إلى 1 هرتز بطريقة أخرى. في البداية حاولت القيام بذلك باستخدام كتلة من Altera تسمىALTCLKCTRL ، ولكن لسبب ما لم يعمل. ثم حاولت تقسيم إشارة الساعة باستخدام عداد ، ولكن (كنت أعرف ذلك بالفعل) هذا الحل في حد ذاته لا يعمل ، لأن المُركِّب لا يفهم أن إشارة الإخراج هي إشارة ساعة وتبدأ في تقسيمها بشكل غير صحيح ، ونتيجة لذلك لا يعمل المعالج. لقد استشرت العديد من الرفاق وبدأنا في استخدام الماكرو Alter "العالمي" (وما يعادله في Xilinx BUFG). 5. إضافة مخبأ بسيط لمختبر التصور

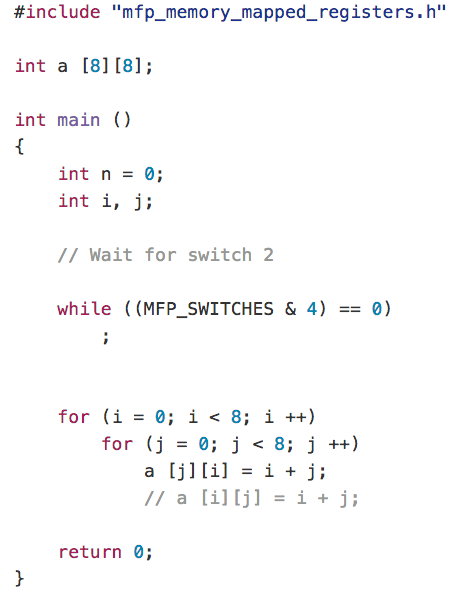

4. تحولتالساعة إلى تردد منخفض للغاية عندما ظهر MIPSfpga وبدأ أساتذة الجامعات الروسية بدراستها ، بدأ بعضهم يشكون من أن الحزمة في شكلها الأصلي ليست مثيرة للاهتمام للغاية للطلاب المتقدمين ، حيث أن المختبرات التي أعدها ديفيد وسارة هاريس تستخدم معالجًا مثل "الصندوق الأسود" ، ما عليك سوى توصيل الأجهزة به. وبعبارة أخرى ، تجاهل هاريس تمامًا أن المعالج مذكور في شفرة المصدر ، وبالتالي فمن الممكن تنفيذ المعامل معه التي تسمح بإخراج الاتصالات من سجلات المعالج التعسفي (ليس فقط السجلات المرئية للمبرمج ، ولكن بشكل عام من أي مشغلات D) ، للاتصال على سبيل المثال ، لمصابيح LED ، ولاحظ ما يحدث للمعالج عند تنفيذ برامج معينة.كما تفهم ، من أجل جعل هذه الملاحظات "مباشرة" ، من الضروري جعل المعالج يعمل على تردد ساعة منخفض جدًا ، على سبيل المثال ، ساعة في الثانية. كيف افعلها؟ يمكن أن يعمل نواة MIPS microAptiv UP المنفذة في ASIC على تقنية 28 نانومتر على ترددات أعلى من 500 ميجاهرتز ، وعلى تقنية 65 نانومتر أكثر من 300 ميجاهرتز. عند تنفيذها على FPGA ، تكون الترددات أقل بكثير ، ولكنها لا تزال عالية - 50-60 ميجاهرتز. ترددات مولدات إشارة الساعة على الألواح هي 50-100 ميجا هرتز ، مع إمكانية زيادة أو تقليل التردد باستخدام حلقة قفل الطور (PLL) / حلقة قفل الطور (PLL) .لسوء الحظ ، باستخدام PLL ، يمكنك تقليل التردد إلى 100 كيلوهرتز تقريبًا ، لكنك تحتاج إلى تقليل التردد إلى 1 هرتز بطريقة أخرى. في البداية حاولت القيام بذلك باستخدام كتلة من Altera تسمىALTCLKCTRL ، ولكن لسبب ما لم يعمل. ثم حاولت تقسيم إشارة الساعة باستخدام عداد ، ولكن (كنت أعرف ذلك بالفعل) هذا الحل في حد ذاته لا يعمل ، لأن المُركِّب لا يفهم أن إشارة الإخراج هي إشارة ساعة وتبدأ في تقسيمها بشكل غير صحيح ، ونتيجة لذلك لا يعمل المعالج. لقد استشرت العديد من الرفاق وبدأنا في استخدام الماكرو Alter "العالمي" (وما يعادله في Xilinx BUFG). 5. إضافة مخبأ بسيط لمختبر التصور يمكنك الآن إجراء تجارب مسلية - على سبيل المثال ، لجعل LED يومض أثناء عدم وجود ذاكرة تخزين مؤقت ، ثم لاحظ في الوقت الحقيقي أن ذاكرة التخزين المؤقت تصل وتخطئ عند ملء صفيف ثنائي الأبعاد. إذا قمت بملء مجموعة المصفوفة سطرًا تلو الآخر ، فستكون الومضات مختلفة عما لو قمت بملء الأعمدة: تجدر الإشارة إلى أنه ليس كل شيء يسير بسلاسة:

يمكنك الآن إجراء تجارب مسلية - على سبيل المثال ، لجعل LED يومض أثناء عدم وجود ذاكرة تخزين مؤقت ، ثم لاحظ في الوقت الحقيقي أن ذاكرة التخزين المؤقت تصل وتخطئ عند ملء صفيف ثنائي الأبعاد. إذا قمت بملء مجموعة المصفوفة سطرًا تلو الآخر ، فستكون الومضات مختلفة عما لو قمت بملء الأعمدة: تجدر الإشارة إلى أنه ليس كل شيء يسير بسلاسة: 1. GPIO في DE0-Nano يختلف عن GPIO في DE0-CV وألواح Xilinx. على وجه الخصوص ، لسبب ما ، لم أتمكن من إعلان منفذ GPIO بالكامل كمنفذ واحد ثم استخدم بتاته الفردية إما كمدخل أو كمخرج. على الرغم من أن DE0-CV تسير على ما يرام. لم يكن لدي الوقت لتقسيم مخرجات GPIO المختلفة بين الإشارات المنطقية المختلفة (على Verilog) ، لذلك لم أقم بفرز المعمل باستخدام مستشعر الضوء على DE0-Nano. لنفس السبب ، لم أقم بتصدير الواجهة مع Bus Blaster إلى DE0-CV.2. الأسوأ من ذلك ، التنزيل عبر UART لـ DE0-Nano لم يعمل في MEPhI ، على الرغم من أنه قبل ذلك كان يعمل في جامعة موسكو الحكومية وعلى جهاز الكمبيوتر المحمول الخاص بي. السبب لا يزال غير واضح بنسبة 100٪:2.1. ربما كانت هناك مشكلة عدم توافق إصدار Windows (7 مع التصحيح) وكابل USB إلى UART المستخدم لـ DE0-Nano. كان الكابل عبارة عن استنساخ كبل صيني رخيص استنادًا إلى شرائح PL2303TA ، على الرغم من أنني لم أجربه قبل الندوة. من المعروف أن الإصدار السابق من هذه الكبلات المستند إلى شرائح مع PL2303HX واجه مشكلة في التوافق مع Windows 8 ( انظر ). أبشع ما لدي مع جهاز كمبيوتر محمول مع إصدار من Windows 7 ، وجهاز كمبيوتر محمول مع إصدار من Windows 8 ، وبدائل مختلفة لهذا السلك. لكنني لم أتحقق من جميع المجموعات قبل الندوة ، على الرغم من أنني كنت قد فعلت ذلك في المساء السابق - للأسف.2.2. قبل ورشة العمل بيومين ، أجريت تغييرات على مقسم الساعة. لم يكن يستحق القيام به سواء.2.3. حسنًا ، عمل كل شيء على الأقل بشكل جيد على DE0-CV.3. في MEPhI ، عرضت نسخة أكثر تعقيدًا من مثال ذاكرة التخزين المؤقت أكثر من ذي قبل في جامعة موسكو الحكومية. لقد كان خطأ - في مثال معقد ، قام المترجم بتحسين شيء ما ، ولم يكن نمط الأضواء واضحًا كما هو الحال في المثال البسيط الأصلي. تم حفظ الوضع إلى حد ما من قبل المتحدث الإضافي المدعو من NIIMI Anton Pavlov ، الذي ، على الرغم من أنه لم يكن لديه الوقت في MEPhI ، أظهر بعضًا يقدم نسخته الخاصة من ربط MIPSfpga المسمى myMIPSfpga ، والذي وصفه أيضًا في الملاحظة "MIPSfpga: خارج الشريعة" . من بين أمور أخرى ، قام أنطون بنقل MIPSfpga إلى لوحة Mars rover 3 الروسية

1. GPIO في DE0-Nano يختلف عن GPIO في DE0-CV وألواح Xilinx. على وجه الخصوص ، لسبب ما ، لم أتمكن من إعلان منفذ GPIO بالكامل كمنفذ واحد ثم استخدم بتاته الفردية إما كمدخل أو كمخرج. على الرغم من أن DE0-CV تسير على ما يرام. لم يكن لدي الوقت لتقسيم مخرجات GPIO المختلفة بين الإشارات المنطقية المختلفة (على Verilog) ، لذلك لم أقم بفرز المعمل باستخدام مستشعر الضوء على DE0-Nano. لنفس السبب ، لم أقم بتصدير الواجهة مع Bus Blaster إلى DE0-CV.2. الأسوأ من ذلك ، التنزيل عبر UART لـ DE0-Nano لم يعمل في MEPhI ، على الرغم من أنه قبل ذلك كان يعمل في جامعة موسكو الحكومية وعلى جهاز الكمبيوتر المحمول الخاص بي. السبب لا يزال غير واضح بنسبة 100٪:2.1. ربما كانت هناك مشكلة عدم توافق إصدار Windows (7 مع التصحيح) وكابل USB إلى UART المستخدم لـ DE0-Nano. كان الكابل عبارة عن استنساخ كبل صيني رخيص استنادًا إلى شرائح PL2303TA ، على الرغم من أنني لم أجربه قبل الندوة. من المعروف أن الإصدار السابق من هذه الكبلات المستند إلى شرائح مع PL2303HX واجه مشكلة في التوافق مع Windows 8 ( انظر ). أبشع ما لدي مع جهاز كمبيوتر محمول مع إصدار من Windows 7 ، وجهاز كمبيوتر محمول مع إصدار من Windows 8 ، وبدائل مختلفة لهذا السلك. لكنني لم أتحقق من جميع المجموعات قبل الندوة ، على الرغم من أنني كنت قد فعلت ذلك في المساء السابق - للأسف.2.2. قبل ورشة العمل بيومين ، أجريت تغييرات على مقسم الساعة. لم يكن يستحق القيام به سواء.2.3. حسنًا ، عمل كل شيء على الأقل بشكل جيد على DE0-CV.3. في MEPhI ، عرضت نسخة أكثر تعقيدًا من مثال ذاكرة التخزين المؤقت أكثر من ذي قبل في جامعة موسكو الحكومية. لقد كان خطأ - في مثال معقد ، قام المترجم بتحسين شيء ما ، ولم يكن نمط الأضواء واضحًا كما هو الحال في المثال البسيط الأصلي. تم حفظ الوضع إلى حد ما من قبل المتحدث الإضافي المدعو من NIIMI Anton Pavlov ، الذي ، على الرغم من أنه لم يكن لديه الوقت في MEPhI ، أظهر بعضًا يقدم نسخته الخاصة من ربط MIPSfpga المسمى myMIPSfpga ، والذي وصفه أيضًا في الملاحظة "MIPSfpga: خارج الشريعة" . من بين أمور أخرى ، قام أنطون بنقل MIPSfpga إلى لوحة Mars rover 3 الروسية والتي كشخص تعرضت للتعذيب بسبب الاستيراد والتصدير (Scylla: مراقبة الصادرات الأمريكية + Charybdis: الجمارك الروسية) ، سأحاول استخدامها في الأحداث التعليمية التالية في روسيا: خلال فترة الاستراحة وبعد الندوة ، أظهر لي مكسيم جوربونوف مشاهد أسطورية مختلفة ، والتي تشمل ثلاث لوحات بروح عصر أندروميدا جالاكسي وموليكولر كافيه ذات الحجم المتعدد باللونين الأحمر والأبيض تأتي من عام 1960: UPD: كما في التعليقات التي بدأت في مناقشة كنيسة mifishnuyu ، وسأوضحها (أنا لم يتم إدخالها كانت هذه القطعة في الأصل ، حيث لم يكن متأكدًا من أنها مناسبة لأوقات المهوس):

والتي كشخص تعرضت للتعذيب بسبب الاستيراد والتصدير (Scylla: مراقبة الصادرات الأمريكية + Charybdis: الجمارك الروسية) ، سأحاول استخدامها في الأحداث التعليمية التالية في روسيا: خلال فترة الاستراحة وبعد الندوة ، أظهر لي مكسيم جوربونوف مشاهد أسطورية مختلفة ، والتي تشمل ثلاث لوحات بروح عصر أندروميدا جالاكسي وموليكولر كافيه ذات الحجم المتعدد باللونين الأحمر والأبيض تأتي من عام 1960: UPD: كما في التعليقات التي بدأت في مناقشة كنيسة mifishnuyu ، وسأوضحها (أنا لم يتم إدخالها كانت هذه القطعة في الأصل ، حيث لم يكن متأكدًا من أنها مناسبة لأوقات المهوس):

ذهبت إلى الكنيسة الأسطورية ، التي كانت حولها صرخات كثيرة على الإنترنت قبل حوالي ثلاث سنوات ، بسبب مغادرة الموظفين معهد موسكو للفيزياء الهندسية احتجاجًا. كشخص محايد ، أي غير مؤمن حقًا ، وليس مؤيدًا متشددًا لواحد أو آخر من جوانب الصراع ، يجب أن أقول أن 1) الكنيسة الأسطورية متواضعة نوعًا ما وليست مبتذلة ، تشبه روحًا الكاتدرائية الأرثوذكسية في سان فرانسيسكو ؛ 2) ليست MEPhI أول جامعة روسية لها دين ، فقد ظهرت دورة الأرثوذكسية في معهد موسكو للفيزياء والتكنولوجيا بالفعل في عام 1988 (ثم جاءت إليه كلية الفيزياء والتكنولوجيا بأكملها ، واستمع الطلاب إلى المحاضرة الأولى الدائمة ، ولكن بعد ثلاثة أشهر لم يعد هناك أكثر من اثني عشر طالبًا) ؛ 3) توجد كنائس في العديد من الجامعات الأمريكية. يتبع.

ذهبت إلى الكنيسة الأسطورية ، التي كانت حولها صرخات كثيرة على الإنترنت قبل حوالي ثلاث سنوات ، بسبب مغادرة الموظفين معهد موسكو للفيزياء الهندسية احتجاجًا. كشخص محايد ، أي غير مؤمن حقًا ، وليس مؤيدًا متشددًا لواحد أو آخر من جوانب الصراع ، يجب أن أقول أن 1) الكنيسة الأسطورية متواضعة نوعًا ما وليست مبتذلة ، تشبه روحًا الكاتدرائية الأرثوذكسية في سان فرانسيسكو ؛ 2) ليست MEPhI أول جامعة روسية لها دين ، فقد ظهرت دورة الأرثوذكسية في معهد موسكو للفيزياء والتكنولوجيا بالفعل في عام 1988 (ثم جاءت إليه كلية الفيزياء والتكنولوجيا بأكملها ، واستمع الطلاب إلى المحاضرة الأولى الدائمة ، ولكن بعد ثلاثة أشهر لم يعد هناك أكثر من اثني عشر طالبًا) ؛ 3) توجد كنائس في العديد من الجامعات الأمريكية. يتبع.

Source: https://habr.com/ru/post/ar387157/

All Articles