توزيع الفيل: لوحات FPGA للمشاريع التعليمية مع MIPSfpga

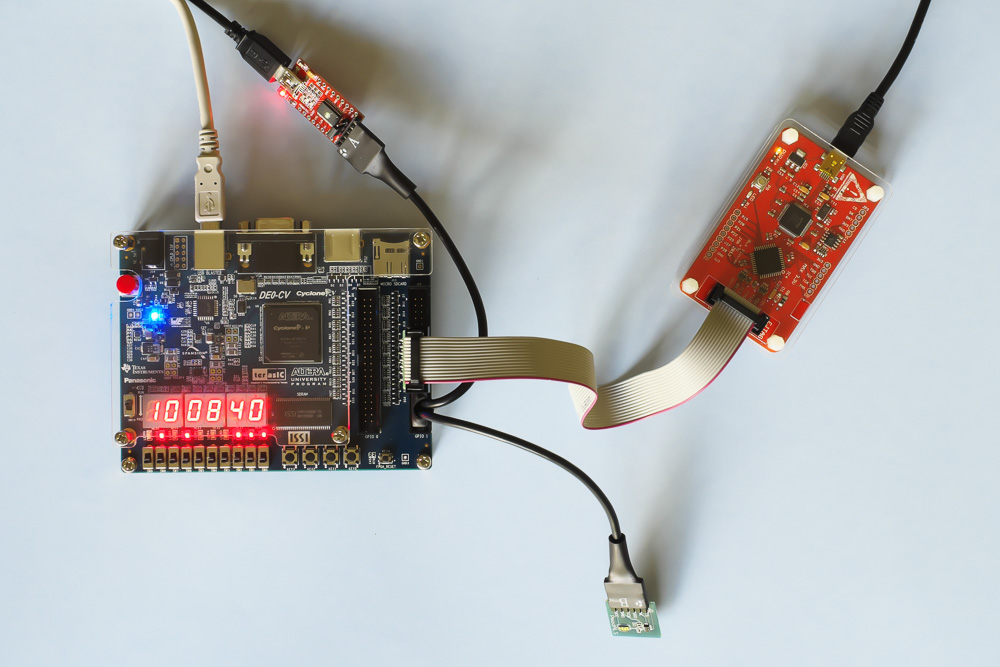

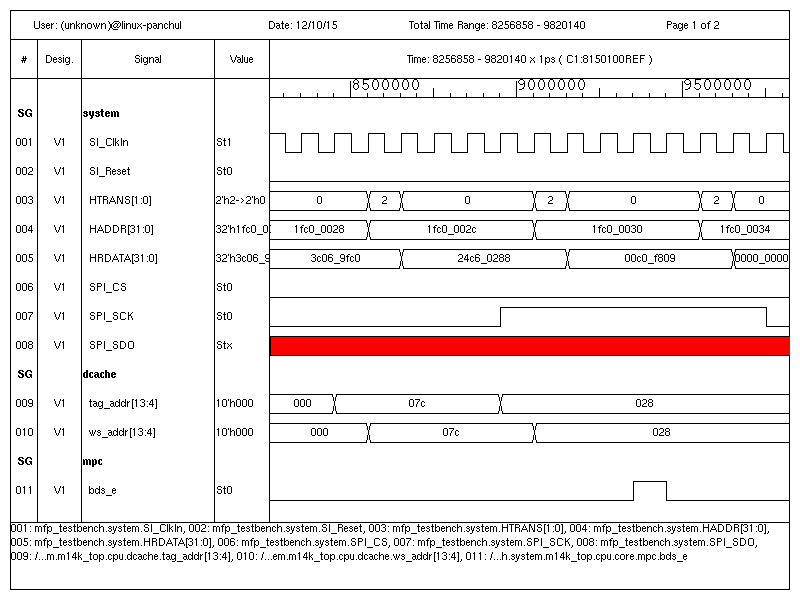

قبل شهر ، عقدت حلقات دراسية حول MIPSfpga ( 1 ، 2 ، 3 ، 4 ) في الجامعات الروسية ، وكاتب من معهد NIIIS يدعى أنتون بافلوف مذكرة حول التحسينات الخاصة به MIPSfpga "MIPSfpga: خارج الشريعة" . نظرًا لأن الأساتذة التقوا بالمنتج الجديد لتدريس طلاب الإلكترونيات بشكل عام بشكل إيجابي ، نشأت الفكرة للمساعدة في البدء باللوحات ، وفي نفس الوقت للعديد من الأشخاص والمنظمات.على وجه الخصوص ، تكريما للعام الجديد ، أنا بالتعاون مع Vitaliy Kravchenko من univeda.ruنحن نخطط لتوزيع صغير للفيلة ، أي لوحات تيراسيك DE0-CV المجانية مع FPGA Altera Cyclone V. لذا يمكنك تكرار انطون بافلوف الفذ. نظرًا لأن هذا التوزيع الخاص يتم _not_ بأموال تقنيات Imagination ، وليس بأموال Altera وليس بأموال مركز Elvis العلمي والإنتاج ، ولكن بأموال المستفيدين من القطاع الخاص ، بما في ذلك أنا شخصيًا ، سيتم توزيع الأفيال بشروط محددة إلى حد ما كما هو موضح أدناه. أهداف الحدث: 1. لزيادة مستوى مشاركة الجامعات الروسية في البحث العالمي في مجال العمارة المصغرة للمعالجات ، وتصميم SoCs والأنظمة متعددة النوى غير المتجانسة 2. لزيادة عدد النصوص الروسية على MIPS Insider حتى يبدأ الزائرون من الصناعة الإلكترونية والأوساط الأكاديمية الدولية في فهم أن الروس قادمون 3. لإنشاء مجموعة من المواد التدريبية حول MIPSfpga ، نيابة عن المجتمع ، والتي يمكن استخدامها من قبل كل من أساتذة الجامعات الروسية وأساتذة الجامعات في دول أخرى - الولايات المتحدة الأمريكية ، اليابان ، الصين ، إلخ.الشروط:1. من المستحسن أن يكون المدفوع له مدرسًا أو طالب دراسات عليا أو طالبًا في جامعة روسية.2. من المرغوب فيه أن هذه الجامعة لم تكن جامعة موسكو الحكومية ، ومعهد موسكو للفيزياء والتكنولوجيا ، و MEPhI ، و MIET و ITMO ، والتي يمكنها تلقي هذه الرسوم من مصادر أخرى.3. من المستحسن جدًا أن يرسل لي صديق مبدع قبل استلام اللوحة وصفًا للمشروع فحسب ، بل يرسل أيضًا رمزًا في Verilog أو VHDL و C و / أو المجمع ، والذي يحاكي به نموذجًا أوليًا لنظام مركب في المستقبل في بيئة ModelSim أو Icarus. المخططات الزمنية هي أيضا موضع ترحيب.4. يتم تحميل كود المشروع عند الانتهاء إلى http://github.com/MIPSfpga - انظر http://github.com/MIPSfpga/mipsfpga-plus5 كمثال ، كما هو موضح في قسم ويكي:5.1. ماذا يوجد في كل ملف5.2. التسلسل الهرمي لوحدات الأجهزة5.3. كيفية المحاكاة - تعليمات مع لقطات الشاشة5.4. الرسوم البيانية لتوقيت المحاكاة5.5. كيفية التوليف - تعليمات مع لقطات الشاشة5.6. نتائج التوليف - الحجم والحد الأقصى للتردد5.7. وصف الجزء البرمجيات5.8. صور FPGA العاملة6. تم توضيح ذلك على http://geektimes.ru في شكل المادة7. نفس الشيء تم وضعه على http://silicon-russia.com8. نفس الشيء تم وضعه على http://community.imgtec.com / forums / cat / mips-insider / mipsfpga9. يمكن أن تكون اللغة (6) و (7) و (8) روسية أو إنجليزية10. إذا لم تفعل أي شيء مع المجلس لمدة شهر ، يتم سحبه منك ونقله إلى شخص آخر11. إذا قمنا (أنا و UnivEDA) بعمل أي أحداث في روسيا مثل المسابقات أو التدريبات ، فسوف نفرض عليك أيضًا رسومًا خذ وقتكأمثلة عن المشاريع ذات اللوحات:1. واجهة بين MIPSfpga وأجهزة استشعار ذات واجهات SPI و I2C و UART وغيرها. مستشعرات للرطوبة ، ودرجة الحرارة ، والصوت ، والبوصلة ، وجهاز تحديد المدى ، وما إلى ذلك.2. الواجهة بين MIPSfpga والخارجية فيما يتعلق بذاكرة FPGA - SDRAM ، DDR ، إلخ. (في الأمثلة الحالية ، تم بناء ذاكرة النظام من ذاكرة كتلة داخل FPGA)3. الواجهة بين MIPSfpga والأجهزة الأكبر هي شاشة VGA ، الماوس ، لوحة المفاتيح ، عصا التحكم.4. تصور ذاكرة التخزين المؤقت عن طريق تشغيل المعالج على تردد 1 ساعة في الثانية وإخراج الإشارات المتعلقة بالمعاملة (الطلب ، يغيب ، وما إلى ذلك).5. تصور تشغيل الناقل والعمليات الحسابية من خلال بدء المعالج بتردد 1 ساعة في الثانية وإخراج إشارات التحكم للناقل ، إلخ.6. إضافة أوامر إلى المعالج باستخدام واجهة CorExtend / تعليمات معرفة من قبل المستخدم (UDI). مثال على ذلك هو أوامر التشفير الخاصة.7. العمل المخبري مع شرح عملية المقاطعة في أوضاع مختلفة ومعالج المقاطعة.8. الجسور بين حافلة AHB-Lite والحافلات الأخرى - AXI و APB و OCP و Wishbone و PLB وما إلى ذلك.9. نظم المعالجات المتعددة دون تماسك مخابئ المستوى الأول و (للأكثر تقدما) مع مخابئ متماسكة وتنفيذ بروتوكولات مثل MESI.10. الانتقال إلى مختلف البرامج وأنظمة التشغيل MIPSfpga - من RTOS البسيط إلى متغيرات Linux المختلفة (يدعم MIPSfpga TLB MMU).يرجى إرسال الاقتراحات إلى yuri.panchul@imgtec.com مع نسخة من yuri@panchul.com

3. لإنشاء مجموعة من المواد التدريبية حول MIPSfpga ، نيابة عن المجتمع ، والتي يمكن استخدامها من قبل كل من أساتذة الجامعات الروسية وأساتذة الجامعات في دول أخرى - الولايات المتحدة الأمريكية ، اليابان ، الصين ، إلخ.الشروط:1. من المستحسن أن يكون المدفوع له مدرسًا أو طالب دراسات عليا أو طالبًا في جامعة روسية.2. من المرغوب فيه أن هذه الجامعة لم تكن جامعة موسكو الحكومية ، ومعهد موسكو للفيزياء والتكنولوجيا ، و MEPhI ، و MIET و ITMO ، والتي يمكنها تلقي هذه الرسوم من مصادر أخرى.3. من المستحسن جدًا أن يرسل لي صديق مبدع قبل استلام اللوحة وصفًا للمشروع فحسب ، بل يرسل أيضًا رمزًا في Verilog أو VHDL و C و / أو المجمع ، والذي يحاكي به نموذجًا أوليًا لنظام مركب في المستقبل في بيئة ModelSim أو Icarus. المخططات الزمنية هي أيضا موضع ترحيب.4. يتم تحميل كود المشروع عند الانتهاء إلى http://github.com/MIPSfpga - انظر http://github.com/MIPSfpga/mipsfpga-plus5 كمثال ، كما هو موضح في قسم ويكي:5.1. ماذا يوجد في كل ملف5.2. التسلسل الهرمي لوحدات الأجهزة5.3. كيفية المحاكاة - تعليمات مع لقطات الشاشة5.4. الرسوم البيانية لتوقيت المحاكاة5.5. كيفية التوليف - تعليمات مع لقطات الشاشة5.6. نتائج التوليف - الحجم والحد الأقصى للتردد5.7. وصف الجزء البرمجيات5.8. صور FPGA العاملة6. تم توضيح ذلك على http://geektimes.ru في شكل المادة7. نفس الشيء تم وضعه على http://silicon-russia.com8. نفس الشيء تم وضعه على http://community.imgtec.com / forums / cat / mips-insider / mipsfpga9. يمكن أن تكون اللغة (6) و (7) و (8) روسية أو إنجليزية10. إذا لم تفعل أي شيء مع المجلس لمدة شهر ، يتم سحبه منك ونقله إلى شخص آخر11. إذا قمنا (أنا و UnivEDA) بعمل أي أحداث في روسيا مثل المسابقات أو التدريبات ، فسوف نفرض عليك أيضًا رسومًا خذ وقتكأمثلة عن المشاريع ذات اللوحات:1. واجهة بين MIPSfpga وأجهزة استشعار ذات واجهات SPI و I2C و UART وغيرها. مستشعرات للرطوبة ، ودرجة الحرارة ، والصوت ، والبوصلة ، وجهاز تحديد المدى ، وما إلى ذلك.2. الواجهة بين MIPSfpga والخارجية فيما يتعلق بذاكرة FPGA - SDRAM ، DDR ، إلخ. (في الأمثلة الحالية ، تم بناء ذاكرة النظام من ذاكرة كتلة داخل FPGA)3. الواجهة بين MIPSfpga والأجهزة الأكبر هي شاشة VGA ، الماوس ، لوحة المفاتيح ، عصا التحكم.4. تصور ذاكرة التخزين المؤقت عن طريق تشغيل المعالج على تردد 1 ساعة في الثانية وإخراج الإشارات المتعلقة بالمعاملة (الطلب ، يغيب ، وما إلى ذلك).5. تصور تشغيل الناقل والعمليات الحسابية من خلال بدء المعالج بتردد 1 ساعة في الثانية وإخراج إشارات التحكم للناقل ، إلخ.6. إضافة أوامر إلى المعالج باستخدام واجهة CorExtend / تعليمات معرفة من قبل المستخدم (UDI). مثال على ذلك هو أوامر التشفير الخاصة.7. العمل المخبري مع شرح عملية المقاطعة في أوضاع مختلفة ومعالج المقاطعة.8. الجسور بين حافلة AHB-Lite والحافلات الأخرى - AXI و APB و OCP و Wishbone و PLB وما إلى ذلك.9. نظم المعالجات المتعددة دون تماسك مخابئ المستوى الأول و (للأكثر تقدما) مع مخابئ متماسكة وتنفيذ بروتوكولات مثل MESI.10. الانتقال إلى مختلف البرامج وأنظمة التشغيل MIPSfpga - من RTOS البسيط إلى متغيرات Linux المختلفة (يدعم MIPSfpga TLB MMU).يرجى إرسال الاقتراحات إلى yuri.panchul@imgtec.com مع نسخة من yuri@panchul.com

Source: https://habr.com/ru/post/ar387803/

All Articles