مقدمة

ذات مرة ، عندما كان كل شيء كبيرًا ، وكنت صغيرًا ، قرأت كتاب Wojciechowski "الألعاب الإلكترونية" ، متحمسًا لإحياء الأجهزة الموصوفة فيه. لذلك ، في عام 2008 البعيد بالفعل ، من بين عدة عشرات من المرحلات الكهرومغناطيسية ، تم تجميع ALU 4-bit ( RCVM1 - Relay Digital Computing Machine - الإصدار 1 ) قادرًا على الجمع والطرح. ثم فكرت - وماذا لو جمعت عددًا أكبر بكثير من المرحلات وقمت ببناء جهاز كمبيوتر كامل التتابع؟ استغرق الأمر 8 سنوات فقط لتجميع التتابع ببطء هنا وهناك حتى العدد المطلوب ، وبدأت في الإنشاء.

اسمحوا لي أن أقدم لكم مشروعك لإنشاء نسخة ثانية من جهاز كمبيوتر رقمي مرحل ، يحمل الاسم الرمزي "BrainfuckPC" - جهاز كمبيوتر 16 بت مع بنية Von Neumann ومجموعة من التعليمات للغة Brainfuck. تم الانتهاء من أعمال التصميم ، وأنا بصدد صنع هذا الوحش.

1 المواصفات

- عرض ناقل العنوان: 16 بت

- عنونة: كلمة بكلمة ، 16 بت / كلمة

- سعة الذاكرة: 64 كيلوسلوف (128 كيلو بايت)

- عرض ناقل البيانات: 16 بت

- مساحة العنوان الموحدة للكود والبيانات (هندسة فون نيومان)

- تردد الساعة (التصميم): 100 هرتز ، 1 تعليمات / دورة

- مجموعة التعليمات: Brainfuck ++

- عدد المرحلات (التصميم): 792

- المرحلات المستخدمة: مفاتيح التبديل ، RES55 (1p) ، RES64 (1z)

توالت التفاصيل

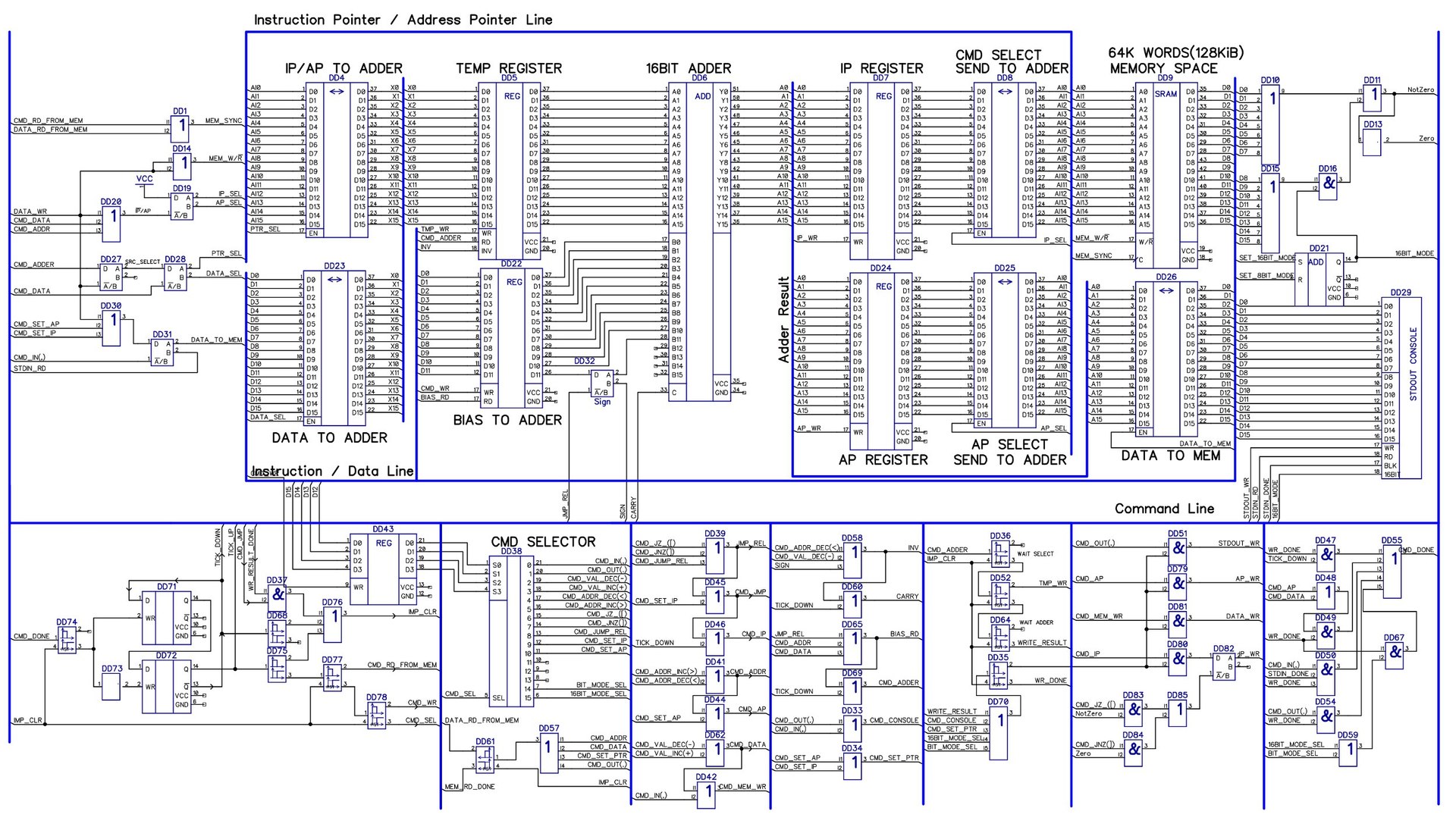

مبدأ العمل العام

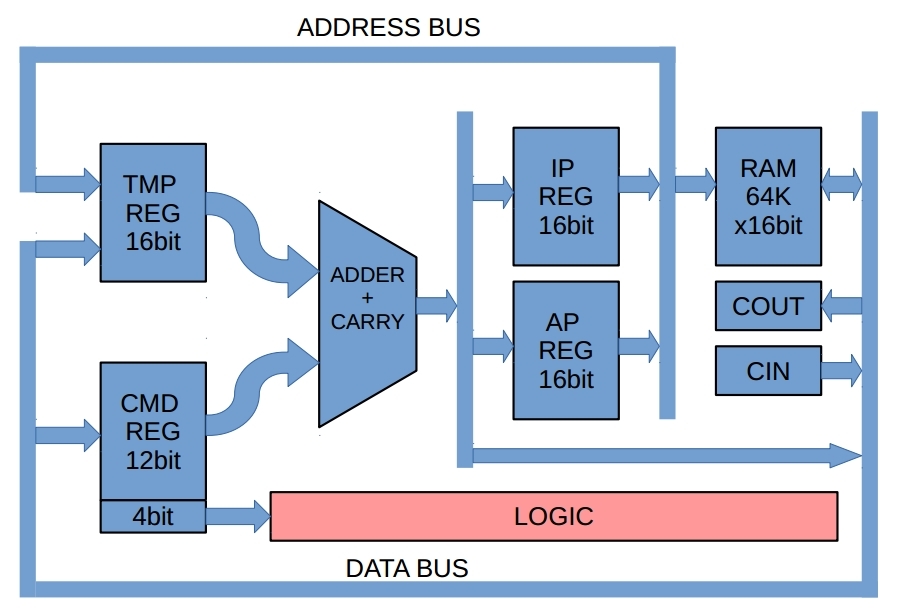

خذ بعين الاعتبار البنية العامة للكمبيوتر:

الشكل 1: هيكل الكمبيوتر المعمم

العنصر المركزي هو الأدمغة ، وليس البسيط ، ولكن مع النقل الموازي. لماذا هذا مطلوب - سأقول أدناه قليلاً.

يتم تخزين البرنامج والبيانات في كتلة الذاكرة. يتم الوصول إليهم على العنوان المسجل في سجل تعليمات IP ، أو في سجل عنوان AP ، بناءً على ما نريد قراءته الآن - البيانات على العنوان المحدد في AP ، أو التعليمات المسجلة على عنوان IP.

لتشغيل شريط Turing هذا (ولغة برمجة Brainfuck تحدده بدقة) ، نحتاج إلى أن نكون قادرين على تنفيذ أحد الإجراءات الثلاثة:

- قم بتغيير القيمة في خلية البيانات الحالية ، أي القيام بعمليات إضافة / فرعية. في Brainfuck ، لا يمكن تغيير القيمة في الخلية إلا بواحد ، أي +1 أو -1. ولكن مع وجود مُعلِم كامل ، فمن الخطأ عدم انهيار السلاسل الطويلة +++++++++++++ (------------) في عملية واحدة AP + = N ( AP- = N) تسريع العملية بشكل كبير الحسابات. (ولا تنس أيضًا تحويل [-] (أو [+]) إلى * AP = 0) ؛

- تغيير رقم خلية البيانات المحددة حاليًا. أي ، المشي عبر ذاكرة البيانات (AP ++ ، AP--) ؛

- قم بتغيير رقم التعليمات الحالية. أولاً ، بعد كل تعليمات ، نحتاج إلى زيادة القيمة في سجل IP بمقدار واحد. ثانيًا ، قم بتغيير هذه القيمة إذا كانت هناك فروع في الكود (افتراضيًا لتنظيم الحلقات). يوجد إشارة تحكم واحدة فقط - Z. وبناءً على ذلك ، هناك أوامر JumpIfZero و JumpIfNotZero.

في المجموع ، نحتاج إلى أن نكون قادرين على تزويد مدخل واحد من المُعلِم بقيمة أي من الكتل الثلاث التالية - AP-register ، IP-register ، DATA-bus. سنفعل ذلك من خلال تسجيل مؤقت ، حيث سنحفظ إحدى القيم المطلوبة ، وربط القيمة المطلوبة باستخدام مفاتيح 16 بت.

في الإدخال الثاني للمُعلِن ، سنقدم رقمًا يتغير من خلاله إحدى هذه القيم إلى علامة زائد أو ناقص. نظرًا للعرض المحدود للإرشادات ، لا يمكنك تغييره إلا من خلال رقم +12 بت. ومع ذلك ، بالنسبة إلى Brainfuck هذا أكثر من كافٍ ("كافٍ للجميع" ، نعم).

سنأخذ هذه البتات الـ 12 من سجل الأوامر ، في وجود مثل هذه الأوامر ، فمن الطبيعي ، لأن جزءًا من الأوامر لا يستخدم المُعلِق على الإطلاق. لا تنس أنه سيتم عرض الأرقام السالبة في الرمز المعزز ، مع تقديم المزيد. إدخال تحويل الوحدة (على سبيل المثال A + invB + 1)

يتم تحميل نتيجة الحساب على الفور إلى حيث حصلنا عليها. بسبب التسجيل المؤقت ، يمكننا القيام بذلك دون ألم.

يمكن العثور على مزيد من التفاصيل (حتى أقول مملة) حول الهندسة المعمارية في هذا الفيديو:

مجموعة التعليمات

بعد رسم مخطط تخطيطي عام قادر على تنفيذ 8 تعليمات أساسية لـ Brainfuck ، أدركت أن لديها إمكانات أكبر بكثير. لذلك ، قمت بتطوير مجموعة أوسع من الإرشادات المتوافقة مع Brainfuck ، ولكنها تتطلب تجميع كل تعليمات Brainfuck المصدر في تعليمات الكمبيوتر ذات 16 بت.

الوصف العام للتعليمات

جميع التعليمات 16 بت. تتكون من عدة أجزاء.

- البتات 15 ، 14 ، 13 - تحديد فئة التعليمات

- بت 12 - بت بت للحصول على تعليمات تسجيل

- البتات 11-0 - تحتوي على 12 بتة أقل من عدد التوقيع. وتتكون البتات الأربعة الأكثر أهمية وفقًا لقيمة البت 12th.

جدول التعليمات

| دليل التعليمات | كود التشغيل | العملية | أي ما يعادل Brainfuck | الوصف |

|---|

| أضف m16 | 0X XX | AP ← AP + m16 | '+' (كرر m16 مرة) | إضافة القاعدة إلى القيمة الحالية للخلية المحددة |

| M16 الفرعية | 1X XX | AP ← AP - m16 | "-" (كرر m16 مرة) | تبعا لذلك ، تطرح القاعدة من |

| ada m16 | 2X XX | AP ← AP + m16 | '>' (كرر m16 مرة) | يزيد من قيمة العنوان |

| الإعلانات m16 | 3 × XX | AP ← AP - m16 | '<' (كرر m16 مرة) | يقلل من قيمة العنوان. |

| jz m16 | 4 × XX | (* AP == 0)؟ IP ← IP + m16: IP ← IP | "[" | انتقل إلى IP + m16 إذا كانت قيمة الخلية الحالية صفرًا |

| jz m16 | 5 × XX | (* AP == 0)؟ IP ← IP - m16: IP ← IP | لا | انتقل إلى IP - m16 إذا كانت قيمة الخلية الحالية صفرًا |

| jnz m16 | 6 × XX | (* AP! = 0)؟ IP ← IP + m16: IP ← IP | لا | انتقل إلى IP + m16 إذا لم تكن قيمة الخلية الحالية صفرًا |

| jnz m16 | 7 × XX | (* AP! = 0)؟ IP ← IP - m16: IP ← IP | "]" | انتقل إلى IP - m16 إذا لم تكن قيمة الخلية الحالية صفرًا |

| و M16 | 8X XX | AP ← AP و m16 | لا | المنطقي AND برقم موجب |

| و M16 | 9X XX | AP ← AP و m16 | لا | المنطقي AND برقم سالب (يجب على شخص آخر تكوين 4 بتات عالية) |

| أو m16 | aX XX | AP ← AP OR m16 | لا | OR المنطقي مع ثابت إيجابي |

| أو m16 | bX XX | AP ← AP OR m16 | لا | OR المنطقي مع ثابت سالب |

| في | c0 00 | * AP ← CIN | '،' | قراءة حرف m8 واحد من وحدة التحكم. إذا كان مخزن الإدخال المؤقت فارغًا ، فانتظره. |

| خارج | ج 01 | COUT ← * AP | "." | طباعة حرف m8 على وحدة التحكم |

| clr.ap | د 01 01 | AP ← 0 | لا | محو تسجيل AP. يتيح الأمر الجمع |

| clr.ip | د 02 02 | IP ← 0 | لا | محو سجل IP. يتيح الأمر الجمع |

| clr.dp | د 04 04 | * AP ← 0 | "[+]" أو "[-]" | مسح خلية الذاكرة. يتيح الأمر الجمع |

| set.ap | د 10 10 | AP ← * AP | لا | اكتب القيمة الحالية لتسجيل AP |

| set.ip | د 0 20 | IP ← * AP | لا | اكتب القيمة الحالية لتسجيل IP |

| get.ap | د 1 00 | * AP ← AP | لا | قراءة القيمة الحالية من تسجيل AP |

| get.ip | d2 00 | * AP ← IP | لا | قراءة القيمة الحالية من تسجيل IP |

| الوضع. b8 | ه 1 00 | | لا | التنشيط 8 بت (1) |

| الوضع. b16 | e2 00 | | لا | تفعيل 16 بت |

| توقف | f0 00 | | لا | أوقف الآلة |

- AP - تسجيل العنوان

- IP - سجل التعليمات

- * AP - موقع الذاكرة الحالي

- CIN - إدخال وحدة التحكم

- COUT - إخراج وحدة التحكم

- عند تنشيط وضع 8 بت ، يستمر المُثبت في العمل في وضع 16 بت. ومع ذلك ، تصبح التعليمات الشرطية (أي اختبار قيمة خلية الذاكرة الحالية من أجل المساواة إلى صفر) 8 بت. ( AP & 0x00FF == 0)؟ و ( AP & 0x00FF! = 0)؟ قرر إدخال وإخراج وحدة التحكم حتى الآن ترك 8 بت دائمًا. ليس في Unicode للطباعة في النهاية؟

في هذا الفيديو ، تحدثت بالتفصيل (ولكن لم أفهم جيدًا) حول ما تفعله كل تعليمات وما هي تعليمات الدماغ التي تتوافق معها:

جامع موازي

لا يجب أن تكون أجهزة الترحيل تتابع فقط ، بل يجب أن تكون سريعة أيضًا. مثل أي جهاز كمبيوتر آخر ، سيكون المنجم أيضًا آلة متزامنة ومجهزة بمولد ساعة. بطبيعة الحال ، أود عدم إضاعة دورات الساعة ومحاولة ملاءمة كل عملية في دورة واحدة - أي أنه بالنسبة للحواف الصاعدة والهابطة للمولد المتزامن ، يمكنني تحميل أمر جديد وتنفيذه. في نفس الوقت ، من المستحسن أن يتم تنفيذ جميع الأوامر لنفس الفترة الزمنية.

كل مرحل لديه تأخير معين في التشغيل والإطلاق ، والذي سنأخذه لوحدة زمنية تقليدية واحدة (cu) إذا استخدمنا المرحل RES22 ، 1u.e. ستساوي 12-15 مللي ثانية (إعلامي) ، RES64 - 1.3 مللي ثانية (إعلامي). العملية الأكثر تكلفة (والأكثر تكرارًا) في سيارتي هي الأفعى.

إنه في حد ذاته بسيط وسريع ، ولكن "هناك تحذير واحد" يكمن في طريقة حساب وإرسال إشارة النقل.

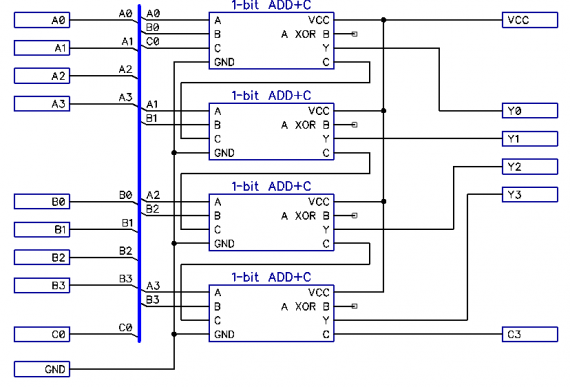

الشكل 2: جامع النقل التسلسلي.

في البداية ، خططت لاستخدام مُحمل حمل متسلسل. في مثل هذا المُلصق ، يعتمد كل تصريف لاحق على حالة إشارة نقل التصريف الحالية. ونتيجة لذلك ، سوف تتقلب مدة العملية الحسابية بين 2 متر مكعب - N * 2 cu ، حيث N هو عدد الأرقام. نتيجة لذلك ، سيصل الحد الأقصى للحمل التسلسلي 16 بت إلى 32 cu

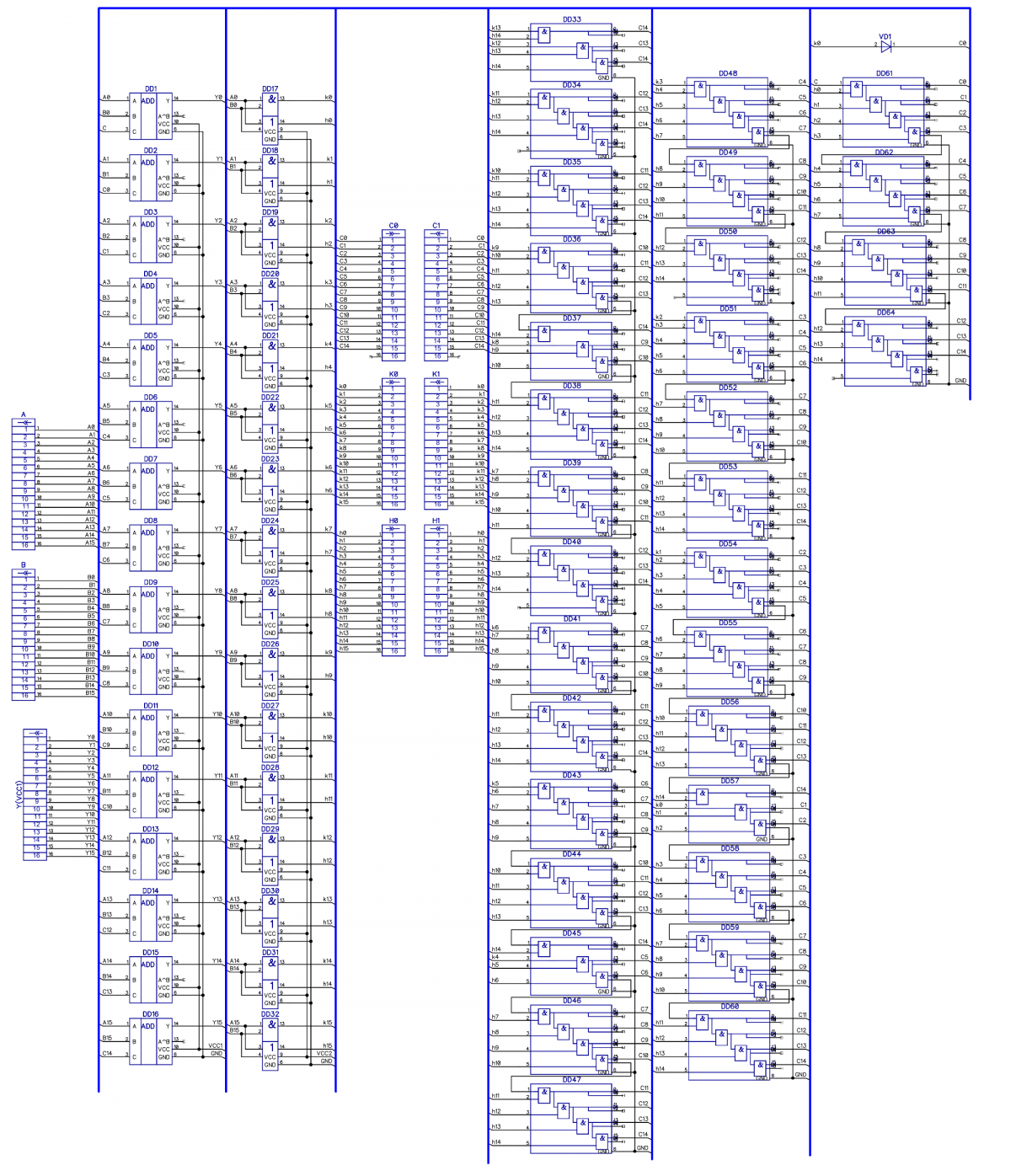

توفر إضافات الحمل المتوازية أقصى أداء. أنها تفتقر إلى عمليات انتشار التحويلات من التفريغ إلى التفريغ. في كل فئة ، يتم إنشاء قيم الإخراج في وقت واحد:

الشكل 3: مُحمل حمل متوازي

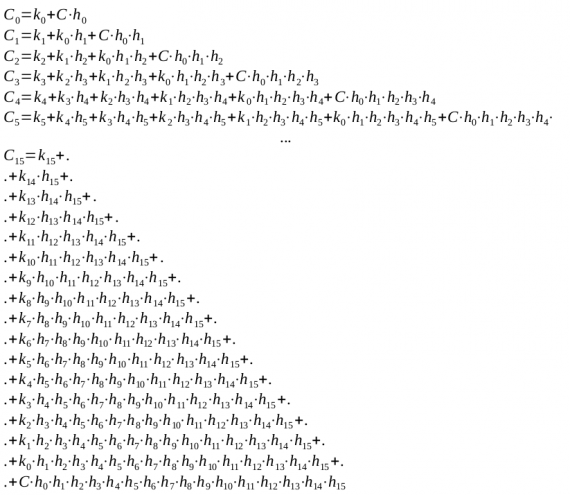

تعتمد القدرة على بناء مُلتزم بالخصائص المُشار إليها على إعادة إنتاج وظائف المجموع والتحويل ، والتي تعتمد فقط على قيم المصطلحات ، بغض النظر عن موقع التفريغ في شبكة التفريغ. الصيد هو أن مخطط النقل الموازي نفسه يصبح أكثر تعقيدًا مع كل تصريف لاحق. هنا ، انظر ماذا يحدث:

الشكل 4: (الذي كان ينبغي أن يكون في شكل صيغ LaTeX ، ولكن ليس) معادلة حساب إشارة النقل للبتات. أين - أحمق و ، - أحادي المعامل OR

ونتيجة لذلك ، يعد تنفيذ الترحيل الموازي مكلفًا للغاية. ومع ذلك ، يمكن ملاحظة أن التفريغ التالي يحتوي على معادلة لحساب السابق (يجب أن يكون هناك ميم "بخير ؟؟" مع نيكولاس كيج) ، لذلك ، من حيث المبدأ ، سيكون كافياً لعمل مخطط حساب نقل فقط للتصريف الأقدم ، وجمع الباقي منه ، مع توفير اختتام نتائج وسيطة.

الشكل 5: رسم تخطيطي كامل لمجمّع موازٍ 16 بت

في الشكل 5 ، العمودين الأولين هما الجمعان بأنفسهما. ثم تأتي الكتل 2AND و 2OR ، التي تشكل القيم الوسيطة لـ h و k ، والتي تظهر في الشكل 4. دفعني وجودهم إلى توسيع قائمة الأوامر بالعمليات المنطقية للإضافة والضرب ، والتي أحتاج إليها فقط لإضافة زوجين من المزالج والرمز الصغير المقابل.

كل شيء آخر هو كتل 5AND استنادًا إلى 4 مرحلات RES64 ، والتي يمكن لحامها بحيث يمكن استخدام وحدة واحدة على سبيل المثال ، 2AND + 3AND. بالنسبة لهذه الكتل ، يتم إخراج كل خطوة AND المنطقية من خلال الصمام الثنائي ، والذي يسمح لك بجمع إشارات النقل الوسيطة.

الوقت المقدر لانتشار الإشارة: تتكيف المضافات مع 1 متر مكعب ، وفي هذا الوقت يتم إنشاء إشارات عند مخرجات كتل 2AND / 2OR ، ثم 1 متر مكعب - عن طريق الضرب في فدرات 5AND ، فإن الجمع المنطقي على الثنائيات لا يؤدي إلى التأخير. حسنا ، آخر واحد أنفقت على إعادة حساب الأفعى.

المجموع 3 متر مكعب مقابل 32 ، أو لا تزيد عن 4.5 مللي ثانية للمعلن.

يسجل

يوجد أربعة سجلات متخصصة 16 بت في الجهاز. لا يوجد RONs. ملزم ضيق فقط ، المتشددين فقط! يتكون من D-flip-flops ، كل D-flip-flop هو وحدة منفصلة على 4 مرحلات RES55 مع الدائرة التالية:

الشكل 6: رسم تخطيطي لوحدة D-flip-flop. في مكان ما لا يزال هناك موصل ، ولكن هنا ليس مهمًا ، لأن كل شيء موقّع.

تأتي البيانات إلى إدخال البيانات ، حيث يحدد التتابع المكان الذي ستذهب إليه إشارة المزامنة - لإعادة تعيين الزناد ، أو لتثبيته (حيث يكون هناك مرحلتان أخريان مسؤولتان ، واحدة ذات قفل ذاتي). يحصل التتابع الرابع على خرج التحويل Q. ميزة مفيدة جدًا.

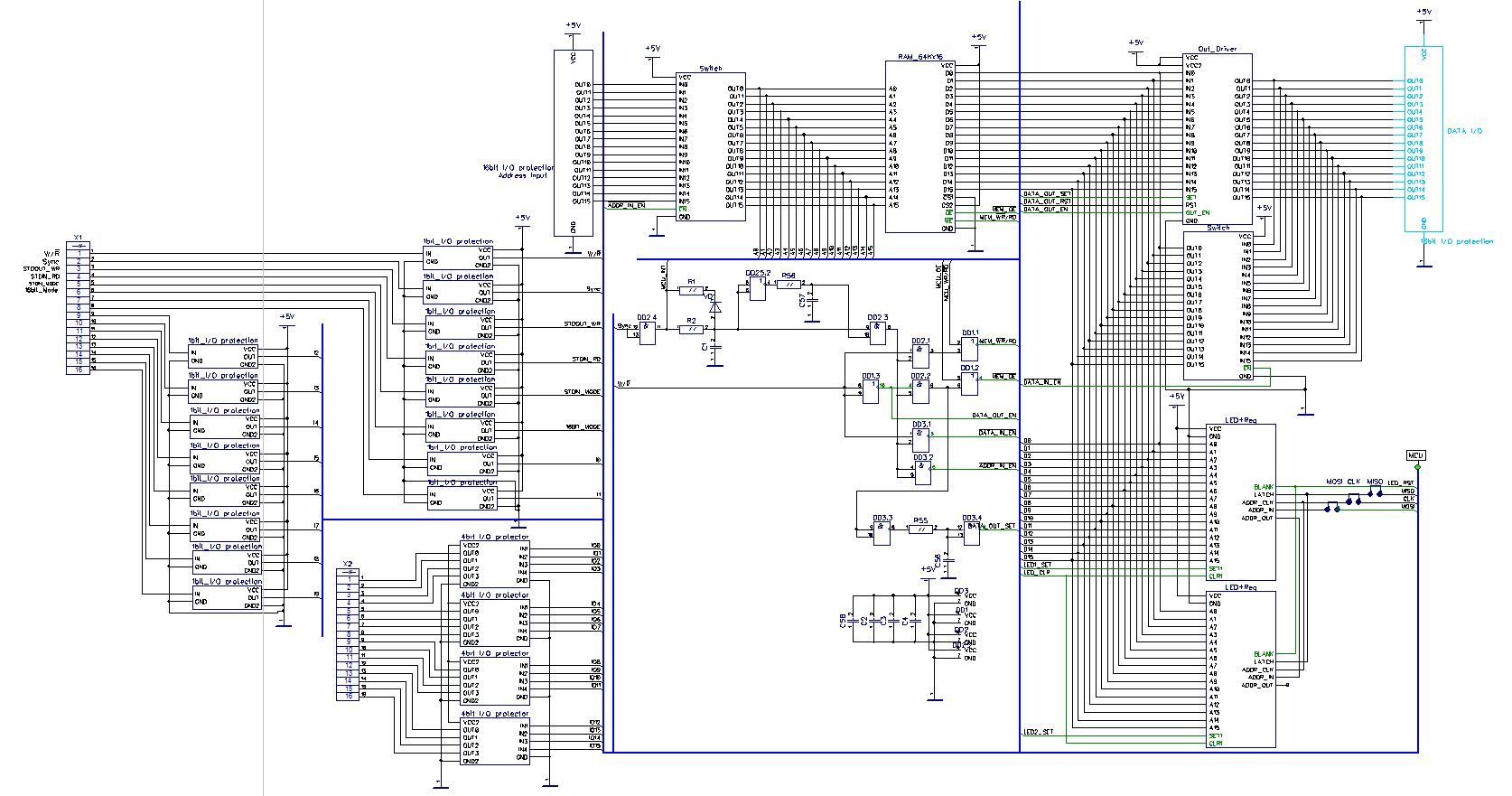

لوحة الذاكرة

الشكل 7: لوحة الذاكرة. أبعاد اللوح 315x200mm

عنصر معقد ومهم للغاية ، على الرغم من أن دائرة الذاكرة نفسها هي جزء صغير من الحشوة الكلية للكتلة. تتمثل مهمة هذا المنتدى ، أولاً ، في حمل 64 كيلوسلوفوس من الذاكرة الإجمالية للبرامج والبيانات. يتم تجميعها على أساس شريحتين مخبأتين 64 كيلوبايت. يتم توصيل إدخال العنوان من خلال دوائر الحماية والمفتاح بناقل عنوان الكمبيوتر ، وعلى جانب ناقل البيانات نظام معقد لمخزن الإدخال المؤقت ومحرك الإخراج ، مع المفتاح أيضًا. للقراءة والكتابة في الذاكرة ، يكون خطان W / R و Sync مسؤولين. يختار الأول ما سنفعله ، والثاني - في الواقع سوف نفعل ذلك.

وبينما لا يوجد هذا المزامنة نفسه ، تعيش بطاقة الذاكرة بشكل طبيعي حياتها الخاصة. في العرض ، يمكنك رؤية مصفوفتين LED 16x16. تعرض هذه الشاشة بعض مساحة الذاكرة. نوع من VideoRAM ، يحدد برمجيا ، بالمناسبة. يستجوب رقاقة الذاكرة ويتحكم في إخراج متحكم Atmega1280.

بالنسبة إلى بطاقة sim ، لا تنتهي مهام وحدة التحكم الدقيقة عند هذا الحد. تعليق وحدة التحكم والإخراج عليها. حيث سيتم إخراجها - لم أقرر بعد ، لذلك يتم فصل محول USB-Serial لوحدة التحكم العادية و ESp8266 لشبكة Wi-Fi على اللوحة. وفقًا للأخيرة ، في الخطط الأكثر إلحاحًا أن يكون لديك صفحة ويب مع القدرة على تنزيل برامج الكمبيوتر إلى الذاكرة ووحدة التحكم نفسها. نعم ، تتضمن مهام MK أيضًا التحميل الأولي للبرنامج في ذاكرة الوصول العشوائي (RAM) ، والتي تتمتع بوصول كامل لها إلى ذاكرة الوصول العشوائي ، بالإضافة إلى ذاكرة EEPROM صغيرة بسعة 1 ميجابايت لتخزين البرامج.

الشكل 8: رسم تخطيطي لبطاقة الذاكرة. لم يتم عرض المخططات الدقيقة والكتل التخطيطية

كتلة المنطق

ليس لدي فكرة كيف سينتهي به الأمر. أحدث إصدار موجود في دائرة الكمبيوتر العامة ، لكني لا أحبها. على الأرجح سأقوم بعمل تسلسل من 12 مرحلة وبمساعدة مفاتيح سأرسل إشارات إلى كتل فردية.

الشكل 9: كل شيء حول كتل 16 بت هو كتلة منطقية

البناء

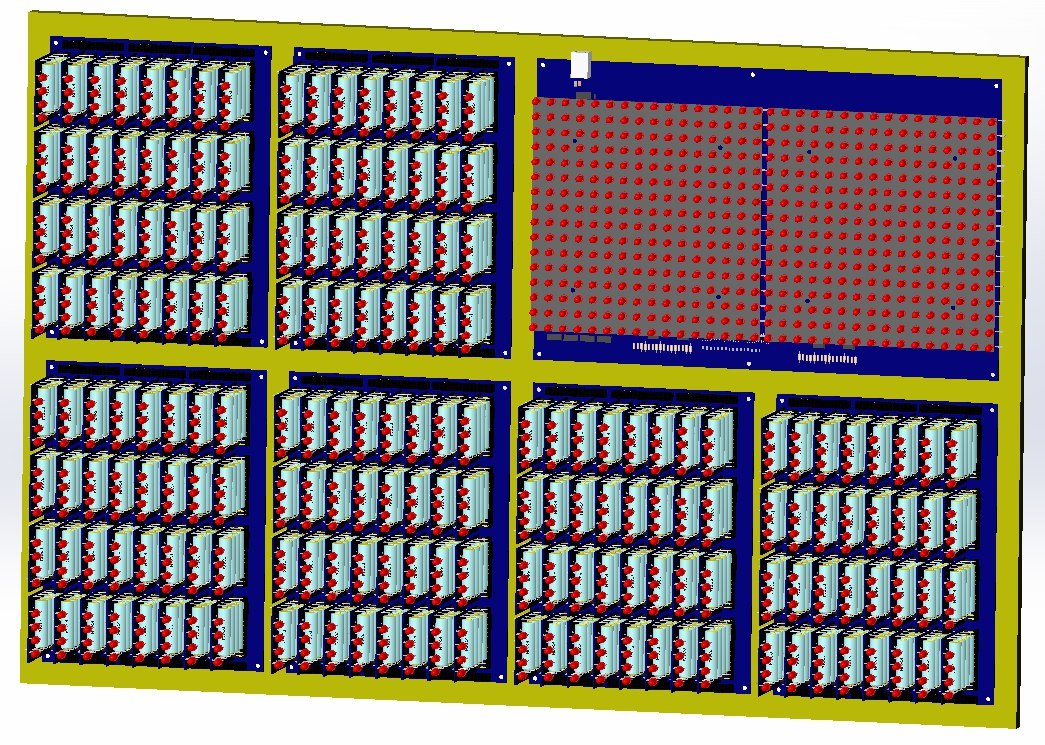

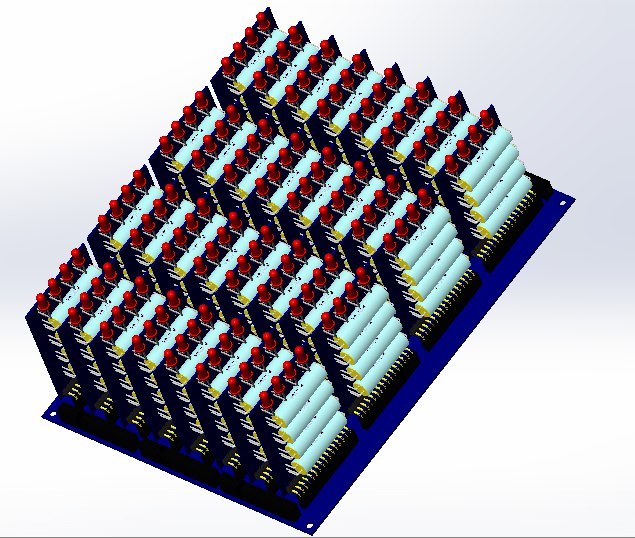

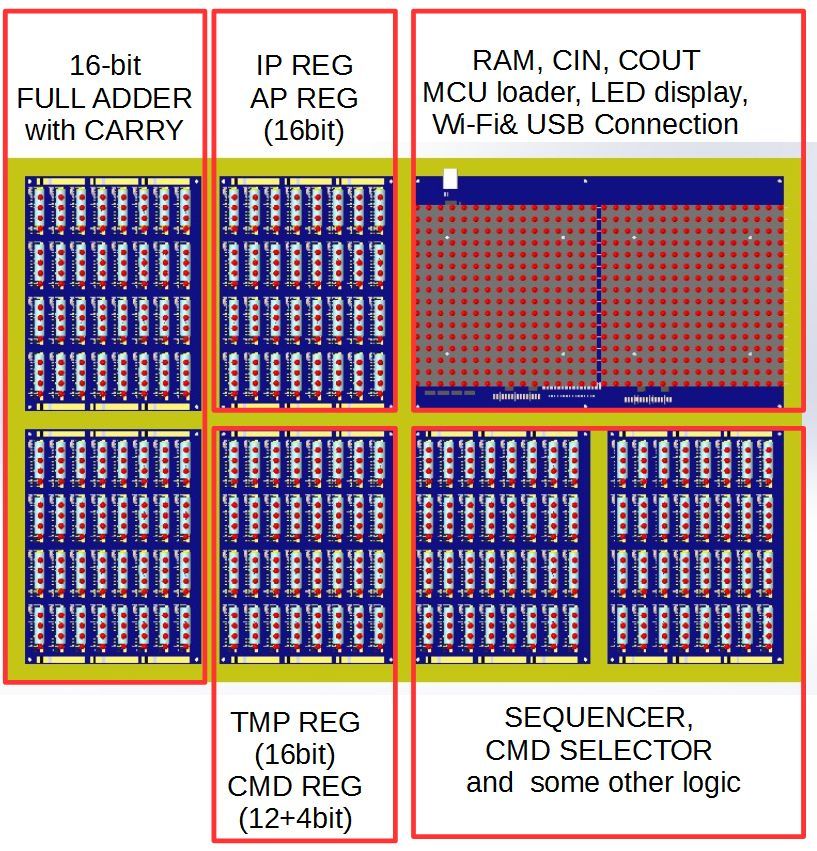

تصميم الآلة نموذجي ، إطار كتلة. يوضح KDPV بوضوح كيف سيتم وضع ملء الجهاز. لكن أول الأشياء أولاً:

الوحدة

العنصر الأساسي للكمبيوتر هو وحدة 60 × 44 مم ، مع موصل 16 دبوس ، يحمل 4 مرحلات ، وحزامها ، و 4 مصابيح LED للإشارة إلى:

الشكل 10: نموذج ثلاثي الأبعاد للوحدة

وحدات بمختلف أنواعها:

- 1-adder مع نقل - 16 جهاز كمبيوتر شخصى ؛

- وحدة 5AND لدائرة النقل المتوازي - 32 قطعة ؛

- وحدة D-flip-flop - 64 جهاز كمبيوتر لكل تسجيل ، بالإضافة إلى القليل من المنطق ؛

- الوحدة النمطية 4x2AND_SW لتنظيم المزالج. هناك 4 مرحلات إغلاق فقط ؛

- وحدة 4x2AND لتنظيم المزالج. هناك 3 من 4 مرحلات مع جهة اتصال متغيرة. في 4 مرحلات لم يكن هناك ما يكفي من دبوس الإخراج ؛

- الوحدة هي الصمام الثنائي ، 8 ديود D226D. لتنظيم مدخلات متعددة OR

- الوحدة العالمية 2AND / 2OR ، تسمح لك بإنشاء 2AND-NOT ، 2OR-NOT ، 4AND ، 4AND-NOT ، 4OR ، 4OR-NOT وأي تركيبة. استنادًا إلى 4 مرحلات مع تبديل جهات الاتصال والنقاط المشتركة ؛

بما أنني ، على الرغم من أنني توصلت إلى كتلة من منطق التحكم ، تم رفضها بالفعل ، فأنا لا أعرف العدد الدقيق للوحدات من كل نوع. سأكتشف ذلك على الطريق. العدد التقديري للوحدات هو 192 قطعة.

كتلة

نأخذ لوحة 150 × 200 مم ، ونلحم 32 موصلات عليها مع 16 دبابيسًا ، ولكن ليس دبابيسًا بسيطة ، ولكن للختام وتثبيت وحداتنا عليه في مصفوفة 8 × 4 ، والحصول على مثل هذه الكتلة:

الشكل 11: بلوك

في سيارتي سيكون هناك 6 كتل من هذا القبيل - كتلتان لكل مُعلن ، وكتلتان لكل تسجيل وكتلتان لكل منطق. أخدش اللفت حول كتلتين إضافيتين من المزالج ، ولكن إذا كانت كذلك ، فإنها تكون مسطحة وملحومة

تم اختيار التثبيت الملفوف للأسباب التالية: أولاً ، يمكن أن تتغير دارات كل لوحة قاعدة ، على الرغم من أنها معروفة مسبقًا ، وهي عرضة للأخطاء. ثانيًا ، من حيث المبدأ ، من المستحيل فصل كتلة المنطق بشكل صحيح في المرة الأولى ، وإذا كان كل شيء واضحًا لكتلة التسجيل ويمكنك ارتكاب خطأ ، على سبيل المثال ، خط التزامن ، فسيتعين عليك إعادة المنطق ألف ومرة. سيكون من الأفضل بكثير إذا قمت بجمع كل مكون من كتلة المنطق تدريجيا. ثالثًا ، عامل ميكانيكي بحت - من المستحيل ماديًا فصل هذه الكتل على لوحة من طبقتين :) الحافلات 16 بت التي تتقاطع مع بعضها البعض بشكل متكرر في جميع الاتجاهات.

في المجموع ، تحتوي كل وحدة على 32 وحدة ، مع إجمالي عدد المرحلات 128 قطعة. قوة كل وحدة 5V 2A.

كمبيوتر

على إطار كبير ، أبعاد 640 × 480 مم (في الواقع أكثر بقليل ، لكن الرقم جميل) هناك ست كتل ترحيل ولوحة ذاكرة:

الشكل 12: موقع كتل الآلة

يتم إدخال الكمبيوتر بالكامل في إطار خشبي مصنوع من الخشب الثمين ، مع الزجاج الأمامي والخلفي.

تصنيع

على الرغم من التاريخ الحالي ، فإن المشروع موجود بالفعل :-) وهو ليس في المرحلة الأكثر نشاطًا ، ولكنه لا يزال في التصنيع.

تتابع

لدي. بأعداد كبيرة ، ولكن المشكلة هي أن هناك ثلاثمائة من أكثر من ألف سهم - قد لا يكون الترحيل 27 فولت و 5 فولت RES55 كافياً بالنسبة لي. لا يمكنني في النهاية تقدير حجم الكارثة ، لكنني أعتقد أنه في المرة القادمة التي سأجمع فيها هذه الآلة الجهنمية ، ستختفي المشكلة بسبب التجديد من الخارج.

الشكل 13: احتياطيات الترحيل. 800 قطعة من التتابع - جديدة ، تم الاستيلاء عليها بنجاح في سوق راديو ميتسا مقابل بنس واحد

واحدة من مصادر التجديد هي لوحات الترحيل من DAC من إمدادات الطاقة المعملية. إليك هذه:

الشكل 14: لوحات من مصادر طاقة من نوع PSU تم شراؤها من سوق الراديو (لا ، لست كذلك

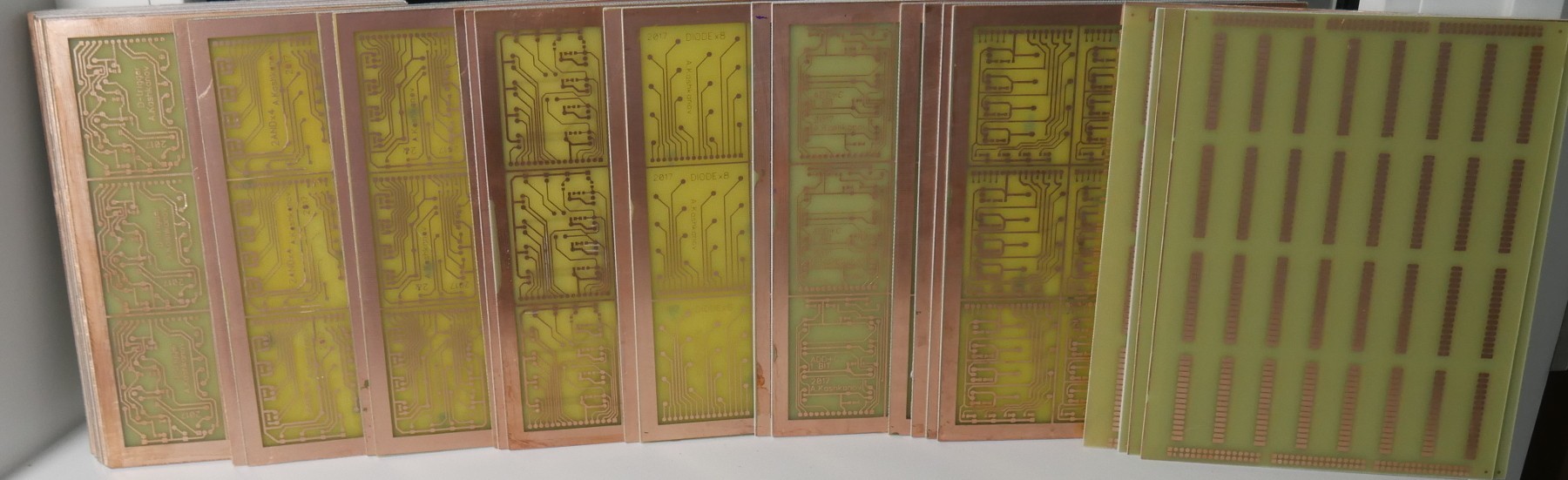

لوحات الدوائر المطبوعة

قررت أن أفعل كل لوحات الدوائر المطبوعة بنفسي. لقد قمت بتثبيت 300 باكز للصينيين وأقوم منذ 4 أشهر بعمل تغطية الفراغات بمقاوم للضوء ، شفاف ، حفر ، تغطية بقناع لحام ، التطوير ، الحفر والطحن.

شكل 15: ألواح محفورة بمختلف أنواعها

أصنع لوحات في لوحات ، 9 وحدات على لوحة 200x150mm. محفوراً 30 صفيحة وتعلق عند وضع قناع لحام. لن أبدأ بأي شكل من الأشكال. قناع اللحام الخاص بي FSR-8000 أزرق ، مكون من عنصرين وقد تعاملت معه بالفعل من قبل.

لم يتم اختيار اللوحات مقاس 200 × 150 مم عن طريق الصدفة - لدينا في سوق الراديو ، في مكان سري واحد ، تم بيعها بثبات لسنوات عديدة ، وجهازي بالكامل مصمم خصيصًا لهذا التنسيق.

في كلمة واحدة ، بدأت في تطبيق مقاوم الضوء (MPF-VSC من Diazonium) باستخدام تغليف وهذه مجرد معجزات. نمت جودة اللصق بشكل ملحوظ.

بعد ذلك ، سيكون من الضروري قطع وحفر هذه الألواح ، والتي لدي حتى آلة قطع ثلاثية الأبعاد.

الشكل 16: آلة الطحن 3DC 2020 الصينية DIY

لقد أخذتها مقابل 175 دولارًا متواضعة حصريًا للإلكترونيات. يكفي حفر الألواح وطحنها ، وأنا بالفعل أبحث في مجموعات من ballscrews + سكك حديدية للآلات ثلاثية الأبعاد. على استعداد لشراء مثل هذا باهظ الثمن بعض الشيء ، ولكن لتجميعه بنفسك عندما يبدأ الطلب - هذا كل شيء.

:

البرامج

, . ( ) Elf. , ( ). //TODO — , .

: . , . . Segmentation Fault!

, . — . leBrainfuck , .

, , Brainfuck . +-<>, [-] . , . , .

. 8 . :

— 10 . LLVM 0,9 . Intel Vtune Amplifier 120 10 .

. , 3 brainfuck-. 100 50 347 — .. , ! , , . .

, , ,

.

-6 , , . — , . — . - — 30-40 - 6 .

????777

المراجع

openSource. :

- https://github.com/radiolok/RelayComputer2 - مستودع به مخططات تخطيطية وتخطيطات ثنائي الفينيل متعدد الكلور. رابط إلى مستودع البرامج الثابتة للوحة الذاكرة سأضيفه لاحقًا

- https://github.com/radiolok/RelayComputer2/blob/master/roadmap.md سأذكر هذه الصفحة بشكل منفصل مع خريطة طريق المشروع التي يتم تسجيل التغييرات الرئيسية عليها.

- https://hackaday.io/project/18599-brainfuck-relay-computer على هذه الصفحة أنشر تقارير تفصيلية عما تم القيام به. وفقًا لمجموعة الكتلة الحرجة ، ستتحول إلى مقال عن GT.

- https://github.com/radiolok/bfutils مترجم ومحاكي.