24-29 أبريل ، ستعقد سلسلة من الحلقات الدراسية لأطفال المدارس في كييف ، والتي لن تبدو كصفوف عادية مع معالجات مدمجة تستخدمها Lego / Arduino / Rasberry Pye كمعيار قياسي. التركيز الرئيسي للندوات ليس لتعليم كيفية برمجة المعالجات ، ولكن لإظهار مبادئ كيفية تصميم المعالجات في الداخل. إنه مثل الفرق بين "تعليم كيفية قيادة السيارة" و "تعليم كيفية تصميم محرك". في الندوات ، سيستخدم الطلاب لغة وصف جهاز Verilog والتوليف المنطقي - التقنيات التي يستخدمها مطورو الشرائح الرقمية في Apple و Samsung وغيرها من الشركات الإلكترونية.

الصفحة الرسمية للندوة ،

التسجيل هناك .

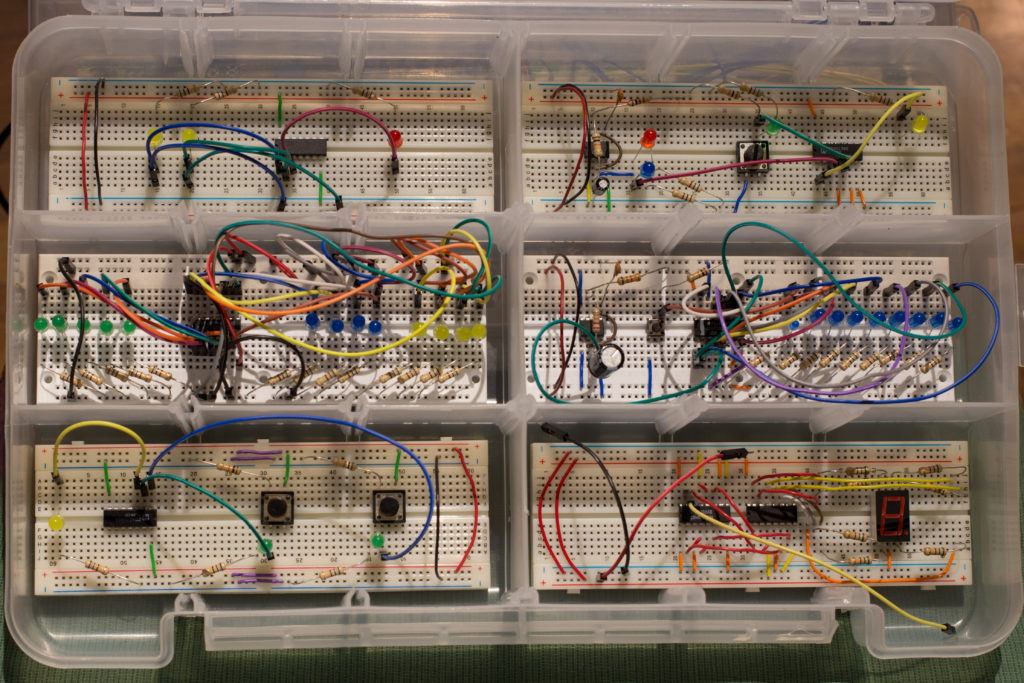

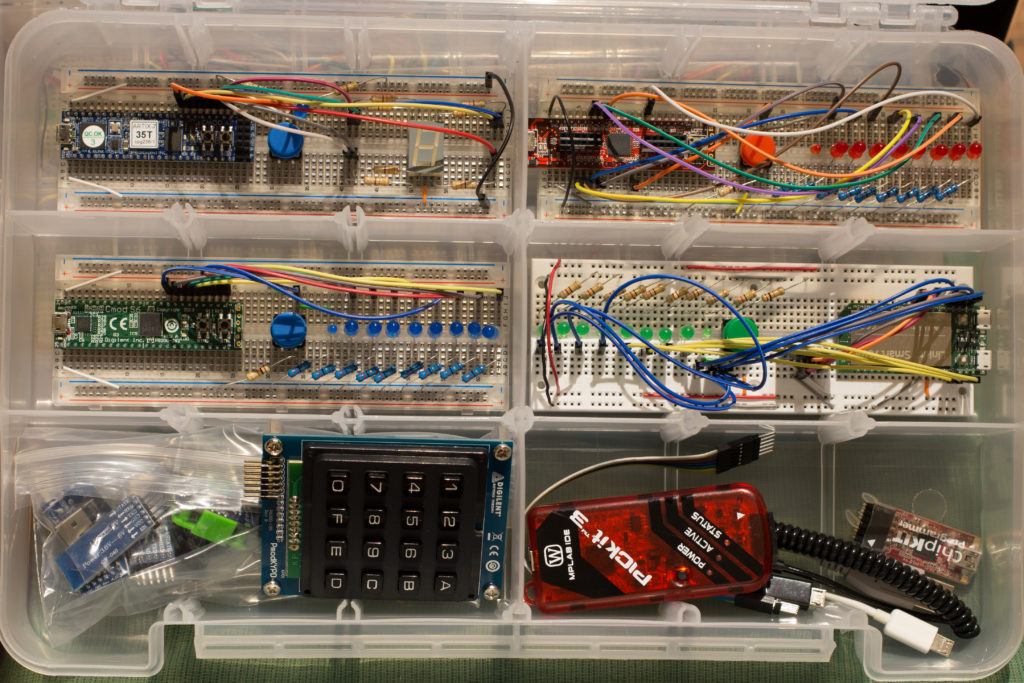

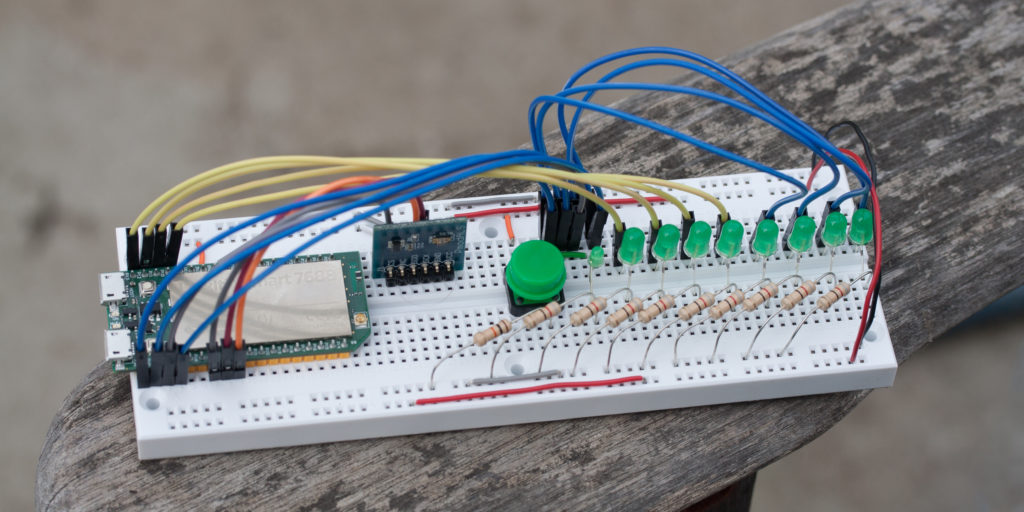

بالنسبة للتمارين ، يتم استخدام الألواح ذات FPGA - مصفوفات العناصر المنطقية ذات الوظيفة المتغيرة (هذه ليست "معالج + ذاكرة" عادية). لطالما تم استخدام FPGAs لتعليم الطلاب كيفية تصميم الإلكترونيات في ستانفورد ومعهد ماساتشوستس للتكنولوجيا ، ومؤخرا في الجامعات الروسية والأوكرانية. يعد استخدام FPGAs لتعليم أطفال المدارس تجربة ، ولديك فرصة للمشاركة فيها. لتسهيل الدخول إلى Verilog و FPGA ، سنبدأ أولاً في التمارين مع الدوائر المصغرة مع درجة صغيرة من التكامل على ألواح الخبز غير الملحومة. ثم سنتعامل مع FPGAs وفي اليوم الأخير من الحلقات الدراسية سنقوم بمقارنة تصميم FPGA مع برمجة المعالجات الدقيقة لإنترنت الأشياء.

سترى أخيرًا ما يحدث بين الترانزستور وأردوينو ، في المنطقة التي نادرًا ما ينظر إليها الطلاب!

برنامج للمدارس الثانوية والصغارالاثنين 24 أبريل. نبدأ الطريق إلى FPGA: المنطق التوافقي والحساب الثنائي على الدوائر الدقيقة ذات درجة صغيرة من التكامل

برنامج للمدارس الثانوية والصغارالاثنين 24 أبريل. نبدأ الطريق إلى FPGA: المنطق التوافقي والحساب الثنائي على الدوائر الدقيقة ذات درجة صغيرة من التكاملالموقع: مساحة Belka KPI للطلاب

- 16: 00-17: 00 ألكسندر بارابانوف ، KNU. من الفيزياء إلى المنطق.

- ما هو التيار والجهد والمقاومة.

- كيف يعمل اللوح؟

- تمرين 1. الدائرة الأولى مع بطارية ، LED ومقاوم. لماذا توصيل المقاوم بدائرة مع LED.

- ما هي الترانزستورات وكيف يتم بناء العناصر المنطقية منها.

- التمرين 2. مراقبة تشغيل الترانزستور.

- 17: 00-18: 00 يوري بانشول ، تقنيات الخيال. الجبر المنطقي والعناصر المنطقية AND-OR-NOT.

- تمرين 3. يتم إعطاء كل طالب شريحة منطقية شخصية من سلسلة CMOS 4000 ، مع وصف فني من الشركة المصنعة ، مع مهمة رسم جدول الحقيقة ، وتوضيح عمله ووصف الوظيفة شفهياً. عناصر المنطق AND و OR و XOR و NOR و NAND مع عدد مختلف من المدخلات.

- تمرين 4: ندرس ماهية المقاومات القابلة للسحب ولماذا هي مطلوبة. أضف 3 أزرار ومقاومات سحب لأعلى للتمرين.

- 18: 00-19: 00 الحساب الثنائي ، الجمع والضرب.

- تمرين 5: يحصل كل طالب على شهادة CMOS 4008.

- 19: 00-21: 00 تمارين إضافية لأولئك الذين تعاملوا مع التمارين 1-5 ولا يريدون العودة إلى المنزل.

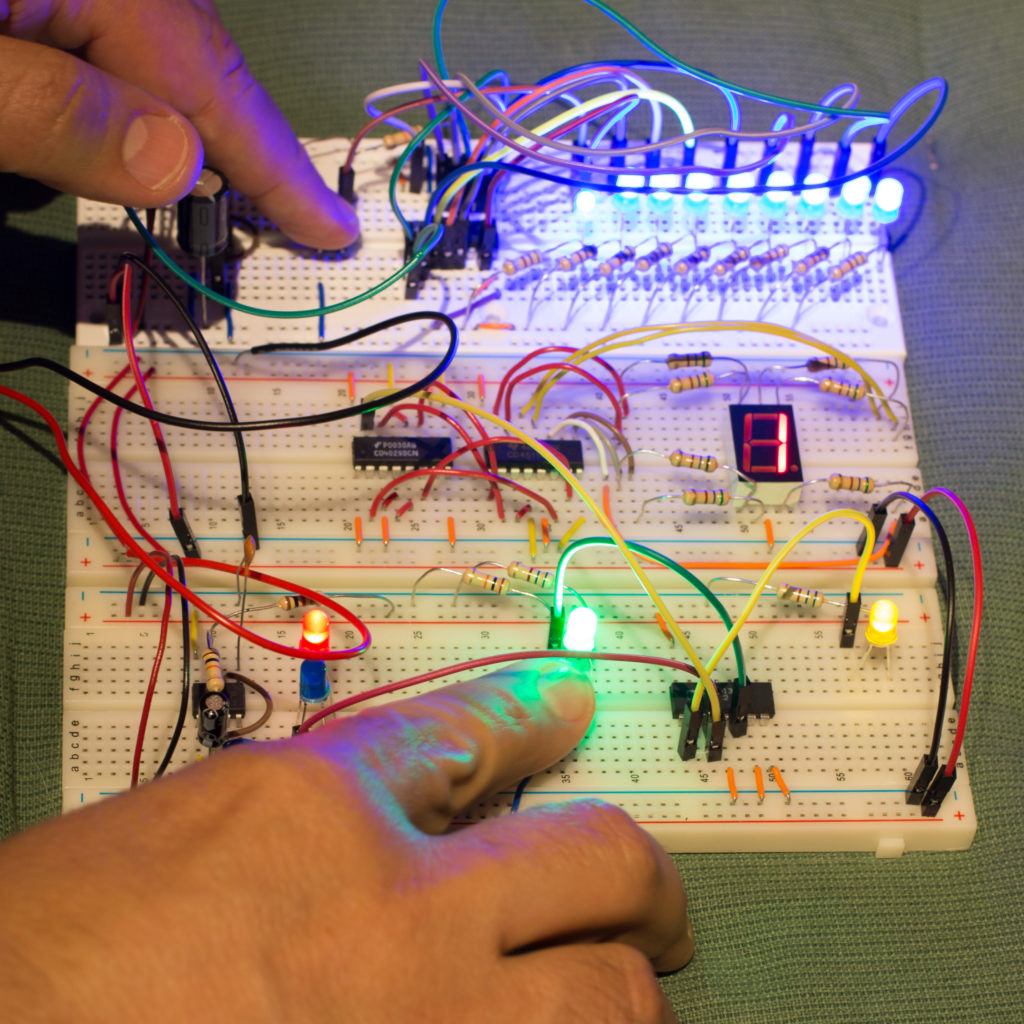

- تمرين 6. مؤشر من سبعة أجزاء ومحركها ، كمثال على دائرة مركبة. اختتام نتيجة المصير لمؤشر السبعة أجزاء.

الثلاثاء 25 أبريل. أضف ذاكرة: المنطق التسلسلي للدوائر المصغرة بدرجة صغيرة من التكامل.

الثلاثاء 25 أبريل. أضف ذاكرة: المنطق التسلسلي للدوائر المصغرة بدرجة صغيرة من التكامل.- 16: 00-16: 30 يوري بانتشول. المنطق التسلسلي هو ما يجعل الكمبيوتر "ذكيًا" ، ويعطيه الذاكرة والقدرة على تكرار العمليات.

- 16: 30-17: 00 يوري بانشول والمدربون في مؤشرات الأداء الرئيسية.

- ما هو الزناد D.

- التمرين 7. نقوم بتوصيل مولد الساعة استنادًا إلى المؤقت 555 في D-flip-flop ونفحص تشغيل الدائرة المترجمة.

- 17: 00-19: 00 عناصر أكثر تعقيدًا للمنطق المتسلسل.

- التمرين 8. قم بتحويل السجل والأضواء المتحركة.

- التمرين 9. واجه مع استنتاج حالة مؤشر السبعة أجزاء.

- 19: 00-21: 00 يوجين كوروتكي ، KPI. تمارين إضافية لأولئك الذين أكملوا التدريبات 6-8 ولا يريدون العودة إلى ديارهم.

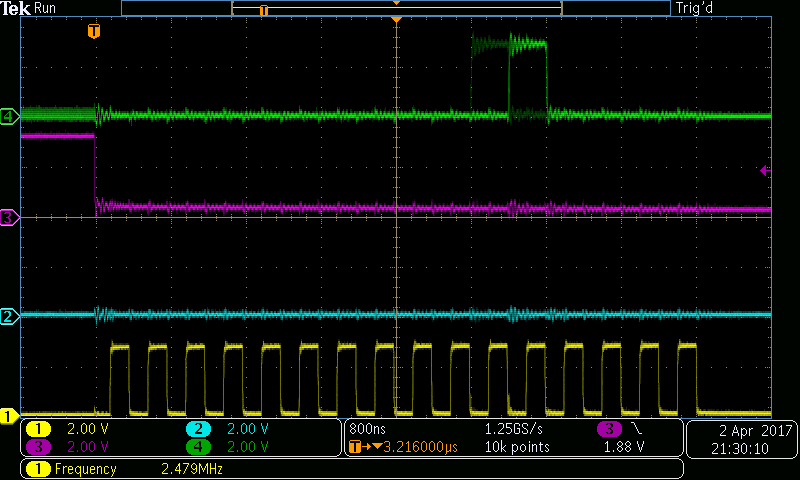

- تمرين 10. نقوم بفحص مولد الساعة على أساس جهاز توقيت رقاقة 555. نلاحظ كيف تختلف فترة تردد الساعة اعتمادًا على مقاومات المقاومات وسعة المكثف.

الأربعاء 26 أبريل. المنطق التوافقي والحساب الثنائي على Verilog و FPGA.

الأربعاء 26 أبريل. المنطق التوافقي والحساب الثنائي على Verilog و FPGA.الموقع: مساحة الطالب Belka KPI.

- 16: 00-16: 30 يوري بانشول ، وكذلك مدربون من KPI ، KNU. مقدمة سريعة للغة وصف أجهزة Verilog واستخدام التركيب المنطقي لـ FPGAs / FPGAs. نحن نعتبر المنطق التوافقي فقط.

- 16: 30-17: 00 مدربون من KPI ، KNU. منطق رامان في فيريلوج.

- التمرين 11. كرر التمرين 2 (العناصر المنطقية) على FPGA باستخدام لوحة Digilent CMOD A7 35T: Breadboardable Artix-7 FPGA Module.

- تمرين 12. نعرض الحروف الأولى من اسمنا ولقبنا على مؤشر من سبعة أجزاء ، نتبدل بينها باستخدام الزر.

- تمرين 13. كرر التمرين 3 (adder) على FPGA. يتم عرض النتيجة على مؤشر من سبعة أجزاء.

- 19: 00-21: 00. تمارين إضافية لأولئك الذين أتقنوا التمارين 9-11 ولا يريدون العودة إلى المنزل.

- التمرين 14: هرمية الوحدات. بناء معددات مع وحدات فرعية.

- التمرين 15. نمذجة كود Verilog بدون FPGA. نقوم بإنشاء بيئة للتحقق من تشغيل الدائرة الموصوفة في Verilog. نستخدم محاكي Icarus Verilog للنمذجة وبرنامج GTKWave لعرض الرسوم البيانية للوقت.

رمز مثال في لغة وصف أجهزة Verilog ، والتي تُترجم (يتم توليفها) إلى دائرة:

module counter ( input clock, input reset_n, output reg [31:0] count ); always @(posedge clock or negedge reset_n) begin if (! reset_n) count <= 32'b0; else count <= count + 32'b1; end endmodule //---------------------------------------------------------------------------- module seven_segment_display_driver ( input [3:0] number, output reg [6:0] abcdefg ); // abcdefg dp // 7 6 4 2 1 9 10 5 7- // 7 6 5 4 3 2 1 pio // --a-- // | | // fb // | | // --g-- // | | // ec // | | // --d-- always @* case (number) 4'h0: abcdefg = 7'b1111110; 4'h1: abcdefg = 7'b0110000; 4'h2: abcdefg = 7'b1101101; 4'h3: abcdefg = 7'b1111001; 4'h4: abcdefg = 7'b0110011; 4'h5: abcdefg = 7'b1011011; 4'h6: abcdefg = 7'b1011111; 4'h7: abcdefg = 7'b1110000; 4'h8: abcdefg = 7'b1111111; 4'h9: abcdefg = 7'b1111011; 4'ha: abcdefg = 7'b1110111; 4'hb: abcdefg = 7'b0011111; 4'hc: abcdefg = 7'b1001110; 4'hd: abcdefg = 7'b0111101; 4'he: abcdefg = 7'b1001111; 4'hf: abcdefg = 7'b1000111; endcase endmodule //---------------------------------------------------------------------------- module top ( input CLK, // 12 MHz inout [48:1] pio // GPIO, General-Purpose Input/Output ); wire reset_n = ! pio [8]; wire [31:0] count; counter counter_i ( .clock ( CLK ), .reset_n ( reset_n ), .count ( count ) ); seven_segment_display_driver display_driver_i ( .number ( count [26:23] ), .abcdefg ( pio [ 7: 1] ) ); endmodule

الخميس 27 أبريل. المنطق التسلسلي وآلات الحالة على Verilog و FPGA.الموقع: مساحة الطالب Belka KPI.

- 16: 00-17: 00. يوري بانتشول. المنطق التسلسلي في Verilog ، آلات الحالة ، مفهوم منهجية RTL (مستوى إرسال التسجيل) ، تأخيرات انتشار الإشارة وقيود على توليف الدوائر الرقمية ، تحديد أقصى تردد ساعة ممكن لدائرة رقمية.

- 17: 00-19: 00. المدربون من KPI ، KNU. المنطق التسلسلي في فيريلوج.

- التمرين 16. واجه النتيجة النهائية لمؤشر السبعة أجزاء. تنفيذ التمرين 9 على FPGA.

- تمرين 17. انقل السجل وأضواء التحريك. تنفيذ التمرين 8 على FPGA.

- تمرين 18. توليد نغمات صوتية من ترددات مختلفة وتراكباتها.

- 19: 00-21: 00. تمارين إضافية لأولئك الذين تعاملوا مع التمارين 17-18 ويريدون العمل عليها.

- التمرين 19. "ابتسامة الحلزون": مثال على آلة الحالة المحدودة.

- تمرين 20. بناء ناقل حسابي. نستخدم محاكي Icarus Verilog لإعداد دوائر متسلسلة.

الجمعة 28 أبريل. مقارنة بين تصميم الدوائر وبرمجة المعالجات الدقيقة المضمنة.

الجمعة 28 أبريل. مقارنة بين تصميم الدوائر وبرمجة المعالجات الدقيقة المضمنة.الموقع: مساحة الطالب Belka KPI.

- 16: 00-16: 30. يوري بانتشول. كيف تختلف البرمجة عن الدوائر الكهربية. آلة فون نيومان هي حالة خاصة للدوائر الإلكترونية. برامج مثل سلسلة من التعليمات لجهاز von Neumann. نظرة عامة على نواة المعالج المستخدم في MediaTek MT7688 و Microchip PIC32MZ.

- 16: 30-19: 00 يوجين كوروتكي. مثال: منصة LinkIt Smart 7688 Internet of Things التي تدعمها MediaTek MT7688.

- يقوم التمرين 21. بوميض مؤشر LED باستخدام برنامج Python.

- التمرين 22. يقرأ البيانات من Digilent PMOD ALS Ambient Light Sensor باستخدام بروتوكول SPI.

- التمرين 23. مقدمة في مفهوم المقاطعات.

- 19: 00-21: 00. تمارين إضافية لأولئك الذين أتقنوا التدريبات على LinkIt Smart 7688 ويرغبون في مواصلة العمل. مثال: متحكم دقيق PIC32.

- يقوم التمرين 24. بوميض مؤشر LED باستخدام برنامج C.

- تمرين 25. يقرأ البيانات من Digilent PMOD ALS Light Sensor باستخدام بروتوكول SPI.

- تمرين 26. تفريغ البرنامج الرئيسي باستخدام المقاطعات. تؤدي الانقطاعات من المؤقت إلى معاملة SPI ؛ وتشير الانقطاعات من SPI إلى استلام الحزمة.

السبت 29 أبريل. هاكاثون

السبت 29 أبريل. هاكاثونالمكان: الجامعة الوطنية “أكاديمية كييف موهيلا”

- المشاريع ذات الدوائر الصغيرة بدرجة صغيرة من التكامل: "كاشف رطوبة التربة" ، "صفارات الإنذار البوليسية"

- المشاريع ذات FPGAs: واجهات لأجهزة الاستشعار ، وأجهزة الحالة من نوع "رمز القفل"

- مشروعات تحتوي على وحدات تحكم دقيقة ومعالجات دقيقة لإنترنت الأشياء: الاتصال بأجهزة الاستشعار والمشغلات

برنامج لطلاب المدارس الابتدائيةالدورة المكثفة لشهر أبريل "مقدمة في الإلكترونيات"الاثنين 24 أبريل.

برنامج لطلاب المدارس الابتدائيةالدورة المكثفة لشهر أبريل "مقدمة في الإلكترونيات"الاثنين 24 أبريل. الإلمام بالأساسيات: قانون أوم والعناصر الإلكترونية السلبية (المقاومات والمكثفات)

المكان: مكتب Radiomag Ukraine LLC ، شارع شوكولوفسكي ، 42-أ

الوقت: 17: 00-19: 00

المحاضر: سيرجي تشيناش

- ما هو التيار والجهد والمقاومة ، قانون أوم

- كيف هو اللوح

- كيفية العمل مع جهاز متعدد

- المقاومات وتطبيقاتها

- مكثف كجهاز تخزين شحنة كهربائية وتطبيقه

الثلاثاء 25 أبريل. المكونات الإلكترونية النشطة: هيكل ومبادئ تشغيل الثنائيات والترانزستورات

المكان: مكتب Radiomag Ukraine LLC ، شارع شوكولوفسكي ، 42-أ

الوقت: 17: 00-19: 00

المحاضر: سيرجي تشيناش

- خصائص أشباه الموصلات وهيكل تقاطع pn

- كيف تعمل الثنائيات وتصنيفها

- مبادئ تشغيل الترانزستورات وتطبيقاتها

الخميس 27 أبريل. دراسات عناصر الإلكترونيات الضوئية: مصابيح LED ، مقاومات ضوئية ، مقاومات ضوئية ، ضوئية

المكان: مكتب Radiomag Ukraine LLC ، شارع شوكولوفسكي ، 42-أ

الوقت: 17: 00-19: 00

المحاضر: سيرجي تشيناش

- عناصر الإلكترونيات الضوئية ومبادئ التشغيل والتطبيق

الجمعة 28 أبريل. إدخال رقاقة NE555

المكان: مكتب Radiomag Ukraine LLC ، شارع شوكولوفسكي ، 42-أ

الوقت: 17: 00-19: 00

المحاضر: سيرجي تشيناش

- ما هي الدوائر المصغرة وتصنيفها

- أنواع الإشارات في الإلكترونيات

- الإلمام بشريحة NE555 ، وإنشاء مولد

- العمل مع راسم الذبذبات

السبت 29 أبريل. لحام منحة

المكان: مكتب Radiomag Ukraine LLC ، شارع شوكولوفسكي ، 42-أ

الوقت: 11: 00-12: 30

نراكم في الندوات!

- مختبر مفتوح للإلكترونيات لامبا ومساحة الطلاب بيلكا ، الجامعة التقنية الوطنية في أوكرانيا "معهد كييف بوليتكنيك سميت على اسم إيغور سيكورسكي"

- جامعة كييف الوطنية تاراس شيفتشينكو

- الجامعة الوطنية "أكاديمية كييف موهيلا"

- الأكاديمية الصغيرة للعلوم في أوكرانيا

- جمعية ذات مسؤولية محدودة "Radiomag of Ukraine"

- تقنيات الخيال

الصفحة الرسمية للندوة ،

التسجيل هناك .