في اليوم الآخر قابلت وأخذت مقابلة فيديو قصيرة من

كاثي جيوري ، نائب الرئيس لعمليات اردوينو الولايات المتحدة الأمريكية . لقد ناقشنا مع Katie اتجاهًا جديدًا قد لمس بالفعل مجتمع Arduino: نظرًا لأن برمجة المتحكمين الدقيقين بمساعدة Arduino قد تم تعلمها بالفعل تقريبًا ، فقد حان الوقت لاتخاذ الخطوة التالية: لتعليم أطفال المدارس استخدام اللغة لوصف معدات Verilog ودوائر FPGA / FPGA ، والمصفوفات المنطقية عناصر ذات وظائف متغيرة. ولجعل إتقان FPGA أسهل ، من الجدير إعادة إحياء التمارين بدرجة صغيرة من رقائق التكامل ، المشهورة في السبعينيات ، كتمهيد ل FPGAs الحديثة. كل هذا سيغلق الفجوة بين الفيزياء والبرمجة ، والعناصر المنفصلة والمتحكمات الدقيقة ، والترانزستور وأردوينو.

يمكن استخدام FPGA واللوحات من أي مصنع (Xilinx ، Altera ، Lattice ، Digilent ، Terasic) ، كل ما أكتب أدناه غير مرتبط بشركة معينة.

شاركت سفيتلانا خوتكا ،

معلمة ستانفورد ، في المحادثة مع كاتيا ، التي أخبرت كاتي عن

تجربة تعليم أطفال المدارس المجانية كيفية استخدام FPGA في كييف بمساعدة المعلمين المتحمسين من العديد من جامعات كييف. بعد ذلك ، شاركت مع خطط كاتي للتجربة التالية من هذا القبيل في

المدرسة الصيفية للمبرمجين الشباب في نوفوسيبيرسك ، المعروفة منذ العصر السوفييتي ، وتحدثت أيضًا مع رفاق آخرين من مجتمع أردوينو الحاضرين حول تنفيذ FPGA في مدرستين وكلية وادي السيليكون.

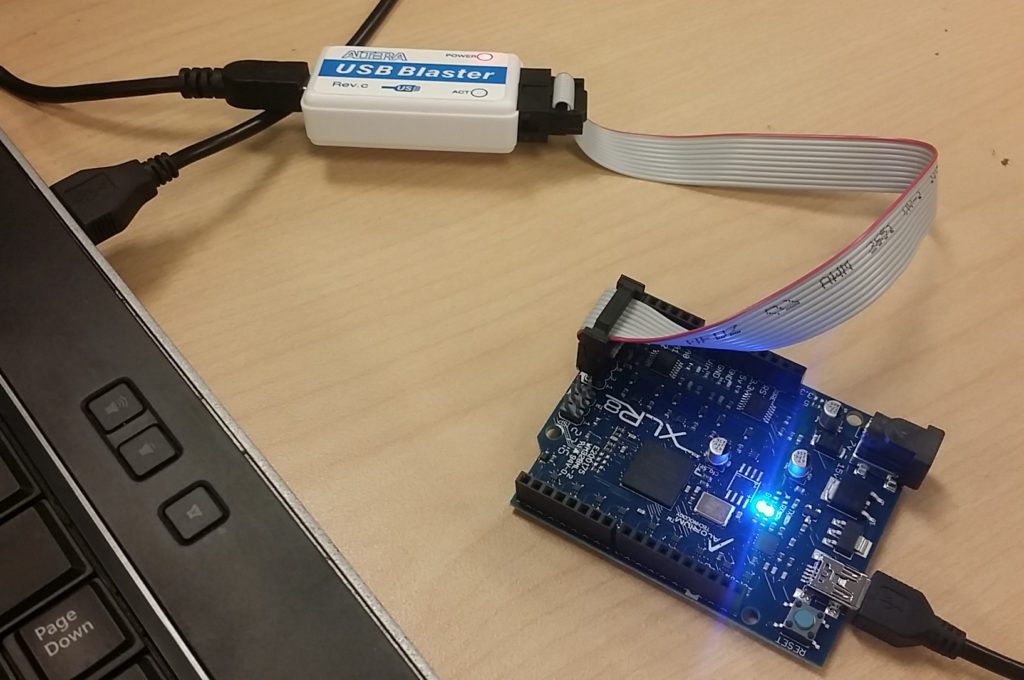

اللوحة الأم مع FPGA ، التي توصي بها كاتيا الآن ، والتي أعيدها إلى حد ما للتكيف مع احتياجاتي (سيكون هناك منشور منفصل حول هذا):

فيما يلي سأقدم معلومات عن نتائج تجربة كييف ، بالإضافة إلى بعض الخطط المستقبلية التي يتم تطويرها من قبل النشطاء - معلمي مدارس التربية البدنية والجامعات في كييف ، تشيرنيغوف ، نوفوسيبيرسك ، موسكو ، نيجني نوفغورود ، سامارا ، سانت بطرسبرغ ، ألماتي ومدن أخرى. في ندوة كييف ، وصل المشاركون إلى مرحلة إنشاء آلات الدولة لقفل الرمز والتكامل مع الأجهزة الطرفية البسيطة (لوحة مفاتيح 16 زر ، مكبر صوت). في المدرسة الصيفية في نوفوسيبيرسك ، سيكون لدينا المزيد من الوقت وسنحاول بناء معالج مع الطلاب. في المستقبل ، من المقرر إجراء دورة سنوية حول أساسيات الإلكترونيات الرقمية على FPGA للمدارس الفيزيائية ، والتي يمكن أن تثري التعليم المدرسي ، كما في الثمانينيات من القرن العشرين تم إثراءها من خلال إدخال عناصر البرمجة.

سنناقش هذا بالتفصيل:

1. لماذا تعليم أطفال المدارس كيفية وصف الأجهزة وكيفية استخدام FPGA؟ مبررات البرنامج.في صورة العالم ممثلة في التعليم المدرسي ، هناك "نقطة عمياء" في مجال مبادئ تصميم الإلكترونيات الرقمية ، بين الفيزياء والبرمجة. لا تغلق دورات الروبوتات واردوينو هذه النقطة العمياء ، حيث أنها تأتي إلى برمجة رقائق جاهزة. التدريبات مع العناصر المنفصلة والدوائر الصغيرة بدرجة صغيرة من التكامل ، على الرغم من فعاليتها في تقديم المبادئ الأساسية ، تستند إلى تقنيات 1960-1970 ولا تحتوي على أي ارتباط بالتصميم الحديث. يمكن إغلاق النقطة العمياء عن طريق إدخال عناصر من لغات وصف الأجهزة (NLA) و FPGA (الدوائر المتكاملة المنطقية القابلة للبرمجة) المتاحة للتجربة المدرسية - مصفوفات العناصر المنطقية القابلة لإعادة التشكيل. وبالتالي ، تصبح صورة العالم جزءًا لا يتجزأ ، وتساهم في خلق بيئة لظهور عدد كبير من المهندسين الشباب الذين لديهم فكرة عن جميع جوانب الدوائر الدقيقة الحديثة لتطبيقات مثل السيارات ذاتية القيادة ، وقادرة على التخصص في المستقبل لتصميم جانب أو آخر من هذه الأجهزة.

كما يرتبط إدخال NLA و FPGA في المناهج الدراسية ارتباطًا جيدًا بدورة الرياضيات والفيزياء في مدرسة الفيزياء والرياضيات - الجبر البولي ، والمخططات الحسابية ، وأجهزة الحالة المحدودة.

لاحظ أن NLA و FPGAs ، على الرغم من التشابه الظاهري للبرمجة ، تستخدم مفاهيم أساسية أخرى:

البرمجة: التنفيذ المتسلسل ، وفروع الاختيار ، والحلقات ، والمتغيرات ، والتعبيرات ، والمصفوفات (مع نموذج الذاكرة المسطحة القابلة للعنونة) ، والوظائف (بناءً على استخدام المكدس) ، والتكرار.

تصميم المنطق الرقمي: عنصر المنطق التوافقي ؛ بناء المنطق التوافقي من هذه العناصر السحابية ، بما في ذلك بدائية الانتقاء باستخدام معددات الإرسال ، بالإضافة إلى الكتل لتنفيذ التعابير الحسابية ؛ مفهوم إشارة الساعة لمزامنة الحسابات والتكرار ؛ مفهوم D- الزناد لتخزين الحالة الحالية بين القياسات آلة الدولة عمليات متوازية ، هرمية الوحدات ، مفهوم خط الأنابيب (ليس فقط للمعالج ، ولكن أيضًا للوحدات الحسابية).

2. الخطة العامة لهذه الدورات:

2. الخطة العامة لهذه الدورات:القسم 1. الارتباط بالفيزياء ، مع مختبر على مكونات منفصلة.

القسم 2. أساسيات المنطق والحساب الرقمي ، مع الدوائر الدقيقة المختبرية بدرجة صغيرة من التكامل.

القسم 3. تصميم الدوائر على أساس توليف لغة وصف الأجهزة ، مع تلك المخبرية على Xilinx أو Altera FPGAs.

القسم 4. بنية المعالج: عرض من جانب المبرمج ، مع مختبر يستخدم محاكي معالج RISC على مستوى التعليمات ، على سبيل المثال MARS MIPS.

القسم 5. العمارة المصغرة: بناء المعالج.

مشروع فردي: دمج مستشعر أو جهاز طرفي آخر مع دائرة مطبقة في FPGA.

3. نتائج تجربة كييف.تم كتابة النص التفصيلي مع نتائج تجربة كييف من

3. نتائج تجربة كييف.تم كتابة النص التفصيلي مع نتائج تجربة كييف من قبل مدرس معهد بوليتكنيك كييف ، Evgeny Korotky. سأكملها باستنتاجاتي الشخصية. الخلفية - منشورات على حبري وجيكتيم -

1 ،

2 ،

3 ،

4 ). في تلك الوظائف تم طرح الأسئلة. فيما يلي الإجابات:

تم تأكيد الفرضية القائلة بأن أطفال المدارس يمكنهم استخدام Verilog

كما تبين أن فيريلوج كان مثيراً للاهتمام لعدد كافٍ من أطفال المدارس (شك بعض الزملاء في ذلك قبل كييف ، بحجة أن الأطفال كانوا أكثر اهتمامًا بمشاريع مثل الذراع الروبوتية مع متحكم دقيق)

فكرة أنه قبل استخدام Verilog ، من المفيد إظهار العناصر المنطقية لأطفال المدارس وحافز D على الدوائر الصغيرة بدرجة صغيرة من التكامل - ليس فقط أنه تم تأكيده بشكل لا لبس فيه ، ولكن حصل على المزيد من التبرير.

إجمالاً ، بعد يوم من الخبرة في الشرطي ، بدأ بعض الطلاب في طرح أسئلة واضحة - على سبيل المثال ، متى يستخدمون الحظر ومتى يستخدمون مهمة غير مانعة.

يبدو أنه من غير الواقعي نقل أطفال المدارس من الصفر إلى أجهزة الدولة التي تنفذ بروتوكولات مثل SPI في أسبوع واحد ، ولكن إلى آلة حالة من قفل رمز أو إشارة مرور - حقًا.

من غير الواقعي أيضًا إحضار أسبوع واحد لتصميم المعالج ، لكننا سنحاول القيام بذلك في غضون أسبوعين في نوفوسيبيرسك.

أثناء تجربة كييف ، حاولنا التحدث عن كل من FPGA والمعالجات المضمنة (MediaTek MT7688 ، التي تقع في مكان ما في الوسط بين Arduino و Intel Galileo أو Rasbery Pye من حيث الأداء). ثم قمنا بعمل هاكاثون (في أكاديمية كييف موهيلا) ولاحظنا عدد أطفال المدارس الذين اختاروا مشروع FPGA للهاكاثون وعدد المشاريع التي تحتوي على معالج متكامل. اتضح - 50 إلى 50. إنه مثير للاهتمام - قبل هاكاثون ، لم يكن لدي أي فكرة عما سيكون الانهيار.

كان لدي قلق من أن أطفال المدارس قد يخلطون بين واجهة المستخدم في Xilinx Vivado ، مع الكثير من الخيارات وعناصر الواجهة. ولكن اتضح أن الطلاب لم يهتموا - واجهة المستخدم الرسومية المعقدة لم تخيفهم.

يستخدم معظم الطلاب Windows. جنبا إلى جنب مع زميلي ألكسندر بيليتس ، لدي فكرة للتحضير لمثل هذه الأحداث بضع عشرات من محركات أقراص SSD القابلة للتشغيل مع Linux (Ubuntu أو CentOS) وارتدائها من حدث إلى آخر. كتب أليكس حتى سيناريو لاستنساخ محركات الأقراص هذه. Ubuntu أكثر صداقة ، ولكن CentOS مدعوم رسميًا أكثر من خلال أدوات أتمتة تصميم الدوائر FPGA ، ولا سيما Xilinx Vivado و Altera Quartus. هل من الممكن القيام ببرنامج Linux التعليمي وبرنامج Verilog / FPGA التعليمي في نفس الوقت خلال المعسكر الصيفي؟ ليس واضحا ، ولكن يمكن تجربته.

اتضح أن Xilinx Vivado عربات التي تجرها الدواب بلا رحمة عند تكوين Artix-7 FPGA ، إذا كنت تستخدم كابلات USB صغيرة رخيصة محمية بشكل سيئ. في بعض التدفق الغامض ، قبل أن أذهب إلى كييف ، وضعت عشرات الحبال عالية الجودة في حقيبتي ، وهذا حفظ الحلقة الدراسية.

كانت لدي فكرة أن استخدام وحدات FPGA القابلة للخبز (ألواح FPGA التي تلتصق في ألواح اللوح) ، مثل Digilent Cmod A7 35T ، يمكن أن تجعل من السهل على الطلاب التبديل من التمارين مع رقائق التكامل الصغيرة إلى التمارين مع FPGA. ما إذا كانت هذه الفكرة صحيحة ، لم أفهم. ربما لن يكون استخدام اللوحات الأم الأكبر حجمًا مع مجموعة غنية من الأجهزة الطرفية ، مثل Terasic DE10-Lite ، أسوأ. على أي حال ، عند التبديل من الدوائر المصغرة بدرجة منخفضة من التكامل (CMOS 4000 أو 74HC) إلى FPGA - تحتاج إلى تغيير جهد الإمداد (من 9 فولت أو 5 فولت إلى 3.3 فولت) ، لذلك لا يمكنك لصق Cmod A7 بدلاً من قول CMOD 4013 في نفس اللوح بأضواء وأزرار ، ونتوقع أن يستمر كل شيء في العمل.

أكدت ملاحظتي أنه من أجل إجراء أحداث تعليمية قصيرة الأجل (أسبوع واحد) ، من المهم أن يكون هناك فريق من الطلاب من جامعة محلية في مكانهم لتوجيه أطفال المدارس. في حالة كييف ، تم توفير مثل هذا الفريق من قبل مدرس معهد بوليتكنيك كييف ، يوجين كوروتكي .

أصبح الأمر أكثر أو أقل وضوحًا في أي الحالات وإلى أي مدى يستحق تضمين برنامج مثل هذه الأحداث جزءًا حول مستوى الترانزستورات وحول إنتاج الدوائر المصغرة. تم تدريس هذا الجزء من قبل الأستاذ المساعد في جامعة كييف الوطنية ألكسندر بارابانوف ، مترجم المواد في الدورة نانومتر ASIC للطلاب. على ما يبدو ، يجب تضمين هذه المادة بالكامل في الدورة السنوية لأطفال المدارس ، في دورة صغيرة - في دورة لمدة أسبوعين في شكل معسكر صيفي ، ولكن مع مدة أقل من أسبوع ، من المحتمل أن تعطي دوائر صغيرة بدرجة صغيرة من الاندماج على الفور (في غضون ساعة واحدة بعد البدء) (على سبيل المثال CMOS 4000) واذكر الترانزستور بشكل عابر ، على شكل "الترانزستور هو جهاز يتدفق فيه التيار من النقطة A إلى النقطة B ، إذا كان الجهد C هو 1 (أو 0) في C. من خلال الترانزستورات ، من الممكن بناء عناصر منطقية AND ، أو OR ، NOT (إظهار الصورة). "

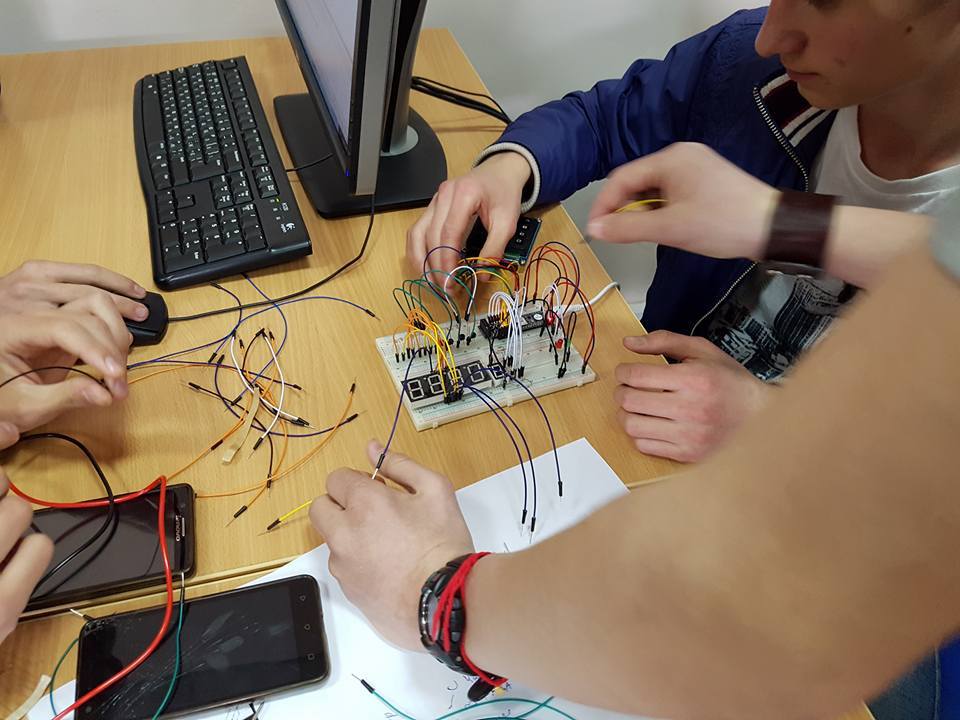

خلال المحاضرات أمام جمهور كبير ، يمكن أن تظهر للطلاب دوائر مجمعة على لوحة توصيل من دوائر صغيرة بدرجة صغيرة من التكامل. هذا مرئي ويثير الاهتمام ولا يتطلب أيضًا ربط التصميم بجهاز كمبيوتر - فقط ببطارية 9 فولت. لقد عرضت ثلاث من هذه الدوائر الأكثر أهمية للفهم - عنصر المنطق XOR ، مُجمع D-الزناد 4 بت المضمن بتردد ترتيب 1 هرتز ( أي قياس في الثانية).

يبقى السؤال مفتوحًا ما إذا كان من الممكن تعليم الطلاب فكرة خط الأنابيب ، وهي واحدة من أقوى الأفكار في التصميم الرقمي وتنظيم الحوسبة بشكل عام. لهذا ، ليس من الضروري بناء معالج ناقل ؛ يمكنك عمل جهاز حسابي ناقل . ربما يمكن ذكر ذلك في نهاية الدورة ، عندما يلعب الأطفال بما فيه الكفاية مع الدوائر التوافقية والمتسلسلة البسيطة وآلات الحالة. على الأرجح سيكون من المثير للاهتمام لمجموعة فرعية صغيرة جدًا من أطفال المدارس ، ولكن الأمر يستحق المحاولة.

للأحداث أكثر أصالة ، يمكنك استخدام المشاريع الفردية وعمل التحقق .

الرمز على GitHub يستخدم لحدث كييف 4. مصادر المعلومات لتطوير المواد المستقبلية.

4. مصادر المعلومات لتطوير المواد المستقبلية.مصادر معلومات لمعلمي مدارس التربية الرياضية ، والتي من المرجح أن تطور معظم المواد التفصيلية ، بعد التجارب الأولية مع الطلاب في أوكرانيا وروسيا ووادي السيليكون:

كتاب دراسي بقلم ديفيد هاريس وسارة هاريس "الدوائر الرقمية وهندسة الكمبيوتر" ، الطبعة الثانية ، الترجمة الروسية. يمكن تنزيل هذا الكتاب المدرسي مجانًا ، راجع مقالات حول حبري - 1 ، 2 ، 3 . في الآونة الأخيرة ، تم إصدار إصدار ورقي جديد مع طباعة ملونة محسنة .

شرائح للمعلمين بالإضافة إلى الكتاب المدرسي هاريس وهاريس. تنزيل مجاني.

مواد من دورة NAND إلى Tetris ، التي تم إنشاؤها في إسرائيل وتم تقديمها في بعض الجامعات الأمريكية. في نفس الوقت ، IMHO ، يجب أن تستخدم الدورة الأفكار والهيكل العظمي ، ولكن القيام بالتنفيذ على مجموعات فرعية من أدوات التصميم "للبالغين" ، بدلاً من أدوات "الأطفال" الاصطناعية ، كما تفعل الدورة. يتم تنزيل الأجزاء الرئيسية مجانًا.

كتاب تشارلز بيتزولد "كود" ، الذي يشرح بشكل كاف العديد من المفاهيم على الأصابع والتي يتوافق مستواها مع مستوى المدرسة (تم اقتراح الفكرة من قبل مدرس مدرسة كييف ORT سيرجي دزيوبا ). مرة أخرى ، من وجهة نظري ، يجدر استخدام الأفكار والهيكل العظمي من الكتاب ، ولكن يجب استبدال معظم المواد بأخرى أكثر صحة (بدلاً من استخدام المزالج (D-latch) استخدم D-flip-flops (D-flip-flop)) وحديثة ، على سبيل المثال ، بدلاً من المركم القائم على 6800 و 8080 القديم يستخدمان مجموعة فرعية من بنية RISC.

مجموعات لبناء الدوائر على لوحة توصيل تعتمد على مكونات منفصلة ودوائر دقيقة بدرجة صغيرة من التكامل من الشركة الأمريكية ETron Circuit Labs ، الشركة الروسية Cyberfizika ، الشركة الأوكرانية Radiomag (يمكنني شرح الاختلافات بين هذه المجموعات في التعليقات ، إذا كنت مهتمًا).

مواد مصنعي FPGAs (Xilinx ، Altera) والبطاقات التعليمية مع FPGAs (Digilent ، Terasic).

أمثلة على الكود والاختبارات وتوصيات المشروع التي طورها أنتون مويسيف ويوري بانشول ويوجين كوروتكي وألكسندر بارابانوف وغيرهم من مهندسي الشركات وأساتذة الجامعات في أحداث مختلفة في كاليفورنيا وكازاخستان وروسيا وأوكرانيا.

5. التخطيط للقضية المستقبلية 1. شكل الدورة السنوية لمدة 35 ساعة أكاديمية ، مبعثرة للعام الدراسي ، ساعة واحدة في الأسبوع

5. التخطيط للقضية المستقبلية 1. شكل الدورة السنوية لمدة 35 ساعة أكاديمية ، مبعثرة للعام الدراسي ، ساعة واحدة في الأسبوعمن الفيزياء إلى العناصر المنفصلة

ما هو التيار والجهد والمقاومة. كيف يعمل اللوح؟ تمرين: الدائرة الأولى مع بطارية ، LED ومقاوم. لماذا توصيل المقاوم بدائرة مع LED. اقرأ علامات المقاوم. المقاومات المتغيرة ، المقاومات الضوئية.

ما هو الترانزستور؟ نظرة عامة على تبديل العناصر من المرحلات والأنابيب اللاسلكية والترانزستورات المنفصلة إلى الترانزستورات في الدوائر المصغرة. تمارين مع الثايرستور (SCR - مقوم متحكم فيه من السليكون - أكثر وضوحًا من الترانزستور) ، pnp ثنائي القطب و npn الترانزستورات.

عمل التحقق.

من العناصر المنفصلة إلى المنطق التوافقي

الجبر البولياني والجبر للمنطق. العمليات والتعابير والبديهيات والهويات ، بما في ذلك قوانين دي مورغان. جداول الحقيقة.

عناصر المنطق التوافقي و OR أو NOT و AND-NOT أو OR-NOT، EXCLUSIVE-OR (AND، OR، NOT، NAND، NOR، XOR). كيف يتم بناء العناصر التوافقية من الترانزستورات. التمرين: بناء AND ، أو NAND ، أو NOR من عناصر منفصلة.

العناصر المنطقية في الدوائر المصغرة بدرجة صغيرة من التكامل. تمرين فردي: يتم إعطاء كل طالب شريحة منطقية شخصية من سلسلة CMOS 4000 ، مع وصف تقني من الشركة المصنعة ، مع مهمة رسم جدول الحقيقة ، وتوضيح عمله ووصف الوظيفة شفهيًا. تحتوي الرقائق على عناصر منطقية AND و OR و XOR و NOR و NAND مع عدد مختلف من المدخلات. ما هي مقاومات السحب وما سبب احتياجها. أضف أزرارًا ومقاومات سحب لأعلى في التمرين السابق.

عمل التحقق.

الحساب الثنائي وتنفيذه

أرقام ثنائية تحويل من ثنائي إلى عشري والعكس. عمليات الجمع والضرب. أرقام سلبية ورمز إضافي.

تنفيذ نصف جامع وكامل باستخدام العناصر المنطقية. الهجرة جامع متعدد البتات مع حمل متسلسل. تمرن على اللوح. ذكر تأخير طويل ومخططات بتأخير أمثل.

استخدام جامع كامل 4-بت CMOD 4008. البناء منه جامع 8-bit ونظام الطرح. الواجبات المنزلية للطلاب المتقدمين: للدراسة وتقديم عرض تقديمي حول تنفيذ الإضافات السريعة مع النقل الجماعي السريع.

عمل التحقق.

المنطق التسلسلي

بناء مولد ساعة يعتمد على الشريحة 555. دراسة تأثير المكثفات والمقاومات على تردد ومدة المستويات العالية والمنخفضة.

بما أن المكثفات متضمنة في الربط 555 ، فقد تكون هناك حاجة إلى تفسيرات إضافية حول ما هي المكثفات ، ولماذا هي مطلوبة في الربط 555 ، وكيف يتم تصنيفها. يمكن أن يكون التمرين الإضافي مع مكثفات الشحن والتفريغ ذات السعات المختلفة مفيدًا أيضًا.

مخططات مع حالة داخلية. بناء مزلاج RS من بوابات NAND. D- CMOS 4013 555 1 .

— (CMOS 4029) (4015). 4511. .

.

—

( ) — . Verilog, , , . : .

Verilog. , , . Always- . : , .

Verilog. . : . : .

Verilog . / . . : , Verilog. Icarus Verilog GTKWave .

: , ( ).

Verilog

Verilog, D- . : always-. Icarus Verilog.

: D-, . . : .

. . : .

. ( ) c . : , : , .

. , .

.

: , RISC- , MARS MIPS .

- . : , , , . . . — MARS MIPS. .

, , . : . .

. . . : , . .

.

:

Verilog MIPS , , . , , . . .

9.1

6. 2.

6. 2., .

, . . .

. CMOS 4000, , , . AND, OR, XOR, NOR, NAND . , .

2 , .

4- CMOD 4008.

8- 4-.

-a == ~ a + 1

555. .

D- CMOS 4013 555 1 .

“ ” CMOS 4015.

(CMOS 4029) 4511.

( ) — . Verilog, , , . Verilog, , . Always- .

.

, .

Verilog. . Verilog . / . .

: .

, Verilog. Icarus Verilog , GTKWave .

Verilog. Verilog, D- . : always-. Icarus Verilog. .

.

.

.

2 3 .

. . . ( ) c .

“ ”.

.

.

: . - . MARS MIPS .

: , , , . . . .

, , . .

. . . , . .

: .

Verilog MIPS , , . , , . . .

.

الملحق أ. ما هي لغة وصف أجهزةVerilog ومدى ارتباطها بتصميم الدوائر المصغرة من منشور على موقع Geektimes Microelectronics محتالون . تقرير بالفيديو من مؤتمر تصميم الإلكترونيات في سان فرانسيسكو.

الملحق أ. ما هي لغة وصف أجهزةVerilog ومدى ارتباطها بتصميم الدوائر المصغرة من منشور على موقع Geektimes Microelectronics محتالون . تقرير بالفيديو من مؤتمر تصميم الإلكترونيات في سان فرانسيسكو.25 Verilog ( — VHDL), (logic synthesis) , (static timing analysis) , , (place-and-route) .

: , , , , static timing analysis, floorplanning, place-n-route, parasitics extraction .. — GDSII, , . Taiwan Semiconductor Manufacturing Company TSMC.

الملحق (ب) ما هو FPGA / FPGA والسبب في دراسة FPGA لا يمكن أن تحل محل دراسة أكثر عمقا اردوينو أو التوت بايمن منصب حبري كيف للبدء في تطوير الأجهزة باستخدام FPGA - تعليمات خطوة بخطوة :

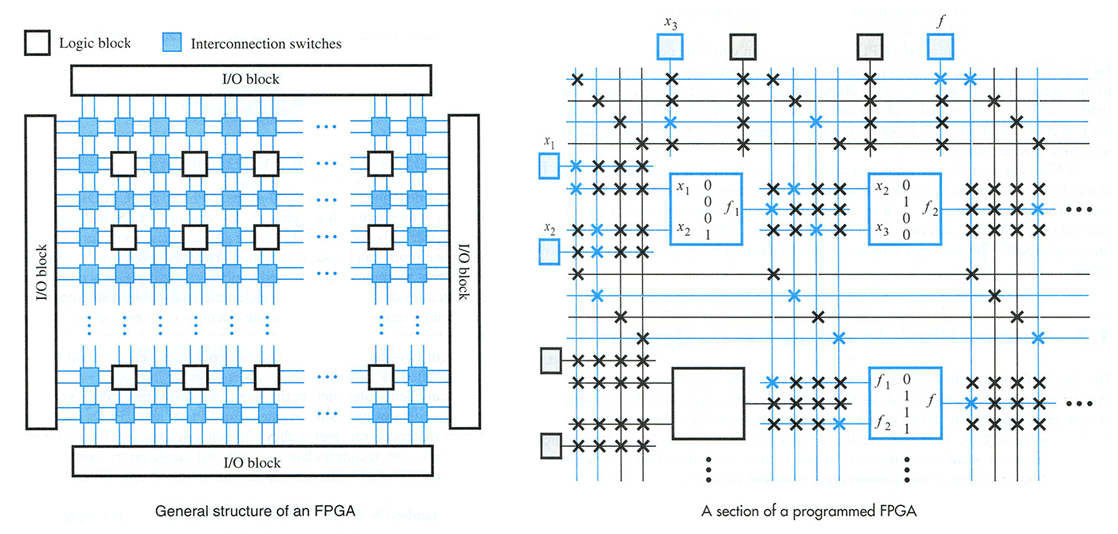

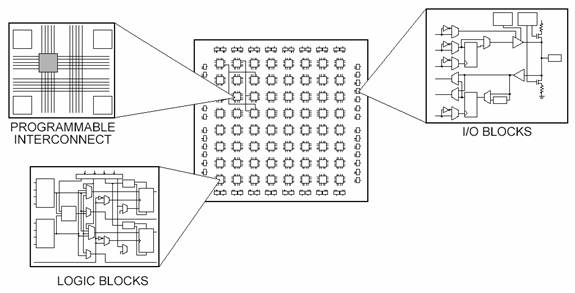

الملحق (ب) ما هو FPGA / FPGA والسبب في دراسة FPGA لا يمكن أن تحل محل دراسة أكثر عمقا اردوينو أو التوت بايمن منصب حبري كيف للبدء في تطوير الأجهزة باستخدام FPGA - تعليمات خطوة بخطوة :FPGA , , . AND , — .. — FPGA , , ..

- / FPGA — , «» ( -) (), ( ) ().

— FPGA, look-up table (LUT) flip-flop. , , .

, FPGA:

:

C. ,

C. ,(system on chip, SoC), IP- (CPU, GPU, DSP) — , . ADAS (advanced driver-assistance systems) .

, , , ( 1980- — 1990- ). (hardware description languages — HDL), (register transfer level — RTL), RTL-to-GDSII, Verilog VHDL , FPGA (field-programmable gate arrays). , -, -. HDL RTL , , , , 1980- .

بالإضافة إلى المؤتمر في تومسك والتجربة التالية المخطط لها في يوليو ونوفوسيبيرسك ، والتي تدعمها مدرسة نوفوسيبيرسك الصيفية للمبرمجين الشباب ، هناك أيضًا خطة مبكرة لتنظيم مثل هذه التجربة في كازاخستان (هذا مهتم بشكل خاص بحضور فينوس زانالينا في ندوة كييف). الملحق د. أمثلة على كود Verilog البسيط والمخططات الناتجة عنه

الملحق د. أمثلة على كود Verilog البسيط والمخططات الناتجة عنهmodule adder

(

input a,

input b,

input carry_in,

output reg sum,

output reg carry_out

);

reg p, q;

always @*

begin

p = a ^ b;

q = a & b;

sum = p ^ carry_in;

carry_out = q | (p & carry_in);

end

endmodule

module counter

(

input clock,

input resetn,

input load,

input [15:0] load_data,

output reg [15:0] count

);

always @ (posedge clock or negedge resetn)

begin

if (! resetn)

count <= 0;

else if (load)

count <= load_data;

else

count <= count + 1;

end

endmodule

كيف يعمل: يوجد

كيف يعمل: يوجد شرح مفصل في النص "مقدمة في تصميم شرائح Harver للمبرمجين الذين لم يفعلوا ذلك أبدًا . "إذا كنت معلمًا وترغب في المشاركة في تطوير مثل هذه المواد (كل هذا على أساس طوعي ، دون التواصل مع شركة معينة) ، فأخبرني بذلك في التعليقات. أي انتقاد مثير للاهتمام أيضا.

شرح مفصل في النص "مقدمة في تصميم شرائح Harver للمبرمجين الذين لم يفعلوا ذلك أبدًا . "إذا كنت معلمًا وترغب في المشاركة في تطوير مثل هذه المواد (كل هذا على أساس طوعي ، دون التواصل مع شركة معينة) ، فأخبرني بذلك في التعليقات. أي انتقاد مثير للاهتمام أيضا.