في كل مقال حول حبري مكرس للمعالجات الدقيقة المحلية ، بطريقة أو بأخرى ، يتم طرح مسألة كتل IP المرخصة ومدى إثارة وجودها وغيابها لقيمة التنمية أو أهليتها أو أمنها. في الوقت نفسه ، لا يفهم العديد من المعلقين موضوع المناقشة جيدًا ، لذلك دعونا نحاول معرفة كيفية عمل الترخيص في صناعة الإلكترونيات الدقيقة ، وما هي الكتل المرخصة الجيدة والسيئة ، وما هي عملية تطوير دائرة صغيرة إذا تم شراء معظم الكتل فيها.

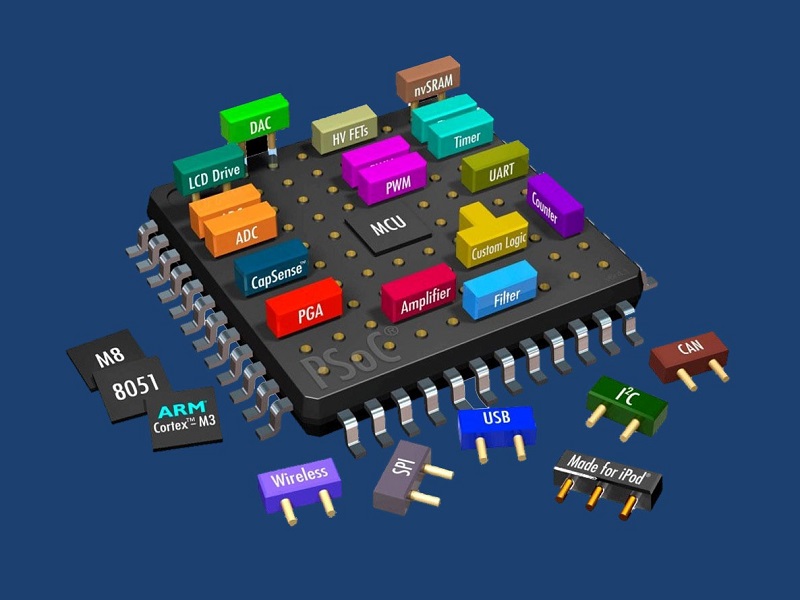

أي دارة دقيقة حديثة هو ما كان يطلق عليه بفخر "نظام على رقاقة" منذ بعض الوقت: حتى المنظمات الخطية ثلاثية الأرجل ومصادر الجهد لديها تعديل رقمي مخفي عن المستخدم ، ماذا يمكننا أن نقول عن المعالجات الدقيقة والمتحكمات الدقيقة التي تحتوي على عشرات الكتل المختلفة ، وتطوير كل منها والتي تتطلب مهارات محددة وخبرة واسعة للتحايل على المزالق التي لم يتم الكتابة عنها في الكتب والمقالات. علاوة على ذلك ، فإن أي مشروع ، كقاعدة عامة ، له ميزة قاتلة خاصة به ، حيث يتوقع المطورون الحصول على ميزة على المنافسين ، وهذه الميزة القاتلة هي التي يجب القيام بها قدر الإمكان ، ويجب ألا تكون جميع الكتل الأخرى ببساطة أسوأ من غيرها.

الانتباه ، والسؤال هو: هل من الضروري الحفاظ على فريق تطوير مكلف يمكنه بشكل مستقل صنع كل الكتل الضرورية بمفرده؟

سؤال أكثر إثارة للاهتمام: إذا كنت قد قمت بتطوير نظام تعليمي للمعالجات الدقيقة ، هل تحتاج إلى احتواء فريق مبرمج

سيكتب مترجمًا له ، وينقل نواة جديدة لأنظمة التشغيل الشائعة ، ويقوم بالكثير من العمل الشاق الآخر ، وعلى الأرجح لن يضع ابتكارك على أحد مع البنيات الشعبية ، التي يعمل عليها الكثير من الناس؟

والأهم من ذلك: هل ستعطي الإجابات الإيجابية على السؤالين السابقين مزايا تنافسية لمنتجك؟

الاستطراد الغنائيفي 5 يونيو ، تقاعد موريس تشانغ ، وهو رجل لم تسمع به من قبل ، ولكن بدونه لن تكون هناك إلكترونيات حديثة. ولد موريس تشانغ في الصين ، في ذروة الحرب الأهلية التي غادرها إلى الولايات المتحدة ، وتخرج من معهد ماساتشوستس للتكنولوجيا ، ثم عمل لسنوات عديدة في شركة Texas Instruments و General Instruments. في تلك السنوات ، كان جزءًا لا يتجزأ من أي شركة إلكترونيات دقيقة هو إنتاجها الخاص ، وكانت المعدات التي كان لها عدة طلبات من حيث الحجم أرخص من الآن ، ولكن مع ذلك ، كانت باهظة الثمن. هنا كيف كتب تشانغ نفسه عن ذلك:

عندما كنت في TI و General Instrument رأيت الكثير من مصممي IC يريدون المغادرة وإنشاء أعمالهم الخاصة ، ولكن الشيء الوحيد ، أو أكبر شيء منعهم من مغادرة تلك الشركات هو أنهم لا يستطيعون جمع ما يكفي من المال لتشكيل شركتهم الخاصة. لأنه في ذلك الوقت كان يعتقد أن كل شركة تحتاج إلى التصنيع ، وتحتاج إلى تصنيع الرقاقات ، وهذا هو الجزء الأكثر كثافة لرأس المال من شركة أشباه الموصلات ، من شركة IC. ورأيت كل هؤلاء الناس يريدون المغادرة ، لكن تم إيقافهم بسبب عدم القدرة على جمع الكثير من المال لبناء رقاقة.

في عام 1985 ، كان موريس تشانغ على وشك التقاعد ، ولكنه قبل بدلاً من ذلك عرض الحكومة التايوانية بالعمل في معهد أبحاث التكنولوجيا الصناعية ، وهو معهد أبحاث كان من المفترض أن يساعد في إحداث ثورة صناعية في تايوان وسد الفجوة بين الاقتصاد المتقدم والدول المتقدمة. في عام 1987 ، وبالتوازي مع عمله في ITRI ، أنشأ Chang شركة TSMC ، وهي شركة نمت لتصبح أكبر مصنع للدوائر المتكاملة في العالم. استند نموذج أعمال TSMC في الأصل إلى حقيقة أن الشركة لا تطور أي شيء ، ولكنها تنتج فقط تطورات الآخرين ، وكانت هذه واحدة من الخطوات الأولى في إنشاء نظام بيئي حديث لتطوير وإنتاج الدوائر المصغرة ، والمعروفة باسم نموذج Fabless.

نهاية الانحدار الغنائيما هو فابليس؟

Fabless هو نموذج لتطوير وإنتاج الدوائر المصغرة حيث لا تمتلك الشركة المطورة إنتاجها الخاص وتستخدم خدمات مصنع تابع لجهة خارجية يتعاون أيضًا مع مطورين آخرين (وأحيانًا يكون لديها منتجاتها الخاصة).

يمكن أن يقلل وجود مصانع الطرف الثالث بشكل جذري من عتبة دخول سوق الإلكترونيات الدقيقة (التي حلم بها موريس تشانغ في وقت واحد) ، من مئات إلى ملايين الدولارات ، بسبب عدم الحاجة إلى شراء وصيانة معدات الإنتاج. كما يسمح لك بتقليل هذه العتبة بشكل أكبر بسبب تشكيل سوق لموردي الكتل الوظيفية المعقدة (وهم أيضًا Silicon IP). إذا أنتجت رقائق في المصنع الخاص بك ، فيمكنك الاعتماد فقط على نقاط القوة الخاصة بك ويجب أن تحتوي على فريق يمكنه إنشاء جميع الكتل الضرورية. إذا لم يتم استخدام المصنع من قِبلك فقط ، ولكن أيضًا من قبل شركات أخرى ، فقد قام شخص ما بالفعل بحل معظم المهام النموذجية المعروضة عليك ، ويمكنك استخدام نتائج عمل شخص آخر - أو إعادة بيع الحل الخاص بك إلى شخص آخر ، بعد أن وافق مسبقًا على السعر والشروط بحيث لم يبق أحد في الخاسر. بالطبع ، من غير المحتمل أن تبيع خبرتك لتوجيه المنافسين ، ولكن هناك الكثير من المواقف التي يمكنك أن تكسب فيها دون التورط في تضارب في المصالح. كان من المحتمل والرغبة في إعادة استخدام نتائج حل المشكلات النموذجية التي ظهرت في سوق كتلة IP ، والتي كان حجمها حتى عام 2017 يقترب من أربعة مليارات دولار ويستمر في النمو بسرعة.

كيف هي مربحة؟

المشتري IP - الادخار في المقام الأول. وفقًا لتقديرات مختلفة ، فإن شراء كتل IP عادة ما يكون أرخص مرتين إلى خمس مرات من التطوير الذاتي. بالإضافة إلى ذلك ، يسمح لك الشراء عادةً بتقليل وقت التطوير بشكل ملحوظ ، حيث لا تحتاج إلى إنتاج رقائق اختبار بشكل مستقل وإصلاح الأخطاء.

إلى مطور بروتوكول الإنترنت - فرصة لبناء عمل تجاري على حل متخصص وتقليل تكلفة ممارسة الأعمال بشكل كبير. جزء كبير من تكلفة الدائرة الصغيرة هو تكلفة التسويق والتعبئة والاختبار والدعم الفني وبرمجيات التطبيق ، وأخيرًا ، نماذج الصور للإنتاج الضخم ، إلخ. الخ. إذا كنت لا تنتج منتجات تامة الصنع ، ولكنك لا تبيع سوى القطع ، فلن يكون لديك جميع هذه النفقات.

المصنع - فرصة لجذب المزيد من العملاء. تسعى المصانع الكبيرة إلى إنشاء نظام بيئي لموردي كتلة IP من حولهم ، لأن استخدامها يمكن أن يسرع بشكل كبير في التصميم ، والأهم من ذلك ، أتمتة ذلك قدر الإمكان. تعتبر مجموعة غنية من المكونات الجاهزة مساعدة كبيرة في تصميم المنتج النهائي ، لأنها تتيح لك القيام فقط بما لديك من دراية بنفسك وعدم إنفاق الموارد الثمينة على تطوير كل شيء بشكل عام - خاصة في الحالات التي يوجد فيها بالفعل حل جاهز تم تطويره من قبل الناس الذين استثمروا في تطويره وقتًا وخبرة أكبر بكثير مما يمكنك تحمله. وفقًا لذلك ، يمكن أن تكون مجموعة واسعة من عناوين IP الجاهزة عاملاً جادًا في اختيار مصنع معين لإنتاج مشروعك.

كيف يعمل؟

دعونا نلقي نظرة على ترخيص النوى باستخدام مثال نظام مخصص كروي على رقاقة. سيحتوي النظام على قلب معالج ، وحافلات لدمج النواة والأجهزة الطرفية ، وكمية معينة من ذاكرة التخزين المؤقت ، وواجهات للتواصل مع العالم الخارجي (مثل CAN و I2C) ، PLL ، DAC و ADC. لنقاء التجربة ، افترض أن كل شيء سيتم شراؤه على الإطلاق ، دون تطوير مستقل. تقول "افتراض غبي" ، ولن تكون على حق تماما. في الواقع ، بالطبع ، مثل هذه الحالات نادرة للغاية ، ولكن لا يزال من الممكن جدًا أن نتخيل أن الميزة القاتلة للمنتج لن تكون كتلة في حد ذاتها ، ولكن مجموعة محددة من الكتل الموجودة. على سبيل المثال ، أنت أول مشترٍ لكتلة (وبالتالي ، لا يمتلكها المنافسون بالفعل) أو توصلت إلى كتلة موجودة لاستخدامها في شريحة غير مميزة بالنسبة لها (وبالتالي ، لا يوجد لدى المنافسين في هذا الجزء أي شيء مشابه).

لذا ، لنبدأ بـ ...

... لا ، ليس من قلب المعالج ، ولكن من الربط التناظري. على سبيل المثال ، خذ المحول التناظري إلى الرقمي (ADC) - وهو وحدة نموذجية لمعظم المتحكمات الدقيقة وأي أنظمة أخرى تتعامل مع البيانات من العالم الخارجي.

إن ADC عبارة عن كتلة تناظرية ، مما يعني أن معلماتها تعتمد بشكل خطير ليس فقط على داراتها ، ولكن أيضًا على كيفية تنفيذ هذه الدوائر بالضبط على رقاقة. إذا أخذنا الملف النهائي مع الطوبولوجيا من عملية تقنية واحدة وأنتجناه في مصنع آخر بنفس معايير التصميم ، فيمكننا الحصول على معلمات مختلفة تمامًا (ناهيك عن التحويل إلى معايير تصميم أخرى). ومع ذلك ، فإن ثقافة "الموردين الثانيين" ، المعروفة من منتصف القرن ، لا تزال موجودة ؛ على سبيل المثال ، يقدم مصنع Towerjazz نسخًا من بعض عمليات تصنيع TSMC.

يعد ADC مثالاً رائعًا لكتلة IP ثابتة مرتبطة بعملية معينة. من أجل شراء مثل هذه الوحدة ، يجب أن تعرف بالضبط ما هي التقنية التي سيتم تصنيع منتجك النهائي عليها ، وكما هو مذكور أعلاه ، يمكن أن يكون توفر عنوان IP الصلب الضروري ميزة تنافسية خطيرة للمصنع.

كيف يتم تسليم Hard IP؟ هذا سؤال مثير للاهتمام ، وللإجابة عليه ، من الضروري مناقشة الشكل الذي يتم تطويره. في حالة معظم الكتل التناظرية ، يتم تطوير الدوائر على مستوى الترانزستورات الفردية ، أي أن ملفات الإخراج ستكون ملف الدائرة الكهربائية والملف مع الهيكل. علاوة على ذلك ، يمكن أن يكون لميزات المخطط والطبولوجيا قيمة تجارية خطيرة ، والتي بالطبع لا أريد أن أعطيها للجانب. ولكي لا يتمكن العميل من إجراء هندسة عكسية للمخطط من خلال الهيكل ، عادة لا يتم إرسال الهيكل أيضًا ، وبالتالي ، في الحالة المعتادة ، تبدو الملفات التي تم تسليمها كما يلي:

- بدلاً من الدائرة الكهربائية ، يتلقى العميل نموذجًا سلوكيًا عالي المستوى لا يكشف عن ميزات التنفيذ. يمكن كتابة هذا النموذج في Verilog-A. والبديل هو أن بعض أنظمة CAD (على سبيل المثال ، Cadence Virtuoso) تدعم تشفير الدوائر الكهربائية ، أي أن العميل سيكون قادرًا على استخدام دائرتك (أو ملف verilog-A) ، ولكنه لن يتمكن من فتح المحتويات وعرضها.

- تخطيط الأبعاد للطبولوجيا ، مع استنتاجات خارجية ملحوظة ووصف لعدد مستويات التعدين التي تحتلها كتلة.

- بيئة اختبار للتحقق من المعلمات الرئيسية.

- التوثيق

في هذه الحالة ، بالطبع ، مشاركة طرف ثالث ضرورية ، والتي يمكنك نقل الطبولوجيا دون خوف من المنافسة والهندسة العكسية. هذا الطرف الثالث هو المصنع ، ويعتبر دوره الوسيط بين العملاء والمقاولين جزءًا مهمًا من النظام البيئي لتطوير الرقائق. بالطبع ، يجب أن يكون للمصنع سمعة واضحة تمامًا (هذا عن الإشارات المرجعية) ، ومن الناحية المثالية ، يجب ألا ينتج أي شيء مماثل من تلقاء نفسه ، لأن العمل في مصنع لشركة منافسة هو في أي حال متعة مشكوك فيها. تنجح Samsung في إنتاج معالجات في نفس الوقت لنفسها ولأبل ، ولكن المصانع الكبيرة الأخرى عادة ما تركز إما على إنتاجها الخاص (مثل Intel) ، أو تتخلى تمامًا عن التطوير الذاتي (مثل TSMC). بالمناسبة ، كانت الرغبة في التخلص من تضارب المصالح هذا أحد العوامل الدافعة لتخصيص Globalfoundries (ثاني أكبر لاعب في سوق المصنع) من AMD.

الاستطراد الغنائيبالمناسبة ، في روسيا ، لا توجد مصانع في روسيا. علاوة على ذلك ، بالنسبة لجميع اللاعبين في السوق على الإطلاق ، فإن إنتاج منتجاتهم الخاصة يمثل أولوية ، ويتم تصنيع جميع الرقائق المحلية بالكامل التي ينتجها مطورو عابرون في مرافق منافسيهم المحتملين - أو في مصانع اللعب الخالص في الخارج.

نهاية الانحدار الغنائيعلاوة على ذلك ، هناك تفاصيل مهمة أخرى للتفاعل بين المورد والمصنع: يدخل المصنع كتلة IP الخاصة بك في قاعدة البيانات الخاصة به ويراجع أيضًا جميع المشاريع الواردة بحثًا عن وجود الهيكل الخاص بك (الذي يمكن أن يحصل عليه شخص ما منك وكذلك بشكل غير قانوني) ، و تحقق معك بشأن ما إذا كان الشخص الذي يطلب الإنتاج لديه ترخيص (نظرًا لأن العديد من التراخيص الرخيصة تشير إلى استخدام الوحدة في مشروع واحد فقط). يسمح وجود تحقق من المصنع لمطور Hard IP باختيار أي خيار ترخيص مناسب - مرتبط بعدد المشاريع ، وعدد الرقائق المباعة ، وتوقيت إطلاق الرقائق في الإنتاج ، إلخ. الخ. ولكن المزيد عن أنواع التراخيص في الجزء التالي.

مثل Hard IP في نظام نموذجي على شريحة ، ستحتاج إلى ADCs و PLL والطبقات المادية لواجهات الإدخال / الإخراج.

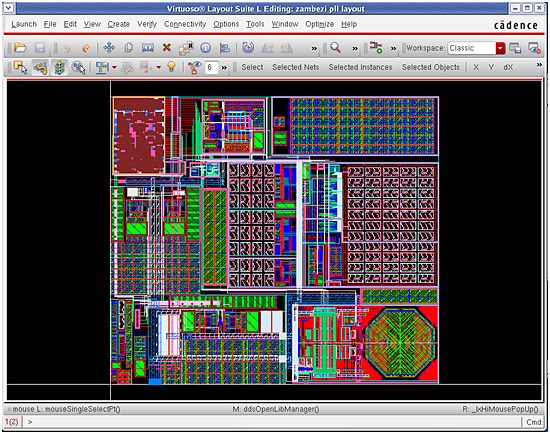

نافذة CAD Cadence Virtuoso Layout Suite مع طوبولوجيا كتلة IP الثابت التناظرية (هذه هي PLL ، إذا كان أي شخص مهتمًا). الحدود الواضحة بين الوحدات الفرعية الفردية (والتي عادة ما يتم إجراؤها من قبل أشخاص مختلفين) ، على سبيل المثال ، عنصر نادر جدًا للدوائر المتكاملة - المحرض في الزاوية اليمنى السفلى ، يمكن رؤيته بوضوح. وفي الجزء العلوي الأيسر توجد كتلة رقمية (ربما تحكم) وواجهة متعددة بت إلى الباقي.

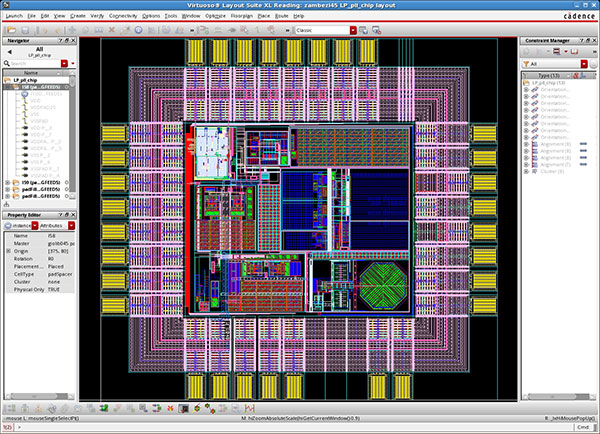

إنه نفس الشيء ، ولكن بالفعل في شكل رقاقة منتهية (على سبيل المثال ، للاختبار). يمكن رؤية وسادات الإدخال / الإخراج والحلقات التي تربطها من الأراضي والإمدادات بوضوح.

يستخدم مصطلح "Hard IP" أيضًا فيما يتعلق بفدرات IP لـ FPGA. في هذه الحالة ، من المفهوم أن كود الكتلة قد تم تحسينه للاستخدام في طراز FPGA معين وتم تصنيعه لوضعه فيه.

Soft IP

الكتلة التالية التي سننظر فيها هي نواة المعالج. في الواقع ، يمكن أن تكون أي دائرة رقمية تقريبًا في مكانها ، على سبيل المثال ، وحدة ترميز إشارة برمز Reed-Solomon ، ولكن نوى المعالج تُسمع على نطاق واسع وتشكل نصفًا جيدًا من السوق بالكامل (بما في ذلك بسبب التعقيد والتكلفة العالية).

الفرق الرئيسي بين تطوير الدوائر الرقمية وتطوير الدوائر التناظرية هو أن الدوائر الرقمية عادةً ما تكون مكتوبة بلغات خاصة عالية المستوى - Verilog أو VHDL ، ثم يقوم نظام CAD خاص بتجميع الدائرة الكهربائية والطبولوجيا من هذا الرمز. لذلك ، حتى وقت التجميع ، لا يرتبط الرمز بتقنية معينة ، ويمكن إنتاج نفس الكتلة في مصانع مختلفة (أو مخيط في FPGA) أو في إصدارات مختلفة من نفس التكنولوجيا (على سبيل المثال ، محسنة للسرعة العالية أو استهلاك منخفض للطاقة) . هذا ، في الواقع ، يتم استخدامه من قبل شركات التطوير ، على سبيل المثال ، ARM. تسمى هذه الكتل الرقمية غير المرتبطة بتقنية معينة Soft IP.

هنا مخطط بت واحد adder:

وإليك ما يبدو عليه مُعلِم ثماني بتات في تصميم شرائح:

module adder(

input wire [7:0]a,

input wire [7:0]b,

output wire [7:0]out,

output wire carry

);

assign {carry, out} = a + b;

endmodule

, , , . , IP- .

Soft IP? :

• Clean, readable, synthesizable Verilog HDL, VHDL

• Cadence Encounter RTL Compiler synthesis scripts

• Documentation – integration and user guide, release notes

• Sample verification testbench

Encrypted source along with a complete certification data package (CDP) including all artifacts required for chip-level compliance.

, — , ( IP ). , . , - -, , .

, LEON3:

- , Cobham Gaisler, LEON3 GPL

- LEON3FT ( ): The LEON3FT core is distributed together with a special FT version of the GRLIP IP library, distributed as encrypted RTL.

- ( ) , LEON2FT, .

, , Verilog-, . Verilog- , , , , . digital watermarks, , IP.

, “Clean, readable, synthesizable” , , IP . , , , ( , hardware trojans) , , , .

, : soft IP , , ? , Soft IP, , .. .… :

ARM, , , , , ( ), IP , - , , . . (, , , ). Apple Imagination Technology in-house , Apple , Imagination ( ).

, — ( IP ) ( ).

soft IP FPGA, , . , Xilinx IP, ( ) , , ( , ).

, , .

— IP- . , -, . , IP, , IP , , IP ( , ); , - .

— . , ( IP).

— . , , , . — . , , .

— , , (, ARM Cortex). — , .

— . (, , ) , — ( , , ). ? , ( - , , ) . , , , , , — .

? : , , , . , Apple, ARM - , , (, ARM ) — .

: , , , , , , ( — ). , , . , , Apple, , , ! ARM, , Apple . , ARM . , , Apple — PowerPC, , PowerPC x86, Apple Intel.

Soft IP , - , IP . :

- , “ — ”, .

- - IP ( ), IP, IP ( IP hardening) . ? , , , .

soft IP ( ), , , .. ..

Configurable IP

IP, hard soft — , . - , - . ? , IP-? ?

( , FPGA) , , , . , , IP- Hard IP, Soft IP ( , ).

— -.

Foundation IP

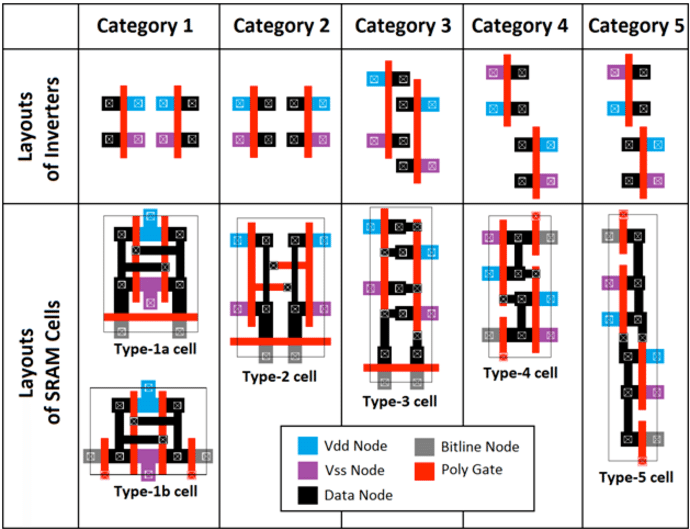

«-hard» IP- — foundation IP, . — , . , , , , , . , , ( ) , (, ) . «generic» , , , , , .

Foundation IP -, , , .

BarsMonster .

Verification IP

, , — , . , , , . , , . , - . “”. .

, — Verification IP. — , , ( ). Synopsys , , Synopsys — IP-. IP Design&Reuse Synopsys 828 Silicon IP ( ARC — ARM) 116 Verification IP .

verification IP CAN, ( APB AHB ARM) - . , , , .

?

, , , , ? .

:

- , ( verification IP ).

- — .

- ( , ).

- Soft IP , .

- , , .

- , , .

- , .

- , ( ).

, , ( ). , - , « - BGA 400-700 ». , Hard IP- 400-700 , , , 4-8 (, Soft IP). — ? , . , «-» .

— Synopsys IC Compiler , .

, — , , , , , , .

, , fabless- IP- , , , . , , ( “”) , , : , , , , , , - . , , — .

: Open Source?/ Open Source . , - ( ) , - . , , - . , , .

—

Opencores.org, — OpenRISC, ( FPGA), ASIC ( Samsung). Opencores, , - , ( ARM), FPGA. FPGA Proven, — ASIC Proven.

—

RISC-V. ( OpenPOWER OpenSPARC) , - , , ( ).

RISC-V — , MIPS, , , , ( , MIPS). RISC-V Foundation Google, Samsung, NXP, NVIDIA . , , , , OpenPOWER, , , ARM , ARM, , , ( Intel). - . RISC-V (

RISC-V), - , . , ,

RISC-V — Falcon NVIDIA.

: ?OpenCores, IP- ( ) . :

TSMC IP Alliance, IP .

Design&Reuse, IP-, ( ).

ChipEstimate, D&R, .

— ?, , , - .

— “” (), “” ( ), “” “” (211), “Neuromatrix” ( “”), RISC-V (Syntacore), ARM, MIPS, SPARC, MCS96, MCS51, C166, AVR, MSP430.

,

“ ” ( ):

IP-:

: ARM Cortex-M4F, ARM Cortex-M0, ARM946E-S c AMBA, ARM VFP9-S, SPARC v.8 c AMBA. 8- RISC .

IP- (PLL) TSMC, KeyASIC AnalogBits, Sidense Memory, - (eFuse) TSMC, IP- , ROM RAM ..

“ ” , IP- - (-, IP-).

IP? IP- (

“ ”,

“”,

211), . Design&Reuse ChipEstimate “ ” ( ) NTLab. , .