في الأسبوع الماضي ، أعلنت Intel عن الاستحواذ على eASIC ، التي تعمل على تطوير أدوات تطوير تعتمد على FPGA لـ "ASICs الهيكلية". ASIC الهيكلية هي تقاطع بين FPGAs التقليدية و ASICs التقليدية ؛ تسمح لك بتقليل الوقت اللازم لتسويق المنتج وتقليل تكلفته.

تستخدم Intel تقنية eASIC

منذ عام 2015 في الإصدارات المخصصة من معالجات Xeon ؛ ستصبح eASIC (120 شخصًا) الآن جزءًا من مجموعة حلول Intel القابلة للبرمجة (PSG).

حتى أولئك الذين لديهم صداقات متبادلة لـ FPGA و ASIC لن يرفضوا شرح "ASICs الهيكلية" منذ زمن طويل والذين لا تقتصر قوة الكمبيوتر على وحدة المعالجة المركزية أو وحدة معالجة الرسومات ، فهناك فئات أخرى من المعالجات ، على سبيل المثال ، FPGA - تم تطويرها بواسطة Altera ، التي حصلت عليها Intel. في FPGA ، يمكن برمجة ملايين البوابات بمرونة لتنفيذ الوظائف المطلوبة. في الواقع ، يتم محاكاة معظم وحدات المعالجة المركزية ووحدات معالجة الرسومات في البداية على FPGAs لاختبار الأداء. FPGA هي طريقة بسيطة لنمذجة دوائر التوصيل البيني ، ونطاقها واسع. قد تحتوي FPGA أيضًا على وحدات أجهزة جاهزة ، مثل نوى ARM أو أجهزة إرسال / استقبال للاتصالات الخارجية.

مثال آخر هو ASIC (الدائرة المتكاملة الخاصة بالتطبيق) ، وهي شريحة مصممة لأداء مجموعة محددة من المهام. تم تحسين ASIC إلى أقصى حد لمهامها ، ولا يمكن تغيير منطق عملها. في كثير من الأحيان ، يتم تصنيف وحدة المعالجة المركزية ووحدة معالجة الرسومات على أنها ASICs بمعنى أن معماريتها الدقيقة ثابتة أيضًا ، ولكن تم تصميمها لحل مجموعة متنوعة من المشكلات وهي عالمية ، في حين يتم إنشاء ASICs لأنواع محددة من الحسابات بوضوح. ميزات ASIC: فهي سريعة واقتصادية ولكنها مكلفة نسبيًا ويصعب تصنيعها.

يمكن أن تسمى ASICs الهيكلية EASIC حل فاتر. ينشئ المهندسون نموذجًا أوليًا باستخدام FPGA ، لكنهم لا يضيعون الوقت في تحسين دوائرهم ، ولكنهم يصنعون شريحة ذات بنية ثابتة على أساسها. ونتيجة لذلك ، فإنها تعمل بشكل أسرع من عينة ذات كتل مخصصة ، على الرغم من أنها تفقد فوائد كفاءة الطاقة. ومع ذلك ، فإن وقت تطويرها قابل للمقارنة مع FPGA ، وليس ASIC - فهو يوفر ما يصل إلى 6 أشهر. تتمثل مساهمة eASIC في أن تحسين طبقة واحدة يستخدم لاستبدال توجيه SRAM بنهاية إلى نهاية ، مما يقلل بشكل كبير من تكاليف الإنتاج. توفر eASIC أيضًا مكتبات خلوية ثابتة ، وأيضًا طبقة واحدة ، مما يقلل بشكل أكبر من الاستهلاك ، وحجم الكريستال والوقت في السوق. أيضًا ، يمكن للمصممين تخطي الإجراءات القياسية عند إنشاء ASICs ، مثل موازنة المزامنة ، وتحليل سلامة الإشارة ، واختبار توهين الطاقة ، وغيرها. وبالتالي ، يمكن وصف "ASICs الهيكلية" بأنها FPGAs التي لا يمكن برمجتها بشكل أكبر ، والتي لها أفضل الصفات لكل من FPGAs و ASICs.

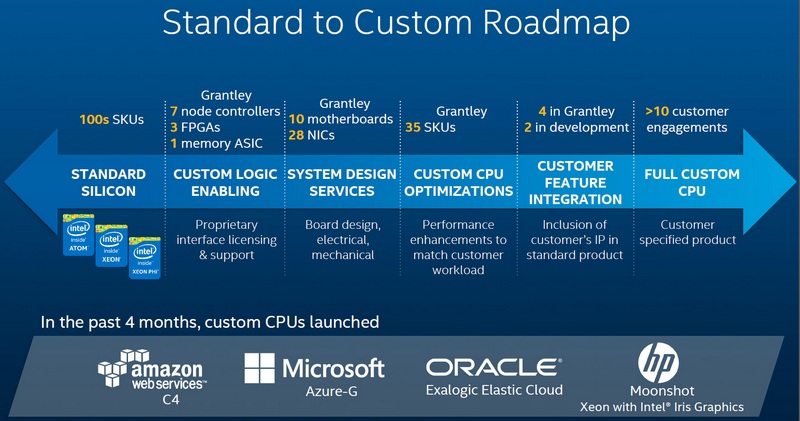

يوضح الرسم البياني الحالة الراهنة والآفاق في مجال معالجات Intel Xeon المخصصة

يوضح الرسم البياني الحالة الراهنة والآفاق في مجال معالجات Intel Xeon المخصصةتحتاج Intel إلى تقنية eASIC لدمج المنطق القابل للبرمجة في معالجات Xeon لتحسين الأداء واستهلاك الطاقة والسعر. إلى جانب Xeon القياسي ، تطلق Intel الآن خيارات مخصصة لأكبر عملائها. كما نرى من الرسم البياني ، سيزيد عمق التخصيص. مع اقتناء eASIC ، ستتسارع هذه العملية وتتوسع. يبدو أن أسلوب "CPU as ASIC" يمكن أن يجلب لنا الكثير من الأشياء المثيرة للاهتمام.