1. مقدمة

نعلم جميعًا مشكلة الدجاج والبيض: لا يرغب أرباب العمل في توظيف الخريجين دون خبرة عمل ، ولكن أين يمكن للخريجين إذن الحصول على خبرة في العمل؟ في الإلكترونيات الدقيقة ، تكون هذه المشكلة حادة بشكل خاص في ضوء الكم الهائل من الخبرة المحددة المطلوبة. منذ العصور السوفياتية ، تشتهر جامعاتنا بأوسع تدريب نظري ، والذي يجب أن يساعد الخريجين في أي موقف صعب في الحياة. ومع ذلك ، تتطلب الصناعة الحديثة خبرة عملية. نضيف هنا قلة الحافز ، الأمر الذي يؤدي إلى حقيقة أن 15٪ من الخريجين يعملون في التخصص ، ونحصل على النقص الحاد في الموظفين في الصناعة ، وهو ما يتطلب الكثير من نوعية الموظفين. ولكن إذا استطاع كل طالب "وميض مصباح كهربائي" من بلورته ، فقد يتطور الوضع بطريقة مختلفة تمامًا.

الشكل 1. KDPV

ما الذي يمنع مثل هؤلاء العمالقة من تدريب الإلكترونيات الدقيقة المحلية ، مثل MEPhI و MIET ، من التصرف بشكل مماثل مع زملائهم الأجانب (على سبيل المثال ، MIT أو UZH) ، أي بالسماح لطلاب الدراسات العليا بإصدار بلوراتهم الخاصة؟ بالطبع ، يمكن الافتراض أن إنتاج الكريستال الخاص به هو مهمة طويلة ومعقدة ومكلفة للغاية ، وبالتالي فهو مكلف بالنسبة للمعهد ومستحيل للطالب. ومع ذلك ، هذا ليس كذلك. دعونا نلقي نظرة على إحدى التقنيات المتاحة في سوق الإلكترونيات الدقيقة المحلية ، والتعارف معها سيسمح للطالب بأن يصبح أكثر جاذبية من حيث التوظيف في المستقبل ، وسيسمح العرض الذي يقدمه للطالب للجامعة بزيادة تصنيفها بشكل كبير في نظر المتقدمين وأصحاب العمل.

2. ما هو BMK؟

BMK هو بلورة مصفوفة أساسية. ألم تصبح أكثر وضوحا؟ ثم خذ خطوة إلى الجانب وانظر إلى دورة إنتاج تصنيع الرقائق المخصصة المبسطة إلى حد كبير:

- تطوير وصف المخطط

- إنشاء الطوبولوجيا

- نقل الملفات التكنولوجية إلى المصنع وانتظار أن تصبح البلورات جاهزة

- قياسات البلورات التي تم الحصول عليها

- غلاف

- للبيع

هناك نقطتان "طويلتان" هنا - تطوير المخطط وتوقع نتائج المصنع. يتم استخدام منهجيات مختلفة لتقليل وقت التطوير ، وفي بيئة الطلاب يكون الحل الأفضل هو العمل الجماعي ، لكننا مهتمون بالنقطة الثانية - ساعات عمل المصنع. نظرًا لحقيقة أن مصنع الإلكترونيات الدقيقة هو إنتاج خامل للغاية ، يجب أن يكون كل شيء وفقًا للخطة. ليس في الوقت المناسب لتاريخ إطلاق الإنتاج؟ المحاولة التالية من خلال الربع. يمكن أن يستمر الإنتاج نفسه ، اعتمادًا على مدى تعقيد المنتج ، حتى ستة أشهر. علاوة على ذلك ، هذه الأشهر الستة هي دورة الإنتاج المعتمدة على الآلات المؤتمتة للغاية ، وليس قلة الموظفين. كيف يمكن تخفيض هذه الشروط؟ من خلال إدخال أساس مشترك معين في جميع المخططات المنتجة ، بحيث تكون مرحلة إدخال الاختلافات سريعة.

هذا الأساس المشترك هو BMK - بلورة ذات ترانزستورات مرتبة مسبقًا ، يتم تحديد الغرض الوظيفي لها بواسطة طبقات المعدن ، والتي تسمح بربط الترانزستورات ببعضها البعض. تشكل هذه الترابط الوظائف الفريدة للكريستال.

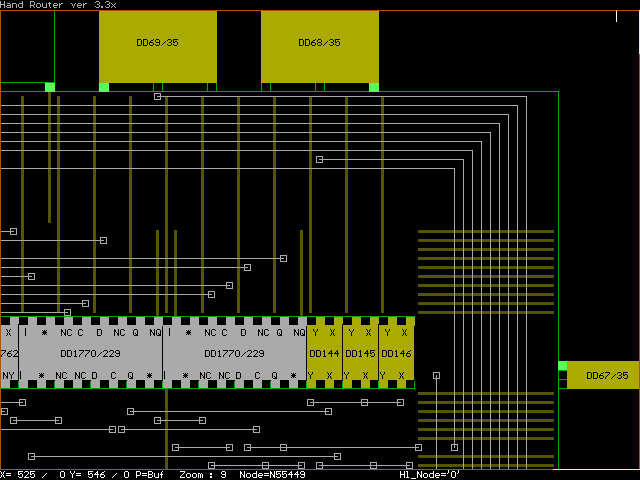

الشكل 2. جهاز التوجيه اليدوي v3.3 ، أصلاً من أحشاء NICEVT ، الذي تم إنشاؤه في الثمانينيات والتسعينيات.

في BMK واحد ، باستخدام مخططات معدنة مختلفة ، من الممكن إنتاج مئات الدوائر الدقيقة المختلفة لمختلف المنظمات. في هذه الحالة ، تصبح BMK نفسها منتجًا للإنتاج الضخم للمصنع ، ويمكن تغيير مراحل التشطيب - طبقات التعدين بسرعة وفقًا لمتطلبات العملاء. وبالتالي ، فإننا نحصل على عمليات إطلاق أكثر تكرارًا للمنتجات الجديدة في الإنتاج وانخفاض الأسعار. بالنسبة لتطوير الطلاب ، فإن هاتين النقطتين مهمتان للغاية.

3. لماذا BMK؟

دعنا نقارن بين فوائد استخدام أساليب التدريب المختلفة ونرى ما يعطي أكبر تأثير بأقل تكلفة.

الجدول 1. مقارنة التأثير التعليمي للتعلم باستخدام طرق مختلفة

ترميز العنوان وإلا فإنه لا يتناسب مع عرض التخطيط.

أ - تطوير موجه FPGA

ب - BMK بدون استخدام FPGA و بإصدار حقيقي

ج - BMK باستخدام FPGA ومع الإصدار الحقيقي

د - أسيك بدون FPGA وبدون إصدار حقيقي

E - ASIC مع FPGA ولا إصدار حقيقي

F - ASIC مع FPGA وإصدار حقيقي

ز- البرنامج التدريبي الحالي في MEPhI ، كف. 27

| مكون الطريق | أ | ب | ج | د | هـ | و | ز |

|---|

| بيان المشكلة | ■ | ■ | ■ | ■ | ■ | ■ | ■ |

| برمجة RTL | ■ | ■ | ■ | ■ | ■ | ■ | ■ |

| برمجة RTL المستندة إلى ASIC | □ | ■ | ■ | ■ | ■ | ■ | □ |

| العمل مع CAD الحديثة | ○ | ■ | ■ | ■ | ■ | ■ | ○ |

| فهم كود FPGA الخاص | ■ | □ | ■ | □ | ■ | ■ | ○ |

| فهم المركب | □ | ■ | ■ | ■ | ■ | ■ | ○ |

| فهم متطلبات التقييد | ○ | ■ | ■ | □ | □ | ■ | □ |

| فهم أهمية التنسيب والتتبع | ○ | ■ | ■ | □ | □ | ■ | □ |

| الاختبار | ■ | ■ | ■ | ■ | ■ | ■ | □ |

| خلق بيئة تحقق | ■ | ■ | ■ | □ | ■ | ■ | □ |

| محاكاة متعددة الزوايا | ■ | ■ | ■ | ■ | ■ | ■ | □ |

| نمذجة الاستخراج | □ | ■ | ■ | ■ | ■ | ■ | □ |

| غلاف | □ | ■ | ■ | □ | □ | ■ | □ |

| الدوائر التناظرية | □ | ■ | ■ | ■ | ■ | ■ | ○ |

| العمل مع تركيبات القياس | □ | ■ | ■ | □ | □ | ■ | ○ |

| العمل في المختبر | ■ | ■ | ■ | □ | □ | ■ | ○ |

| التكلفة | 1 | 2 | 3 | 0 | 1 | 4 | 0 |

■ - موجود في البرنامج ؛

□ - غائب في البرنامج ؛

○ - الخيارات ممكنة.

يتم ملء هذا الجدول فقط من رؤيتي لكيفية تأثير وجود مرحلة معينة في مشروع التخرج الكروي في الفراغ على اجتهاد الطلاب. في الواقع ، يمكن لشخص ما إتقان المسار بأكمله دون مساعدة التدريس ، بينما لا يستطيع شخص ما كتابة معدد إرسال على Verilog. يعكس خط "التكلفة" التموضع في الأعلى ، ولكن ليس بأي حال من الأحوال مضاعفات. أيضا ، "التكلفة" لا تأخذ في الاعتبار التكلفة الفعلية لل CAD ، لعدد من الأسباب المختلفة.

الآن أصبح من الواضح أنه بتكلفة إضافية أقل ، فإن المسار الذي يهدف إلى إطلاق BMK ، باستخدام FPGAs ومع الإصدار الحقيقي يغطي بالضبط نفس مجموعة المهارات اللازمة لإصدار ASIC. أما بقية المسارات ، على الرغم من أنها تغطي نطاقًا عريضًا من المهارات ، إلا أنها في الواقع لا تؤديها بضمير حي من قبل الطلاب بسبب نقص الدافع لتطبيق قدر كبير من الجهد دون أي نتيجة واضحة.

4. مراقبة السوق

حتى الآن ، أصبح تصميم الدوائر المصغرة للمبتدئين مهمة بسيطة إلى حد ما: لقد سمع الجميع عن FPGAs (الدوائر المتكاملة المنطقية القابلة للبرمجة) ، والمزج من التعليمات البرمجية ، وبرامج ترتيب المكونات والتتبع اللاحق للدوائر المصغرة. في الوقت نفسه ، يجد العديد من المطورين المبتدئين صعوبة في تخيل ما هو BMK ، وكيفية العمل معه ، وما المزايا التي يوفرها. لسوء الحظ بالنسبة لمصنعي BMK ، يؤدي هذا الموقف إلى النتائج التالية:

"يوضح تحليل عام 2009 تدفق بعض المستهلكين بسبب توسيع نطاق تطبيق FPGAs المستوردة على أساس التصاريح الصادرة". (ج) التقرير السنوي لشركة Anstrem OJSC لعام 2009.

هناك العديد من مصنعي BMK في سوق الإلكترونيات الدقيقة الحديثة: المحلية والأجنبية. على وجه الخصوص ، في دولة الاتحاد الروسي وبيلاروسيا ، هناك ما لا يقل عن ستة من مصنعي الرقائق الذين يقدمون BMCs الخاصة بهم من أجل التطوير: Angstrem OJSC و IEC NN و Progress NIIMA JSC والمركز العلمي ومركز الإنتاج التكنولوجي و Physics NPO OJSC و Integral Minsk ".

عادة ، يتم استخدام أنظمة CAD المتخصصة لشركات معروفة مثل Cadence أو Synopsis أو Mentor Graphics لتطوير الدوائر المصغرة ، ولكن في حالة BMC ، كل شيء أكثر تعقيدًا إلى حد ما. لا يوفر هذا البرنامج دعمًا رسميًا لـ BMK ، كنوع منفصل من الدوائر المصغرة ، ولكن من الممكن جعله يعمل في الوضع الصحيح باستخدام الحيل المختلفة. في هذه الحالة ، يجب على مطوري BMK تطوير طرق التصميم الفريدة الخاصة بهم ، والتي تستخدم أحيانًا برنامج OpenSource ، على سبيل المثال ، Yosis ، جنبًا إلى جنب مع البرامج المطورة بشكل مستقل.

- في حالة Angstrom OJSC ، من الصعب جدًا العثور على المعلومات الدقيقة و CAD المستخدمة. ومع ذلك ، هناك متطلبات مسبقة للاعتقاد بأن CAD "Nevod" الخاص بهم لم يعد مستخدمًا وتم الانتهاء من الانتقال إلى استخدام منتجات Cadence.

- لا تقدم IEC NN و OJSC NPO Fizika و JSC NIIMA Progress و Integral معلومات عن CAD المستخدم ، ولكن Integral لديها PDK تحت الإيقاع ، لذلك يمكننا أن نستنتج أن بقية المسار موجود أيضًا.

- NPK يستخدم "مركز التكنولوجيا" CAD "Ark" الخاص بهم ، والذي ينفذ مسار التصميم بالكامل تقريبًا. في أي حال ، تمت الموافقة على هذا على موقعة على الإنترنت.

5. كم عدد الصمامات كافية للجميع؟

من الأسباب الشائعة لعدم الرغبة في العمل مع BMK هو عدم اليقين بشأن ما إذا كان المخطط المطور سيتناسب مع BMK وبأي سرعة ستعمل كل هذه. بالطبع ، يكون الأمر جيدًا عندما يكون هناك سلسلة BMK مع مكتبة تصميم واحدة ، ويمكنك التخطي إلى بلورة أكثر قوة أو أسرع إذا لزم الأمر ، ولكن هذا ليس ممكنًا دائمًا. هنا ، على سبيل المثال ، كل شيء واضح حول TSMC: هناك العديد من الشركات التي تعلن صراحة عن سرعة داراتها المنفذة على واحدة أو أخرى من تلك. العملية. ماذا عن BMK لدينا؟ أين يمكنني الحصول على قائمة بالمنتجات التي تم إنشاؤها على أساس BMK ورؤية أدائها؟

بعض الأمثلة:

- رقمي إلى تناظري BMK. حوالي 300 بوابة + 8 ترانزستورات كهربائية. تم تنفيذ مخطط مؤقت لمدة دقيقتين مع مستويين من الحماية. مراقبة الحمل على المرايا الحالية ، ترانزستورات الطاقة للتحكم في الحمل. تقليل استهلاك الطاقة ، العمل مع الكوارتز 32.768 كيلو هرتز ، نطاق جهد الإمداد من 1.8 فولت إلى 9 فولت.

- سعيد الرقمية. BMK المستمر. 100،000 صمام. المنطق العروض الخاصة. الوجهة + NCO (مذبذب متحكم فيه رقميًا). مرحلة البطارية 40 بت ، الجيب - 12 بت. يتحكم تسجيلان في تردد الجيب والتحكم المتوازي والتحكم التسلسلي. الإخراج متوازي.

- رقمي إلى تناظري BMK. حوالي 400 بوابة + DAC من 10 فئات. مولد جيب 7 بت مع الإخراج الحالي.

- BMK الرقمي. من 1500 إلى 3000 صمامات. محطات مختلفة لقناة متعددة الإرسال GOST 26765.52-87.

- BMK الرقمي. حوالي 500 بوابة. مولد من ثماني قنوات للتحكم في اللفات الأولية للمحولات.

- BMK الرقمي. حوالي 3000 بوابة. دائرة الأغلبية للحافلة 8 بت.

لسوء الحظ ، فإن تفاصيل السوق تؤدي إلى حقيقة أن الغالبية العظمى من التطورات في BMK لا تزال غير معروفة لعامة الناس. البيانات العامة لا تعطي فكرة واضحة عن السرعة ، والأرقام الواردة في الكتيبات تبدو غامضة. ومع ذلك ، بالنسبة لمهام التعرف على التكنولوجيا ، لا يتطلب الأمر الكثير ، كما أن الحصول على بعض الخبرة خلفها بالفعل أسهل كثيرًا في إعطاء تقدير تقريبي لمدى تعقيد مخطط معين.

6. عملية التنمية

دعنا ننتقل إلى الأكثر إثارة للاهتمام. لدينا: BMK لـ ~ 3k صمامات (1 صمام = 2 ترانزستورات CMOS) مع بنية القناة ، والأسلاك في طبقة معدنية واحدة وطبقة فرعية من البولي سيلكون ؛ الحماس الموافقة على إدارة المؤسسة للتدريب الذاتي للموظفين.

ولدت فكرة البلورة المستقبلية بدافع الكسل ، وبالتحديد من قراءة منتدى واحد ، حيث كان هناك ، على وجه الخصوص ، محادثة حول الحلول المدمجة للدائرة لحساب رموز الجيب. بدا لي هذا الموضوع مثيرًا للاهتمام ، وقررت أن أرى ما يمكن فعله في هذا الاتجاه.

الآن دعونا نرى ما تم فعله ، وما لم يكن ، وما هي الأخطاء وما هي الاستنتاجات التي تم التوصل إليها.

6.1 التصميم

أظهرت الدراسات السطحية أن هناك خوارزمية لحساب قيم الجيب ، والتي تتطلب من العمليات الحسابية فقط الجمع والطرح والتحول إلى اليمين. اتضح أن هذه ليست مجرد خوارزمية ، ولكن عائلة بأكملها تسمى CORDIC (تنسيق الإحداثيات الرقمية للتدوير). يمكن لأولئك المهتمين بتفاصيل تشغيل الخوارزمية الرجوع إلى قائمة المراجع في نهاية المقالة ، لكنني سأوضح فقط أنه باستخدام هذه الخوارزمية ، لا يمكن حساب الجيب فقط ، ولكن أيضًا جيب التمام ، قوس الظل ، ضرب وقسمة الحجج ، وحساب بعض الوظائف الزائدية.

بعد دراسة العديد من المنشورات حول هذه الخوارزمية ، وتنظيم هذه المعرفة في رأسي ، اكتشفت أنه يمكنك محاولة تنفيذ هذه الخوارزمية على BMK بسعة حوالي 3 صمامات.

فماذا ينتهي بنا في هندسة الدوائر؟

- توسيع خوارزمية CORDIC خط الأنابيب لحساب الجيب.

- 4 بتات إضافية في ناقل البيانات الداخلي للتعويض عن أخطاء التقريب.

- مجمِّع تراكمي 11 بت لقيمة الطور.

- يتم تعيين زيادة الطور بواسطة الناقل المتوازي.

- نسق بيانات الإخراج: 7 بت + تسجيل ، ناقل متوازي.

يبدو أن كل شيء على ما يرام ، ولكن ماذا يحدث إذا لم تعوض عن أخطاء التقريب؟ وإليك ما (مقارنة الحافلة الداخلية 11 بت و 8 بت):

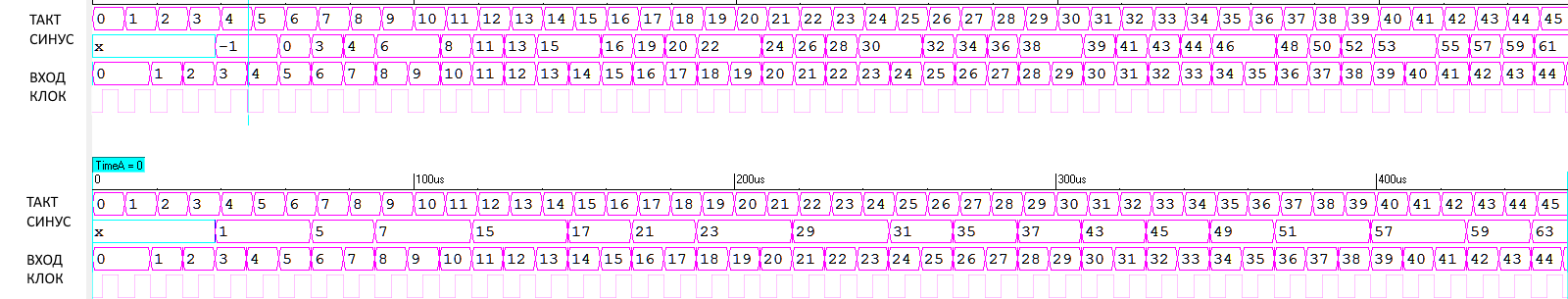

الشكل 3. مقارنة إخراج خوارزمية CORDIC عند استخدام الحافلات الداخلية من 11 بت و 8 بت ، على التوالي.

إذا انتبهت إلى الأسطر الثانية من البيانات ، يمكنك أن ترى أن أخطاء التقريب يمكن أن تقلل بشكل فعال من جودة حساباتك.

إذا قمنا في المستقبل بإرفاق هذه الشريحة بـ 7 بت DAC ، نحصل على مولد جيب مناسب تمامًا (DDS ، في رأينا - التوليف الرقمي المباشر). في هذه الحالة ، سيكون لدينا الفرصة لتعديل تردد الجيب ، ولكن لن تكون هناك إمكانية لتعديل المرحلة.

بشكل عام ، يختلف مسار العمل مع BMCs الصغيرة إلى حد ما عن مسار التصميم الحالي. إذا فكرت في الأمر ، تصبح الاختلافات واضحة: مع مثل هذا الحجم الصغير للصمام ، من الضروري استخدام كل صمام بكفاءة عالية ، والنموذج الرئيسي للتصميم الحديث ليس على الإطلاق. وتقول إنه يجب أن يكون المنتج في كل مرحلة متوافقًا هندسيًا مع الأنظمة الحديثة للاختبار الآلي والتحقق والقياس. في هذه الحالة ، تبقى مسألة كفاءة الصمام خارج الأقواس ، حيث أن النفقات العامة اللازمة. في الواقع ، في سنوات التطور الديناميكي لتقنيات الإنتاج ، كان التفكير في الكفاءة غير ضروري. لذلك عندما (وإذا) ما زلنا نصل إلى الحد المادي ونتوقف عند زيادة كثافة الترانزستورات على البلورة ، فإن مشاكل كفاءة استخدام المنطقة ستصل إلينا في النمو الكامل. حسنًا ، مع BMKs الصغيرة ، فإنها تقف بالفعل على ارتفاع كامل ، وبالتالي الاستنتاج: في BMK للدبابات الصغيرة يمكنك ويجب عليك استخدام تصميمات معقدة باستخدام مخططات إنشاء كتل صعبة مختلفة ، ومزاليج مختلفة ، وردود فعل وأشياء أخرى ، لاستخدامها في الطريق الحديث المهندس الكبير كان سيمزق يديه.

المشكلة الرئيسية في استخدام مثل هذه الأشياء هي أنه لاستخدامها ، يجب على المهندس أن يكون على دراية واضحة بما يفعله ولماذا. ومع ذلك ، إذا كان هناك فهم ، يمكن أن يكون الربح رائعًا. إذا لم يكن هناك فهم ... حسنًا ، يمكنك التصوير في الساق بملايين الطرق الفعالة المختلفة.

كيف كان مسار التصميم في حالتي:

- التخطيط اليدوي كمخطط لعناصر المكتبة

- تقدير حجم الدائرة الناتجة

- معالجة الدائرة حتى يتجاوز حجم الدائرة 80٪ من سعة BMK

- وهذا يشمل أيضًا العمل على إنشاء عناصر مكتبة جديدة واختبارها ودمجها في مسار التصميم

- وضع اختبارات للدائرة

- تتبع الدائرة اليدوي

قد يعترض المصممون ذوو الخبرة على الفور على أنه قد تم تفويت العديد من الخطوات المهمة ، لكنني نسيت حقًا أن أذكر أي شيء.

يوضح التصميم اليدوي جيدًا مدى أهمية مكتبة مكونات الجودة. لم تتناسب المتغيرات الأولى للدائرة في البلورة ببساطة من خلال حجم المنطق ، ولكن في حالة قناة BMC - قناة حيث تمر الأسلاك عبر القنوات الموضوعة بين "صفوف" الترانزستورات - يتم شغل حوالي 30 ٪ من حجم الدائرة بواسطة التوصيلات البينية. لذلك ، كان عليّ توسيع المكتبة إلى حد ما ، بناءً على الهيكل الذي تم الحصول عليه في هذا المشروع بالذات. سمح هذا النهج بحفظ عدد كبير من البوابات وحتى أكثر أو أقل بحرية وضع جميع الطرق.

حشوة الكريستال النهائية هي 72 ٪ ، وذهب ثلث آخر من البلورة إلى الأسلاك. ثم تم نقل الملفات إلى المصنع ، وعادت إلى مشروعات عملي الحالية.

باستخدام طريقة التصميم "اليدوي" ، يجب تذكر النقاط التالية:

- لا يمكنك استخدام عناصر المكتبة بدون تفكير بناءً على وظيفتها. من الضروري دراسة ما يتكون هذا العنصر على مستوى الترانزستور ، سواء كان رقميًا أو تمثيليًا. ما هي قدراته الحاملة من حيث المدخلات والمخرجات ، سواء كان منطق CMOS محض ، أو TG ، أو أي شيء آخر.

- من الضروري مراعاة وتنسيق قوة العناصر وحملها.

- إذا كان لديك مشغل متزامن ، فأنت بحاجة إلى تسجيله بإشارات ذات قوة متساوية.

- إذا كنت تستخدم نوعًا من الإشارة بدون تضخيم متوسط ، وتم تحميلها على العديد من المستهلكين ، فقد تفشل الإشارة كثيرًا. قد يكون هذا ضئيلاً في الظروف العادية ، ولكنه مهم عند اختبار WWF (العوامل الخارجية).

لا يوجد نظام تصميم يمكن أن يحل محل عقلك. بشكل عام ، لا يمكنك تشغيل محاكاة إذا كنت لا تفهم كيف تعمل الدائرة.

6.2 القياسات

قياساتها مرحلة مهمة للغاية في العمل مع الكريستال. يمكن تمييز ثلاثة أنواع من القياسات: التكنولوجية والوظيفية والكهربائية. أولها تحقق من أن المصنع لم يتم سحبه وأن البلورة مصنعة بشكل صحيح من الناحية التكنولوجية. تتحقق الأخيرة من أن النظرية (أي النمذجة) تتلاقى مع الممارسة (الكريستال الحقيقي). , : , , . , , . , - . , . — , — . , … , , . .

, . , Fairchild 80- USB, . FORMULA "", . HP - Unix' . National Instruments , , , (). Agilent, . , ?) .

, -, , . , , , , Fairchild, , NI. , . - , , .

, , :

- , .

- . , .

- "" .

- , , , .

- .

- :

- /, , . /.

- , .

- , – . .

- , «» , .

- , .

, , .

. 4 (!) . , , . , ?) " ".

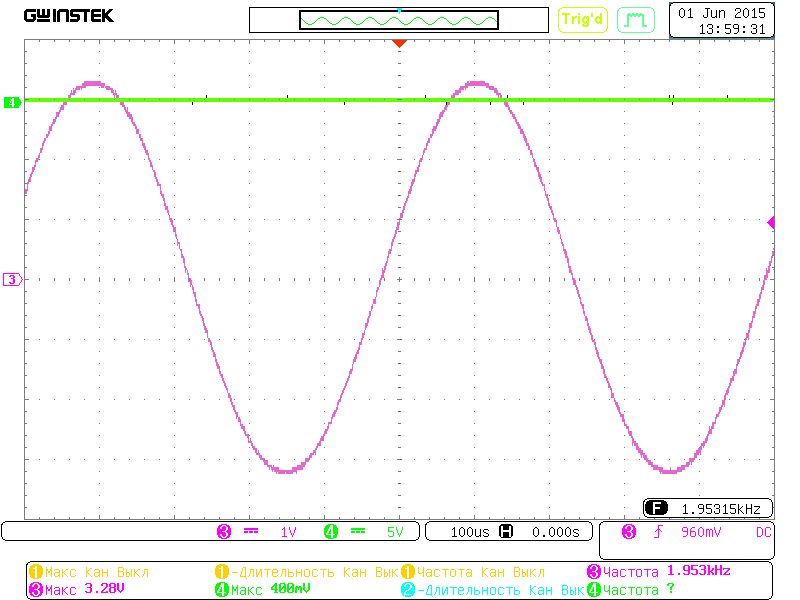

4. .

, . , , . 80 , , , , 8- .

, . :

5.

6.

, , .

, — . , . 8- . .

6.3

?

- ;

- NCO(numerically controlles oscillator);

- , , NCO ROM(cROM);

- ;

- :

- , ;

- ;

7. , HRT.

:

- — 83%.

- 14

- 11

- (sin & cos, 12 )

- 16

, , ? , . , - .

, . , . , — . .

7. ?

.

.

30 000 100 2. , " " . , , Setup&Hold, , Verilog' , , , — , , . , — , , , … . — , .

. .

-

MIT Massachusetts Institute of Technology

UZH Universität Zürich

ASIC Application specific integrated circuit

-- []

CORDIC Coordinate Rotation Digital Computer

-

NCO Numerically controlled oscillator

ROM Read-only memory

cROM Compressed ROM

- CORDIC IP Block Design, Vitaliy Kuhar, Stockholm, Sweden 2008

- CORDIC. , . . , . .

- Comparison of parallel and pipelined CORDIC algorithm using RCA and CSA, Guerrero, Meloni

- CORDIC for dummies.pdf

- Sine/Cosine using CORDIC Algorithm, Prof. Kris Gaj

- Lecture_cordic.pdf