مرحبًا

تستعرض المقالة بنية نظام الذاكرة الظاهرية ARMv7.

عنوان المفسدلا يتم النظر في التفاصيل الدقيقة للتخزين المؤقت و DMA و LPAE وما شابه ذلك هنا. للحصول على وصف أكثر تفصيلاً ، ارجع إلى الأدبيات الموجودة في نهاية المقالة.

مقدمة

يقوم نظام الذاكرة الظاهرية بالعديد من المهام. أولاً ، يسمح لك بوضع عمليات المستخدم في مساحات ذاكرة منفصلة ومعزولة عن بعضها البعض. هذا يسمح لك بزيادة موثوقية النظام ، ولا تؤثر أخطاء عملية واحدة على تشغيل العمليات الأخرى. ثانيًا ، يمكن لنظام التشغيل تزويد العملية بذاكرة أكبر من ذاكرة النظام. يتم دفع الصفحات غير المستخدمة من الذاكرة إلى التخزين الدائم ، ويتم تحميل الصفحات الضرورية من هناك ، مما يشكل وهمًا بحجم أكبر من الذاكرة مما هو عليه بالفعل. ثالثًا ، تسهل المساحة الافتراضية المستمرة كتابة برامج مخصصة. يتم تنفيذ جميع العمليات في نفس المساحة ، ويخفي نظام التشغيل منها تكوين الذاكرة الحقيقية في النظام.

التعاريف

يتم استخدام التعريفات التالية في المقالة:

العنوان الافتراضي - العنوان الذي يستخدمه قلب المعالج. يستخدم مؤشر المكدس وعداد التعليمات وسجل الإرجاع عنوانًا افتراضيًا.

العنوان الفعلي - عنوان الإخراج على ناقل المعالج.

الصفحة هي وحدة معالجة الذاكرة الظاهرية.

مقطع - تناظري للصفحة ، حجم أكبر.

الإطار هو وحدة معالجة الذاكرة الفعلية.

جدول الصفحة - مجموعة من السجلات لترجمة العناوين.

ASID هو معرف مساحة العنوان.

TLB - المخزن المؤقت للترجمة السريعة للعناوين.

MMU هي وحدة إدارة الذاكرة.

TLB

TLB هو مخزن مؤقت للأجهزة سريع جدًا يحتوي على نتائج ترجمات العناوين الأخيرة. يصل طلب kernel لترجمة عنوان الصفحة ويصل ASID الحالي إلى TLB. إذا كان هناك إدخال صالح هناك ، يتم التحقق من أذونات الوصول إلى هذه الذاكرة ، ويتم إرجاع طريقة الوصول وعنوان الإطار المقابل إلى MMU. إذا تم رفض الوصول إلى الذاكرة ، يتم طرح استثناء الأجهزة. إذا حدث خطأ TLB (لم يتم العثور على سجل) ، فسيكون السلوك الإضافي حساسًا لحالة الأحرف بواسطة TTBCR. يمكن إجراء بحث في جداول الصفحات أو يتم طرح استثناء.

من المهم ملاحظة أنه عند معالجة جداول الصفحات ، يجب عليك إعادة تعيين TLB بشكل صحيح ، لأنه قد يتم تخزين المعلومات غير ذات الصلة هناك.

تحديث الإدخالات في TLB شفاف لمبرمج robin robin.

من الممكن أيضًا تحميل وتأمين بعض الإدخالات في TLB لمنع ازدحامها.

الشكل 1. TLB

الشكل 1. TLBجداول الصفحات

ARMv7 عبارة عن بنية 32 بت ، لذا لدينا 4 جيجابايت من الذاكرة الافتراضية القابلة للعنونة.

تنقسم جداول الصفحات إلى مستويين - L1 و L2.

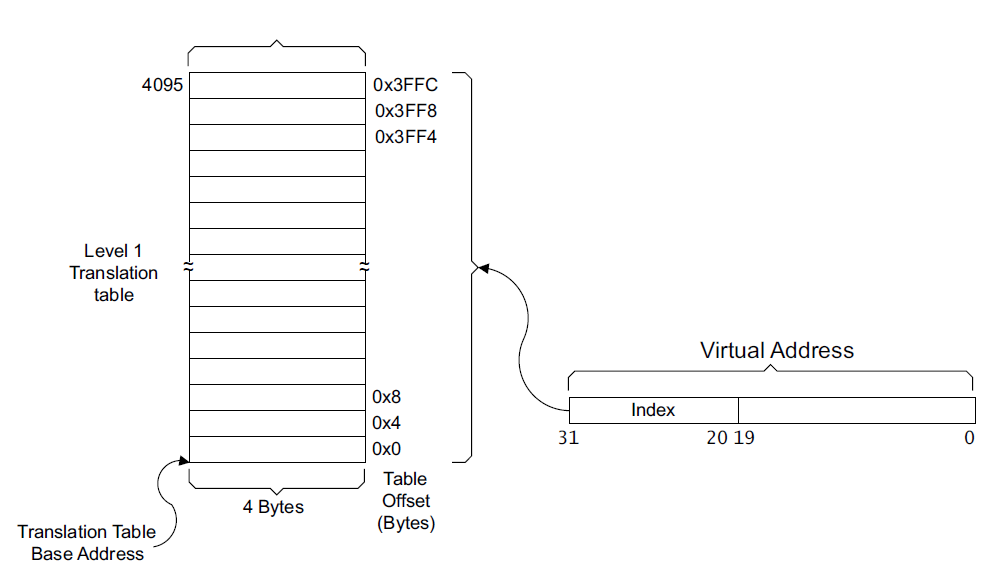

يصف الجدول L1 مساحة 4 غيغابايت لجميع العناوين. يتكون من 4096 تسجيل 32 بت ، كل منها يصف 1 ميجا بايت. يتم تحديد الإدخالات في الجدول من خلال 12 بت عالية من العنوان الظاهري.

التين. 2 ابحث عن الإدخالات في الجدول L1

التين. 2 ابحث عن الإدخالات في الجدول L1يقع الجدول L1 في الذاكرة الفعلية ومحاذاة إلى حد 16 كيلو بايت. هناك 4 خيارات لهذه الإدخالات: لوصف الصفحات والأقسام والأقسام الفوقية. حسنًا ، سجل فارغ للذاكرة التي لم يتم تعيينها بعد.

التين. 3 أنواع الإدخالات في L1

التين. 3 أنواع الإدخالات في L1تشير البتتان 0 و 1 إلى نوع السجل 00b-Fault ، و 01 b هو واصف الصفحة ، و 10 b هو واصف القسم (والتقاطع).

إذا كانت الذاكرة الفعلية مقسمة إلى صفحات ، فإن الجدول L1 يخزن عنوان الجدول L2 (فعلي ، محاذاة إلى 1 كيلو بايت). يتم تحديد البت 9 من قبل الشركة المصنعة (التنفيذ محدد) ، البتات [8: 5] - لآلية المجال (موقوفة في ARMv7) ، SBZ - الأصفار.

إذا قررنا تقسيم الذاكرة إلى أقسام ، فمن الضروري كتابة العنوان الفعلي المقابل في L1. يشير القسم مباشرة إلى منطقة الذاكرة الفعلية المحاذية 1 ميجا بايت. لا حاجة للجدول L2. يعتبر Supersection حالة خاصة من التقسيم ، ويجب تكرار الإدخال في جدول L1 16 مرة ، كما أن محاذاة الكتل المخصصة للذاكرة الفعلية والظاهرية هي 16 ميغابايت أيضًا.

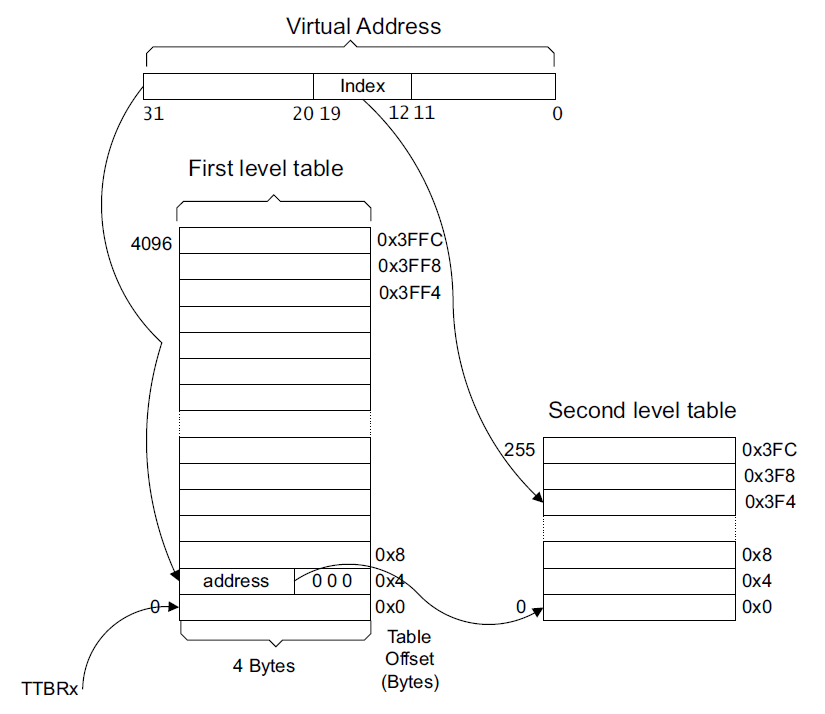

يتكون الجدول L2 من 256 إدخالاً من 32 بتة. يجب محاذاة 1 كيلو بايت.

التين. 4 ابحث عن الإدخالات في الجدول L2

التين. 4 ابحث عن الإدخالات في الجدول L2تتكون الفهارس في الجدول L2 من متوسط 8 بت [19:12] من العنوان الافتراضي. يحتوي كل إدخال جدول على عنوان الإطار.

التين. 5 أنواع الإدخالات في L2

التين. 5 أنواع الإدخالات في L2يمكن أن تكون الصفحات بحجمين: 64 كيلوبايت (صفحة كبيرة) و 4 كيلوبايت (صفحة صغيرة).

تقوم بتات AP و APX بتعيين أذونات القراءة / الكتابة في الوضع المميز / غير المميز (kernel / user). تعد وحدات البت TEX و C و B و S مسؤولة عن نوع الذاكرة والتخزين المؤقت والتخزين المؤقت للقراءة والكتابة. يسمح بت nG - nonGlobal بالوصول إلى الصفحة لجميع العمليات أو لمعرف ASID واحد فقط.

يقلل استخدام الصفحات الكبيرة من عدد الإدخالات في TLB. بدلاً من 16 إدخالًا (4Kb * 16 = 64 كيلوبايت) ، سيتم تخزين واحد فقط هناك. ومع ذلك ، يجب إدخال 16 إدخالاً متطابقاً في الجدول L2.

تسمح القدرة على معالجة أحجام مختلفة من الكتل ، من ناحية ، بتخصيص الذاكرة مع الدقة المطلوبة ، من ناحية أخرى ، لتقليل عدد المكالمات لجداول الصفحات في ذاكرة بطيئة نسبيًا.

يسجل

للتحكم في النظام (بما في ذلك MMU) في بنية ARM ، تم تصميم معالج مشترك CP15 خاص. لإدارة الذاكرة هناك واحد ونصف من تسجيلاتها. نحن مهتمون بالعديد منها - Control ، TTBR0 / 1 ، TTBCR ، ContextID.

في سجل التحكم ، يكون البت الأقل أهمية مسؤولاً عن تشغيل / إيقاف تشغيل وحدة المعالجة المركزية ، كل شيء بسيط.

يحتوي زوج السجلات TTBR0 / 1 على العناوين الفعلية لجداول المستوى الأول. في هذه العناوين ، تبدأ MMU في البحث عن الصفحة المطلوبة.

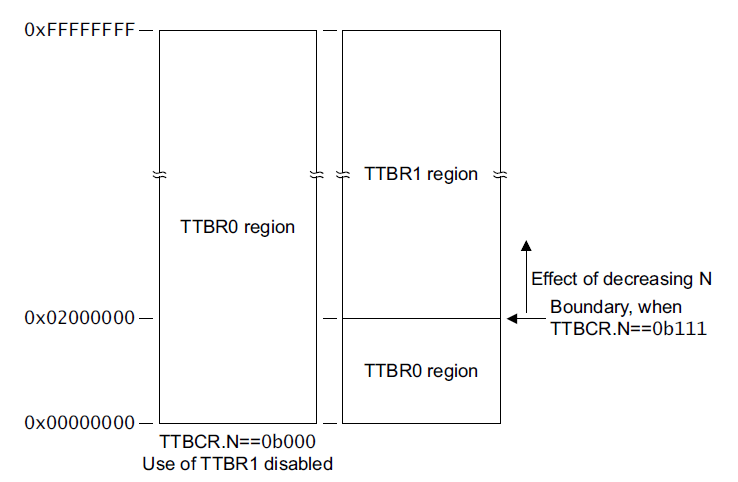

يسمح لك سجل TTBCR بتقسيم مساحة العنوان بالكامل إلى قسمين بين TTBR0 و TTBR1. كل واحد منهم سيبث الجزء الخاص به من العناوين. يتم استخدام وحدات البت [2: 0] لتعيين الحجم. الرقم المسجل (من 0 إلى 7 عشري) يخفي الجزء القديم من العناوين الافتراضية. إذا كانت قيمته "0" ، يتم بث جميع العناوين عبر TTBR0. إذا كانت "1" ، يتم إخفاء عناوين 31 بت ويمر 2 غيغابايت أقل من المساحة الافتراضية عبر TTBR0 ، والأعلى من خلال TTBR1. "2" - 31 و 30 بت مقنعة ويتم الحصول على التقسيم إلى 1 جيجابايت و 3 جيجابايت ، على التوالي. وبالتالي ، يمكن استخدام الجزء السفلي من العناوين لتطبيقات المستخدم ، مما يؤدي إلى زيادة التحميل على سجل TTBR0 لعملية جديدة ، ويمكن ترك الجزء العلوي لاحتياجات النظام.

التين. 6 تقسيم مساحة العنوان

التين. 6 تقسيم مساحة العنوانالبتات [5: 4] مسؤولة عن سلوك TLB المفقود - ابحث في جداول الصفحات أو استثناء.

يحتوي سجل ContextID على حقل ASID للعملية الحالية. يجب تغييره مع محتويات السجل TTBR0 عند تغيير السياق.

ترجمة العنوان

خوارزمية تحويل العناوين الافتراضية إلى العنوان الفعلي كما يلي:

- ابحث عن العنوان الظاهري المطلوب و ASID في المخزن المؤقت TLB

- إذا لم يكن TLB يحتوي على العنوان المطلوب ، فسيتم إجراء بحث عن الأجهزة في جداول الصفحات

إذا طلبت النواة سابقًا صفحة افتراضية ، فسيتم تخزينها في TLB. في هذه الحالة ، تقوم وحدة المعالجة المركزية (MMU) بإخراجها من ذاكرة التخزين المؤقت ولا يلزم القيام بأي شيء. إذا كانت الصفحة مطلوبة لأول مرة (أو تم إخراجها من هناك - TLB ليست كبيرة جدًا) ، فسيتم إجراء البحث في الجداول L1-L2. وبالتالي ، فإن تعيين العناوين الافتراضية والمادية هو كما يلي:

- في السجل TTBR0 \ TTBR1 ، يتم البحث في عنوان الجدول L1.

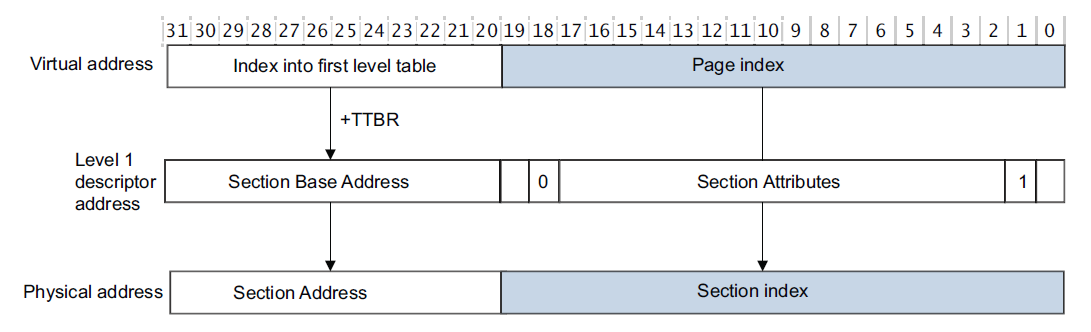

- أعلى 10 بتات من العنوان الظاهري تشكل فهرسًا في الجدول.

- أ) إذا كان السجل يتوافق مع القسم (الاستبدال) ، فسيتم التحقق من سمات القسم ، وإذا كان كل شيء على ما يرام ، فإن العنوان المادي الناتج يتكون من العنوان الأساسي للقسم (التقاطع) والعشرون (24) بت الأقل من العنوان الظاهري.

عنوان المفسد التين. 7 ترجمة العنوان في الاستبدال

التين. 7 ترجمة العنوان في الاستبدال

ب) إذا كان السجل جدول L2 ، فسيستمر البحث فيه. يشكل الجزء الأوسط من العنوان الظاهري للصفحة فهرس الجدول.

عنوان المفسد التين. 8 ترجمة العنوان في الجدول L2

التين. 8 ترجمة العنوان في الجدول L2

- تحديث TLB قيد التقدم

في المجموع ، يتكون النظام الفرعي للذاكرة الافتراضية من الأجزاء التالية:

- سجلات التحكم CP15 المتعددة

- جداول الصفحات التي تحتوي على قواعد ترجمة العنوان

- TLB - ذاكرة التخزين المؤقت لعمليات البث الناجحة

- MMU هي وحدة ترجمة العنوان.

الأدب

ARMv7-A و ARMv7-R كتيب مرجع العمارة ARM

ARM Cortex-A Series Programmer's Guide