تقنيات الإلكترونيات الدقيقة الحديثة - مثل "عشرة هنود صغار". تكلفة التطوير والمعدات كبيرة جدًا بحيث أنه مع كل خطوة جديدة إلى الأمام ، يسقط شخص ما. بعد الأخبار حول رفض GlobalFoundries تطوير 7 نانومتر ، بقي ثلاثة منهم: TSMC و Intel و Samsung. وما هي بالضبط "معايير التصميم" وأين هذا الحجم الذي نعتز به للغاية هو 7 نانومتر؟ وهل هناك على الإطلاق؟

الشكل 1. الترانزستور فيرتشايلد FI-100 ، 1964.دخلت أول ترانزستورات MOS التسلسلية إلى السوق في عام 1964 ، وكما يمكن للقراء المحنكين أن يروا من الرسم ، لم

يكنوا مختلفين

تقريبًا عن أكثر أو أقل حديثًا - باستثناء الحجم (انظر إلى السلك للحصول على المقياس).

لماذا تقلل حجم الترانزستورات؟ الإجابة الأكثر وضوحًا على هذا السؤال تسمى قانون مور ، وتنص على أنه يجب مضاعفة عدد الترانزستورات على الشريحة كل عامين ، مما يعني أن الأبعاد الخطية للترانزستورات يجب أن تنخفض بمعامل اثنين. "يجب" - وفقًا لملاحظات جوردون مور (وبعض المهندسين الآخرين) في السبعينيات. من قانون مور ، هناك العديد من العوامل الأخرى التي تشكل خارطة طريق ITRS للإلكترونيات الدقيقة. إن أبسط وأقسى صياغة طرق تنفيذ قانون مور (المعروف أيضًا باسم قانون التصغير في Dennard) هو أن الزيادة في عدد الترانزستورات على الشريحة يجب ألا تؤدي إلى زيادة في كثافة استهلاك الطاقة ، أي مع انخفاض حجم الترانزستورات ، يجب تقليل جهد الإمداد والتيار التشغيلي نسبيًا.

يتناسب التيار من خلال ترانزستور MOS مع نسبة عرضه إلى طوله ، مما يعني أنه يمكننا الحفاظ على نفس التيار ، مما يقلل بشكل نسبي كل من هذه المعلمات. علاوة على ذلك ، بتقليل حجم الترانزستور ، نقوم أيضًا بتقليل سعة البوابة (بما يتناسب مع منتج طول وعرض القناة) ، مما يجعل الدائرة أسرع. بشكل عام ، في الدائرة الرقمية لا يوجد أي سبب تقريبًا لجعل الترانزستورات أكبر من الحد الأدنى للحجم. بعد ذلك ، تبدأ الفروق الدقيقة في الترانزستورات المنفصلة لقناة p المنطقية عادة ما تكون أوسع قليلاً من تلك الخاصة بالقناة n من أجل التعويض عن الاختلاف في حركة حاملات الشحن ، وفي الذاكرة ، على العكس من ذلك ، تكون الترانزستورات n-channel أوسع بحيث يمكن كتابة الذاكرة بشكل طبيعي من خلال مفتاح غير مكتمل ، ولكنها في الحقيقة الفروق الدقيقة ، وعلى مستوى العالم - كلما كان حجم الترانزستور أصغر - كلما كان ذلك أفضل للدوائر الرقمية.

هذا هو السبب في أن طول القناة كان دائمًا أصغر حجم في طوبولوجيا الدائرة المصغرة ، والتسمية الأكثر منطقية.

وتجدر الإشارة هنا إلى أن المنطق أعلاه حول الحجم غير صالح للدوائر التناظرية. على سبيل المثال ، يوجد الآن على الشاشة الثانية لجهاز الكمبيوتر الخاص بي زوج متطابق من الترانزستورات يستخدم تقنية 150 نانومتر ، 32 قطعة لكل منها 8/1 ميكرون. يتم ذلك من أجل ضمان هوية هذين الترانزستور ، على الرغم من الاختلاف التكنولوجي للمعلمات. المنطقة ذات أهمية ثانوية.يمتلك التقنيون والطبوغرافيون ما يسمى بنظام لامدا بأحجام الطوبولوجيا النموذجية. إنه مريح للغاية لدراسة التصميم (وتم اختراعه في جامعة بيركلي ، إذا لم أكن مخطئًا) ونقل التصاميم من مصنع إلى آخر. في الواقع ، هذا تعميم للأحجام النموذجية والقيود التكنولوجية ، ولكنه خشن قليلاً ، بحيث يعمل بالضبط في أي مصنع. في مثالها ، من الملائم النظر إلى الأحجام النموذجية للعناصر في الشريحة. المبادئ الأساسية لنظام لامدا بسيطة للغاية:

- إذا كان تحول العناصر على اثنين من أقنعة الليثوغرافيا الضوئية المختلفة له عواقب كارثية (على سبيل المثال ، دائرة كهربائية قصيرة) ، فيجب أن يكون هامش الأحجام لمنع التناقضات على الأقل لامدا اثنين ؛

- إذا كان تحول العناصر له نتائج غير مرغوب فيها ، ولكن ليس لها نتائج كارثية ، فيجب أن يكون هامش الحجم لامدا واحدًا على الأقل ؛

- الحجم الأدنى المسموح به لنوافذ قناع الصور هو لامدا.

يتبع من الفقرة الثالثة ، على وجه الخصوص ، أن لامدا في التقنيات القديمة هو نصف معيار التصميم (بتعبير أدق ، طول قناة الترانزستور ومعايير التصميم هما لامدا).

الشكل 2. مثال على الطوبولوجيا التي يقوم بها نظام لامدا.عمل نظام لامدا بشكل مثالي على معايير التصميم القديمة ، مما يسمح لك بنقل الإنتاج بسهولة من مصنع إلى مصنع ، وتنظيم موردي الرقائق الثانية والقيام بأشياء أكثر فائدة. ولكن مع تزايد المنافسة وعدد الترانزستورات على الشريحة ، بدأت المصانع تسعى جاهدة لجعل الهيكل أصغر قليلاً ، لذلك لا يمكنك الآن تلبية قواعد التصميم التي تتوافق مع نظام لامدا "النظيف" ، إلا في المواقف التي يقوم المطورين بتخريبها بشكل مستقل ، مع الأخذ في الاعتبار احتمال الإنتاج رقاقة في مصانع مختلفة. ومع ذلك ، على مر السنين ، طورت الصناعة اتصالًا مباشرًا "معايير التصميم = طول قناة الترانزستور" ، والتي كانت موجودة بنجاح حتى وصلت الترانزستورات إلى عشرات النانومترات.

الشكل 3. الشكل 3. القسم التخطيطي للترانزستور.يوضح هذا الشكل مقطعًا مبسطًا للغاية من ترانزستور مستوٍ تقليدي (مسطح) ، يوضح الفرق بين طول القناة الطوبولوجية (Ldrawn) وطول القناة الفعال (Leff). من أين يأتي الفرق؟

بالحديث عن التكنولوجيا الإلكترونية الدقيقة ، غالبًا ما يتم ذكر الطباعة الحجرية الضوئية ، ولكن في كثير من الأحيان تكون عمليات أخرى أخرى ، لا تقل أهمية عن العمليات التكنولوجية: النقش ، زرع الأيونات ، الانتشار ، إلخ. الخ. بالنسبة لمحادثاتنا معك ، فإن التذكير بكيفية عمل الانتشار وزراعة الأيونات ليس ضروريًا.

الرقم 4 الشكل 4. مقارنة نشر وزراعة أيون.مع الانتشار ، كل شيء بسيط. تأخذ رقاقة السيليكون التي يتم تطبيق الرسم عليها مسبقًا (بمساعدة الطباعة الحجرية الضوئية) ، وتغطي بأكسيد السيليكون تلك الأماكن التي لا تكون هناك حاجة للشوائب ، وفتح تلك حيث تكون هناك حاجة إليها. بعد ذلك ، تحتاج إلى وضع الشوائب الغازية في نفس الغرفة مع الكريستال والحرارة إلى درجة حرارة يبدأ فيها الشوائب في اختراق السيليكون. من خلال تعديل درجة حرارة ومدة العملية ، من الممكن تحقيق الكمية وعمق الشوائب المطلوبين.

والناقص الواضح للانتشار هو أن الشوائب تخترق السليكون في جميع الاتجاهات بنفس الطريقة ، إلى أسفل ، هذا الجانب ، وبالتالي تقليل طول القناة الفعالة. ونحن نتحدث الآن عن مئات النانومتر! في حين تم قياس معايير التصميم بعشرات الميكرون ، كان كل شيء على ما يرام ، ولكن بالطبع ، لا يمكن أن تستمر هذه الحالة لفترة طويلة ، وتم استبدال الانتشار بزراعة أيون.

أثناء عملية زرع الأيونات ، تتسارع حزمة أيون الشوائب ويتم توجيهها إلى رقاقة السيليكون. في هذه الحالة ، تتحرك جميع الأيونات في اتجاه واحد ، مما يلغي عمليا انتشارها إلى الجانبين. من الناحية النظرية بالطبع. من الناحية العملية ، انتشرت الأيونات مع ذلك قليلاً ، وإن كان ذلك على مسافات أقصر بكثير من أثناء الانتشار.

ومع ذلك ، إذا عدنا إلى نمط الترانزستور ، فسوف نرى أن الفرق بين طول الطوبولوجيا وطول القناة الفعالة يبدأ بالضبط بسبب هذا الزحف الصغير. من حيث المبدأ ، يمكن تجاهلها ، لكنها ليست السبب الوحيد للاختلاف. لا تزال هناك تأثيرات قناة قصيرة. هناك خمسة منهم ، وبطرق مختلفة يغيرون معلمات الترانزستور إذا اقترب طول القناة من قيود مادية مختلفة. لن أصفهم جميعًا ، وسوف أتطرق إلى أكثرها صلة بنا - DIBL (تخفيض الحاجز الناجم عن التصريف ، انخفاض الناجم عن الحاجز المحتمل).

من أجل الوصول إلى الحوض ، يجب أن يتغلب الإلكترون (أو الثقب) على الحاجز المحتمل لتقاطع الحوض pn. يقلل جهد البوابة من هذا الحاجز ، وبالتالي التحكم في التيار من خلال الترانزستور ، ونريد أن يكون جهد البوابة هو جهد التحكم الوحيد. لسوء الحظ ، إذا كانت قناة الترانزستور قصيرة جدًا ، فإن تقاطع الصرف pn يبدأ في التأثير على الترانزستور ، مما يقلل أولاً من جهد المسام (انظر الشكل أدناه) ، وثانيًا ، يبدأ الجهد عبر الترانزستور في التأثير ليس فقط على جهد البوابة ، ولكن أيضًا عند التصريف ، لأن سمك تقاطع التصريف يزيد بالتناسب مع الجهد عند التصريف ، وبالتالي يقصر القناة.

الشكل 5 الشكل 5. تأثير تخفيض الحاجز الناجم عن الصرف (DIBL).

المصدر - ويكيبيديا.بالإضافة إلى ذلك ، يؤدي انخفاض طول القناة إلى حقيقة أن حاملات الشحن تبدأ بالانتقال بحرية من المصدر إلى المصرف ، وتجاوز القناة وتشكيل تيار تسرب (تيار سيئ في الشكل أدناه) ، وهو أيضًا استهلاك ثابت للطاقة ، والذي كان غيابه أحد الأسباب المهمة للنجاح المبكر لـ CMOS -التقنيات المثبطة مقارنة بالمنافسين القطبين في ذلك الوقت. في الواقع ، يحتوي كل ترانزستور في التكنولوجيا الحديثة على مقاوم موازٍ له ، قيمته أصغر ، وكلما كان طول القناة أصغر.

الشكل 6. الزيادة في الاستهلاك الثابت بسبب التسربات في تقنيات القنوات القصيرة.

المصدر - ملخصات.الشكل 7. نسبة استهلاك الطاقة الثابتة من المعالجات الدقيقة في معايير التصميم المختلفة.

المصدر - B. Dieny et. al.، "تأثير النقل الدوراني واستخدامه في مكونات Spintronic" ، المجلة الدولية لتقنية النانو ، 2010الآن ، كما ترون في الشكل أعلاه ، يتجاوز الاستهلاك الثابت الديناميكي بشكل كبير ويمثل عقبة مهمة أمام إنشاء دوائر منخفضة الطاقة ، على سبيل المثال ، للإلكترونيات القابلة للارتداء وإنترنت الأشياء. في الواقع ، في الوقت الذي أصبحت فيه هذه المشكلة مهمة ، بدأ تسويق موهليز بمعايير التصميم ، لأن التقدم في الطباعة الحجرية بدأ يفوق التقدم في الفيزياء.

لمكافحة التأثيرات غير المرغوبة للقناة القصيرة بمعايير التصميم 800-32 نانومتر ، تم اختراع الكثير من الحلول التكنولوجية المختلفة ، ولن أصفها جميعًا ، وإلا ستنمو المقالة إلى أحجام غير لائقة جدًا ، ولكن مع كل خطوة جديدة كان علي تقديم حلول جديدة - إضافية منشطات المناطق المجاورة لتقاطعات pn ، المنشطات في العمق لمنع التسرب ، التحول المحلي للسيليكون في الترانزستورات إلى السيليكون الجرمانيوم ... لم يتم اتخاذ خطوة واحدة في تقليل حجم الترانزستورات. اوه كذلك.

الشكل 8. طول القناة الفعالة في تقنيات 90 نانومتر و 32 نانومتر. يتم إطلاق الترانزستورات على نفس المقياس. نصف الدوائر في الأشكال هي شكل من أشكال المطابقة الضعيفة الإضافية للمصارف (LDD ، تصريف مخدر قليلاً) ، مصنوعة لتقليل عرض تقاطعات pn.

المصدر - ملخصات.انخفضت أحجام المعدن النموذجية والمسافات بين العناصر أثناء الانتقال من 90 نانومتر إلى حوالي 28 نانومتر بما يتناسب مع انخفاض في رمز التصميم ، أي أن الحجم النموذجي للجيل التالي كان 0.7 من الجيل السابق (بحيث ، وفقًا لقانون مور ، للحصول على تخفيض بمقدار شقين في المنطقة). في الوقت نفسه ، انخفض طول القناة في أحسن الأحوال بمقدار 0.9 من الجيل السابق ، ولم يتغير طول القناة الفعالة عمليًا على الإطلاق. يتبين بوضوح من الشكل أعلاه أن الأبعاد الخطية للترانزستورات لم تتغير ثلاث مرات على الإطلاق من 90 نانومتر إلى 32 نانومتر ، وكانت جميع ألعاب التقنيين تدور حول تقليل تداخل الغالق والمساحات المخدرة ، وكذلك حول التحكم في التسريبات الثابتة ، والتي لم يُسمح بها القناة أقصر.

ونتيجة لذلك ، أصبح هناك شيئان واضحان:

- اذهب إلى ما دون 25-20 نانومتر بدون عمل اختراق تكنولوجي لا يعمل ؛

- أصبح من الصعب بشكل متزايد على المسوقين رسم صورة لتقدم التكنولوجيا باستخدام قانون مور.

يعد قانون مور بشكل عام موضوعًا مثيرًا للجدل ، لأنه ليس قانونًا للطبيعة ، ولكنه ملاحظة تجريبية لبعض الحقائق من تاريخ شركة معينة ، تم استقراءها للتقدم المستقبلي للصناعة بأكملها. في الواقع ، ترتبط شعبية قانون مور ارتباطًا لا ينفصم مع مسوقي Intel ، الذين جعلوا رايتهم ، وفي الواقع ، دفعوا الصناعة إلى الأمام لسنوات عديدة ، مما أجبرها على الامتثال لقانون مور حيث قد يكون الأمر يستحق الانتظار قليلاً.ما هي طريقة اكتشاف المسوقين للوضع؟ أنيقة للغاية.

طول قناة الترانزستور جيد ، ولكن كيف يمكنك تقدير الكسب في المنطقة منه ، مما يعطي الانتقال إلى معايير التصميم الجديدة؟ منذ فترة طويلة ، استخدمت الصناعة مساحة خلية ذاكرة سداسية الترانزستور ، وهي اللبنة الأكثر شيوعًا في بناء المعالجات الدقيقة. هذه الخلايا هي التي تتكون عادة من ذاكرة تخزين مؤقت وملف تسجيل يمكن أن يشغل نصف بلورة ، وهذا هو السبب في أن مخطط وتوبولوجيا خلية سداسية الترانزستورات يتم إلصاقها دائمًا إلى أقصى حد (غالبًا ما يكون الأشخاص الخاصون الذين يفعلون ذلك بالضبط) ، لذلك هذا مقياس جيد حقًا كثافة التعبئة.

الرقم 9 الشكل. مخطط خلية ذاكرة ثابتة الترانزستور ستة.الرقم 10 الشكل. خيارات طوبولوجيا مختلفة لخلية ذاكرة ثابتة الترانزستور ستة. المصدر - G. Apostolidis et. al.، "Design and simulation of 6T SRAM Cell Structures in 32nm Technology"، Journal of Engineering Science and Technology Review، 2016لذلك لفترة طويلة في أوصاف التقنيات ، كان عدد معايير التصميم مصحوبًا بالرقم الثاني - مساحة خلية الذاكرة ، التي ، من الناحية النظرية ، يجب أن تستمد من طول القناة. ثم كان هناك استبدال مثير للاهتمام للمفاهيم. في الوقت الذي توقف فيه التدرج المباشر عن العمل ، وتوقف طول القناة عن التناقص كل عامين وفقًا لقانون مور ، خمن المسوقون أنه من الممكن عدم اشتقاق منطقة خلية الذاكرة من معايير التصميم ، ولكن لاشتقاق عدد معايير التصميم من منطقة خلية الذاكرة!

وبطبيعة الحال ، "كنا نمتلك طول قناة يبلغ 65 نانومتر ومساحة خلية ذاكرة من X ، والآن يبلغ طول القناة 54 نانومتر ، لكننا ضغطنا على المعدن ، والآن أصبحت منطقة الخلية X / 5 ، والتي تقابل تقريبًا الانتقال من 65 إلى 28 نانومتر. لذا دعنا نقول للجميع أن لدينا معايير تصميم 28 نانومتر ، ولن نخبر أحدا عن طول القناة 54 نانومتر؟ " في الإنصاف ، يعد "اللادغة اللاذعة" أيضًا إنجازًا مهمًا ، ولبعض الوقت بعد بدء المشاكل مع تصغير الترانزستورات نفسها ، أو الحد الأدنى لعرض المعدن ، أو حجم التلامس مع الترانزستور ، أو أي شكل آخر في الهيكل يتوافق مع معايير التصميم المعلنة. ولكن بعد ذلك بدأت الرقصات بترانزستورات FinFET ، حيث لم يكن للأبعاد الرئيسية أي علاقة مع دقة الطباعة الحجرية ، ومعدلات التصغير للترانزستورات وكل شيء آخر اختلف أخيرًا ، وظلت منطقة خلية الذاكرة هي الشكل الطبيعي الوحيد ، والذي يتم على أساسه إعلامنا الآن عن "10" ، " نانومتر 7 "و" 5 ".

الشكل 11. مقارنة بين تقنيات Intel 14 نانومتر و 10 نانومتر.

المصدر - إنتل.إليك مثال رائع على هذا "المقياس الجديد". لقد أظهرنا كيف تغيرت الأحجام المميزة في خلية الذاكرة. العديد من المعلمات ، ولكن ليس كلمة حول طول وعرض قناة الترانزستور!

كيف حلوا مشكلة استحالة تقليص طول القناة والسيطرة على تسرب التكنولوجيا؟

وجدوا طريقتين. الأول في الجبهة: إذا كان سبب التسرب هو عمق كبير للزرع ، فلنقلله ، ويفضل بشكل جذري. السليكون الموجود على تقنية العوازل (SIC) معروف منذ فترة طويلة جدًا (وقد تم استخدامه بنشاط طوال هذه السنوات ، على سبيل المثال ، في معالجات AMD 130-32 نانومتر ، و 90 نانومتر من سوني بلاي ستيشن 3 فك التشفير ، وكذلك في ترددات الراديو أو الطاقة أو إلكترونيات الفضاء) ، ولكن مع انخفاض في معايير التصميم ، حصلت على رياح ثانية.

الشكل 12. مقارنة الترانزستورات المصنوعة باستخدام تكنولوجيات الحجمية التقليدية و FDSOI (SOI المستنفدة بالكامل).

المصدر - ST Microelectronics .كما ترون ، الفكرة أكثر من أنيقة - يقع أكسيد تحت طبقة نشطة رقيقة جدًا ، مما يزيل تيار التسرب الضار على الكرمة! في نفس الوقت ، بسبب انخفاض قدرة الوصلات pn (تمت إزالة أربعة من الجوانب الخمسة لمكعب التصريف) ، تزداد السرعة وينخفض استهلاك الطاقة. هذا هو السبب في الإعلان عن تكنولوجيا FDSOI 28-22-20 nm بنشاط كمنصة لإنترنت الأشياء من الرقائق الدقيقة - يتم تقليل الاستهلاك بالفعل عدة مرات ، إن لم يكن بأمر من الحجم. ومع ذلك ، يسمح هذا النهج في المستقبل بتوسيع الترانزستور المسطح التقليدي إلى مستوى 14-16 نانومتر ، وهو ما لم تعد التكنولوجيا الحجمية تسمح به.

ومع ذلك ، لا تقل FDSOI بشكل خاص عن 14 نانومتر ، ولدى التكنولوجيا أيضًا مشاكل أخرى (على سبيل المثال ، التكلفة العالية الرهيبة لركائز SOI) ، والتي توصلت الصناعة إلى حل آخر - الترانزستورات FinFET. فكرة ترانزستور FinFET هي أيضًا أنيقة للغاية. هل نريد أن يتم التحكم في معظم المساحة بين المصرف والمصدر بواسطة الغالق؟ لذا دعنا نحيط هذه المساحة بمصراع من جميع الجهات! حسنا ، ليس كل شيء ، سيكون ثلاثة كافيين.

الشكل 13. هيكل FinFET.

المصدر - A. Tahrim et.al.، "Design and Performance Analysis of 1-Bit FinFET Full Adder Cells for Subthreshold Region at 16 nm Process Technology"، Journal of Nanomaterials، 2015الشكل 14. مقارنة استهلاك الطاقة من مختلف خيارات adder على الترانزستورات المستوية وعلى FinFET.

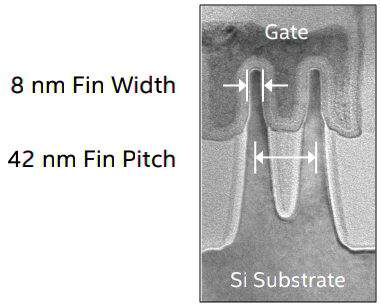

المصدر - A. Tahrim et.al.، "Design and Performance Analysis of 1-Bit FinFET Full Adder Cells for Subthreshold Region at 16 nm Process Technology"، Journal of Nanomaterials، 2015في FinFET ، القناة ليست مسطحة وتقع مباشرة تحت سطح الركيزة ، ولكنها تشكل زعنفة رأسية (الزعنفة هي الزعنفة) ، تبرز فوق السطح وتحيط بها مصراع من ثلاثة جوانب. وبالتالي ، يتم التحكم في المساحة الكاملة بين المصرف والمصدر بواسطة مصراع ، ويتم تقليل التسربات الثابتة بشكل كبير. أول Intel FinFETs التي تم إنتاجها بكميات كبيرة كانت Intel بمعايير تصميم 22 نانومتر ، وتم سحب البقية من قبل كبار المصنعين الآخرين ، بما في ذلك مدافع KNI مثل Global Foundries (AMD سابقًا).

يتيح لك رأسية القناة في FinFET ، من بين أمور أخرى ، الحفظ على مساحة الخلية ، لأن FinFET مع قناة واسعة ضيقة جدًا في الإسقاط ، وهذا بدوره ساعد المسوقين مرة أخرى بقصصهم حول منطقة خلية الذاكرة وانخفاضها بمقدار شقين مع كل جديد خطوة "معايير التصميم" ، لم تعد مرتبطة بالأبعاد المادية للترانزستور.الشكل 15. طوبولوجيا الخيارات المختلفة لخلايا الذاكرة (5T-9T) في التكنولوجيا مع FinFET. المصدر - M. Ansari et. al. ، "خلية SRAM 7T قريبة من العتبة ذات هوامش عالية للكتابة والقراءة ووقت كتابة منخفض لتقنيات FinFET تحت 20 نانومتر" ، مجلة VLSI حول التكامل ، المجلد 50 ، يونيو 2015. فيمايلي أمثلة لخيارات مختلفة لخلايا الذاكرة في التكنولوجيا مع FinFET. انظر كيف أن العرض الهندسي للقناة أصغر بكثير من الطول؟ يمكنك أيضًا ملاحظة أنه على الرغم من كل الاضطرابات ، لا يزال نظام لامدا بين طوبولوجي قيد الاستخدام للتقديرات الكمية. وماذا عن الأعداد المطلقة؟الشكل 16. بعض أحجام الترانزستورات في تقنيات 14-16 نانومتر.

المصدر - وقائع مؤتمر ConFab 2016.كما يتضح من الشكل ، لا يزال طول القناة الطوبولوجية في 16 نانومتر من تقنيات FinFET أكبر من 20-25 نانومتر ، والتي تم ذكرها أعلاه. وهذا منطقي ، لأنه لا يمكن خداع الفيزياء. ولكن يمكن استخلاص استنتاج آخر أكثر إثارة للاهتمام من نفس الشكل: إذا نظرت عن كثب ، يصبح من الواضح أن الحد الأدنى للحجم المتاح في الترانزستورات ليس طول القناة ، ولكن عرض الزعنفة. وهنا ننتظر اكتشافًا مضحكًا: عرض الزعنفة في تقنية معالجة Intel 16 نانومتر هو (أسطوانة الأسطوانة!) ثمانية نانومتر. الشكل 17. أبعاد الزعانف في تقنية معالجة Intel 14 نانومتر.

الشكل 17. أبعاد الزعانف في تقنية معالجة Intel 14 نانومتر.

المصدر - wikichip.orgكما ترون ، هنا المسوقين ، المرتبطين بحجم خلية الذاكرة ، خدعوا أنفسهم ، والآن يضطرون للتعبير عن الرقم أكثر مما يستطيعون. في الواقع ، بالطبع ، في ظروف التغيير الأساسي في هيكل الترانزستور وتوقع المستخدمين لسماع نوع من المقاييس ، ربما كان استخدام مقياس يعكس كثافة التعبئة هو القرار الصحيح الوحيد ، وكان المسوقون على حق في النهاية ، على الرغم من أن هذا يؤدي في بعض الأحيان إلى مواقف مضحكة عندما تسمى معايير التصميم نفسها في شركات مختلفة بشكل مختلف. على سبيل المثال ، عند قراءة الأخبار التي تفيد بأن TSMC قد أطلقت بالفعل 7 نانومتر ، وتؤخر Intel مرة أخرى بدء إنتاج 10 نانومتر ، من الجدير بالذكر أن 7 نانومتر TSMC و 10 نانومتر Intel في الواقع هي نفس معايير التصميم من حيث وكثافة التعبئة وحجم الترانزستورات الفردية.ما هي الخطوة التالية؟

في الواقع ، لا أحد يعرف. لقد استنفد قانون مور نفسه منذ فترة طويلة ، وإذا كان قبل عشر سنوات كان الجواب على السؤال "ماذا بعد؟" يمكن العثور عليه في تقارير المراكز البحثية ، والآن يُسمع بشكل متزايد أنه يجب التخلي عن التطورات الواعدة ، حيث تبين أنها صعبة التنفيذ بشكل مفرط. حدث هذا بالفعل مع الرقائق التي يبلغ قطرها 450 ملم ، وهذا هو الحال جزئيًا مع الطباعة الحجرية EUV (التي اعتاد العلماء تشغيلها لمدة عشرين عامًا) ، وربما يحدث هذا مع الترانزستورات على الجرافين والأنابيب النانوية الكربونية. هناك حاجة إلى اختراق تكنولوجي آخر ، لكن الطريق المؤسف إليه ، للأسف ، غير واضح حتى الآن. وصل الأمر إلى النقطة التي اتصل بها المدير الجديد لـ TSMC Mark Liuالاتجاه الأكثر وعدًا في تطوير التكنولوجيا الإلكترونية الدقيقة ليس تقليل حجم الترانزستورات ، بل التكامل ثلاثي الأبعاد. إن التكامل ثلاثي الأبعاد "الحقيقي" ، بدلاً من الجمع بين العديد من الرقائق في حزمة واحدة ، سيشكل بالفعل علامة فارقة في تطوير الإلكترونيات الدقيقة ، ولكن يبدو أن قانون مور ، كقانون تقليل حجم الترانزستورات ، قد مات تمامًا.