معدل البيانات الرباعي (QDR-IV) هو معيار ذاكرة عالي الأداء لتطبيقات الشبكة وهو مثالي للجيل القادم من أجهزة الشبكة ومعدات الاتصالات وأنظمة الحوسبة.

يحتوي QDR-IV SRAM على وحدة مضمنة لاكتشاف الأخطاء وتصحيحها (ECC) لضمان تكامل البيانات. هذه الوحدة قادرة على معالجة جميع أخطاء الذاكرة أحادية البت ، بما في ذلك تلك التي تسببها الأشعة الكونية وجسيمات ألفا. ونتيجة لذلك ، سيكون لدى وحدات الذاكرة معدل خطأ في البرنامج (SER) لا يزيد عن 0.01 من الفشل / ميجابايت. تم تجهيز QDR-IV بوظيفة تكافؤ العنوان القابلة للبرمجة التي تضمن تكامل البيانات في ناقل العنوان.

الميزات المميزة لذاكرة QDR SRAM:

- تضمن وحدة تصحيح الأخطاء المتكاملة سلامة البيانات وتقضي على أخطاء البرامج

- الوحدات متوفرة في نسختين: QDR-IV HP (معدل البيانات 1334 Mtrans / s) و QDR-IV XP (معدل البيانات 2132 Mtrans / s)

- منفذا بيانات ذاكرة DDR1 ثنائي الاتجاه مستقلان

- وظيفة انقلاب الحافلة لتقليل الضوضاء أثناء توصيل خطوط الإدخال والإخراج

- نظام التفاوض المتكامل (ODT) يقلل من تعقيد اللوحة

- تدريب انحراف لتحسين توقيت التقاط الإشارة

- قوة إشارة الإدخال / الإخراج: 1.2V إلى 1.25V (منطق الإرسال والاستقبال عالي السرعة (HSTL) / المنطق المنهي (SSTL)) ، 1.1V إلى 1.2V (POD2)

- 361 دبوس FCBGA3 حزمة

- عرض الناقل: x18 ، x36 بت

مقدمة

معالج DDRx هو أداة سهلة الاستخدام في HyperLynx تتيح لك التحكم في أشكال الموجات الزمنية للتحكم الدفعي وتحليل سلامة الإشارة لبروتوكولات DDR JEDEC القياسية. يمكن تشغيل معالج DDRx في كل من مرحلة تحليل ما قبل الطوبولوجيا وفقًا لسيناريو "ماذا لو" ، وعلى لوحة يتم تتبعها بالكامل. بالإضافة إلى ذلك ، تتيح لك الأداة استيراد معظم تنسيقات النماذج التي تم إنشاؤها بواسطة موردي الشرائح الرئيسيين.

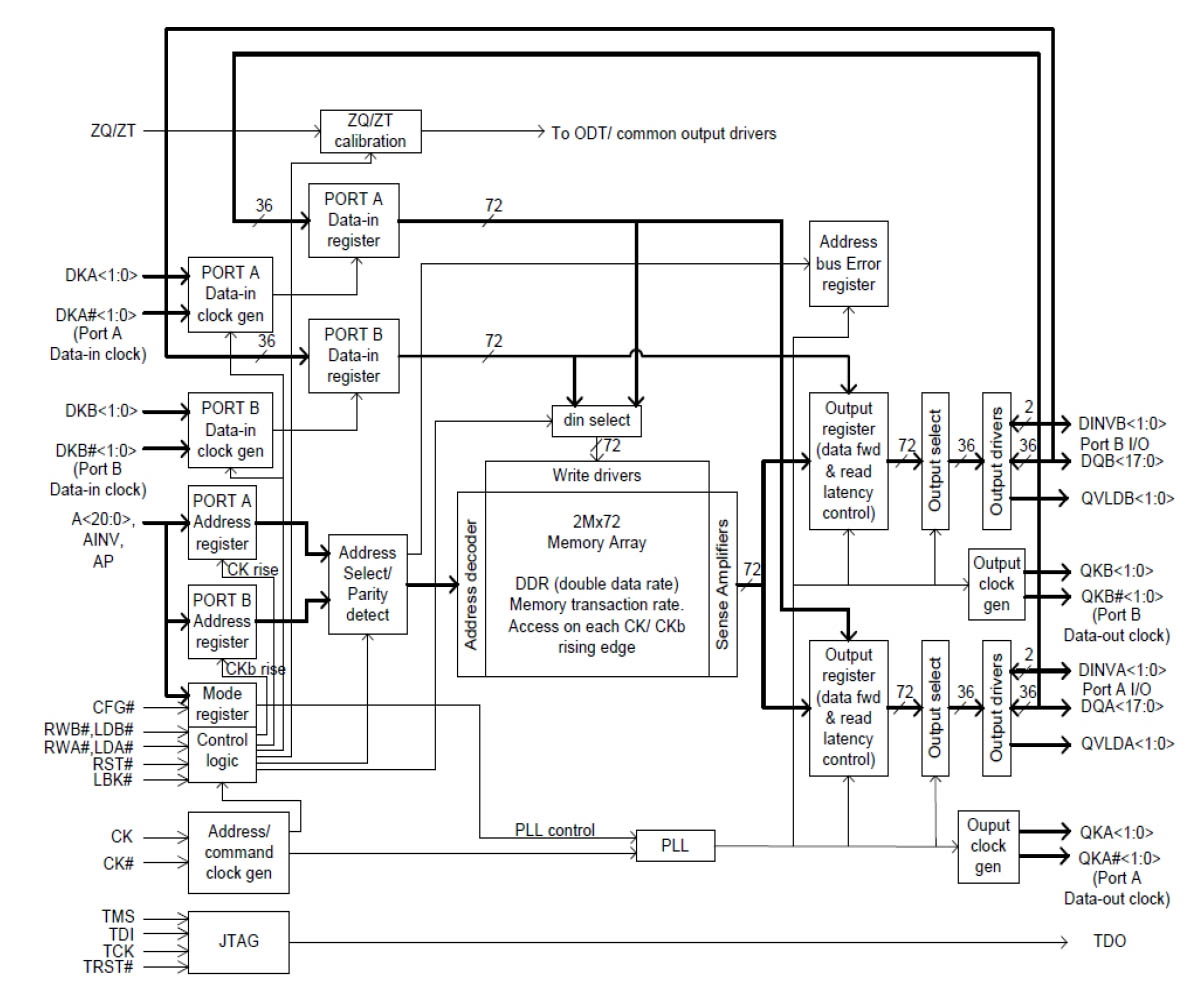

يسمح لك معالج DDRx بالتحقق من جميع أجزاء ناقل الذاكرة للتأكد من توافقها مع سلامة الإشارة ، بالإضافة إلى الامتثال لمتطلبات المزامنة بين الإشارات. توضح هذه المقالة بالتفصيل استخدام المساعد التفاعلي لتحليل المشاريع التي تنفذ بروتوكول QDR4 (الشكل 1).

التين. 1. البنية الداخلية لـ QDR على مثال الوحدة النمطية CY7C4142KV13 (قابلة للنقر)

التين. 1. البنية الداخلية لـ QDR على مثال الوحدة النمطية CY7C4142KV13 (قابلة للنقر)نظرة أولى على QDR-IV في HyperLynx DDRx WIZARD

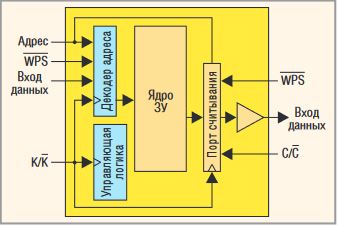

يحدد بروتوكول QDR-IV اثنين من أزواج أحادية الاتجاه لإشارة ستروب البيانات: أحدهما لقراءة البيانات ، والآخر للكتابة ، والتي تدعم مستقلة عن بعضها البعض وعمليات القراءة والكتابة المتزامنة ، ويمكن أن تعمل المنافذ بترددات مختلفة (الشكل 2). وبالتالي ، يتم القضاء تمامًا على خطر حدوث خلل.

التين. 2. توفر منفذين منفصلين للقراءة والكتابة في بنية QDR SRAM

التين. 2. توفر منفذين منفصلين للقراءة والكتابة في بنية QDR SRAMبالنسبة لهذا البروتوكول ، سيستخدم معالج DDRx بوابات منفصلة لقراءة البيانات وكتابتها. يتم تنفيذ QDR IV عادةً باستخدام ناقل x36 أو x18 بت (انظر الشكل 3 أ و 3 ب).

يتيح معالج DDRx محاكاة QDR-IV في ثلاث خطوات:

- التحقق من قراءة البيانات

- فحص سجل البيانات

- فحص ناقل العنوان / التحكم

نظرًا لأنه يمكن إجراء عمليات فحص ناقل العنوان / التحكم بشكل مستقل عن عمليات فحص قراءة / كتابة البيانات ، يمكن أن يوفر لك هذا الوقت من خلال دمج هذه الخطوة مع أي من خطوات اختبار البيانات. فيما يلي وصف لجميع السيناريوهات الثلاثة لهذه الاختبارات.

الميزات التكنولوجية

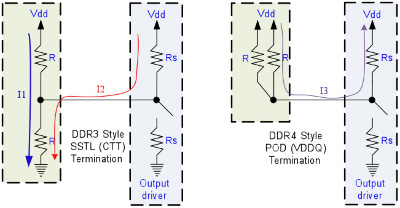

يدعم QDR-IV تقنية الاستنزاف المفتوح الزائف (POD) ومنطق الإنهاء المنهجي لسلسلة كعب الروتين (SSTL) (الشكل 4).

التين. 4. الفروق بين POD و SSTL

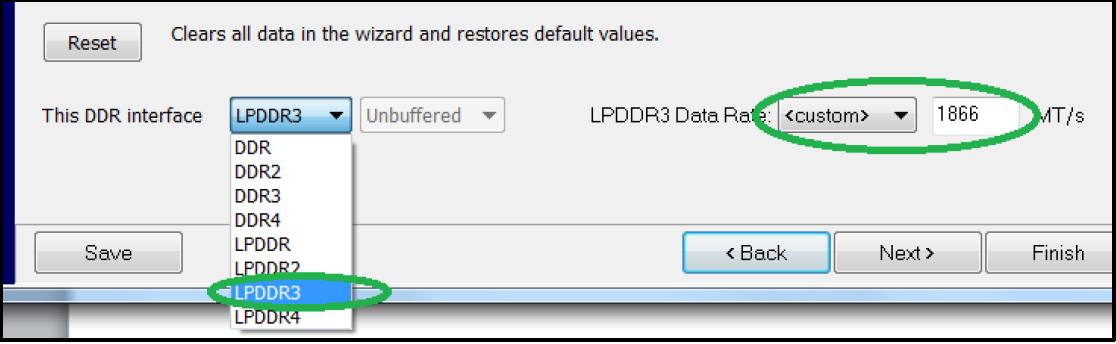

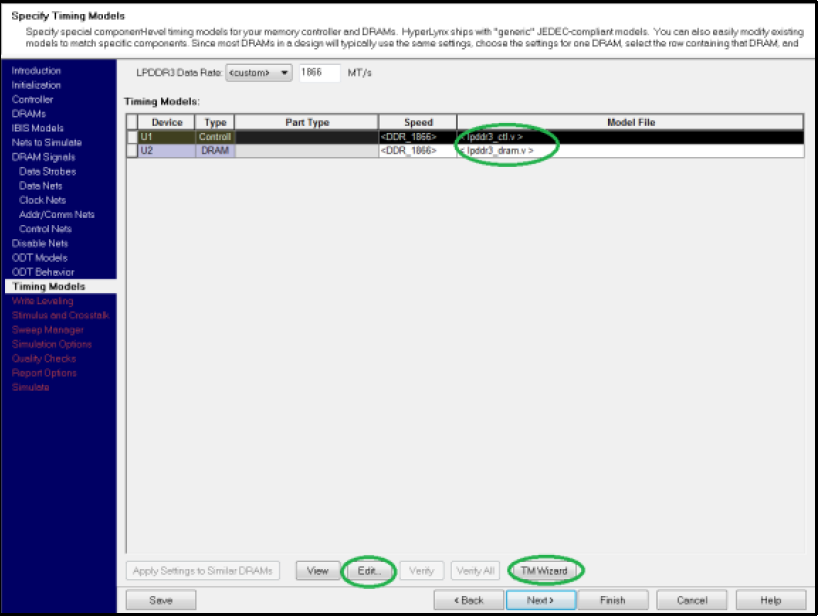

التين. 4. الفروق بين POD و SSTLبغض النظر عن المعيار المنطقي المستخدم ، حدد

LPDDR3 كتقنية (الشكل 5) ، نظرًا لعدم وجود دعم

لتدريب Vref ، كما هو الحال مع وحدة POD الخاصة بـ DDR4. بدلاً من ذلك ، يتم استخدام القيم الثابتة Vref و Vinh / Vinl ، على غرار DDR3 و LPDDR3. نظرًا لأن QDR-IV يستخدم معدل بيانات مزدوج لإشارات العناوين مثل LPDDR3 ، فمن المستحسن تحديد هذا الخيار. بعد ذلك ، أدخل معدل نقل بيانات المستخدم ، على سبيل المثال ، 1866 MT / s أو 2133 MT / s ، حيث MT / s هو عدد عمليات النقل الضخمة في الثانية (عمليات النقل الضخمة في الثانية).

التين. 5. اختيار المنطق القياسي

التين. 5. اختيار المنطق القياسيإشارة البيانات: قراءة العملية

بالنسبة لعمليات قراءة إشارة البيانات ، سيتحكم DRAM في إشارات DQ بالتزامن مع إشارات QK التفاضلية القوية. وبالتالي ، يركز الإعداد على عملية قراءة البيانات ، ويعين الدوائر (الإشارات) اللازمة لبوابة QK المقابلة.

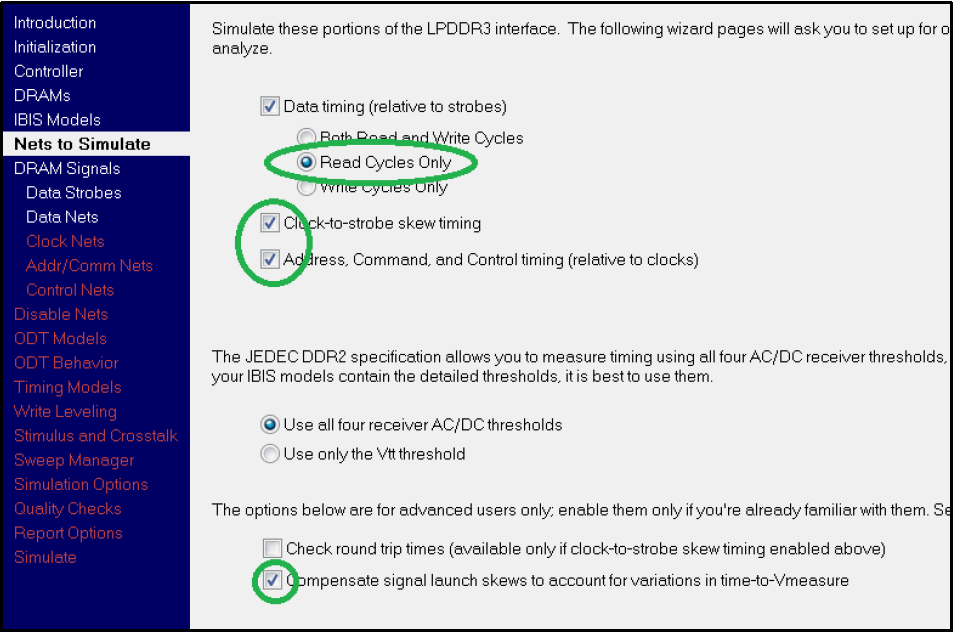

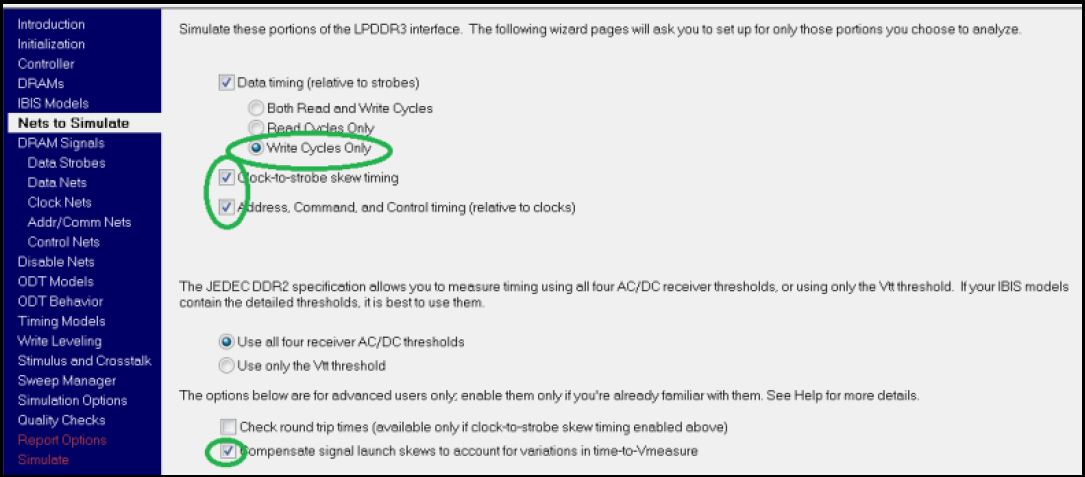

في قسم

شبكات المحاكاة (الشكل 6) ، ضع علامة في المربع "

دورات القراءة فقط ".

مربعات الاختيار "ساعة إلى ستروب" و "التحقق من العنوان" اختيارية.

أيضا ، تحقق من تثبيت

انحرافات إطلاق إشارة التعويض لمراعاة الاختلافات في خانة الاختيار الوقت إلى القياس .

التين. 6. قراءة البيانات

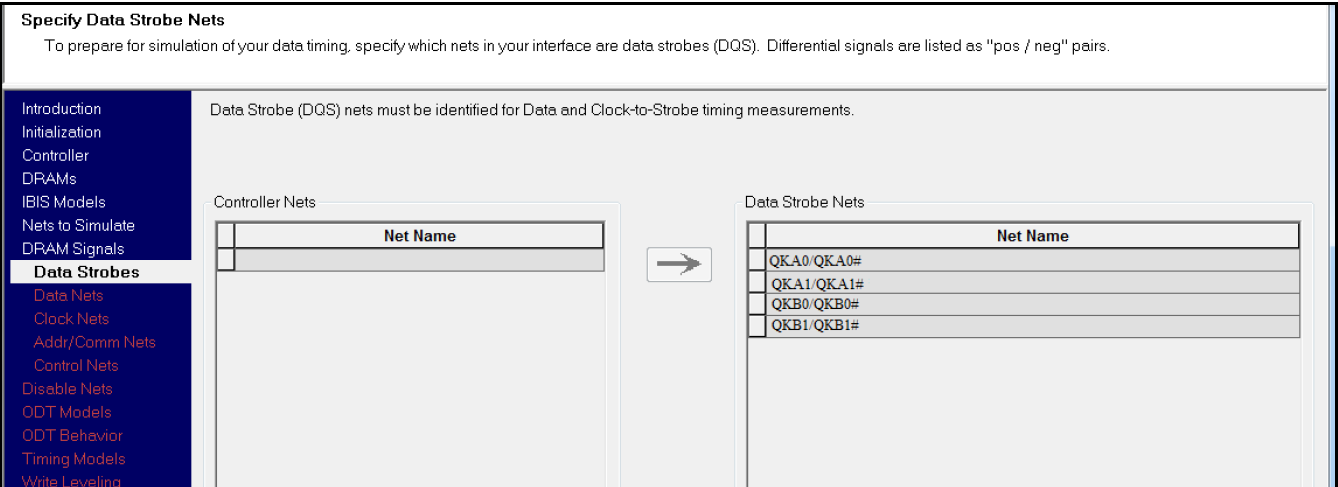

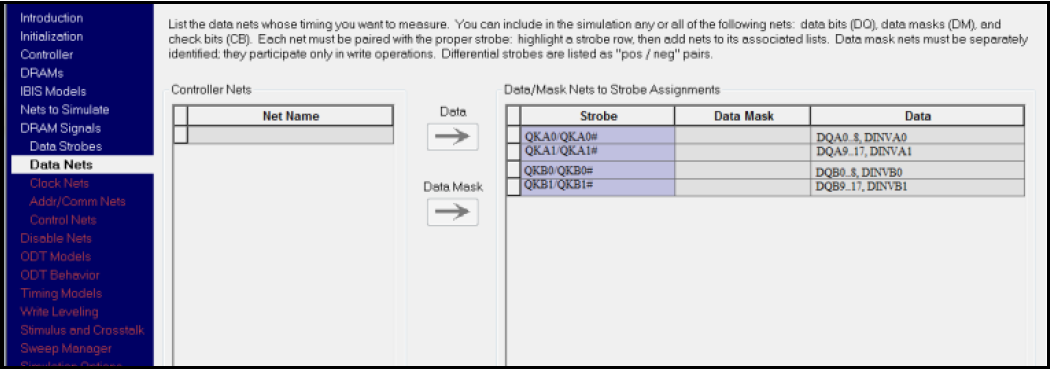

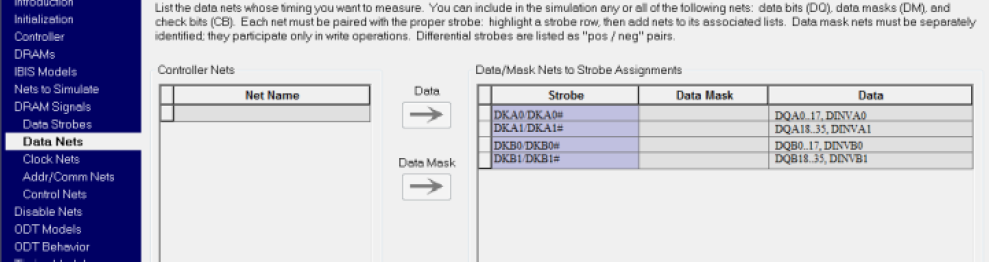

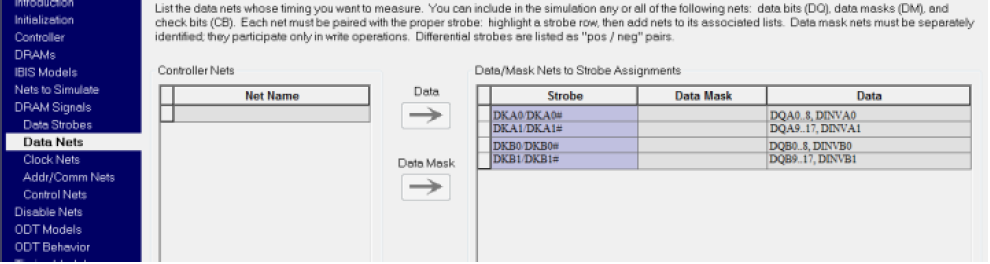

التين. 6. قراءة البياناتتأكد من تحديد جميع ستروب البيانات الضرورية (الشكل 7).

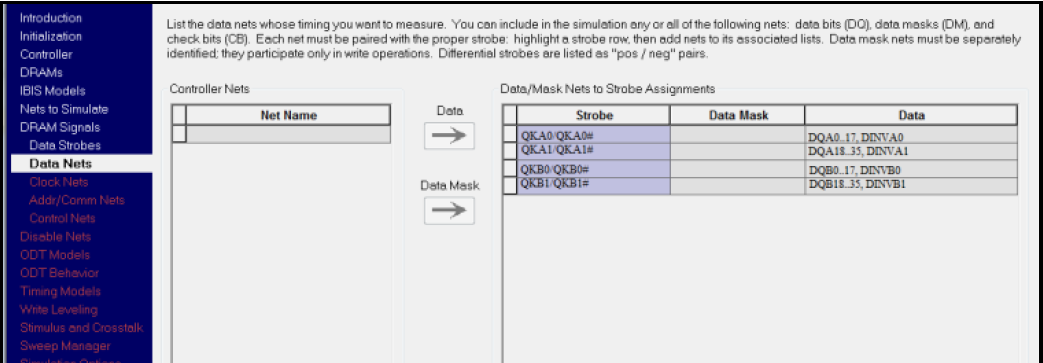

في قسم

شبكات البيانات ، تحقق من أن كل إشارة تطابق كل بوابة بشكل صحيح. يرجى ملاحظة أن الإشارات تختلف عن الحافلات x18 و x36 bit ، لذا تأكد من أن pinout مناسب لحالتك الخاصة (الشكل 8 أ و 8 ب).

التين. 7. قراءة ستروب البيانات

التين. 7. قراءة ستروب البيانات التين. 8 أ. مجموعة الإشارة لحافلة 36 بت

التين. 8 أ. مجموعة الإشارة لحافلة 36 بت التين. 8 ب. مجموعة إشارة للحافلة ذات 18 بت

التين. 8 ب. مجموعة إشارة للحافلة ذات 18 بتعادة ما يتم اختبار الناقل المتوازي عن طريق ضبط / عقد الوقت بين ستروب والإشارة. كل هذه المتطلبات ، بالإضافة إلى القيم المؤقتة الأخرى ، مطلوبة بواسطة معالج DDRx للتحقق من النتائج. قد تختلف هذه القيم من رقاقة إلى شريحة ، لذلك يوصى بإدخال قيم تنطبق على جهاز ذاكرة معين. بالإضافة إلى ذلك ، لا تتوافق معلومات التوقيت الافتراضية لـ LPDDR3 مع QDR-IV. لذا ، يجب إدخال جميع معلومات التوقيت الخاصة بـ QDR-IV وتتوافق مع وثائق الشريحة الخاصة بك.

يمكن القيام بذلك إما باستخدام

معالج التوقيت (الشكل 9) ، الذي يطالب المستخدم بملء عدة نماذج للجيل اللاحق للقيم المؤقتة ، أو يمكنك تحرير ملفات المزامنة .V التي تتوافق مع وحدة التحكم والذاكرة.

التين. 9. تحديد قيم التوقيتيرجى ملاحظة

التين. 9. تحديد قيم التوقيتيرجى ملاحظة : بما أن المحاكاة تتم في وضع

LPDDR3 ، فيجب تفسير النتائج وفقًا لذلك.

إشارة البيانات: عملية الكتابة

تشبه عملية كتابة البيانات وتحليلها تحليل عملية القراءة الموضحة أعلاه. ولكن هناك اختلافان رئيسيان سننظر فيهما الآن. باستثناء هذين الفروق الدقيقة ، يمكن تكرار الخطوات التي تم اتخاذها لعملية قراءة البيانات لمحاكاة كتابة البيانات.

في قسم

شبكات المحاكاة (الشكل 10) ، تأكد من تحديد

دورات الكتابة فقط .

من الممكن أيضًا محاكاة

عمليات كتابة إشارة العنوان . ولا تنس أن تتأكد

من تحديد خانة الاختيار Compensate Skew Launch لمراعاة الاختلافات في الوقت المحدد إلى Vmeasure .

التين. 10. تسجيل البيانات

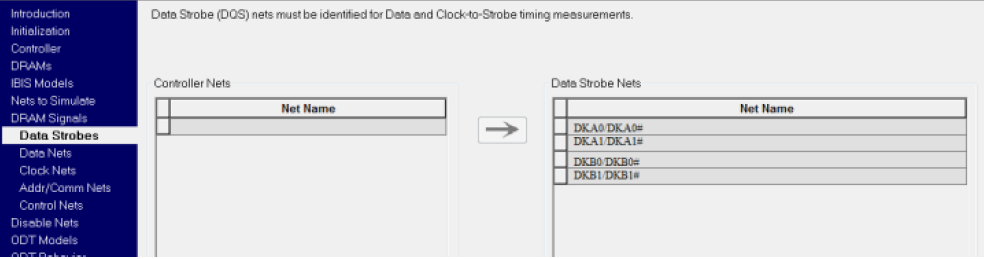

التين. 10. تسجيل البياناتتأكد من تحديد البوابات الصحيحة في قسم

Data Strobe (الشكل 11). الفرق الرئيسي بين معاملة القراءة ومعاملة الكتابة هو القوية المستخدمة لمزامنة البيانات ؛ يختلف هذا القوية عن القوية المستخدمة لعملية قراءة البيانات (الشكل 12 و 13).

التين. 11. بوابات بيانات السجل

التين. 11. بوابات بيانات السجل التين. 12. مجموعات إشارة ستروب إشارة (ناقل 36 بت)

التين. 12. مجموعات إشارة ستروب إشارة (ناقل 36 بت) التين. 13. مجموعات إشارة ستروب إشارة (ناقل 18 بت)

التين. 13. مجموعات إشارة ستروب إشارة (ناقل 18 بت)عنوان الحافلة والقيادة والتحكم

يستخدم QDR-IV أقفال تفاضلية CK / CK # لتحديد إشارات التحكم والعنوان وإشارات الأوامر. يتم استخدام الحافة الأمامية لإشارة CK لإدخال معلومات حول المنفذ A ، وتستخدم الحافة اللاحقة لتحديد المعلومات حول المنفذ B.

مع مراعاة سلامة الإشارة ، يجب أن تلبي الأشكال الموجية لخطوط العنوان متطلبات التثبيت والتأخير لكل من الحواف الأمامية والخلفية لإشارة الساعة. هذا مشابه جدًا لسلوك LPDDR3.

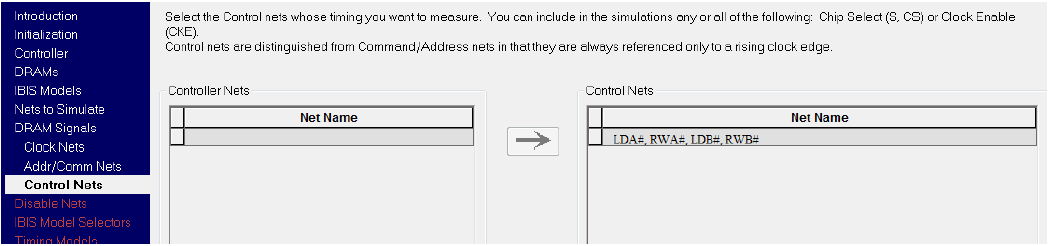

تتم مزامنة الإشارات

LDA # و LDB # و RWA # و RWB # بنفس معدل البيانات (معدل البيانات المفردة). وهذا يعني أن هذه الإشارات متزامنة فقط على إحدى جبهتين من نبضات الساعة. تتم مزامنة الإشارات LDA # و RWA # على الحافة الصاعدة للساعة ، والإشارات LDB # و RWB # على الحافة المتساقطة.

الكتل متماثلة إلى حد كبير - لا تختلف الجبهة التفاضلية الأمامية كثيرًا عن الخلف. وهذا يعني أنه لضمان سلامة الإشارة ، يجب أن تكون قيم التوقيت لـ

LDB # و RWB # هي نفسها تقريبًا ، إن لم تكن متطابقة ، عند أخذ العينات عند

الحواف الصاعدة أو

الهابطة للساعة. تتم مزامنة إشارات التحكم LPDDR3 أيضًا على الحافة المرتفعة فقط.

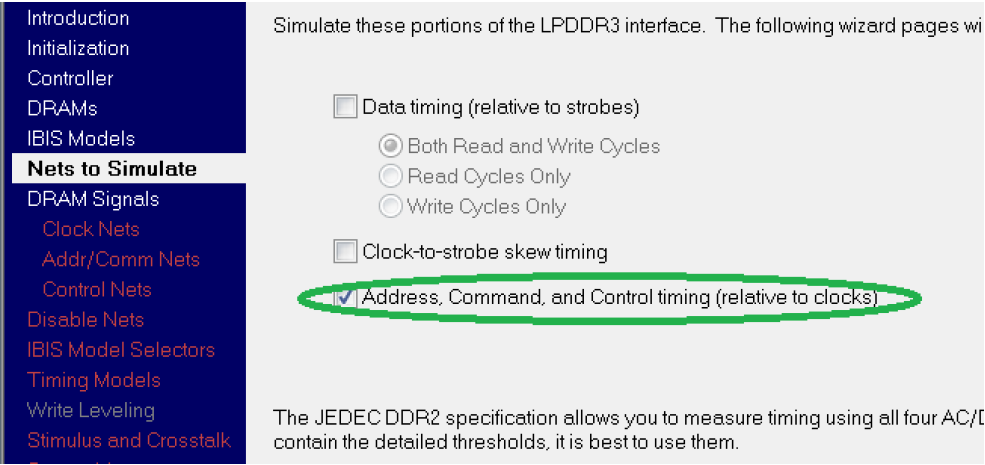

تعتبر الخطوات التالية خاصة بمحاكاة ناقل العنوان والأمر والتحكم باستخدام ناقل QDR-IV.

تأكد من

تحديد خانة الاختيار

توقيت العنوان والقيادة والتحكم (بالنسبة إلى الساعات) في قسم "

شبكات المحاكاة" (الشكل 14).

التين. 14. ضع علامة في المربع العنوان ، الأمر والتحكم

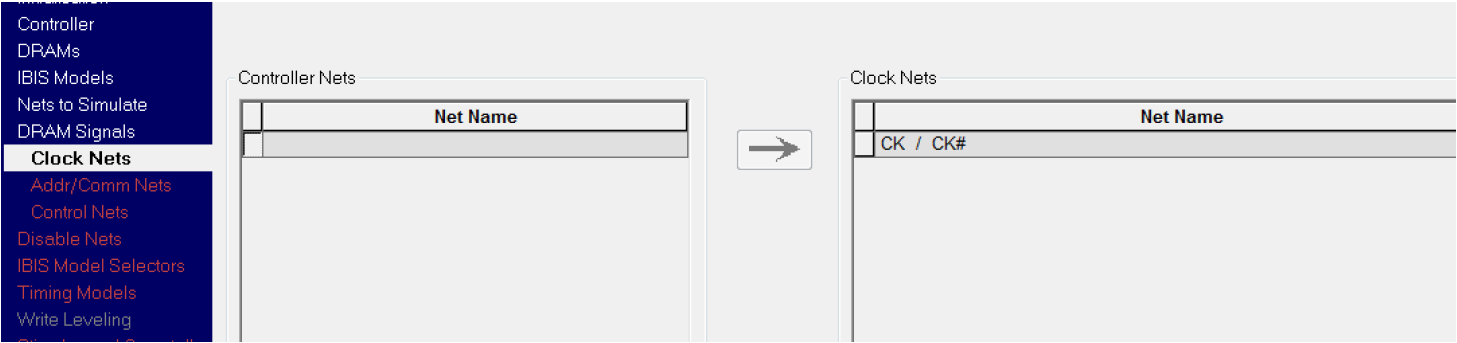

التين. 14. ضع علامة في المربع العنوان ، الأمر والتحكمفي قسم

شبكات الساعة ، تأكد من تحديد الزوج التفاضلي لإشارات الساعة CK / CK # (الشكل 15).

التين. 15. اختيار الساعة التفاضلية

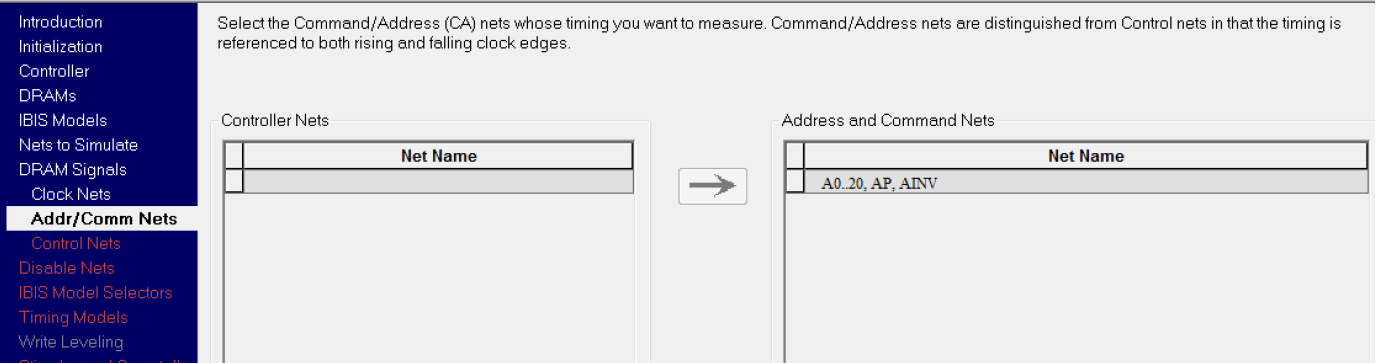

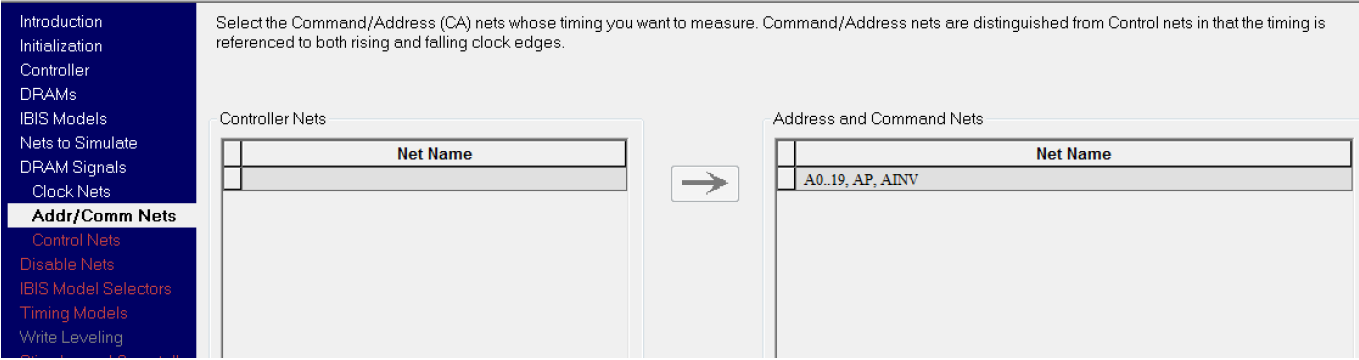

التين. 15. اختيار الساعة التفاضليةفي قسم

Addr / Comm Nets ، تأكد من تحديد البتات

A [20: 0] للأجهزة التي تحتوي على x36 بت والبتات

A [19: 0] للأجهزة ذات x18 بت. بالإضافة إلى ذلك ، قم بتعيين

إشارات AP و AINV (الشكل 16 و 17).

التين. 16. إعدادات الحافلات x36 بت

التين. 16. إعدادات الحافلات x36 بت التين. 17. إعدادات الحافلات x18 بت

التين. 17. إعدادات الحافلات x18 بتفي قسم

شبكات التحكم ، حدد إشارات LDA # و LDB # و RWA # و RWB # (الشكل 18).

التين. 18. إشارات التحكم

التين. 18. إشارات التحكمكما هو الحال مع نمذجة إشارة البيانات ، تأكد من أنك تستخدم الملفات الصحيحة مع معلمات التوقيت. يشبه ما تبقى من النمذجة وتقييم النتائج LPDDR3.

"تفسير نتائج تقرير HyperLynx DDRx"الخلاصة

باتباع الإرشادات البسيطة في هذه المقالة ، يمكنك الاستفادة من حزمة مساعد معالج DDRx واستخدامها لمحاكاة واختبار ناقل QDR-IV.

آمل أن يكون هذا الدليل مفيدًا لشخص ما.

مع خالص التقدير ، فيليبوف بوغدان (

pbo ).

أغتنم هذه الفرصة أيضًا ، أود أن أدعو مطوري REU إلى ندوة نظمتها Nanosoft و Mentor Graphics:

"جيل جديد من حلول تصميم الأجهزة الإلكترونية من Mentor Graphics"