تحياتي يا هبر! اسمي دانييل سميرنوف ، أدرس في كلية الدراسات العليا في جامعة ITMO ، حيث يعمل فريقنا في مجال الإلكترونيات القابلة للبرمجة للمشاريع المتعلقة بأجهزة استشعار الألياف البصرية في مختبر البرمجة والنمذجة. كقاعدة أجهزة لأجهزة الاستشعار ، يتم استخدام FPGAs - مصفوفة بوابة قابلة للبرمجة الميدانية. منذ بضع سنوات ، علمنا أن مصنعي FPGA يقومون بإجراء مسابقات بين طلاب التطوير. منذ ذلك الحين ، كل عام يتم تشكيل فريق منا للمشاركة في هذا الحدث ، ومنذ أن تبين أن هذا العام كان خاصًا ، قررنا مشاركة كيف كان كل شيء من الداخل.

الدخول

كان أكتوبر 2017 ، قمت بإجراء فحص روتيني أسبوعي: تحليل للمؤتمرات الجارية حول الموضوعات التي يتم تنفيذها في قسمنا. في مرحلة ما ، أتلقى رسالة إخبارية من Terasic:

بدأت منافسة جديدة في تطوير المشاريع باستخدام لوحات التصحيح على FPGA ، الآن في جميع أنحاء العالم. تمر تجربة المسابقة نفسها في العام الماضي من خلال رأسي وتتذكر: التأجيل حتى الأسبوعين الأخيرين من الشهر ، تصحيح الأخطاء وضبط الخوارزميات الطويلة وإصدار جميع القنوات إلى الشاشة ووعد بعدم تأجيلها حتى اليوم الأخير.

لقد كانت تجربة رائعة ، تعلمنا خلالها الكثير عن نظام أساسي مثل SoC FPGA - الترابط بين مجموعة كبيرة من العناصر المنطقية ومعالج Cortex-A9 ، بالإضافة إلى تفاعلها مع بعضها البعض ومع الأجهزة الطرفية على لوحة التصحيح.

منافسة جديدة - قواعد جديدة ومتطلبات جديدة ومستوى جديد. تجري المسابقة الآن على عدة مراحل: أولاً ، تقام المراحل الإقليمية ، ثم النهائية في سان خوسيه ؛ يتم إرسال اللوحة إلى جميع المشاركين نفس

DE10-Nano ، بالإضافة إلى ذلك ، يمكنك الآن اختيار ليس فقط الوحدات الثلاث الأساسية ، ولكن أيضًا نسخة كبيرة من اللوحات من الأجهزة التناظرية! ومع ذلك ، على عكس المسابقات في السنوات السابقة ، هذه المرة من الضروري التوقيع على ضمان للمشروع ، وفي حالة عدم الإنجاز ، يجب على المشاركين إعادة الرسوم. إنه أمر عادل ، مع الأخذ في الاعتبار إحصاءات السنوات الماضية:

<...> سجل 71 فريقًا من 20 دولة أوروبية المسابقة <...> استعرض 25 قاضيًا من الصناعة (ALTERA) والأكاديمية (CNFM) في فرنسا 32 مشروعًا [1].

كان المستشار العلمي ، مثل الطلاب الذين أرادوا المشاركة في هذا العمل ، يعاني بالفعل من عبء ثقيل على مشاريع مختلفة ، لكن الإثارة خلال المسابقة والدافع لتعلم الكثير من الأشياء الجديدة أصبحت حججًا ثقيلة للمشاركة في المسابقة مرة أخرى. بقي من أجل التوصل إلى مشروع يمكنك التقدم إليه.

فكرة لمشروع

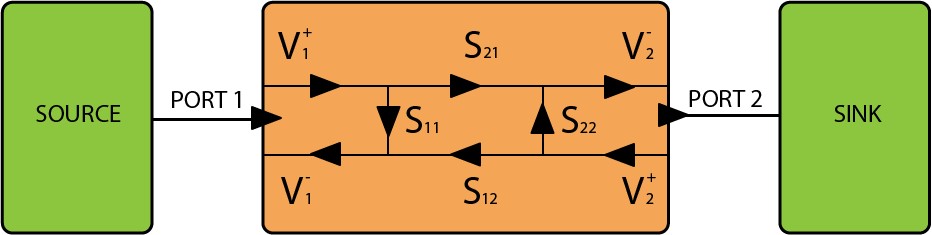

حتى لا يقف المشروع جانباً ، تقرر تنفيذ جهاز مفيد للقسم ، والذي يمكن تطويره وتحسينه لاحقاً بسهولة. استنادًا إلى مجالات نشاط القسم ، كانت هناك خيارات مختلفة: مقياس انعكاس بصري ، منظار الذبذبات الستروبكوبي ، وما إلى ذلك. بالنظر بسرعة إلى التطبيقات الحالية واللوحات الإضافية المتاحة ، تم الكشف عن أن مقياس الانعكاس قد تم الإعلان عنه بالفعل ، ولكن لا يمكن تجميع منظار الذبذبات الستروبوسكوبي على هذه العناصر. الفكرة الوحيدة التي تبقى على قيد الحياة هي محلل شبكة المتجهات. في اليوم الآخر تم إحضار ملفين إلى المختبر ، ولم يكن هناك وثائق. كانت المهمة هي تحديد الخصائص التقريبية على الأقل لهذه الملفات. كان من المعروف أن الدائرة التذبذبية تم تجميعها فيها ، لذلك كانت المهمة الرئيسية هي معرفة تردد الرنين. في مثل هذه المهام ، يمكن لمحلل شبكة النواقل (VAC أو VNA - Vector Network Analyzer) أن يجد التطبيق فقط. يتيح لك VNA تعريف مصفوفة التشتت ، والمعروفة أيضًا باسم مصفوفة معلمة S. في هذه الطريقة ، يعتبر العنصر قيد الدراسة بمثابة صندوق أسود ، يتم فيه تحليل الحادث والإشارات المنعكسة من منافذ هذا الجهاز. لذلك ، بالنسبة لنظام ثنائي المنفذ ، تكون المصفوفة كما يلي:

حيث V1 + V2 + هي موجات كهرومغناطيسية تصل إلى الموانئ ؛

V1- V2- - موجات كهرومغناطيسية تغادر المنافذ ؛

Sij هي عناصر مصفوفة الانتثار متعدد المسارات. [2]

مخطط قياس المعلمات S من متعدد

مخطط قياس المعلمات S من متعددفشلنا في فحص المكونات والدوائر باستخدام الأشعة السينية (على الأقل بواسطة الأشعة السينية لمترو الأنفاق) ، لذلك تم تجميع الدائرة التالية على الركبتين: تم ضبط الترددات بالتناوب مع خطوة من خلال الدوران إلى إدخال الملف باستخدام مولد ، تم توصيل المنفذ الثاني للدوران بإدخال الملف ، والمدخل الثالث إلى مرسمة الذبذبات التي تحتوي في برنامجها على وضع تحليل تردد السعة. مثل هذه الدائرة تجعل من الممكن قياس المعلمة S11 ، أي انعكاس. في النهاية ، بعد الكثير من الألم والمعايرة ، تمكنت من إزالة هذه الخاصية - ولكن بأي ثمن؟ لطالما توقع القسم الحصول على محلل شبكة متجه لمثل هذه المهام (قياس AFC للأجهزة الإلكترونية) ، ولكن هذا الشراء كان دائمًا ما يتأخر إلى حد ما.

بعد الضجة مع الملفات ، تقرر تجميع محلل الدائرة الخاص بك مع التصور والضبط المريح. ليس من الصعب العثور على الإثارة والرغبة في تعلم شيء جديد لنفسك من الطلاب وطلاب الدراسات العليا العاملين في القسم ، لذلك تم تجميع الفريق بسرعة من مهندس إلكتروني ومطور مبرمج للأنظمة على رقاقة وأنا ومرشدين.

لم يقل من فعله. بعد العديد من المناقشات حول نطاق التردد وخوارزميات المعالجة والمعلمات الأخرى للمشروع ، احتوى التطبيق على ما يلي:

- المشروع المطالب به هو محلل دائرة متجه يعتمد على SoC FPGA على لوحة DE10-Nano ؛

- الألواح الإضافية المطلوبة: لوحة بها مولد تردد قابل للبرمجة وخلاط عالي التردد ولوحة مع ADC ؛

- نطاق تردد التشغيل: وفقًا للمعلمات المعروضة لألواح إضافية ؛

- إمكانيات التوسع السريع في عدد المنافذ المتصلة ؛

- إخراج السعة ومكونات الطور على الشاشة ؛

- وظائف الإدخال / الإخراج الأساسية الأخرى لمحلل شبكة المتجه.

للانتقال إلى المرحلة التالية ، كان من الضروري أن تحصل صفحة المشروع على عدد كاف من "الإعجابات" من المستخدمين الذين سجلوا على الموقع. في البداية ، سار كل شيء على ما يرام ، ولكن بعد ذلك بدأت بعض المشاريع المريبة تكتسب قيمًا غير واقعية ومتباينة للإعجابات والآراء مقارنة بالمشاريع الأخرى. اتضح أن موقع المسابقة كان عرضة للغش.

بعد مرور بعض الوقت ، أبلغ المنظمون أن لجنة الحكام ستظل تختار المرشحين النهائيين ، وبالتالي فإن الإعجابات من المستخدمين ، في الواقع ، فقدت وزنها. في 31 يناير ، ظهر فريقنا في قوائم أولئك الذين ذهبوا إلى المرحلة التالية وبدأنا نفكر في مشروعنا بمزيد من التفصيل تحسبًا لتصحيح الأخطاء.

حقيقة قاسية

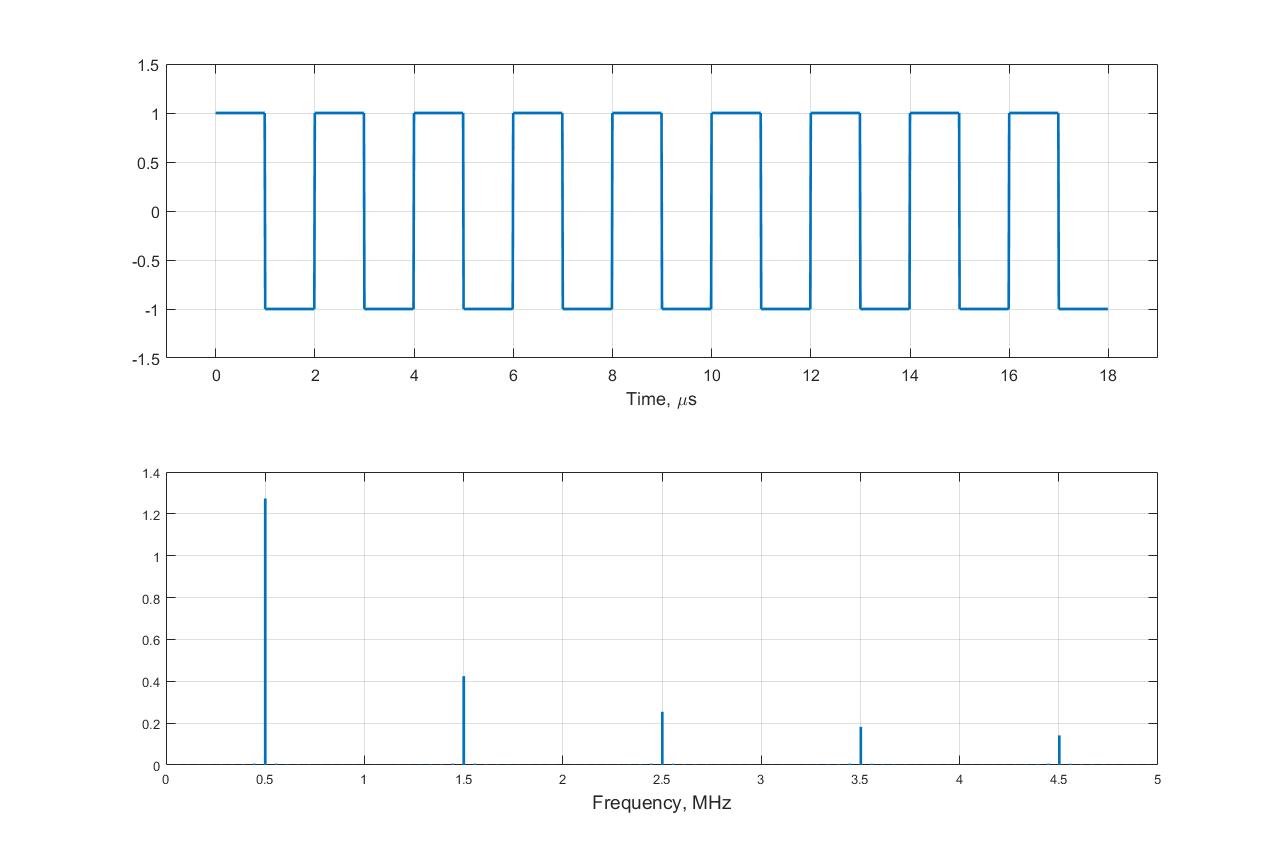

الأول جاء لوحة DE10-Nano. سارة ، لكنها غريبة بعض الشيء: توقعوا أن تجتمع الألواح معًا. بعد بضعة أيام ، تأتي مكالمة من الجمارك: جاءت الرسوم ، وكلها معًا تتجاوز حد السعر ، لذلك تحتاج إلى دفع مبلغ تخليص جمركي يساوي تقريبًا تكلفة هذه الرسوم. مثل هذا الموقف أزعجنا ، لكنه لم يناسبنا: رفضنا المجالس. لم يكن لدينا خلاطات ومولدات ، نحن بحاجة إلى إيجاد حلول جديدة. ماذا تفعل؟ لم يكن أول ما يتبادر إلى الذهن هو الحل الأكثر دقة ، بل هو الحل غير المعتاد: استخدم ساق GPIO المعتادة وتولد متعرجًا منه. يتم تثبيت مرشح التمرير المنخفض التمثيلي عند إخراج هذه القدم مع نطاق قطع أكبر قليلاً من الحد الأقصى لتردد التعرج. بالنسبة للمبتدئين ، تم اقتراح تضمين تحليل من 1 ميجاهرتز (على سبيل المثال): ثم بعد المرشح سنحصل على جيب نقى أكثر أو أقل (سيتم قطع أعلى التوافقيات بواسطة المرشح) ، وهكذا حتى ينخفض التردد إلى الإشارة التي بعدها المرشح سيكون هناك توافقيتان. التعرج هو مجموع التوافقيات الفردية ، والمساهمة النسبية لكل توافقي معروفة مسبقًا [3].

مثال للتعرج في نطاقات الوقت والتردد: تظهر مكونات الإشارة التوافقية عند 500 كيلوهرتز و 1.5 ميجاهرتز وما إلى ذلك على الطيف.

مثال للتعرج في نطاقات الوقت والتردد: تظهر مكونات الإشارة التوافقية عند 500 كيلوهرتز و 1.5 ميجاهرتز وما إلى ذلك على الطيف.مع مرشح بتردد قطع 1 ميغا هرتز ، يمكنك النزول إلى 33. (3) كيلو هرتز. بعد هذا التردد ، يجب أن نحصل على مجموع جيبين خلف الفلتر. النسبة النسبية لاتساعها معروفة (دالة صادقة) ، واستجابة الجهاز المقاس لتردد 1 ميجاهرتز (أول توافقي فردي) أيضًا ، لذا نحتاج إلى إنشاء معادلة بمجهول واحد وحساب خاصية الاستجابة لتردد 33 ، (3) كيلو هرتز! في البداية ، بدا هذا الحل بسيطًا جدًا ، لذلك تم إخبار المبتدئين للجميع على أمل أن يجد شخص خطأ. لم يتم العثور على أخطاء ، ولكن تم اكتشاف عدد من القيود مع تقدم المناقشة:

- قدم GPIO ليس أفضل مصدر للتعرج ، خاصة مع زيادة التردد ؛

- سيكون لحام مرشح مضغوط على المكونات المتاحة مهمة غير تافهة ؛

- حتى إذا كان من الممكن التحايل على هذه القيود ، تنشأ مشكلة التزامن لاكتشاف المرحلة.

لنفترض أننا حللنا جميع المشكلات في الجانب التناظري ؛ برمجياً ، ينشأ اثنان آخران:

- مع تناقص التردد ، سيساهم خطأ كل كشف وحساب سابق في القياس اللاحق ؛

- مع تناقص التردد ، سيزداد الوقت اللازم لحساب الخصائص بشكل ملحوظ.

وأخيرًا وليس آخرًا. يمكن استخدام الدائرة الموصوفة إذا كان يمكن وصف العنصر المقاس بواسطة وظيفة النقل الخطي. ومع ذلك ، إذا قمنا بقياس صندوق أسود بخصائص غير خطية - فإن الفكرة لديها مشاكل أكثر من جيدة. لم يكن هناك الكثير من الوقت المتبقي (يجب أن تظهر النتيجة الأولى بعد شهرين من وصول اللوحة) ، لذلك ، بعد بعض المداولات ، قررنا التحقق مرة أخرى من إمداداتنا مقابل لوحات التصحيح الحالية - ووجدنا

DAC 14 بت في 125 Msps ! ليس الحل الأكثر أناقة ، ولكن لا يوجد خيار ، نستخدمه كمولد إشارة خرج.

المفهوم الأول

يتلقى DAC المحدد كمولد بيانات عند إدخال الناقل المتوازي ويقوم بإغلاقها بإشارة ساعة قادمة من FPGA. هذه الدائرة مثالية للتزامن في دائرتنا. ومع ذلك ، بقيت الأسئلة مع الكشف.

نعم ، على نفس اللوحة يوجد ADC 14 بت بسرعة 65 msps. لكن إمكانيات المولد فقط هي التي يحتمل أن تكون أعلى ، ووفقًا لنظرية Kotelnikov ، لن يعمل هذا ADC بعد ذلك عند أقصى ترددات.

تم العثور على الحل أثناء مناقشة هذه المشكلة مع مهندسي الإلكترونيات ذوي الخبرة. اتضح أنه بالنسبة لمهمتنا ، يمكننا استخدام دائرة مضخم قفل: إخراج مثل هذا الكاشف هو قيمتان ثابتتان ، مكونات طورية وتربيعية ، يمكنك من خلالها الحصول على اتساع وطور الإشارة ، وبما أنها ثابتة ، يمكن اكتشافها حتى مع تثبيت ADC البطيء على DE10-Nano! تقرر أولاً وضع نموذج للدائرة في LTSpice ، وعندها فقط حدد المكونات وتجميع الدائرة ، مع الأخذ في الاعتبار أن إدخال الكاشف هو إشارة من المروج ، وأن المخرجات متصلة بـ ADC على لوحة DE10-Nano.

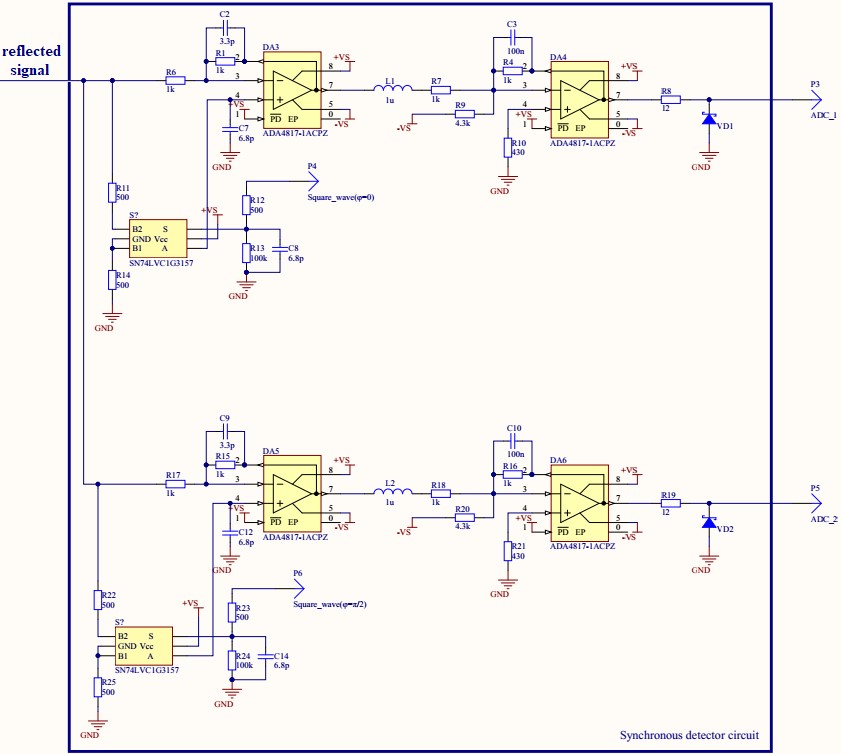

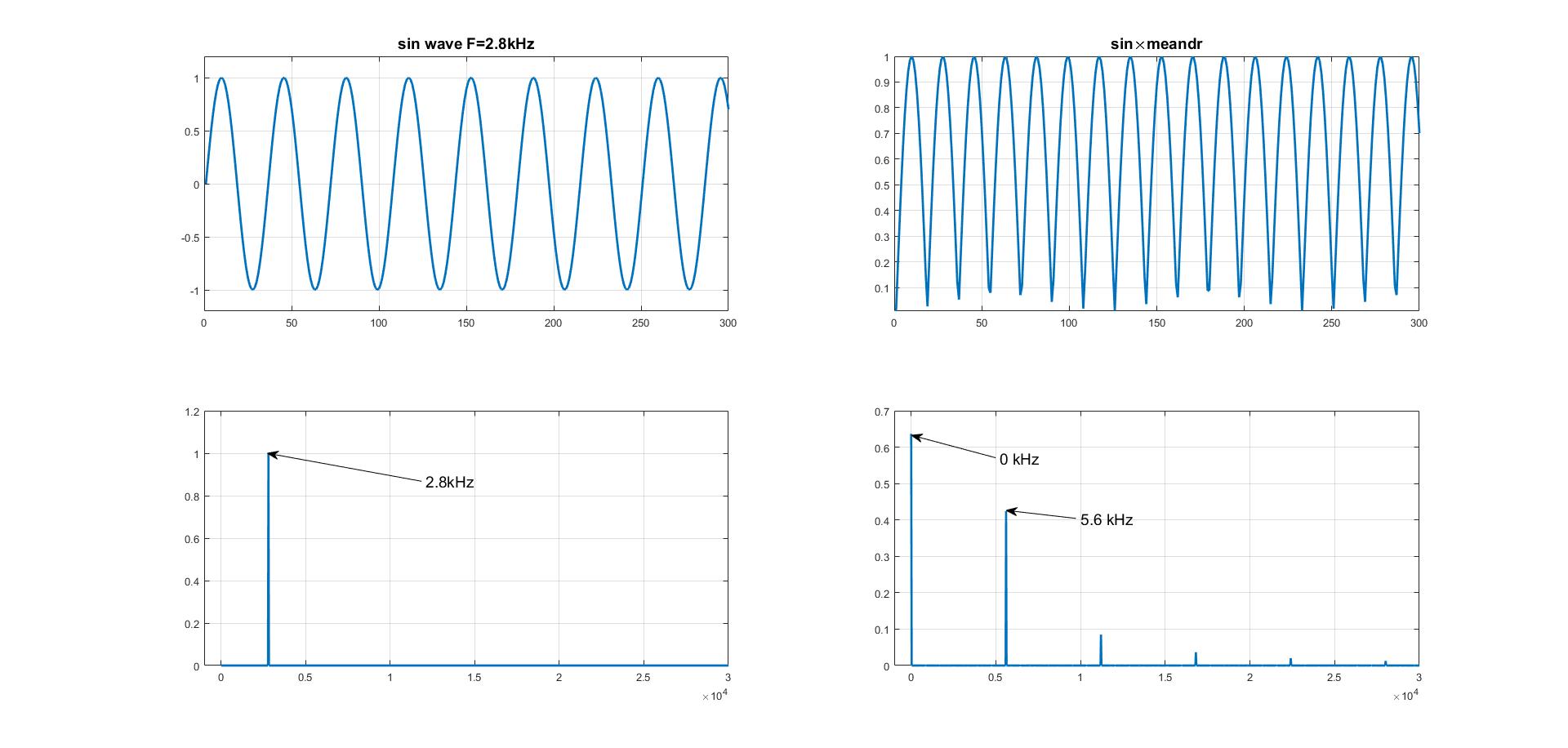

حول الكاشف المتزامن والمروركما يستخدم كاشف متزامن في معالجة الإشارات الرقمية للكشف عن إشارات مختلفة على خلفية الضوضاء. تتمتع زيورخ إنسترومنتس بوصف جيد [4] ، في حالتنا يكون الكشف كما يلي: يتم ضرب الإشارة المنعكسة للتردد المعروف بواسطة التعرج باستخدام مفتاح عالي التردد ومكبر للصوت:

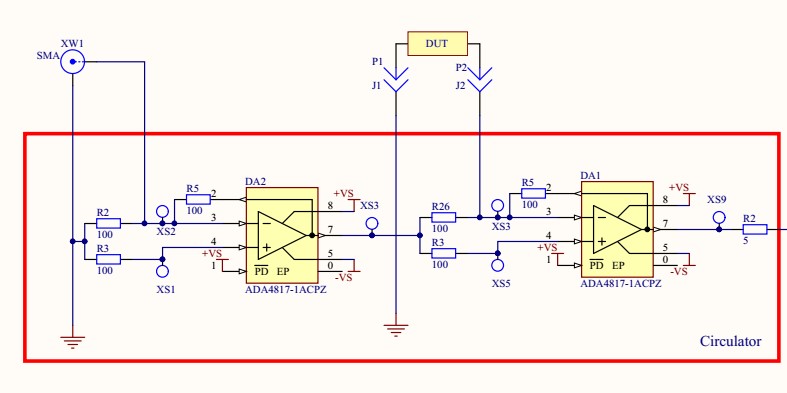

دائرة كشف الانعكاس

دائرة كشف الانعكاسفي الواقع ، يتم تنفيذ الضرب كتبديل وضع التشغيل لمكبر الصوت التشغيلي ، ويتم التحكم في التبديل بواسطة اثنين من المتعرجات القادمة من لوحة DE10-Nano: أحدهما في المرحلة مع الإشارة الأصلية (المستقبلة عند إدخال الجهاز) ، والآخر مع تأخير طور 90 درجة.

نتيجة الضرب هي نقل الإشارة المفيدة إلى مكون التيار المستمر ، ولم تعد جميع الترددات المذكورة أعلاه مثيرة للاهتمام وبالتالي يمكن تصفيتها:

طيف الإشارة قبل وبعد الضرب: عند خرج مضخم التشغيل ، يمكنك تجميع مرشح بسيط بتمرير منخفض لعزل مكون التيار المستمر فقط

طيف الإشارة قبل وبعد الضرب: عند خرج مضخم التشغيل ، يمكنك تجميع مرشح بسيط بتمرير منخفض لعزل مكون التيار المستمر فقطدارة على مضخمات تشغيل (أمبير أمبير) هي دائرة اتصال سلسلة من مكبرات الصوت التشغيلية المغلقة في حلقة. تُستخدم دوارات OA للعديد من الأغراض ، على وجه الخصوص ، لضبط الهوائيات ومكبرات الصوت والمولدات وشبكة جيجابت إيثرنت وما إلى ذلك. في نطاق التردد يصل إلى مئات ميغاهيرتز. عند إنشاء VAC ، تم استخدام دائرة دائرية تم إنشاؤها على أساس مضخمين تشغيليين [5].

مخطط الدائرة لتوصيل الجهاز المقاس

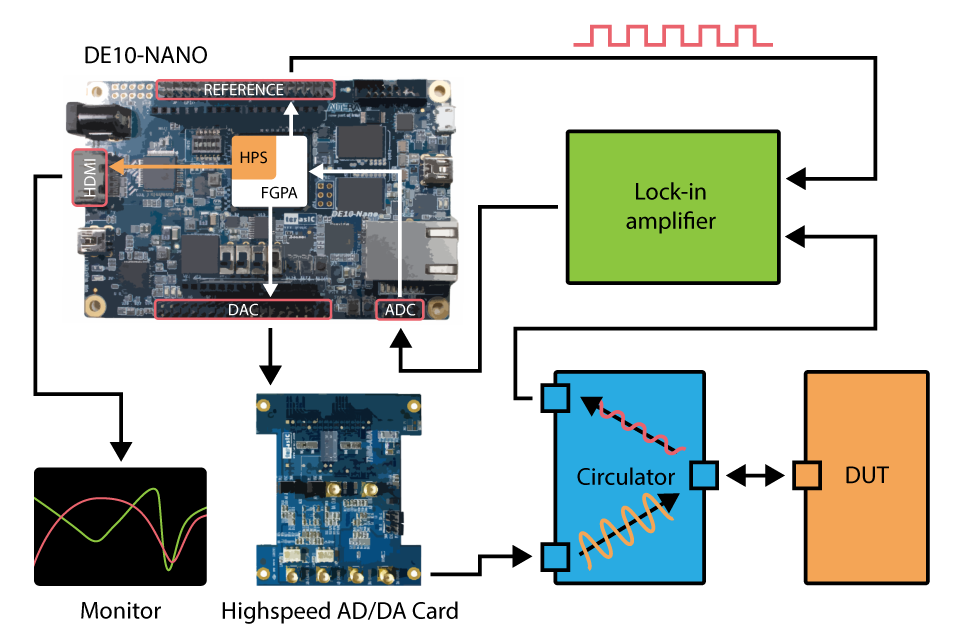

مخطط الدائرة لتوصيل الجهاز المقاس  مفهوم المشروع المحدث

مفهوم المشروع المحدثتم تغذية الإشارات الجيبية بتردد من 1 هرتز إلى 1 ميجاهرتز مع خطوات تم ضبطها على بضع هرتز إلى المنفذ الأول للدوران. تم توصيل الجهاز المدروس بالمنفذ الثاني ، اعتمادًا على استجابة التردد التي تغير فيها معامل الانعكاس للإشارة. تم تغذية الإشارة المنعكسة إلى المنفذ 3 ، حيث تم تجميع دائرة كاشف متزامن لتحديد خصائص التردد والطور. للتشغيل الصحيح ، تم مطابقة منافذ المروج مع مقاومة 100 أوم ، والتي ارتبطت بمقاومة خرج DAC واختيار الأجهزة قيد الدراسة.

تم ترك أقل من شهر قبل اكتمال المشروع ، وبحلول نهاية الموعد النهائي ، كان من الضروري إعداد مواد الإبلاغ: وصف تفصيلي للمشروع على صفحة المسابقة ، ومشروع منشور على GitHub في المجال العام وتقرير فيديو عن العمل المنجز.

نظرًا لأننا نفهم الآن البيانات التي ستدخل في المدخلات والمخرجات ، فقد بدأنا العمل في مشروع لـ SoC FPGA. رأينا المشروع قيد التنفيذ على النحو التالي: يقوم المستخدم بتعيين نطاق التردد الذي يتم التخطيط للقياس فيه ، ويبدأ FPGA في إنشاء التوافقيات في فاصل زمني محدد بدوره باستخدام DAC ، يتلقى ADC التربيع ومكونات الطور عند الإدخال ، وتحويلها إلى قيم السعة والطور عند التردد الحالي ، يتم عرض القيم التي تم الحصول عليها في الوقت الحقيقي على الشاشة المتصلة بلوحة التصحيح. كانت هناك بالفعل إنجازات في عرض المعلومات على الشاشة ، لذلك كان الجزء الرئيسي هو العرض الصحيح للبيانات في الوقت الحقيقي وإخراج الصورة إلى HDMI. نحن غير مجمعين. تولت المجموعة الأولى المهام في البرنامج للمعالج ، لفهم المزيد من التهيئة اللازمة ، والأسئلة حول تصور البيانات. طلبنا منهم أيضًا رفع دقة الشاشة إلى 1024 × 768 [6]. تركت المجموعة الثانية تفاصيل حول تنفيذ الجزء على FPGA ، والذي يجب بعد ذلك تزويده بالمعالج عبر ناقل الواجهة lightweight_h2f ، بالإضافة إلى اختبار تشغيل أول كاشف متزامن للنموذج الأولي. بعد إزالة أوجه القصور وقياس خصائص العديد من العناصر بنجاح ، لم يكن هناك الكثير من الوقت المتبقي ، لذلك تم تخصيص اليومين التاليين لربط الأنظمة معًا ، وإضافة التقارير وتحرير الفيديو.

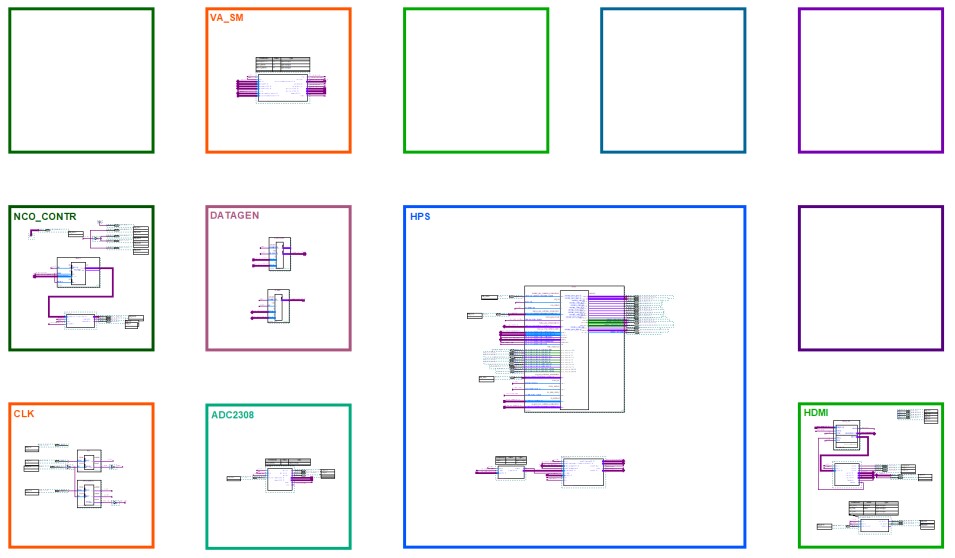

ظهور ملف المستوى الأعلى في Quartus II

ظهور ملف المستوى الأعلى في Quartus IIالدقائق الأخيرة

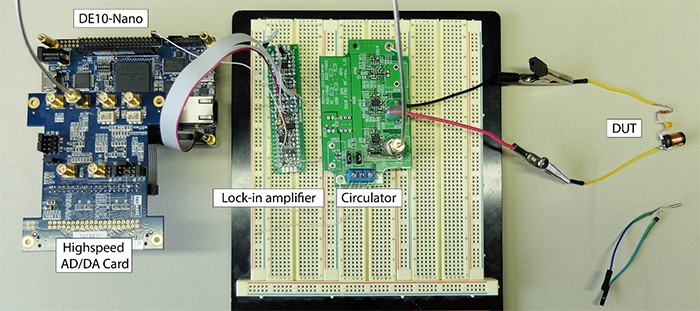

بعد قضاء أكثر من يومين في المختبر ، قمنا بتجميع النظام بأكمله. لم يعمل هذا النطاق لكامل نطاق التردد المحتمل ، وقام بقياس المعلمة S11 فقط وعكس خصائص الطور والسعة المقاسة للجهاز المتصل على الشاشة. لا يزال الجهاز الذي تم تجميعه خارجيًا لا يبدو جذابًا للغاية - ثلاث لوحات منفصلة متصلة بأسلاك أحادية النواة ، ولكن هذا نموذج أولي

يعمل ، ويمكنك وضع marafet في المرحلة التالية. كتبنا النص ، وضحنا مراحل التنفيذ ، صوّرنا مقطع فيديو ، تم تحميله جميعًا على الموقع وبدأنا في الانتظار.

بالطبع ، أرسلنا بعض الأصدقاء إلى هذه المواد لإضافة طرق عرض قليلاً. ومع ذلك ، في يوم واحد ، بدأت الآراء تنمو بنفسها ، كما لو أن شخصًا ما قد دمج هذا في الترويج. بعد قليل من التحليل اتضح: تم ملاحظة مشروعنا على hackaday.io [7] وكانت الغالبية العظمى من الآراء من هناك. كان من المثير للاهتمام رؤية الردود الأولى على مشروعنا. مستوحاة ، بدأنا ننتظر النتائج.

ومع ذلك

هذه ليست السنة الأولى من مشاركتنا في المسابقة. كان هذا المشروع بالنسبة لنا الأكثر تفكيرًا بين عمل الطلاب الذي تم تنفيذه سابقًا. لكنها لم تنمو معًا: لم نذهب إلى المرحلة التالية. ربما يرجع ذلك إلى سوء تفاهم بيننا وبين القضاة. ربما لا يدخل المشروع ببساطة مجال الاتجاهات الحالية لـ FPGAs (التشفير والحوسبة المتوازية والشبكات العصبية وما إلى ذلك). لكن بالنسبة لنا ، هذه خطوة كبيرة في تطوير SoC FPGA ، وهو فرع جديد من التطوير ، والأهم من ذلك ، الخبرة.

ملاحظة

مبروك للممثلين الروس الذين احتلوا المركز الثاني في نهائي المسابقة!

أشكر زملائي في المشروع Danila Nikiforovsky و

Yevgeny Vostrikov والقادة

Ivan Deineku و

Philipp Shuklin و Artem Aleinik على مشاركتهم النشطة ودعمهم.

المراجع

[1] مسابقة Innovate Europe 2015

www.innovateeurope.org/eu/2015winner.html[2] دليل المهندس للاختبار الآلي للواجهة عالية السرعة ، خوسيه موريرا ، هوبرت ويكمان ، 2010 ، الملحق و ص .503

[3] طيف تسلسل دوري من النبضات المستطيلة ،

en.dsplib.org/content/fourier_series_pimp/fourier_series_pimp.html[4] مبادئ اكتشاف

التعلق وحالة الفن ، أدوات زيورخ

www.zhinst.com/applications/principles-of-lock-in-detection[5]

المروج / العازل منخفض التردد بدون الفريت والمغناطيس

www.cqham.ru/oth9.htm[6] مشروع VAC للوحة DE10-Nano github.com/tvShushtov/em078_vector_analyzer

[7] مقال عن مركز طلبات التأشيرة على Hackaday

hackaday.com/2018/05/09/vector-network-analyzer-uses-soc-fpga