قامت Intel بتطوير شريحة 8087 في عام 1980 من أجل تحسين أداء أجهزة الكمبيوتر باستخدام معالجات خط 8086/8088 (مثل IBM PC) عند تنفيذ عمليات النقطة العائمة. منذ أن تم تصميم المعالجات الدقيقة الأولى لإجراء العمليات بأعداد صحيحة ، كان تنفيذ العمليات بأرقام الفاصلة العائمة بطيئًا ، أي عن أداء العمليات التجاوزية ، مثل الدوال المثلثية أو اللوغاريتمات. زاد المعالج 8087 بشكل كبير من سرعة تنفيذ مهام النقطة العائمة ؛ تم تنفيذ كل شيء أسرع 100 مرة تقريبًا. كما تم تنفيذ بنية 8087 في معالجات Intel اللاحقة ، ولا تزال تعليمات 8087 مستخدمة في أجهزة الكمبيوتر الحديثة x86. طرحت إنتل شريحة 8087 في عام 1980 ، المصممة لتحسين أداء حوسبة النقطة العائمة على معالجات 8086 و 8088.

نظرًا لأن المعالجات الدقيقة المبكرة عملت فقط مع الأعداد الصحيحة ، كانت عملية حساب الفاصلة العائمة بطيئة ، وبدت العمليات المتعالية مثل المحفزات أو اللوغاريتمات أسوأ. سمحت لنا إضافة 8087 معالج رياضي للنظام إلى تسريع عمليات الفاصلة العائمة بمقدار 100 مرة. أصبحت هندسة 8087 جزءًا من معالجات Intel اللاحقة ، ولا تزال تعليمات 8087 (على الرغم من أنها قديمة) جزءًا من أجهزة كمبيوتر سطح المكتب x86 الحديثة.

قدمت شريحة 8087 عملية حسابية سريعة للكمبيوتر الشخصي IBM الأصلي وأصبحت جزءًا من بنية x86 المستخدمة اليوم. واحدة من الميزات غير المعتادة في 8087 هي ROM متعدد المستويات (ذاكرة للقراءة فقط) ، قادرة على تخزين بتتين لكل ترانزستور ، وهو ضعف كثافة ROM التقليدية. بدلاً من تخزين البيانات الثنائية ، حفظت كل خلية في 8087 ROM واحدة من أربع قيم مختلفة ، والتي تم فك شفرتها بعد ذلك إلى بتتين. نظرًا لأن 8087 بحاجة إلى كمية كبيرة من ROM للرمز الصغير (1) ، وكان عدد الترانزستورات على الشريحة محدودًا جدًا ، استخدمت Intel تقنية غير عادية لحل المشكلة. في هذه المقالة ، سأشرح كيف نفذت Intel هذه ROM ذات الطبقات.

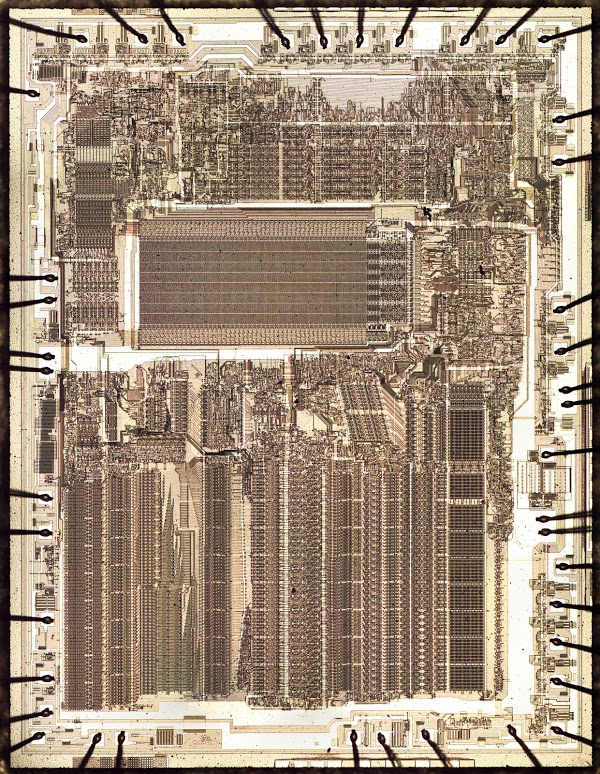

فتحت شريحة 8087 وتصويرها بمجهر ، والحصول على الصورة أدناه. في الصورة ، أشرت إلى الكتل الوظيفية الرئيسية بناءً على الهندسة العكسية الخاصة بي (انقر لتكبير الصورة). مصفوفة المعالج 8087 معقدة للغاية ، مع 40000 ترانزستور (2). يستخدم 8087 أرقام فاصلة عائمة 80 بت: تم حجز 64 بت للعشري ، و 15 بت للأسي ، وبت آخر موقّع. (مثال على رقم بقاعدة 10: من 6.02 × 1023 ، 6.02 هو العشري و 23 هو الأس). في الجزء السفلي من الصورة ، تشير كلمة "معالجة جزء" إلى جزء من مخطط الجزء العشري. من اليسار إلى اليمين ، يشمل ذلك: التخزين المستمر ، وتحويل 64 بت ، وأداة طرح / طرح 64 بت ، ومكدس التسجيل. أعلى بقليل هو مخطط معالجة الأس.

رقاقة معالج رياضي لعمليات إنتل 8087 النقطة العائمة ، مع تعيين الكتل الوظيفية الرئيسيةيتطلب تنفيذ التعليمات على 8087 عدة خطوات ، وفي بعض الحالات أكثر من 1000. يستخدم البرنامج الثابت 8087 الرمز الصغير لتحديد العمليات ذات المستوى المنخفض في كل خطوة: التحولات ، الزيادة ، عينات الذاكرة ، ثوابت القراءة ، إلخ. يمكنك رؤية الرمز الصغير كبرنامج بسيط ، مكتوبة في شكل أوامر صغيرة ، حيث يولد كل أمر متحكم إشارات تحكم للعديد من مكونات الشريحة. تظهر الصورة أعلاه ROM مع برنامج الرمز الصغير 8087. يشغل ROM جزءًا كبيرًا من الشريحة ، مما يوضح بوضوح سبب ضرورة وجود ROM مدمج متعدد المستويات. على يسار ROM هو "المحرك" الذي تم تشغيل برنامج الرمز الصغير عليه ، في الواقع ، معالج بسيط.

يعمل 8087 كمعالج مشترك مع المعالج 8086. عندما اكتشف 8086 تعليمات خاصة بفاصلة عائمة ، تجاهلها المعالج وسمح لـ 8087 بتنفيذ التعليمات بالتوازي. لن أشرح بالتفصيل العمل الداخلي لـ 8087 ، ولكن باختصار ، تم تنفيذ عمليات الفاصلة العائمة باستخدام عمليات الجمع / الطرح والتحويل الصحيحة. لإضافة أو طرح رقمين للفاصلة العائمة ، أجرى 8087 تحولًا بتًا في الرقم حتى المحددات الثنائية (أي أن الفاصل العشري هو فاصلة ، ولكن في النظام الثنائي) متساوية ، ثم تمت إضافتها أو طرحها. تم إجراء الضرب والقسمة والجذر التربيعي من خلال التحولات المتكررة أو الإضافات أو الطرح. استخدمت العمليات التجاوزية (tan ، arctan ، log ، power) خوارزميات CORDIC ، والتي تستخدم التحولات وإضافة ثوابت خاصة ، تتم معالجتها واحدة تلو الأخرى. واجه 8087 أيضًا العديد من الحالات الخاصة: اللانهاية ، والفيضان ، NaN (ليس رقمًا) ، والأرقام غير المنسقة ، والعديد من أوضاع التقريب. سيطر الرمز الصغير المخزن في ROM على كل هذه العمليات.

تنفيذ ROM

تتكون شريحة 8087 من مصفوفة سليكونية صغيرة يغطى بها السيليكون مع شوائب في أماكن للحصول على خصائص أشباه الموصلات المطلوبة. يتم تطبيق البولي سيليكون (نوع خاص من السيليكون) على سطح السيليكون ، الذي يشكل الأسلاك والترانزستورات. وأخيرًا ، تكمل طبقة معدنية أعلى السيليكون الدائرة الكهربائية العاملة. في الصورة أدناه ، على الجانب الأيسر ، يظهر جزء صغير من الرقاقة ، حيث يمكن رؤيته تحت المجهر ، ويظهر أسلاك معدنية صفراء. على الجانب الأيمن من الصورة ، تمت إزالة المعدن بالحمض ، مما أدى إلى تعريض البولي سيليكون والسيليكون. عندما يعبر السليكون السيليكون ، يتم تشكيل الترانزستور. المناطق الوردية هي سيليكون مخدر ، والخطوط العمودية الرقيقة هي سيليكون. الدوائر الصغيرة هي نقاط الاتصال بين طبقات السيليكون والمعدن ، وربطها ببعضها البعض.

هيكل ROM في Intel 8087 FPU. تظهر الطبقة المعدنية على اليسار ، والبولي سيليكون والسيليكون على اليمين.على الرغم من وجود العديد من الطرق لبناء ROMs ، فإن الطريقة القياسية هي إنشاء شبكة من "الخلايا" حيث تقوم كل خلية بتخزين بت واحد. قد تحتوي كل خلية على ترانزستور (مما يعني 0 بت) أو لا تحتوي على ترانزستور ، مما يعني 1 بت. في الصورة أعلاه ، يمكنك رؤية شبكة من الخلايا ذات الترانزستورات (حيث يتم تطبيق البولي سيليكون على السيليكون) والترانزستورات المفقودة (حيث توجد فجوات في السيليكون). لقراءة المعلومات من ROM ، يتم تنشيط خط اختيار عمود واحد (بناءً على العنوان) لتحديد البتات المخزنة في هذا العمود والحصول على بت واحد من كل صف عند الإخراج. يمكنك رؤية خطوط اختيار العمود الرأسي (خطوط تحديد العمود) من البولي سيليكون ، والصفوف المعدنية الأفقية في الصورة أعلاه. الخطوط العمودية للسيليكون المخدر مؤرضة.

يوضح الرسم البياني أدناه (المقابل لقطاع ROM 4x4) كيفية عمل ROM. تحتوي كل خلية إما على ترانزستور (أسود) ، أو ليس لديها ترانزستور (رمادي اللون). عندما يتم تطبيق الجهد على خط اختيار عمود البولي سيليكون ، يتم تشغيل الترانزستورات في هذا العمود وتأريض الصفوف المعدنية المقابلة. (في هذه الحالة ، يشبه ترانزستور NMOS بوابة مفتوحة إذا كان المدخل 0 ، ومغلقًا إذا كان المدخل 1). تخرج "الصفوف" المعدنية للدائرة البيانات المخزنة في "العمود" المحدد.

مخطط ROM 4 × 4يتم إنشاء إشارات اختيار العمود بواسطة دائرة وحدة فك الترميز. بما أن هذه الدائرة مبنية من صمامات NOR ، فسأشرح أولاً تصميم الصمامات. يوضح الرسم البياني أدناه بوابة NOR بأربعة مدخلات مبنية من أربعة ترانزستورات ومقاوم سحب (على الرغم من أن الترانزستور الخاص يؤدي في الواقع وظيفة المقاوم). على الجانب الأيسر من الدائرة ، تكون جميع المدخلات 0 ، لذلك يتم إيقاف تشغيل جميع الترانزستورات ، ويحتفظ مقاوم السحب لأعلى بإشارة الخرج عند مستوى "مرتفع". على الجانب الأيمن ، تم تطبيق 1 على أحد المدخلات ، وتشغيل الترانزستور. يكون الترانزستور مؤرضًا ، لذا فإن إشارة الخرج أصبحت الآن "منخفضة". وبالتالي ، إذا كانت أي مدخلات عالية (1) ، فإن الناتج منخفض (0). لذا فإن هذه الدائرة تنفذ صمام NOR.

بوابة NOR بأربعة اتجاهات مبنية من ترانزستورات NMOSتستقبل دائرة وحدة فك ترميز العمود اختيار بتات العنوان الواردة وتنشيط خط التحديد المقابل. يحتوي مفكك التشفير على بوابة NOR ذات 8 مدخلات لكل عمود ، أي بوابة NOR واحدة لكل عنوان. تُظهر الصورة عنصرين NOR اللذين يولدان إشارات اختيار العمود (من أجل البساطة ، سأعرض فقط أربعة من المدخلات 8). يستخدم كل عمود مجموعة مختلفة من أسطر العنوان وخطوط العناوين المبطنة كمدخل ، واختيار عنوان مختلف. خطوط العنوان في طبقة معدنية ، والتي تتم إزالتها في الصورة أدناه ؛ يتم تمييز خطوط العنوان باللون الأخضر. لتحديد العنوان المرتبط بالعمود ، انظر إلى الدبابيس المربعة المرتبطة بكل ترانزستور ولاحظ خطوط العنوان المتصلة. إذا كانت جميع خطوط العنوان المتصلة بالترانزستورات في العمود عند مستوى منخفض (0) ، فستختار بوابة NOR هذا العمود.

جزء من وحدة فك ترميز العنوان. يختار مفكك تشفير العنوان الأعمدة الفردية في ROM ، ويتم العد من اليمين إلى اليسار. توضح الأرقام في الأعلى العنوان المرتبط بكل ناتج.تظهر الصورة أدناه جزءًا صغيرًا من وحدة فك ترميز ROM مع جميع المدخلات 8 لبوابات NOR. يمكنك قراءة العناوين الثنائية من خلال فحص الروابط في شريط العناوين بعناية. لاحظ النمط الثنائي: ينضم a1 إلى قيم التغيير في كل عمود ، وينضم a2 إلى البديل كل عمودين ، وينضم a3 إلى كل أربعة أعمدة ، وما إلى ذلك. يتم إصلاح A0 لأن دائرة فك الشفرة هذه تحدد الأعمدة الفردية ؛ تقوم دائرة ROM مماثلة بتحديد العناوين الزوجية (كان مثل هذا الفصل ضروريًا لفك الشفرة على الشريحة ، حيث أن كل عمود من وحدات فك الشفرة يبلغ عرضه ضعف خلية ROM).

جزء من وحدة فك ترميز العناوين لرمز ROM الصغير 8087. يقوم مفكك الشفرة بتحويل عنوان 8 بت إلى إشارات اختيار العمودالمكون الأخير من ROM هو مجموعة من معددات الإرسال التي تقلل من 64 خط إنتاج إلى 8 خطوط. يختار كل معدد 8 إلى 1 أحد إدخالاته الثمانية بناءً على العنوان. يوضح الرسم البياني أدناه أحد معددات خط المعالجات 8087 ، وهي مبنية من ثمانية ترانزستورات كبيرة تمر كل منها متصلة بأحد خطوط "الخط". ترتبط جميع الترانزستورات بالخرج ، لذلك عندما يتم تشغيل الترانزستور المحدد ، فإنه ينقل مدخلاته إلى الإخراج. إن الترانزستورات المتعددة الإرسال أكبر بكثير من الترانزستورات في ROM لتقليل تشوه إشارة ROM. يولد مفكك التشفير (مشابه لما سبق ذكره ، ولكنه أصغر) ثمانية خطوط تحكم معدد إرسال من ثلاثة أسطر عناوين.

أحد معددات الصف 8 في ROM. هنا يمكنك أن ترى طبقات من السيليكون (بولي) ، مع مركبات معدنية مطلية باللون البرتقاليللتلخيص ، يخزن ROM البتات في الشبكة. يستخدم ثمانية بتات العنوان لتحديد عمود في الشبكة. ثم حدد ثلاثة بتات من العنوان المخرجات الثمانية المطلوبة من "السطور".

ROM متعدد الطبقات

حتى الآن ، قمت بشرح جهاز ROM نموذجي يقوم بتخزين بت واحد لكل خلية. إذن كيف تمكنت 8087 من تخزين بتتين لكل خلية؟ إذا نظرت بعناية ، يحتوي الرمز الصغير 8087 ROM على أربعة أحجام مختلفة من الترانزستورات - إذا كنت تفكر في عدم وجود ترانزستور كأحد الأحجام (6). مع أربعة خيارات لكل ترانزستور ، يمكن لخلية واحدة ترميز بتتين ، مما يضاعف الكثافة تقريبًا (7). يشرح القسم الحالي كيف تولد الأحجام الأربعة للترانزستورات أربعة تيارات مختلفة ، وكيف تحول الدوائر التناظرية والرقمية للرقاقة هذه التيارات إلى بتين.

يُظهر رسم مصغر للرمز الصغير ROM 8087 أربعة أحجام مختلفة من الترانزستورات. هذا يسمح لـ ROM بتخزين بتتين لكل خلية.يتحكم حجم الترانزستور في التيار من خلال الترانزستور (8). عامل هندسي مهم هو العروض المختلفة للسيليكون (الوردي) ، حيث يتقاطع مع البولي سيليكون (خطوط عمودية) ، مما يخلق ترانزستورات بعرض بوابة مختلفة. نظرًا لأن عرض البوابة يتحكم في التيار من خلال الترانزستور ، فإن الأحجام الأربعة للترانزستور تولد أربعة تيارات مختلفة: يمر الترانزستور الأكبر بمعظم التيار ، ولا يتدفق تيار على الإطلاق إذا لم يكن هناك ترانزستور.

يتم تحويل التيار ROM إلى بت في بضع خطوات. أولاً ، يقوم المقاوم للسحب بتحويل التيار إلى جهد. ثم ، يقارن ثلاثة مقارنات الجهد مع الجهد المرجعي لتوليد إشارات رقمية ، وتحديد الجهد العالي / المنخفض. أخيرًا ، تقوم البوابات المنطقية بتحويل إشارات الإخراج من المقارنة إلى بتين خرج. يتكرر هذا النمط ثماني مرات ، مما يولد ما مجموعه 16 بت عند الإخراج.

مخطط لقراءة بتين من خلية ROMالرسم البياني أعلاه ينفذ خطوات التحويل هذه. ونتيجة لذلك ، يتم اختيار أحد الترانزستورات ROM بواسطة خط اختيار "العمود" والمضاعف (الذي تمت مناقشته سابقًا) الذي يولد أحد التيارات الأربعة. بعد ذلك ، يقوم مقاوم سحب (12) بتحويل تيار الترانزستور إلى جهد ، ونتيجة لذلك يعتمد الجهد على حجم الترانزستور المحدد. يقارن المقارنون هذا الجهد مع ثلاث فولتات مرجعية ، ويخرجون 1 إذا كان جهد ROM أعلى من الجهد المرجعي. تتطلب المقارنات والجهد المرجعي تصميمًا دقيقًا ، حيث يمكن أن تختلف الفولتية بمقدار 200 مللي فولت فقط.

تقع الفولتية المرجعية في الوسط بين قيم الجهد المتوقعة في ROM ، والتي تسمح ببعض تقلبات الجهد. يكون جهد ROM "المنخفض" أقل من جميع الفولتية المرجعية ، لذلك ستخرج جميع المقارنات 0. جهد ROM الثاني أعلى من المرجع 0 ، وبالتالي فإن مخرجات المقارنة المنخفضة 1. في جهد ROM الثالث ، يخرج المقارنان السفليان 1 ، وعلى الأكثر جهد ROM عند خرج جميع المقارنات الثلاثة 1. وبالتالي ، فإن المقارنات الثلاثة تنتج أربعة أنماط إخراج مختلفة ، اعتمادًا على ROM الترانزستور. ثم تقوم العناصر المنطقية بتحويل ناتج المقارنة إلى بتين إخراج (10).

تصميم المقارن مثير للاهتمام لأنه جسر بين العالمين التناظري والرقمي ، ينتج 1 أو 0 إذا كان جهد ROM أعلى أو أقل من الجهد المرجعي. يحتوي كل جهاز للمقارنة على مضخم تفاضلي يضخم الفرق بين جهد ROM والجهد المرجعي. يدفع خرج مكبر الصوت التفاضلي بوابة تثبت الخرج وتحوله إلى إشارة مستوى منطقي. مكبر الصوت التفاضلي (أدناه) هو دائرة تناظرية قياسية. المصدر الحالي (الرمز أدناه) يوفر التيار المباشر. إذا كان أحد الترانزستورات لديه جهد دخل أعلى من الآخر ، فإن معظم التيار يمر عبر هذا الترانزستور. سيؤدي انخفاض الجهد عبر المقاومات إلى انخفاض الناتج المقابل ويصبح الناتج الآخر أعلى.

رسم تخطيطي يوضح تشغيل زوج تفاضلي. سوف يمر معظم التيار عبر ترانزستور بجهد دخل أعلى ، مما يؤدي إلى إشارة خرج أقل. رمز الدائرة المزدوجة أدناه هو مصدر تيار مباشر Iتظهر الصورة أدناه أحد المقارنات على رقاقة. طبقة معدنية في الأعلى ، ترانزستورات تحتها. سأدرس فقط النقاط الرئيسية لهذا المخطط المعقد ؛ انظر الملاحظة 12 للحصول على التفاصيل. يتم توفير إشارة من ROM ومضاعف إلى اليسار. تعمل دائرة السحب 12 على تحويل التيار إلى جهد. يقارن ترانزستورات مضخم تفاضلي كبير الجهد ROM مع الجهد المرجعي (الإدخال من الأعلى). تذهب المخرجات من مكبر الصوت التفاضلي إلى دائرة الغالق (مبعثرة في الصورة) ؛ يكون ناتج الغالق في الزاوية اليمنى السفلية. يتكون المصدر الحالي لمكبر الصوت التفاضلي ومقاومات السحب لأعلى من ترانزستورات وضع الاستنفاد. يتم استخدام ثلاث مقارنات خرج في كل دائرة خرج ، مما يعطي إجمالي 24 مقارنًا.

أحد المقارنات في 8087. تحتوي الشريحة على 24 مقارنًا لتحويل مستويات الجهد من ROM متعدد المستويات إلى البيانات الثنائيةيتم إنشاء كل جهد مرجعي بواسطة ترانزستور من الحجم المحدد بعناية ودائرة سحب لأعلى. تم تصميم الدائرة المرجعية للجهد لتكون قريبة قدر الإمكان من دائرة إشارة ROM ، بحيث تؤثر أي تغييرات في تصنيع الرقائق على كلا العنصرين بشكل متساوٍ. يستخدم الجهد المرجعي وإشارة ROM نفس دائرة الحمل. بالإضافة إلى ذلك ، تحتوي كل دائرة جهد مرجعي مرجعي على ترانزستور كبير جدًا ، مطابق للترانزستور المضاعف ، على الرغم من عدم وجود تعدد إرسال في دائرة الإشارة المرجعية - فقط لضمان "مطابقة" الدوائر. تتطابق دوائر الجهد المرجعي الثلاث باستثناء حجم الترانزستور المرجعي (9).

دائرة تولد ثلاث فولتات مرجعية. أحجام الترانزستورات المرجعية هي بين أحجام الترانزستورات ROM. لم تتم إزالة طبقة الأكسيد بالكامل من هذا الجزء من المصفوفة ، بسبب ظهور الدوامات اللونية في الصورةلتجميع اللغز بأكمله ، توضح الصورة أدناه موقع مكونات الرمز الصغير ROM على الشريحة (12). يتكون الجزء الرئيسي من دارة ROM من ترانزستورات تقوم بتخزين البيانات. تقع دائرة وحدة فك ترميز العمود أعلى وأسفل بيانات ROM. نصف أجهزة فك تشفير اختيار الأعمدة في الأعلى ونصفها في الأسفل للحصول على تخطيط أفضل. دائرة الخرج على اليمين. قطع ثمانية معددات 64 خطًا من الخطوط إلى ثمانية. ثم تدخل ثمانية أسطر من المقارنات ، لتولد 16 بت عند إخراج ROM إلى اليمين. تولد الدائرة المرجعية فوق المقارنات ثلاث فولتات مرجعية. في الجزء السفلي الأيمن ، يتحكم مفكك تشفير خط صغير في معددات الإرسال.

ROM البرامج الثابتة من Intel 8087 FPU المسمى بالمكونات الرئيسيةعلى الرغم من أنه قد يبدو في البداية أن ROM متعدد المستويات سيكون نصف مثل ROM التقليدي ، إلا أن التأثير غير ملحوظ بسبب الدائرة الإضافية للمقارنات ، وبسبب حقيقة أن الترانزستورات نفسها أكبر قليلاً ، بسبب الحاجة إلى استخدام عدة أحجام. على الرغم من ذلك ، وفرت ROM متعددة المستويات حوالي 40 ٪ من المساحة التي ستشغلها ROM العادية.

الآن بعد أن فهمت بنية ROM ، يمكنني ببساطة (ولكن بشكل ممل) قراءة محتويات ROM ، فقط بالنظر إلى حجم كل ترانزستور تحت المجهر. ولكن ، بدون معرفة مجموعة تعليمات الرمز الصغير ، فإن محتويات ROM غير مجدية.

الاستنتاجات

8087 « » . Intel 1981 iAPX 432.11 , 1980- . , - , , , , , , (14).

, , -. - (13). - 4 ( 16 ) , (QLC, quad-level cell). , 1980- , .

, @kenshirriff 8087. RSS-. 8087.

- 8087 1648 ( ), 16 , 26368 . , Intel .

- 8087: Intel , 40 000 , , 45 000. . , , PLA , , «» , . , .

- 8086 8087 ; . , 8087 8086 , 8087. , 8086 , . , 8087 8086 ( 8088), , 8086. , 8086, . 8087 , 8086. , 8086 8087, , . , 8087 , , . 8087 , , . 8087 8087, .

- , , , , , . , ROM, , . , 8 1/8 , 1/8 . , , (, 1 × 16) , . , «» . , Intel ; 1405 512 . , «» - 20 .

- IBM : ( , ), (link). , Xerox Alto, . , . , .

- , Hacker News , 8087 . , , .

- 1980- . Mostek : . , . Intel, ( ), . ( ) . ( ), , . Z-80 «», , , , . , , Z-80 , , , .

- . ( — .) ( , ) , . MOSFET . Wikipedia

- , -. , . , Reference 0 , . , , . : , , , . - , , , .

- : = 00, = 01, = 11, = 10. ; , , . (. «Two Bits Per Cell ROM», Stark).

- Intel iAPX 43203 (1981) , 8087. «The interface processor for the Intel VLSI 432 32 bit computer,» J. Bayliss et al., IEEE J. Solid-State Circuits, vol. SC-16, . 522-530, 1981 . 43203 - iAPX 432. Intel iAPX 432 1975 , «», Intel 1980- . iAPX 432 , Intel 8086 , 1978 . Intel 8086 , x86, iAPX 432 1986 .

- ( «Multiple-Valued ROM Output Circuits») . . (T3, T4, T5) . 4 5 , 3, ( ). ( ) T6, . ().

- - SLC ( single level cell — ), MLC (multi level cell — ), TLC (triple level cell — ) QLC (quad level cell — ). , - , , - .

- «Electronics» «Four-State Cell Doubles ROM Bit Capacity» (. 39, 9 1980 .), Intel, . Intel « » COMPCON (. 209-212, 1981 .). Intel «Multiple-valued ROM output circuits» (Proc. 14th Int. Symp. Multivalue Logic, 1984). , , — « A Survey of Multivalued Memories » («IEEE Transactions on Computers», 1986 ., . 99–106) « A review of multiple-valued memory technology » (IEEE Symposium on Multivalued Logic, 1998).

, . هل تحب مقالاتنا؟ هل تريد رؤية مواد أكثر إثارة للاهتمام؟ ادعمنا عن طريق تقديم طلب أو التوصية به لأصدقائك ،

خصم 30 ٪ لمستخدمي Habr على نظير فريد من خوادم مستوى الدخول التي اخترعناها لك: الحقيقة الكاملة حول VPS (KVM) E5-2650 v4 (6 نوى) 10GB DDR4 240GB SSD 1Gbps من 20 $ أو كيفية تقسيم الخادم؟ (تتوفر الخيارات مع RAID1 و RAID10 ، حتى 24 مركزًا وحتى 40 جيجابايت DDR4).

VPS (KVM) E5-2650 v4 (6 Cores) 10GB DDR4 240GB SSD 1Gbps 1 ,

.

ديل R730xd أرخص مرتين؟ فقط لدينا

2 x Intel Dodeca-Core Xeon E5-2650v4 128GB DDR4 6x480GB SSD 1Gbps 100 TV من 249 دولارًا في هولندا والولايات المتحدة! اقرأ عن

كيفية بناء مبنى البنية التحتية الطبقة باستخدام خوادم Dell R730xd E5-2650 v4 بتكلفة 9000 يورو مقابل سنت واحد؟