يتطلب تصميم الأجهزة الإلكترونية باستخدام وحدات ذاكرة DDR SDRAM السريعة اهتمامًا خاصًا بسلامة الإشارة. يتحدث المقال عن أداة النمذجة الحديثة لحل مثل هذه المشاكل.اليوم ، تم تجهيز جميع الإلكترونيات الحديثة تقريبًا بوحدات ذاكرة. تم تصميم الخوادم وأجهزة الكمبيوتر والهواتف الذكية ووحدات تحكم الألعاب وملاحات GPS ومعظم الأجهزة الأخرى بناءً على المعالجات و FPGA. تتطلب هذه الأجهزة ذاكرة عالية السرعة مع عرض نطاق ترددي كبير للقناة أو ذاكرة ذاكرة ثنائية التردد (DDR). مع كل جيل جديد من DDR SDRAM (ذاكرة ديناميكية متزامنة مع وصول عشوائي وسرعة نقل البيانات المضاعفة) ، يتم تقليل سرعة تبادل البيانات والسعة واستهلاك الذاكرة.

عند تصميم لوحات الدوائر المطبوعة للأجهزة ذات ذاكرة DDR ، يمكن أن تنشأ عدد من الصعوبات ، أحدها مشكلة سلامة الإشارة. تتناول هذه المقالة مشكلات ضمان سلامة الإشارات في الأجهزة التي تستخدم ذاكرة DDR.

ضوضاء وتشويش إشارة البيانات الرقمية

عند استقبال / إرسال إشارة الساعة الخاصة بناقل الذاكرة من وحدة التحكم إلى الدائرة المصغرة ، قد يحدث تداخل مختلف بسبب ارتعاش أجهزة الإرسال والاستقبال وفقدان خطوط النقل والضوضاء والتداخل. كل هذا يؤدي إلى ظهور التشويه وتشويه شكل إشارة الواجهة الرقمية.

يمكن اعتبار أي طاقة غير مرغوب فيها تضاف إلى إشارة مثالية بمثابة ضوضاء. يمكن أن يكون سببه التداخل من الخطوط المجاورة ، وقناة الإرسال سيئة التصميم ، والممانعة غير المتسقة ، وعوامل أخرى تؤدي إلى عدم وضوح جبهة النبض. في حالة عدم وجود ضوضاء ، تكون الإشارة الفعلية مطابقة للأفضل.

أي انحراف عن الشكل الموجي المثالي يؤثر على سلامته. تؤثر انحرافات الوقت (الارتعاش) وانحرافات السعة / الجهد (الضوضاء) أيضًا على أداء النظام. إذا لم تتأكد من سلامة الإشارات ، فسيستخدم نظام DDR المعلومات الخاطئة ، مما سيزيد بشكل كبير من كثافة أخطاء البت BER (معدل خطأ البت). في النهاية ، سيعمل النظام بشكل غير صحيح وغير فعال.

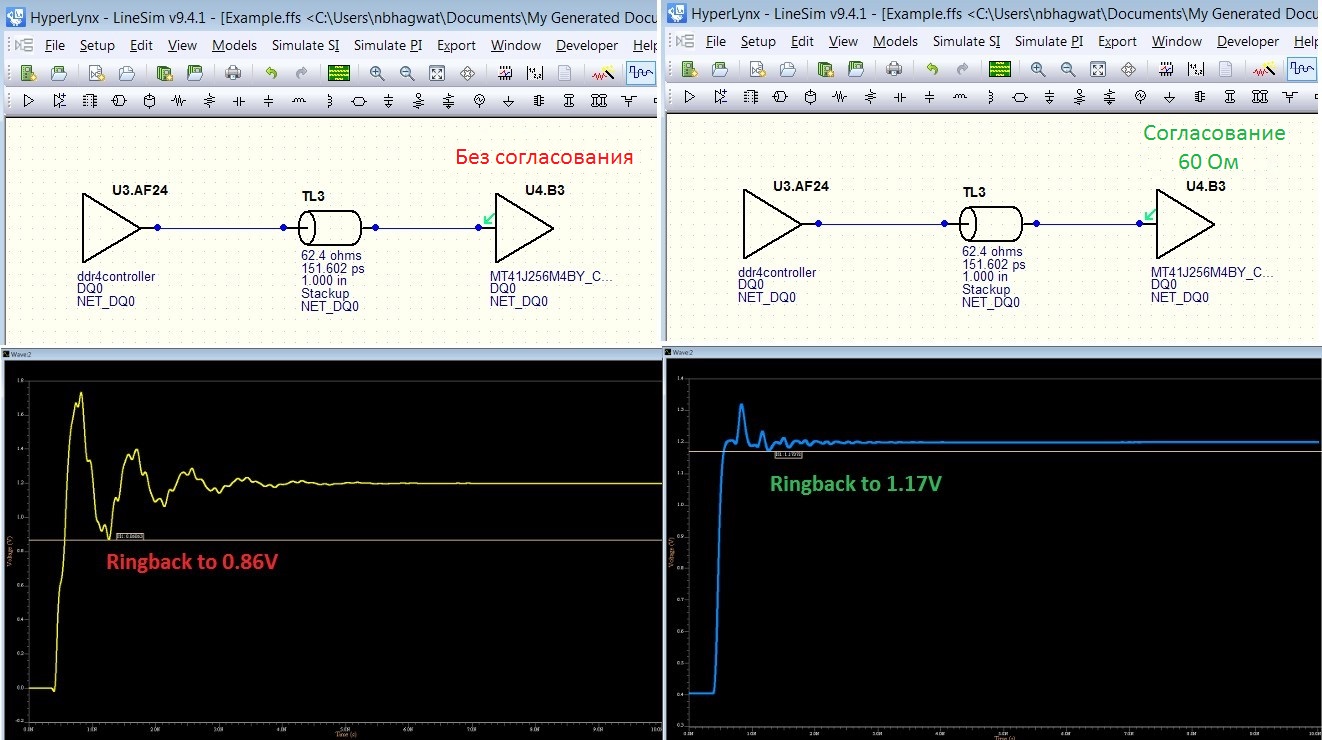

فكر في مثال محدد. إذا قام المهندس بتوصيل جهاز الإرسال بجهاز استقبال غير متناسق يقع على مسافة معينة منه ، فسيكون شكل الموجة مشابهًا للشكل الموضح في الشكل 1 أ: هنا يمكنك بوضوح رؤية "الرنين" عند مستوى 0.86 فولت وانبعاثات زائفة متزايدة عند المستوى 1.75 V بإشارة 1.2 V. كل هذا يمكن أن يؤدي إلى خلل في منطق DDR4 ، وإذا تم تصميم لوحة الدائرة بمثل هذه الطوبولوجيا ، فإن أخطاء احتمالية بنسبة 100 ٪ ستحدث في تدفق البيانات ، والتي بدورها يمكن أن تؤدي إلى التشغيل غير الصحيح للنظام .

من الناحية النظرية ، من الممكن حل المشكلات المتعلقة بـ "الرنين" والانبعاثات عن طريق تقليل طول خط النقل ، ولكن للأسف ، نادرًا ما يعمل هذا في الممارسة. تتمثل الطريقة الأكثر فعالية في مطابقة جهاز الاستقبال / المرسل بمقاومة ، ونتيجة لذلك ينخفض مستوى الضوضاء ، ويصبح شكل الإشارة أفضل بكثير (انظر الشكل 1 ب).

التين. 1. طوبولوجيا تواجه مشاكل في جودة الإشارة: أ) قبل التنسيق ب) بعد التنسيق

التين. 1. طوبولوجيا تواجه مشاكل في جودة الإشارة: أ) قبل التنسيق ب) بعد التنسيقفي هذا الصدد ، يُطرح السؤال عن تصنيف الموافقة الذي يجب استخدامه وكيفية حسابه ، لأنه حتى التغيير البسيط في التصنيف يمكن أن يؤثر بشكل كبير على أداء النظام. الطريقة الوحيدة لحل هذه المشكلة هي المحاكاة ، على وجه الخصوص ، باستخدام معالجات التسوية التفاعلية المستخدمة في HyperLynx.

مشاكل التوقيت في DDRx

نظرًا لأن الحافلات المتوازية التي تعمل بترددات جيجاهيرتز ، مثل DDR3 / 4 ، تستخدم بشكل متزايد في تصميم لوحات الدوائر المطبوعة ، فإن مشاكل سلامة الإشارة تكون حادة بشكل خاص. تختلف ذاكرة DDR3 SDRAM ، على سبيل المثال ، بشكل كبير من حيث السرعة وأداء التردد عن DDR2: الحد الأقصى لتردد ساعة DDR2 هو 800 ميجاهرتز ، والحد الأقصى لتردد DDR3 هو 1600 ميجاهرتز. بسبب انخفاض جهد الإمداد للخلايا ، تمكن مبدعو النوع الجديد من ذاكرة الوصول العشوائي من تقليل استهلاك الطاقة بنسبة تصل إلى 15 ٪ ، والتي ، نظرًا للأداء المثير للإعجاب لـ DDR2 ، يمكن أن تسمى اختراقاً حقيقياً. يستخدم DDR3 طوبولوجيا ناقل / تحكم / تحكم "Fly-by" للشبكة مع مطابقة الوحدة الداخلية (ODT). في نفس الوقت ، تخلق DDR3 مشاكل جديدة لسلامة الإشارة ، على وجه الخصوص ، مرتبطة بدوائر ODT ، ومعدلات بيانات أعلى وتشويه للوقت.

على الرغم من حقيقة أن هناك وحدات تحكم تقوم بمعايرة القراءة / الكتابة التلقائية ، مما يحسن الفترات الزمنية ، يحتاج المطور إلى ضمان التوقيت الصحيح. الحدود الزمنية في واجهات DDR3 صغيرة جدًا لدرجة أن النهج التجريبي للتحسين لم يعد كافيًا ، ومن أجل ضمان تشغيل الواجهة بسرعات عالية ، من الضروري إجراء تحليل مفصل للدائرة.

يصعب تحليل هذه العلاقات الزمنية المعقدة دون مساعدة من أدوات إضافية. من أجل تحديد المشاكل المحتملة وإزالتها بشكل عام أو لحساب العلاقات الزمنية المعقدة ، يجب على المهندسين تحليل علاقات السبب والنتيجة ، وهي مهمة معقدة وتستغرق وقتًا طويلاً.

غالبًا ما تؤدي مشاكل التصميم هذه إلى تأخيرات في تخطيط المشروع ، ونتيجة لذلك ، تزيد بشكل كبير من الوقت الذي يستغرقه المنتج النهائي لدخول السوق. يمكن لأدوات المحاكاة المتطورة والفعالة مساعدة المهندسين في العثور على الأخطاء وتصحيحها بسرعة من خلال تحسين الإشارات إلى مستوى BER مقبول.

تحليل سلامة الإشارة لأنظمة DDR SDRAM

وافقت لجنة التوحيد القياسي الهندسية لأشباه الموصلات في JEDEC على قائمة بالمتطلبات التي يجب اتباعها عند تطوير منتجات عالية الجودة. من المهم أن تلبي SDRAMs DDR هذه المتطلبات لضمان التشغيل السليم ومنع مشاكل سلامة الإشارة. ومع ذلك ، فإن تنفيذ جميع القياسات والحسابات الضرورية غالباً ما يكون محفوفاً بالعديد من الصعوبات.

في بعض الأحيان ، يمكن تجنب هذه الحسابات تمامًا من خلال اتباع تعليمات التخطيط بدقة التي يقدمها بائع وحدة التحكم. ولكن ماذا لو تعذر تنفيذ هذه التوصيات بسبب القيود المختلفة في مشاريع محددة؟ ماذا تفعل إذا استغرق الأمر الكثير من الوقت للتأكد من أن المشروع يلبي جميع التوصيات والمتطلبات؟ في مثل هذه الحالات ، تحتاج إلى استخدام أدوات للتحقق من المشروع بسرعة قبل وضعه في الإنتاج.

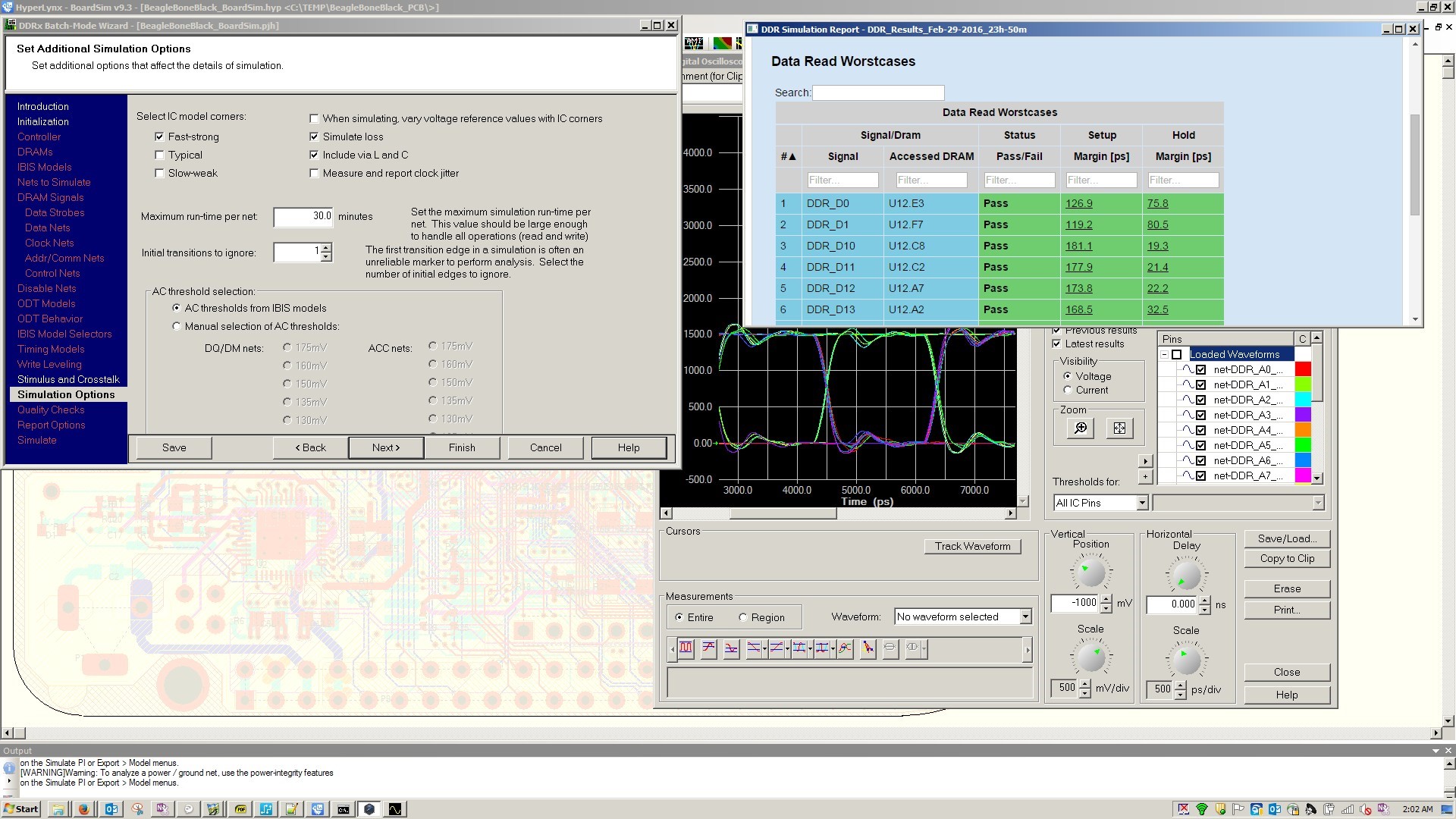

باستخدام HyperLynx DDR (انظر الشكل 2) ، يمكنك محاكاة قناة DDR بأكملها في تكرار واحد. للقيام بذلك ، ما عليك سوى ربط طرازات الجهاز المناسبة المتوفرة على مواقع الشركات المصنعة. بعد ذلك ، سيستغرق وقت الإعداد للمحاكاة عشر دقائق فقط ، مما سيسمح بمزيد من النمذجة دون تأخير.

التين. 2. النمذجة مع المساعد التفاعلي HyperLynx DDR

التين. 2. النمذجة مع المساعد التفاعلي HyperLynx DDRعملية الإعداد بسيطة بشكل بديهي ، حيث يطلب المساعد جميع المعلمات اللازمة لإعداد المحاكاة بشكل تفاعلي. يقوم المستخدم ببساطة بإدخال المعلومات ذات الصلة ، مثل اختيار نماذج IBIS لوحدات التحكم وأجهزة الذاكرة ، ومعدلات النقل لدورات القراءة / الكتابة ، ODT ، وما إلى ذلك. يمكن حفظ جميع التكوينات التي تم إنشاؤها للاستخدام في المستقبل ، مما سيقلل وقت الإعداد في المشاريع المستقبلية. يمكن إجراء المحاكاة قبل أو بعد التتبع ، مما يساعد على تحديد متطلبات مكدس ثنائي الفينيل متعدد الكلور.

تحليل نتائج المحاكاة

تتضمن المحاكاة تحليل سلامة الإشارة ومزامنة ناقل DDR بأكمله. عند الانتهاء من عملية المحاكاة ، يتم إنشاء تقرير يتضمن بيانات عن مرور (عدم اجتياز) الشيكات ، وفقًا لمعلومات التكوين والبيانات التي تم إدخالها في المساعد التفاعلي. يمكن تصفية النتائج وتنظيمها بشكل صحيح من أجل دراسة متأنية لمشاكل التوقيت وسلامة الإشارة في دورات قراءة / كتابة البيانات ، في حافلات العناوين والأوامر أو الدوائر التفاضلية. ترتبط جميع نتائج التقرير ببيانات المحاكاة المقابلة ، للوصول السريع إلى الأداة لعرض الأشكال الموجية الرسومية للإشارات.

يمكن حفظ بيانات المحاكاة في وضع الدُفعات التي تم إنشاؤها بواسطة معالج DDRx إلى القرص ، مما يسمح لك باستخدام HyperLynx مرسمة الذبذبات لمحاكاة العديد من الدوائر في وقت واحد ودراسة مشاكل سلامة الإشارة بالتفصيل في وضع عدم الاتصال.

الخلاصة

تفتح DDR SDRAM إمكانيات جديدة في تطوير الأجهزة الإلكترونية. كما هو الحال مع واجهات أخرى عالية السرعة ، فإن استخدام ذاكرة DDR له العديد من الميزات. يجب دراسة مشكلة سلامة الإشارة بعناية لتجنب التكرارات غير الضرورية والمكلفة في تصنيع المنتجات. تعد النمذجة طريقة ممتازة لحل هذه المشكلة ، مما يسمح لك بمراعاة التأثيرات على مستوى اللوحة ، مثل التغييرات في المعاوقة وتأخير الوقت ، مما يوفر تحكمًا شاملاً في واجهة الذاكرة. ستساعد أدوات التحليل القوية على ضمان امتثال المشاريع لتوصيات JEDEC والتأكد من أن المنتج النهائي سيعمل بأداء وموثوقية عالية.

يمكن مشاركة HyperLynx DDR من قبل العديد من شركات تصميم CAD PCB ، بما في ذلك PADS و Xpedition.

تم نشر هذا المقال في مجلة MODERN ELECTRONICS No. 7، 2018 (www.soel.ru)