مقدمة

أرحب بالجميع. اليوم أريد أن أشارك تجربتي وما زلت ، في رأيي ، أشرح بوضوح عن هذا ، للوهلة الأولى ، معيارًا بسيطًا لوحدة تحكم مضيف USB 2.0.

في البداية ، يمكنك أن تتخيل أن منفذ USB 2.0 هو 4 دبابيس فقط ، اثنان منها ينقلان البيانات ببساطة (مثل ، على سبيل المثال ، منفذ COM) ، ولكن في الواقع ، كل شيء ليس كذلك ، وحتى العكس تمامًا. لا تسمح لنا وحدة تحكم USB ، من حيث المبدأ ، بنقل البيانات عن طريق منفذ COM العادي. EHCI هو معيار معقد إلى حد ما يسمح بنقل بيانات موثوق وسريع من البرنامج إلى الجهاز نفسه ، وفي الاتجاه المعاكس.

قد تجد هذه المقالة مفيدة إذا لم تكن لديك ، على سبيل المثال ، مهارات كتابة كافية لبرامج التشغيل وقراءة وثائق أحد الأجهزة. مثال بسيط: أنت تريد كتابة نظام التشغيل لجهاز كمبيوتر صغير ، بحيث لا تقوم بعض أنظمة تشغيل Windows أو توزيعات Linux الأخرى بتنزيل الحديد ، وتستخدم كل طاقتها حصريًا لأغراضك الخاصة.

ما هي EHCI؟

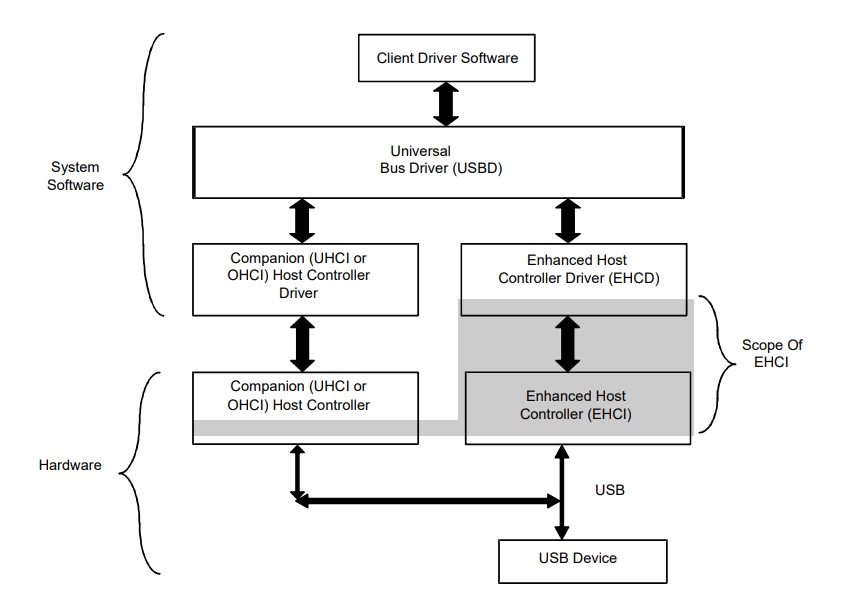

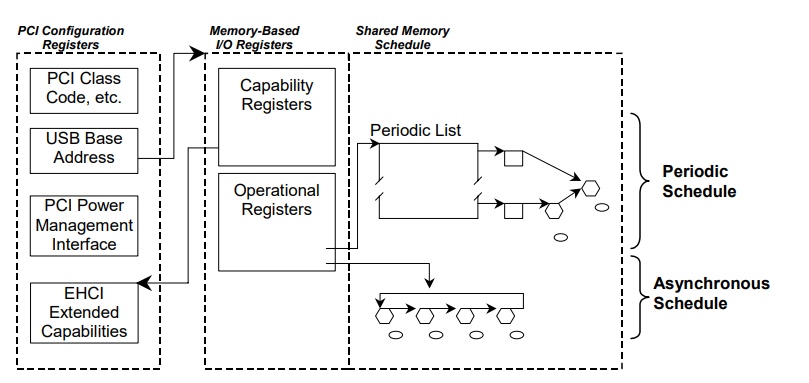

حسنًا ، لنبدأ. EHCI - واجهة تحكم المضيف المحسنة ، تم تصميمها لنقل البيانات والتحكم في الطلبات إلى أجهزة USB ، وفي الاتجاه الآخر ، وفي 99٪ من الحالات ، يمثل رابطًا بين أي برنامج وجهاز مادي. تعمل EHCI كجهاز PCI ، وبالتالي تستخدم MMIO (Memory-Mapped-IO) للتحكم في وحدة التحكم (نعم ، أعرف أن بعض أجهزة PCI تستخدم المنافذ ، ولكن هنا قمت بتعميم كل شيء). تصف وثائق إنتل فقط مبدأ التشغيل ، ولا توجد تلميحات على الإطلاق من الخوارزميات المكتوبة على الأقل في الرمز الزائف. لدى EHCI نوعان من سجلات MMIO: القدرة والتشغيل. يعمل الأول على الحصول على خصائص جهاز التحكم ، بينما يعمل الآخر على التحكم فيه. في الواقع ، سأعلق جوهر الاتصال بين البرنامج ووحدة تحكم EHCI:

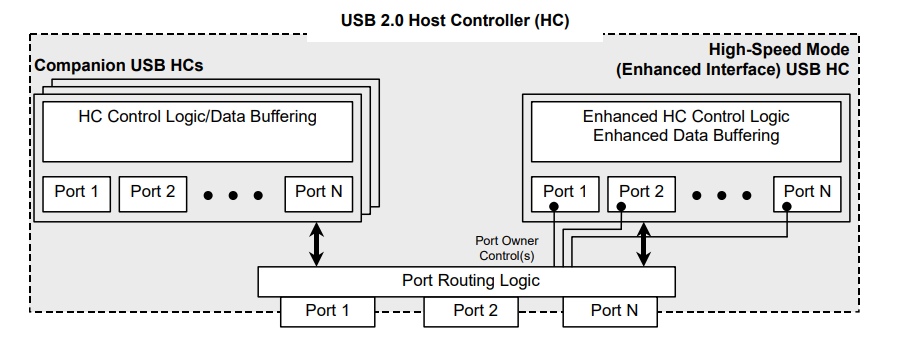

تحتوي كل وحدة تحكم EHCI على عدة منافذ ، يمكن توصيل كل منها بأي جهاز USB. يُرجى أيضًا ملاحظة أن EHCI هي نسخة محسنة من UHCI ، والتي تم تطويرها أيضًا بواسطة Intel قبل بضع سنوات. للتوافق مع الإصدارات السابقة ، ستكون أي وحدة تحكم UHCI / OHCI تحتوي على إصدار أقل من EHCI مصاحبة لـ EHCI. على سبيل المثال ، لديك لوحة مفاتيح USB (ومعظم لوحات المفاتيح لهذا العام حتى الآن كانت كذلك) تعمل على USB 1.1 (لاحظ أن السرعة القصوى لـ USB 1.1 هي 12 ميغابت في الثانية ، و FullSpeed USB 2.0 مزود بنطاق ترددي تصل إلى 480 ميجا بت في الثانية) ، ولديك جهاز كمبيوتر مزود بمنفذ USB 2.0 ، عند توصيل لوحة المفاتيح بالكمبيوتر ، ستعمل وحدة تحكم مضيف EHCI بأي شكل من الأشكال مع USB 1.1. يظهر هذا النموذج في الرسم البياني التالي:

أيضًا ، للمستقبل ، أريد أن أحذرك على الفور من أن برنامج التشغيل الخاص بك قد لا يعمل بشكل صحيح بسبب مثل هذا الموقف السخيف: قمت بتهيئة UHCI ، ثم EHCI ، أثناء إضافة جهازين متطابقين ، قم بتعيين بت التحكم في مالك المنفذ إلى سجل المنفذ ، ثم توقف UHCI عن العمل ، بسبب حقيقة أن EHCI يسحب المنفذ تلقائيًا إلى نفسه ، ويتوقف المنفذ على UHCI عن الاستجابة ، ويجب مراقبة هذا الموقف.

أيضًا ، دعنا نلقي نظرة على رسم تخطيطي يوضح بنية EHCI نفسها:

على اليمين مكتوب عن قائمة الانتظار - عنهم بعد ذلك بقليل.

يسجل جهاز تحكم EHCI

بادئ ذي بدء ، أود أن أوضح مرة أخرى أنه من خلال هذه السجلات ستتحكم في جهازك ، وبالتالي فهي مهمة جدًا - وبدونها ، لا يمكن برمجة EHCI.

تحتاج أولاً إلى الحصول على عنوان MMIO المعطى لوحدة التحكم هذه ، عند الإزاحة + 0x10 سيكون عنوان سجلاتنا التي طال انتظارها. هناك شيء واحد: أولاً ، تذهب سجلات القدرة ، وبعدها فقط - التشغيل ، وبالتالي ، عند الإزاحة 0 (من العنوان السابق الذي تلقيناه عند الإزاحة 0x10 بالنسبة إلى بداية MMIO الخاص بـ EHCI) هناك بايت واحد - طول تسجيلات القدرة.

سجلات القدرة

عند الإزاحة 2 ،

يوجد سجل

HCIVERSION - رقم المراجعة الخاص بـ HC هذا ، والذي يأخذ 2 بايت ويحتوي على نسخة BCD من المراجعة (ما يمكن العثور عليه BCD على ويكيبيديا).

عند الإزاحة +4 ،

يوجد سجل

HCSPARAMS ، حجمه هو كلمتان ، ويحتوي على المعلمات الهيكلية للجهاز

وتوضح بتاته ما يلي:

- Bit 16 - مؤشرات المنفذ - مصابيح LED المتوفرة لأجهزة USB المتصلة.

- Bits 15:12 - رقم وحدة التحكم المصاحبة المعينة لوحدة التحكم هذه

- Bits 11: 8 - عدد المنافذ على وحدة التحكم المصاحبة

- Bit 7 - قواعد توجيه المنفذ - يوضح كيفية تعيين هذه المنافذ إلى المنافذ المصاحبة

- Bit 4 - التحكم في طاقة المنفذ - يشير إلى ما إذا كان من الضروري تشغيل الطاقة لكل منفذ ، 0 - يتم توفير الطاقة تلقائيًا

- Bits 3: 0 - عدد المنافذ لوحدة التحكم هذه.

- عند الإزاحة +8 يكمن سجل HCCPARAMS - إنه يعرض معلمات التوافق ، بتاته تعني ما يلي:

- بت 2 - توفر طابور غير متزامن ،

- بت 1 - توفر طابور دوري (تسلسلي)

- بت 0 - 64 بت التوافق

سجلات العملية

عند الإزاحة 0 ، يكون سجل

USBCMD هو سجل أوامر وحدة التحكم ، وتعني

بتاته ما يلي:

- Bits 23:16 - التحكم في عتبة المقاطعة - يوضح عدد الإطارات الصغيرة التي سيتم استخدامها لإطار عادي واحد. كلما كانت أكبر ، وأسرع ، ولكن إذا كان أكثر من 8 ، فستتم معالجة الإطارات الصغيرة بنفس سرعة 8.

- بت 6 - المقاطعة بعد كل معاملة في قائمة الانتظار غير المتزامنة ،

- بت 5 - هو قائمة الانتظار غير المتزامنة المستخدمة

- Bit 4 - استخدام قائمة الانتظار التسلسلية ،

- Bits 3: 2 - حجم FrameList'a (المزيد عن ذلك لاحقًا). 0 يعني 1024 عنصرًا ، 1 - 512 ، 2 - 256 ، 3 - محجوز

- Bit 1 - تعيين لإعادة تعيين وحدة تحكم المضيف.

- بت 0 - تشغيل / إيقاف

.

بعد ذلك ، عند الإزاحة +4 ، يوجد سجل

USBSTS - حالة وحدة تحكم المضيف ،

- يشير البت 15 إلى ما إذا كان يتم استخدام قائمة انتظار غير متزامنة.

- يشير البت 14 إلى ما إذا كان يتم استخدام قائمة انتظار تسلسلية ،

- بت 13 - يشير إلى أنه تم الكشف عن قائمة انتظار فارغة غير متزامنة ،

- يتم تعيين البت 12 إلى 1 ، إذا حدث خطأ أثناء معالجة المعاملة ، فستقوم وحدة التحكم المضيفة بإيقاف جميع قوائم الانتظار.

- يتم تعيين بت 4 إلى 1 ، إذا حدث خطأ فادح ، توقف وحدة تحكم المضيف جميع قوائم الانتظار.

- Bit 3 FrameList (Register) Rollover - يتم ضبطه على 1 عندما تقوم وحدة تحكم المضيف بمعالجة قائمة الإطارات بأكملها.

- بت 1 - مقاطعة خطأ USB - هل أقوم بإنشاء مقاطعة خطأ؟

- بت 0 - مقاطعة USB - يتم تعيينه بعد معالجة المعاملات الناجحة ، إذا تم تثبيت بطاقة IOC في TD

لا تعب؟ يمكنك صب طيور النورس القوية وإحضار الكبد ، نحن في البداية!

عند الإزاحة +8 ، يوجد تسجيل

USBINTR - سجل تمكين المقاطعة

لكي لا تكتب لفترة طويلة ، والأكثر من ذلك ، حتى لا تقرأ لفترة طويلة ، يمكن العثور على قيم بتات هذا السجل في المواصفات ، وسيتم ترك رابط لها أدناه. هنا فقط أكتب 0 ، لأن ليس لدي أي رغبة على الإطلاق في كتابة معالجات ، ومقاطعات الخريطة ، وما إلى ذلك ، لذلك أعتقد أن هذا لا معنى له على الإطلاق.

عند الإزاحة +12 (0x0C) ،

يوجد سجل

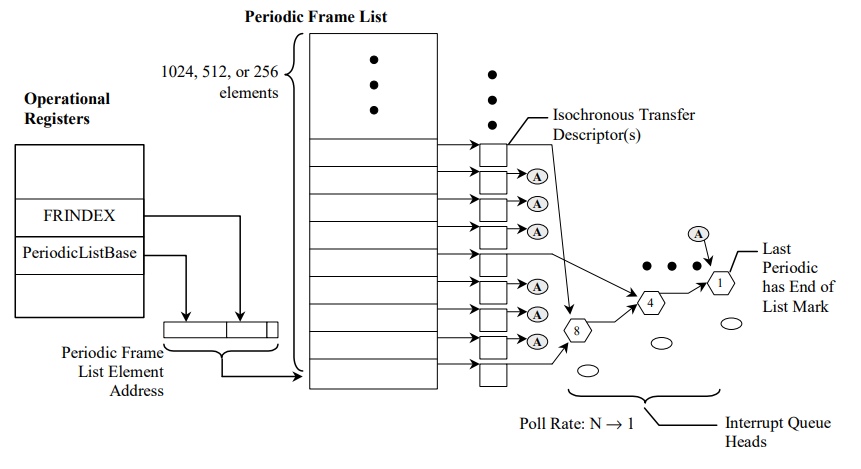

FRINDEX ، حيث يكمن رقم الإطار الحالي ببساطة ، وأريد أن أشير إلى أن البتات الأربعة الأخيرة تظهر رقم الإطار الصغير ، في 28 بت العلوي رقم الإطار (القيمة ليست بالضرورة أصغر من حجم frameList ولكن إذا كنت بحاجة إلى فهرس ، فمن الأفضل أن تأخذه بقناع 0x3FF (أو 0x1FF ، وما إلى ذلك).

يكون سجل

CTRLDSSEGMENT في الإزاحة + 0x10 ؛ ويظهر على وحدة تحكم المضيف أهم 32 بتًا من عنوان ورقة الإطار.

يحتوي سجل

PERIODICLISTBASE على إزاحة قدرها + 0x14 ، يمكنك وضع 32 بتًا أقل من ورقة الإطار فيه ، لاحظ أنه يجب محاذاة العنوان مع حجم صفحة الذاكرة (4096).

يحتوي سجل

ASYNCLISTADDR على إزاحة قدرها + 0x18 ، يمكنك وضع عنوان قائمة الانتظار غير المتزامنة فيه ، لاحظ أنه يجب محاذاة عند حد 32 بايت ، بينما يجب أن يكون في أول أربعة غيغابايت من الذاكرة الفعلية.

يشير تسجيل

CONFIGFLAG إلى ما إذا تم تكوين الجهاز. يجب تعيين بت 0 بعد الانتهاء من إعداد الجهاز ، مع إزاحة + 0x40.

دعنا ننتقل إلى تسجيلات المنفذ. يحتوي كل منفذ على سجل حالة الأمر الخاص به ، ويتم إزاحة كل سجل منفذ

+ 0x44 + (رقم PortNumber - 1) * 4 ، بتاته تعني ما يلي:

- Bit 12 - طاقة المنفذ ، 1 - يتم توفير الطاقة ، 0 - لا.

- تم تعيين Bit 8 - Port Rest - لإعادة تعيين الجهاز.

- Bit 3 - تمكين / تعطيل المنفذ - يتم تعيينه عند تغيير حالة "تضمين" المنفذ.

- بت 2 - تشغيل / إيقاف المنفذ.

- Bit 1 - تغيير حالة الاتصال ، يتم تعيينه على 1 ، على سبيل المثال ، إذا قمت بتوصيل جهاز USB أو فصله.

- بت 0 - حالة الاتصال ، 1 - متصل ، 0 - لا.

الآن دعنا ننتقل إلى العصير نفسه.

نقل البيانات وهياكل الاستعلام

يتضمن تنظيم بنية معالجة الطلبات قوائم الانتظار واصفات النقل (TDs).

في الوقت الحالي ، سننظر فقط في 3 هياكل.

قائمة متسلسلة

يتم تنظيم القائمة التسلسلية (الدورية ، Pereodic) على النحو التالي:

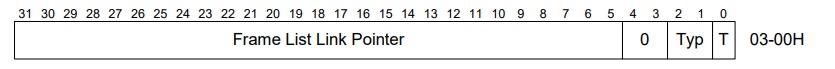

كما ترى في الرسم البياني ، تبدأ المعالجة بالحصول على الإطار المطلوب من إطار الورقة ، حيث يشغل كل عنصر من عناصره 4 بايت وله البنية التالية:

كما ترى في الصورة ، يتم محاذاة نقل قائمة الانتظار / الواصف عند حد 32 بايت ، يعني البت 0 أن وحدة تحكم المضيف لن تعالج هذا العنصر ، وتشير البتات 3: 1 إلى نوع ما ستتعامل معه وحدة التحكم المضيفة: 0 - TD متزامن (iTD) ، 1 - بدوره ، 2 و 3 في هذه المقالة لن أفكر.

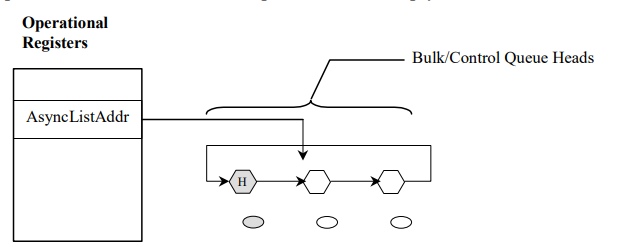

قائمة انتظار غير متزامنة

تقوم وحدة تحكم المضيف بمعالجة قائمة الانتظار هذه فقط عندما يكون الإطار المتسلسل فارغًا أو عندما تقوم وحدة تحكم المضيف بمعالجة القائمة التسلسلية بالكامل.

قائمة الانتظار غير المتزامنة هي مؤشر لقائمة انتظار تحتوي على قوائم انتظار أخرى تحتاج إلى معالجة. مخطط:

qTD (واصف نقل عنصر قائمة الانتظار)

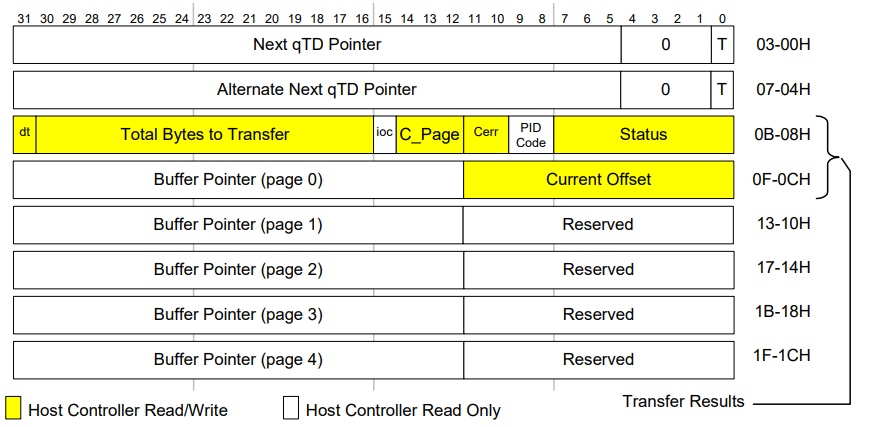

هذا TD لديه الهيكل التالي:

مؤشر qTD التالي

مؤشر qTD التالي - مؤشر استمرار قائمة الانتظار للمعالجة (للتنفيذ الأفقي) ، بت 0 يشير مؤشر qTD التالي إلى عدم وجود قائمة انتظار أخرى.

رمز qTD - الرمز المميز لـ TD ، يعرض معلمات نقل البيانات:

- Bit 31 - تبديل البيانات (المزيد عن ذلك لاحقًا)

- بت 30:16 - كمية البيانات المراد نقلها ، بعد إتمام المعاملة ، تنخفض قيمتها بمقدار البيانات المنقولة.

- بت 15 - IOC - المقاطعة عند اكتمالها - تسبب المقاطعة بعد اكتمال معالجة الواصف.

- توضح البتات 14:12 عدد المخزن المؤقت الحالي إلى / الذي يتم تبادل البيانات منه ، المزيد عن ذلك لاحقًا.

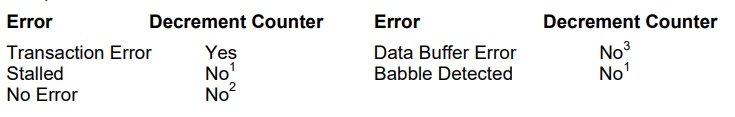

- Bits 11:10 - عدد الأخطاء المسموح بها. يوضح هذا الجدول عندما ينخفض عدد الأخطاء:

الحاشية السفلية 1 - يؤدي الكشف عن Babble أو Stall تلقائيًا إلى إيقاف تنفيذ رأس قائمة الانتظار. الحاشية السفلية 3 - أخطاء المخزن المؤقت للبيانات هي مشاكل مع المضيف. لا تأخذ في الاعتبار عمليات إعادة محاولة الجهاز. - 9: 8 - رمز PID - نوع الرمز المميز: 0 - الرمز المميز للإدخال (من المضيف إلى الجهاز) ، 1 - الرمز المميز للإخراج (من الجهاز إلى المضيف) ، 2 - الرمز "SETUP"

- البتات 7: 0 تشير إلى حالة TD:

تشير البتة 7 إلى أن TD في حالة نشطة (بمعنى أن وحدة تحكم المضيف تعالج TD)

بت 6 - تم الإيقاف - يشير إلى حدوث خطأ وتوقف تنفيذ TD.

Bit 4 - Babble Detected - كمية البيانات التي أرسلناها إلى الجهاز ، أو لكل ثورة ، أقل مما نرسله ، على سبيل المثال ، أرسل لنا الجهاز 100 بايت من البيانات ، ونقرأ 50 بايت فقط ، ثم 50 بايت أخرى سيتم أيضًا تعيين البت المُوقوف إذا تم تعيين هذا البت إلى 1.

بت 3 - خطأ في المعاملة - حدث خطأ أثناء المعاملة.

قائمة مؤشر صفحة المخزن المؤقت qTD - أي من 5 مخازن. يحتوي على رابط إلى المكان الذي يجب أن تتم فيه المعاملة في الذاكرة (إرسال البيانات إلى الجهاز / استقبال البيانات من الجهاز) ، يجب محاذاة جميع العناوين في المخازن المؤقتة ، باستثناء العنوان الأول ، مع حجم الصفحة (4096 بايت).

رأس الخط

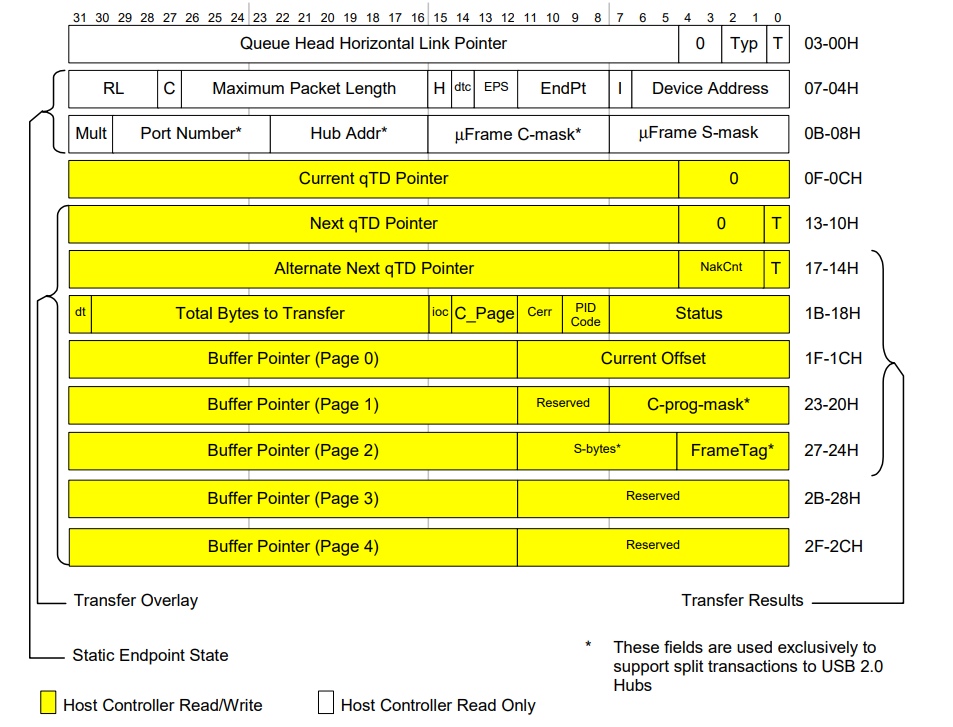

يحتوي رأس قائمة الانتظار على الهيكل التالي:

مؤشر الارتباط الأفقي لرأس قائمة الانتظار

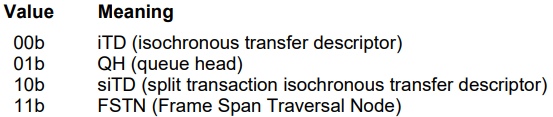

مؤشر الارتباط الأفقي لرأس قائمة الانتظار - المؤشر إلى قائمة الانتظار التالية ، تحتوي البتات 2: 1 على القيم التالية اعتمادًا على نوع قائمة الانتظار:

قدرات / خصائص نقطة النهاية

قدرات / خصائص نقطة النهاية -

خصائص قائمة الانتظار:

- تحتوي البتات 26:16 على الحد الأقصى لحجم الحزمة للإرسال

- Bit 14: التحكم في تبديل البيانات - يوضح المكان الذي يجب أن تأخذ فيه وحدة تحكم المضيف قيمة تبديل البيانات الأولية ، 0 - يتجاهل بت DT في qTD ، ويحفظ بت DT لرأس قائمة الانتظار.

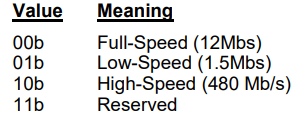

- Bit 13:12 - خصائص معدل الإرسال:

- Bits 11: 8 - رقم نقطة النهاية التي تم تقديم الطلب إليها

- بت 6: 0 - عنوان الجهاز

إمكانات نقطة النهاية: Head Queue Head DWord 2 - استمرار الكلمة المزدوجة السابقة:

- بت 29:23 - رقم المحور

- بت 22:16 - عنوان المحور

مؤشر ارتباط qTD الحالي - المؤشر إلى qTD الحالي.

ننتقل إلى الأكثر إثارة للاهتمام.

سائق EHCI

لنبدأ بالاستفسارات التي يمكن لـ EHCI الإجابة عليها. هناك نوعان من الطلبات: Control - a la command و Bulk - إلى نقاط النهاية ، لتبادل البيانات ، على سبيل المثال ، تستخدم الغالبية العظمى من محركات أقراص USB المحمولة (USB MassStorage) نوع نقل البيانات Bulk / Bulk / Bulk. يستخدم الماوس ولوحة المفاتيح أيضًا الطلبات المجمعة لنقل البيانات.

تهيئة EHCI وتكوين قوائم انتظار غير متزامنة ومتسلسلة:

في الواقع ، رمز إعادة تعيين المنفذ إلى حالته الأصلية:

volatile u32 *reg = &hc->opRegs->ports[port];

طلب التحكم بالجهاز:

static void EhciDevControl(UsbDevice *dev, UsbTransfer *t) { EhciController *hc = (EhciController *)dev->hc; UsbDevReq *req = t->req;

رمز معالجة قائمة الانتظار:

if (qh->token & TD_TOK_HALTED) { t->success = false; t->complete = true; } else if (qh->nextLink & PTR_TERMINATE) if (~qh->token & TD_TOK_ACTIVE) { if (qh->token & TD_TOK_DATABUFFER) kprintf(" Data Buffer Error\n"); if (qh->token & TD_TOK_BABBLE) kprintf(" Babble Detected\n"); if (qh->token & TD_TOK_XACT) kprintf(" Transaction Error\n"); if (qh->token & TD_TOK_MMF) kprintf(" Missed Micro-Frame\n"); t->success = true; t->complete = true; } if (t->complete) ....

والآن طلب نقطة النهاية (طلب مجمع)

static void EhciDevIntr(UsbDevice *dev, UsbTransfer *t) { EhciController *hc = (EhciController *)dev->hc;

أعتقد أن الموضوع مثير للاهتمام للغاية ، على الإنترنت باللغة الروسية لا يوجد تقريبًا أي توثيق وأوصاف ومقالات حول هذا الموضوع ، وإذا كان هناك ، فهو ضبابي للغاية. إذا كان موضوع العمل مع الأجهزة وتطوير نظام التشغيل مثيرًا للاهتمام ، فهناك الكثير لتقوله.

أرصفة:

مواصفات